# JPE 16-3-2

http://dx.doi.org/10.6113/JPE.2016.16.3.832 ISSN(Print): 1598-2092 / ISSN(Online): 2093-4718

# Effect of Non-Idealities on the Design and Performance of a DC-DC Buck Converter

Man Mohan Garg<sup>†</sup>, Mukesh Kumar Pathak<sup>\*</sup>, and Yogesh Vijay Hote<sup>\*</sup>

<sup>†,\*</sup>Department of Electrical Engineering, Indian Institute of Technology (IIT), Roorkee, India

# Abstract

In this study, the performance of a direct current (DC)–DC buck converter is analyzed in the presence of non-idealities in passive components and semiconductor devices. The effect of these non-idealities on the various design issues of a DC–DC buck converter is studied. An improved expression for duty cycle is developed to compensate the losses that occur because of the non-idealities. The design equations for inductor and capacitor calculation are modified based on this improved expression. The effect of the variation in capacitor equivalent series resistance (ESR) on output voltage ripple (OVR) is analyzed in detail. It is observed that the value of required capacitance increases with ESR. However, beyond a maximum value of ESR ( $r_{c,max}$ ), the capacitor is unable to maintain OVR within a specified limit. The expression of  $r_{c,max}$  is derived in terms of specified OVR and inductor current ripple. Finally, these theoretical studies are validated through MATLAB simulation and experimental results.

Key words: Buck converter, Duty cycle, Equivalent series resistance, Non-idealities, Output voltage ripple

### I. INTRODUCTION

Direct current (DC)-DC converters are widely used as power supply in various applications [1]-[4]. Several applications, such as aerospace, military, chemical refineries, and mines, require highly regulated, optimally designed, and compact power supplies. For such applications, an optimum design of inductance and capacitance for buck converter is reported in [5], [6]. In all practical DC-DC converters, power loss occurs because of the internal resistances of inductors, capacitors, and non-ideal switching devices. Most power electronic textbooks and papers have neglected some or all these non-ideal elements while analyzing and designing DC-DC converters [7]-[11]. However, this condition is unacceptable for an accurate and well-designed power supply because these non-idealities affect the desired values of the duty cycle, inductor, and capacitor of a DC-DC converter [12], [13]. For example, the expression for the duty cycle of an ideal buck converter is

$$D = V_o / V_g \tag{1}$$

where  $V_{0}$  is the output voltage, and  $V_{g}$  is the input voltage.

However, this relation does not remain valid for a non-ideal buck converter. Owing to the parasitic resistances of inductor, capacitor, diode, and switch, practical DC–DC converters have power losses. Therefore, the actual duty cycle of a non-ideal DC–DC buck converter should be greater than the ideal duty cycle given in Equ. (1) to compensate these losses. An improved expression for this actual duty cycle is derived in this study.

Similarly, the equivalent series resistance (ESR) of an output capacitor plays an important role in the design of capacitors [14]. As the ESR increases, the output voltage ripples (OVR) also increases, thereby reducing the effectiveness of filter capacitors. Moreover, high ESR may lead to instability and increase the power loss in converters [15]. Therefore, arbitrary selection of ESR is inadvisable for a precisely designed DC-DC buck converter. However, the ESR of a capacitor is a parasitic parameter that cannot be avoided by capacitor manufacturers. Nonetheless, power supply designers always prefer a capacitance with low ESR. No analytical solution is available in the literature to evaluate the upper limit of ESR that can be used without exceeding the specified OVR at a particular switching frequency. In this study, a formula for the maximum value of ESR is developed through an in-depth analysis of capacitor voltage ripples to select a capacitor with proper ESR.

The remainder of this paper is organized as follows to

Manuscript received Jan. 29, 2015; accepted Aug. 10, 2015

Recommended for publication by Associate Editor Joung-Hu Park. <sup>†</sup>Corresponding Author: garg.mbm@gmail.com

Tel: +91-1332-285-311, Indian Institute of Technology, Roorkee \*Department of Electrical Engineering, Indian Institute of Technology (IIT), Roorkee, India

resolve the above-mentioned issues for a buck converter: First, a detailed analysis of a non-ideal buck converter is presented. Second, improved relationships for duty cycle, inductance, and capacitance design are proposed. Third, the analytical expression for maximum allowable ESR for specified OVR is proposed. Finally, MATLAB simulations and experimental results are obtained to confirm these theoretical studies.

# II. ANALYSIS OF A NON-IDEAL DC–DC BUCK CONVERTER

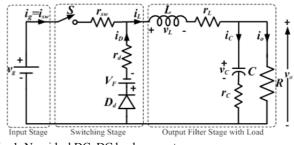

The power circuit of a non-ideal DC–DC buck converter is shown in Fig. 1. All symbols have a standard meaning, as indicated in Table I. The buck converter is operating in a continuous current conduction mode with duty cycle *D* and switching frequency *f* (or switching period *T*) [7]. The voltage and current equations of the buck converter during the switch-on period  $(0 < t \le DT)$  and the switch-off period  $(DT < t \le T)$  are expressed below:

*Mode 1*: Switch-on  $(0 \le t \le DT)$

$$v_{L,on}(t) = L \frac{di_L(t)}{dt} = v_g(t) - (r_{sw} + r_L)i_L(t) - v_o(t)$$

(2)

$$i_{c,on}(t) = i_L(t) - \frac{v_o(t)}{R}$$

(3)

$$v_{o,on}(t) = v_c(t) + r_c i_c(t)$$

$$\tag{4}$$

*Mode 2*: Switch-off  $(DT < t \le T)$

$$v_{L,off}(t) = L \frac{di_L(t)}{dt} = -(r_d + r_L)i_L(t) - V_F - v_o(t)$$

(5)

$$i_{c,off}(t) = i_L(t) - \frac{v_o(t)}{R}$$

(6)

$$v_{o,off}(t) = v_c(t) + r_c i_c(t)$$

(7)

### A. Steady-State Analysis

For steady-state analysis, the time variables are substituted by their respective DC values as [8]

$i_L(t) = I_L, v_g(t) = V_g, v_c(t) = V_C v_o(t) = V_o.$

According to the principle of inductor volt-second balance, in the steady-state, the average inductor voltage must be equal to zero.

$$V_{L} = \frac{1}{T} \int_{0}^{T} v_{L}(t) dt = D v_{L,on}(t) + (1 - D) v_{L,off}(t) = 0$$

(8)

Similarly, according to the principle of capacitor charge balance, in the steady-state, the average capacitor current must be equal to zero.

$$I_{c} = \frac{1}{T} \int_{0}^{T} i_{c}(t) dt = Di_{c,on}(t) + (1 - D)i_{c,off}(t) = 0$$

(9)

The average output voltage of the buck converter is

$$V_o = \frac{1}{T} \int_0^T v_o(t) dt = D v_{o,on}(t) + (1 - D) v_{o,off}(t) .$$

(10)

By substituting Equs. (2) and (5) into Equ. (8), we obtain

Fig. 1. Non-ideal DC–DC buck converter.

$$DV_g = D'V_F + V_o + (r_L + Dr_{sw} + D'r_d)I_L.$$

(11)

Substituting Equs. (3) and (6) into Equ. (9) obtains

$$I_L = \frac{V_o}{R} = I_o . \tag{12}$$

Similarly, substituting Equs. (4), (7), and (9) into Equ. (10) gives

$$V_o = V_C \,. \tag{13}$$

Replacing Equ. (12) into Equ. (11) provides the relationship for average output voltage as

$$V_{o} = \frac{DV_{g} - D'V_{F}}{1 + \frac{(r_{L} + Dr_{sw} + D'r_{d})}{R}},$$

(14)

where D' = 1 - D.

Equ. (14) depicts that the output voltage of the buck converter depends on non-idealities and load resistance.

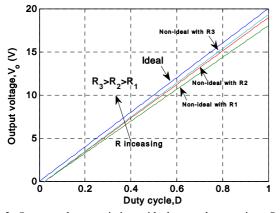

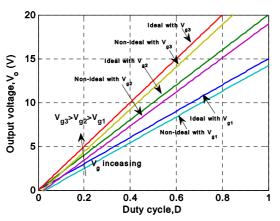

The output voltage variation versus duty cycle plot is shown in Fig. 2 at a constant input voltage and different load resistances. For a particular duty cycle, the non-ideal buck converter produces an output voltage less than that of the ideal buck converter. The output voltage decreases further as the load resistance is decreased. Fig. 3 shows the output voltage variation for different values of input voltages at constant R. For a particular duty cycle, the difference between the output voltage of ideal and non-ideal buck converter becomes larger as input voltage increases. Therefore, the metal oxide semiconductor field-effect transistor (MOSFET) switch should be kept ON for an extended time to achieve the same output voltage in the presence of non-idealities. In other words, the actual duty cycle must be greater than the ideal duty cycle given by Equ. (1).

An improved expression of actual duty cycle is derived by solving Equ. (14) as

$$D = D_{ideal} \frac{1 + \frac{r_L}{R} + \frac{r_d}{R} + \frac{V_F}{V_o}}{1 + \left(\frac{r_d - r_{sw}}{R}\right) \frac{V_o}{V_g} + \frac{V_F}{V_g}},$$

(15)

where  $D_{\text{ideal}} = V_{\text{o}}/V_{\text{g}}$  is the duty cycle for an ideal buck converter.

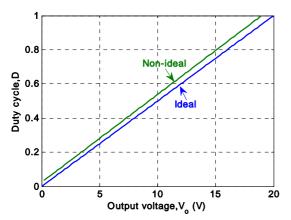

The modified duty cycle D in Equ. (15) and the ideal duty cycle  $D_{\text{ideal}}$  in Equ. (1) are plotted with the desired output voltage  $(V_o)$ , as shown in Fig. 4. It verifies that the actual duty cycle should be greater than the ideal duty cycle to obtain the

Fig. 2. Output voltage variation with duty cycle at various R and constant  $V_{g}$ .

Fig. 3. Output voltage variation with duty cycle at various  $V_g$  and constant R.

Fig. 4. Duty cycle variation with output voltage.

desired output voltage.

# B. Inductor Current Ripple (ICR) and Inductor Design

Let  $x_L$  be the ICR factor and  $\Delta i_L$  be the ripple current such that  $\Delta i_L = x_L I_L$ .

The magnitude of ripple current  $\Delta i_{\rm L}$  in the steady-state is

$$\Delta i_{L} = \frac{(r_{d} + r_{L})I_{L} + V_{F} + V_{o}}{L}D'T .$$

(16)

Substituting  $I_{\rm L}$  from Equ. (12),

Fig. 5. Inductance variation with duty cycle.

Fig. 6. Capacitor current and voltage ripple waveforms.

$$\Delta i_L = \frac{D'V_o}{Lf} \left( 1 + \frac{V_F}{V_o} + \frac{r_L + r_d}{R} \right). \tag{17}$$

Replacing  $\Delta i_{\rm L} = x_{\rm L} I_{\rm L} = x_{\rm L} V_{\rm O}/R$  and rearranging Equ. (17),

$$L = \frac{(1-D)R}{x_L f} \left( 1 + \frac{V_F}{V_o} + \frac{r_d + r_L}{R} \right).$$

(18)

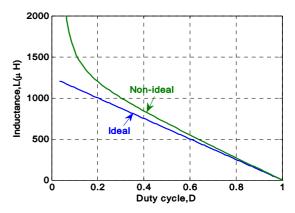

Equ. (18) provides the design value of inductance for the desired ICR in terms of converter parameters and non-ideal elements. The required inductance is calculated for ideal and non-ideal buck converters and is plotted with respect to duty cycle in Fig. 5, which depicts clearly that in the non-ideal case, the required inductance value is more than the ideal case. The difference becomes significant at low duty cycles.

### C. OVR and Capacitor Design

The capacitor current and voltage ripple waveforms in the steady-state are shown in Fig. 6. If the ESR of output capacitor is considered, then the OVR  $\Delta v_0$  consists of the following two components:

1. Voltage ripple caused by capacitor  $(\Delta v_c)$

2. Voltage ripple caused by the presence of ESR ( $\Delta v_{rc}$ ) Analysis during switch-on (0 < t  $\leq$  DT): The capacitor current

Analysis during switch-on  $(0 < t \le DT)$ . The capacitor current dynamics can be given as [16]

$$i_c(t) = \frac{\Delta i_L t}{DT} - \frac{\Delta i_L}{2}.$$

(19)

The voltage ripple contribution by the capacitor itself is

$$\Delta v_c(t) = \frac{1}{C} \int_0^t i_c(t) dt + \Delta v_c(0) = \frac{\Delta i_L}{2C} \left( \frac{t^2}{DT} - t \right) + \Delta v_c(0) , (20)$$

where  $\Delta v_{c}(0)$  is the initial voltage across the capacitor at t = 0. The voltage ripple contribution by the ESR of the capacitor is

$$\Delta v_{rc}(t) = r_c i_c(t) = r_c \Delta i_L \left(\frac{t}{DT} - \frac{1}{2}\right).$$

(21)

Therefore, the total voltage ripple during the switch-on period is

$$\Delta v_o(t) = \Delta i_L \left[ \frac{t^2}{2CDT} + \left( \frac{r_c}{DT} - \frac{1}{2C} \right) t - \frac{r_c}{2} \right] + \Delta v_c(0) . \quad (22)$$

The minimum value of  $\Delta v_0(t)$  occurs at time  $t_1$  and is given by

$$t_{1} = \frac{DT}{2} - r_{c}C \text{ and } \Delta v_{o}\left(t_{1}\right) = -\Delta i_{L}\left(\frac{DT}{8C} + \frac{r_{c}^{2}C}{2DT}\right) + \Delta v_{c}\left(0\right), (23)$$

$$\Delta v_{rc}(t_1) = -\Delta i_L \frac{r_c^2 C}{DT}, \Delta v_c(t_1) = \Delta i_L \left(-\frac{DT}{8C} + \frac{r_c^2 C}{2DT}\right) + \Delta v_c(0) (24)$$

Analysis during switch-off  $(DT < t \le T)$ : The capacitor current dynamics can be given as

$$i_c(t) = \frac{-\Delta i_L(t - DT)}{D'T} + \frac{\Delta i_L}{2}.$$

(25)

The voltage ripple contribution by the capacitor itself is

$$\Delta v_c(t) = \frac{\Delta i_L}{2C} \left( -\frac{\left(t - DT\right)^2}{D'T} + \left(t - DT\right) \right) + \Delta v_c(DT), (26)$$

where  $\Delta v_c(DT)$  is the initial voltage across the capacitor at t = DT. In the steady-state,  $\Delta v_c(DT) = \Delta v_c(0)$ .

The voltage ripple contribution by the ESR of the capacitor is

$$\Delta v_{rc}(t) = r_c i_c(t) = r_c \Delta i_L \left(\frac{-(t-DT)}{D'T} + \frac{1}{2}\right).$$

(27)

Therefore, the total voltage ripple during the switch-off period is

$$\Delta v_o(t) = \Delta i_L \left[ \frac{-(t - DT)^2}{2CD'T} + \left( \frac{-r_c}{D'T} + \frac{1}{2C} \right) (t - DT) + \frac{r_c}{2} \right] + \Delta v_c(DT)$$

(28)

The maximum value of  $\Delta v_0(t)$  occurs at time  $t_2$  and is given by

$$t_{2} = \frac{(1+D)T}{2} - r_{c}C \text{ and } \Delta v_{o}(t_{2}) = \Delta i_{L} \left(\frac{D'T}{8C} + \frac{r_{c}^{2}C}{2D'T}\right) + \Delta v_{c}(DT), (29)$$

$$\Delta v_{rc}(t_2) = \Delta i_L \frac{r_c^2 C}{(1-D)T}, \ \Delta v_c(t_2) = \Delta i_L \left(\frac{D'T}{8C} - \frac{r_c^2 C}{2D'T}\right) + \Delta v_c(DT) (30)$$

1) Voltage Ripples: The total peak-to-peak OVR is

$$\Delta v_o = \Delta v_o(t_2) - \Delta v_o(t_1).$$

(31)

Substituting the values from Equs. (23) and (29) into Equ. (31) and simplifying them gives

$$\Delta v_o = \Delta i_L \left( \frac{1}{8fC} + \frac{r_c^2 Cf}{2DD'} \right).$$

(32)

Fig. 7. Variation in voltage ripples with ESR.

Letting  $r_c = 0$  gives the OVR for the ideal capacitor as available in the literature.

We can also find the contribution of capacitor voltage ripple and ESR voltage ripple in the peak-to-peak OVR. The ripple voltage contribution by the capacitor is

$\Delta v_{\mathcal{C}} = \Delta v_{\mathcal{C}}(t_2) - \Delta v_{\mathcal{C}}(t_1).$

The ripple voltage contribution by ESR is

$$\Delta v_{rc} = \Delta v_{rc}(t_2) - \Delta v_{rc}(t_1) .$$

By substituting the values from Equs. (24) and (30), we have

$$\Delta v_{\mathcal{C}} = \Delta i_L \left( \frac{1}{8fC} - \frac{r_c^2 Cf}{2DD'} \right),\tag{33}$$

$$\Delta v_{rc} = \Delta i_L \frac{r_c^2 C f}{D D'} \,. \tag{34}$$

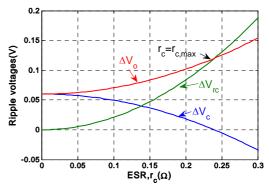

The three voltage ripple variations defined in Equs. (32)-(34) are plotted with respect to ESR, as shown in Fig. 7. From this figure, with an increase in ESR,  $\Delta v_{\rm rc}$  increases at a faster rate than  $\Delta v_{\rm c}$  decreases, thereby causing a net increase in  $\Delta v_{\rm o}$ . However, as the value of  $r_{\rm c}$  increases beyond  $r_{\rm c,max}$ .  $\Delta v_{\rm rc}$  becomes higher than  $\Delta v_{\rm o}$ , which is practically impossible. This result implies that the capacitor is no longer able to keep OVR within the specified limit for  $r_{\rm c} > r_{\rm c,max}$ . The exact relation for this  $r_{\rm c,max}$  is derived later.

2) Output Capacitor Design: Let the specified maximum OVR be  $\Delta v_{om}$ . The capacitor is designed such that the following condition must be satisfied:

$$\Delta v_o \le \Delta v_{om} \quad . \tag{35}$$

By substituting  $\Delta v_0$  from Equ. (32) and simplifying it, gives

$$r_c^2 C^2 - \frac{2DD'}{f} \left(\frac{\Delta v_{om}}{\Delta i_L}\right) C + \frac{DD'}{4f^2} \le 0.$$

(36)

Equ. (36) is a quadratic constraint in C. It is solved to generate the minimum value of the capacitor C as

$$C_{\min} = \frac{\frac{2DD'}{f} \left(\frac{\Delta v_{om}}{\Delta i_L}\right) - \sqrt{\left(\frac{2DD'}{f} \left(\frac{\Delta v_{om}}{\Delta i_L}\right)\right)^2 - 4r_c^2 \frac{DD'}{4f^2}}{2r_c^2} . (37)$$

This equation provides the value of minimum capacitance required for  $r_c \le r_{c,max}$ .

3) Derivation for Maximum Permissible ESR: The additional

term  $\frac{r_c^2 C f \Delta i_L}{2DD'}$  in Equ. (32) appears because of the presence

of ESR. As ESR increases, OVR also increases. If the ESR of capacitor is not selected properly, then it may increase the total OVR beyond the maximum permissible value. Therefore, the relationship for the maximum permissible value of ESR for the specified OVR and switching frequency should be determined. In Equ. (37),  $C_{\min}$  must be a real quantity that satisfies the following condition:

$$\left(\frac{2DD'}{f}\left(\frac{\Delta v_{om}}{\Delta i_L}\right)\right)^2 - 4r_c^2 \frac{DD'}{4f^2} \ge 0.$$

(38)

On simplifying,

$$r_c \le 2\sqrt{DD'} \frac{\Delta v_{om}}{\Delta i_L} . \tag{39}$$

Therefore, the maximum permissible value of ESR ( $r_{c,max}$ ) for specified OVR ( $\Delta v_{om}$ ) and ICR( $\Delta i_L$ ) is given by

$$r_{c,\max} = 2\sqrt{DD'} \frac{\Delta v_{om}}{\Delta i_L} . \tag{40}$$

If the ESR value is greater than the  $r_{c,max}$  in Equ. (40), then the capacitor will not be able to keep the steady-state OVR in the specified limit. This condition is verified by the experimental results in the subsequent section.

Substituting Equ. (40) into Equ. (37) obtains the minimum value of capacitor at  $r_c = r_{c,max}$  as

$$C_{\min}\big|_{r_{\mathcal{C}}=r_{\mathcal{C}},\max} = \frac{1}{4f} \frac{\Delta i_L}{\Delta v_{om}} \,. \tag{41}$$

From Equ. (32), for an ideal capacitor ( $r_c = 0$ ), the minimum value of *C* is

$$C_{\min}\big|_{r_{\mathcal{C}}=0} = \frac{1}{8f} \frac{\Delta i_L}{\Delta v_{om}} \,. \tag{42}$$

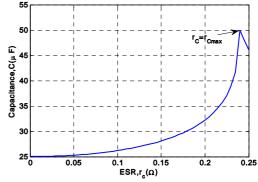

Equ. (41) provides the minimum capacitance required for the worst-case ESR ( $r_{c,max}$ ). Fig. 8 shows the variation in minimum capacitance value as a function of ESR. The capacitor value increases with an increase in ESR. At  $r_c = r_{c,max}$ , the capacitor value becomes double that of with  $r_c = 0$ . For  $r_c > r_{c,max}$ , the capacitance value is a complex value. However, as shown in Fig. 8, MATLAB simulation plots only the real part.

Substituting the values of  $\Delta i_{\rm L}$  from Equ. (17) into Equ. (40),

$$r_{c,\max} = 2\sqrt{\frac{D}{D'}} \frac{\left(\frac{\Delta v_{om}}{V_o}\right)Lf}{\left(1 + \frac{V_F}{V_o} + \frac{r_L + r_d}{R}\right)}.$$

(43)

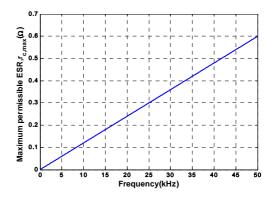

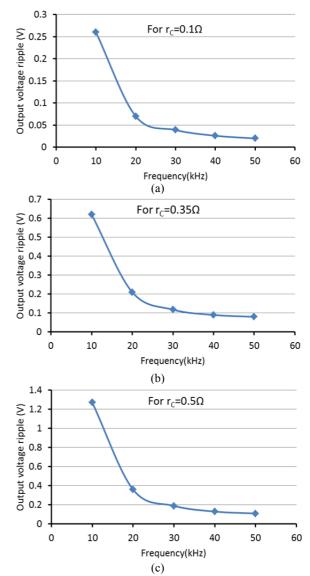

This relation depicts that for specified OVR, the maximum permissible value of ESR ( $r_{c,max}$ ) is proportional to switching frequency. Therefore, as the switching frequency of the converter increases, the power supply designer is allowed to use a high ESR capacitor without violating the OVR constraint. Fig. 9 shows the variation in  $r_{c,max}$  with frequency. If the switching frequency is 50 kHz, then the designer may use a capacitor with an ESR of 0.6  $\Omega$ . As the frequency increases, the required capacitor value decreases.

Fig. 8. Value of the minimum capacitance at different ESR.

Fig. 9. Maximum permissible ESR  $(r_{c,max})$  vs. frequency.

# **III. SIMULATION AND EXPERIMENTAL RESULTS**

For MATLAB simulation, the buck converter parameters given in Table I are used. For given specifications, according to the relation proposed in Equ. (15), the actual duty cycle is calculated as 0.6415, which is greater than the ideal duty cycle (=0.6). For this actual duty cycle, the inductance value is calculated as 490  $\mu$ H using Equ. (18). The maximum value of ESR( $r_{c,max}$ ) and the minimum capacitance ( $C_{min}$ ) are calculated as 0.2398  $\Omega$  and 50  $\mu$ F, respectively, using Equs. (40) and (41) for the OVR and ICR specified in Table I.

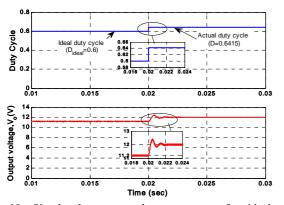

The simulated output voltage for ideal and actual duty cycles is shown in Fig. 10. The results confirm that for ideal duty cycle D = 0.6, the output voltage is 11.2 V; for actual duty cycle D = 0.6415, the output voltage is settled to 12 V (as desired).

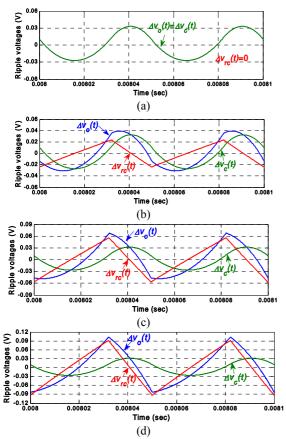

We consider four cases for four different values of ESR to investigate the effect of ESR variation on OVR. In each case, the total OVR  $\Delta v_{o}$ , the ripple caused by capacitor  $\Delta v_{c}$  and the ripple caused by ESR  $\Delta v_{rc}$  are evaluated and plotted for two switching cycles, as discussed below.

*Case 1* ( $r_c = 0$ ): This is the case for an ideal capacitor. However, such a capacitor cannot be obtained in practice. The voltage ripples are shown in Fig. 11(a). The voltage ripple  $\Delta v_o$  is the same as  $\Delta v_c$ . The peak-to-peak OVR is 0.06 V.

*Case 2* ( $r_c = 0.1 \Omega < r_{c,max}$ ): The voltage ripples are displayed in Fig. 11(b). Owing to the presence of ESR, the total peak-to-peak OVR is increased to 0.07 V. However, this value

Fig. 10. Simulated output voltage response for ideal and non-ideal duty cycles.

Fig. 11. Simulated voltage ripple waveforms for different ESR values (a)  $r_c = 0$ , (b)  $r_c = 0.1 \Omega$  ( $r_c < r_{c,max}$ ), (c)  $r_c = 0.2398 \Omega$  ( $r_c = r_{c,max}$ ), and (d)  $r_c = 0.4\Omega$  ( $r_c > r_{c,max}$ ).

Fig. 12. Experimental setup for the DC-DC buck converter.

TABLE I Buck Converter Specifications

| Parameter                                 | Value        |

|-------------------------------------------|--------------|

| input voltage, $V_{g}$                    | 20 V         |

| output voltage, $V_0$                     | 12 V         |

| frequency, f                              | 20 kHz       |

| load resistance, R                        | 10 Ω         |

| inductance, $L/r_{\rm L}$                 | 490 μΗ/0.5 Ω |

| capacitance, C                            | 50 µF        |

| diode forward voltage, $V_{\rm F}$        | 0.5 V        |

| resistance switch/diode $(r_{sw}/r_d)$ ,  | 0.05/0.03 Ω  |

| desired ICR, $\Delta i_{\rm L}/I_{\rm L}$ | 0.4          |

| desired OVR, $\Delta v_{om}/V_o$          | 0.01         |

| TABLE II           |

|--------------------|

| KEY COMPONENT LIST |

| Component Name | Specifications                            |

|----------------|-------------------------------------------|

| MOSFET switch  | IRF540N                                   |

| diode          | MUR1560                                   |

| inductor       | ferrite core (E-type) with copper winding |

| capacitor      | aluminum electrolytic                     |

is smaller than the maximum allowed OVR (0.12 V).

*Case 3* ( $r_c = r_{c,max} = 0.2398 \Omega$ ): The voltage ripples are shown in Fig. 11(c). The ESR voltage ripples increase further, such that the peak-to-peak OVR reaches 0.12 V, which is equal to the maximum allowed OVR.

*Case 4* ( $r_c = 0.4 \Omega > r_{c,max}$ ): As shown in Fig. 11(d), the voltage ripples caused by ESR highly increase. The peak-to-peak OVR is 0.19 V, which is greater than the allowed OVR limit (0.12 V). Thus, the desired performance of the buck converter is degraded.

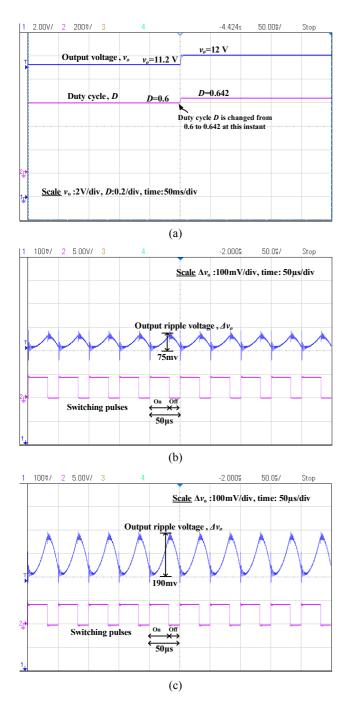

A hardware prototype of buck converter is set up to verify the theoretical studies and simulation results, as shown in Fig. 12. A ferrite core inductor of 490  $\mu$ H (with 0.5  $\Omega$  ESR) and an electrolytic capacitor of 50  $\mu$ F (with 0.1  $\Omega$  ESR) are used. The other key components are listed in Table II. The experimental results are shown in Fig. 13. Fig. 13(a) shows that the output voltage is 11.2 V with a duty cycle of 0.6. If the duty cycle is maintained at 0.642, as obtained from the proposed formula in Equ. (15), then the output voltage is 12 V. Figs. 13(b) and 13(c) show the OVR for  $r_c < r_{c,max}$  and  $r_c > r_{c,max}$ , respectively. For  $r_c = 0.1 \Omega$ , the OVR is 75 mV, which is within the maximum specified limit (120 mV). For  $r_c = 0.4 \Omega$ , the OVR is 190 mV, as shown in Fig. 13(c). This value is greater than the maximum specified limit (120 mV). Therefore, the experimental results validate the theoretical and simulation results. The dependency of OVR on switching frequency is also experimentally validated for different values of the capacitor ESR. Fig. 14(a) shows that with  $r_c = 0.1 \Omega$ , the OVR is less than 0.12 V for a frequency greater than 20 kHz. Fig.

Fig. 13. Experimental results: (a) output voltage response with ideal and proposed duty cycles, (b) OVR with  $r_c = 0.1 \Omega$ , and (c) OVR with  $r_c = 0.4 \Omega$ .

14(b) shows that with  $r_c = 0.35 \ \Omega$ , the OVR is within the specified limit for a frequency above 30 kHz. Similarly, Fig. 14(c) depicts that if the converter operates at a switching frequency greater than or equal to 50 kHz, then the OVR is within the desired limit even with a large ESR value of 0.5  $\Omega$ . Hence, if the converter operates at a higher frequency, the OVR may remain within the specified limit even with a higher ESR value. The OVR depends on ESR and converter frequency in an opposite manner.

Fig. 14 Experimental results of output voltage variation with frequency with (a)  $r_c = 0.1 \Omega$ , (b)  $r_c = 0.35 \Omega$ , and (c)  $r_c = 0.5 \Omega$ .

### **IV. CONCLUSION**

In this study, the duty cycle formula for a non-ideal DC–DC buck converter is improved considering parasitic elements. The effect of these parasitics on inductor and capacitor designs is analyzed. Analyses show a significant difference in inductor and capacitance values with the inclusion of non-ideal components. The ESR of output capacitor contributes significant ripples to output voltage. For specified OVR and switching frequency, the maximum allowable value of this ESR is derived. The simulation and experimental results indicate that an ESR beyond this maximum value results in unwanted OVR. Therefore, this analysis may be interesting and useful for a power electronic engineer to design a high-precision power supply. The proposed analysis, with suitable modifications, can be generalized to design other types of DC–DC converters.

### REFERENCES

- M. G. Villalva, T. G. de Siqueira, and E. Ruppert, "Voltage regulation of photovoltaic arrays: small-signal analysis and control design," *IET Power Electronics*, Vol. 3, No. 6, pp. 869-880, Nov. 2010.

- [2] J. C. Vilchis, C. Aguilar, and J. Arau, "Multi-mode synchronous buck converter with non-uniform current distribution for portable applications," in *IEEE Int. Power Electronics Congress*, pp. 114-120, Aug. 2008.

- [3] S. Singh, G. Bhuvaneswari, and B. Singh, "Power quality improvement in telecommunication power supply system using buck rectifier," in *IEEE India Conf.(INDICON)*, pp. 1-4, Dec. 2011.

- [4] K. Hirachi, T. Iwade, T. Mii, H. Yasutsune, and M. Nakaoka, "Improved control strategy on buck-type converter with power factor correction scheme," in *Proc. Int. Conf. Power Electronics, Drives and Energy Systems for Industrial Growth*, Vol. 2, pp. 826-832, Jan. 1996.

- [5] S. Liu, J. Liu, Y. Yang, and J. Zhong, "Design of intrinsically safe buck DC/DC converters," in proc. Int. Conf. Electrical Machines and Systems(ICEMS), Vol. 2, pp. 1327-1331, Sep. 2005.

- [6] S.-L. Liu, Y.-B. Ma, and Y.-W. Zhang, "Optimal design of inductance and capacitance of output intrinsically safe Buck DC-DC converters," in *Int. Conf. Industrial and Information Systems(IIS)*, Vol. 2, pp. 408-411, Jul. 2010.

- [7] N. Mohan, T. M. Undeland, and W. P. Robbins, *Power Electronics- Converters, Applications, and Design, 3rd ed.* John Wiley, 2003.

- [8] R. W. Erickson and D. Maksimovic, *Fundamentals of Power Electronics, 2nd ed.* Kluwer Academic Publishers, 2001.

- [9] M. H. Rashid, Power Electronics Handbook, 2nd ed. Academic Press, 2001.

- [10] E. Babaei, M. E. S. Mahmoodieh, and M. Sabahi, "Investigating buck DC-DC converter operation in different operational modes and obtaining the minimum output voltage ripple considering filter size," *Journal of Power Electronics*, Vol. 11, No. 6, pp. 793-800, Nov. 2011.

- [11] S. Liu, J. Liu, H. Mao, and Y. Zhang, "Analysis of operating modes and output voltage ripple of boost DC-DC converters and its design considerations," *IEEE Trans. Power Electron.*, Vol. 23, No. 4, pp. 1813-1821, Jul. 2008.

- [12] H. Do, "Single-switch buck converter with a ripple-free inductor current," *Journal of Power Electronics*, Vol. 11, No. 4, pp. 507-511, Jul. 2011.

- [13] R. Li, T. O'Brien, J. Lee, J. Beecroft, and K. Hwang, "Analysis of parameter effects on the small-signal dynamics of buck converters with average current mode control," *Journal of Power Electronics*, Vol. 12, No. 3, pp. 399-409, May 2012.

- [14] R. M. O'Connell, "On the output voltage ripple in the ideal boost and buck-boost DC-DC converters," *International Journal of Electronics*, Vol. 90, No. 4, pp. 243-254, Apr. 2003.

- [15] G. H. Zhou, X. Zhang, B. C. Bao, J. P. Xu, and J. Yang, "Effect of output capacitor ESR on dynamic performance of voltage-mode hysteretic controlled buck converter," *Electronics Letters*, Vol. 49, No. 20, pp. 1293-1294, Sep. 2013.

- [16] D. Czarkowski and M. K. Kazimierczuk, "Circuit models of PWM DC-DC converters," in *Proc. IEEE National*

Aerospace and Electronics Conference(NAECON), Vol. 1, pp. 407-413, May 1992.

Man Mohan Garg received his B.E. (Electrical Engineering) from the M.B.M. Engineering College Jodhpur, India, in 2008. He received his M.Tech in Electrical Drive and Power Electronics from the Indian Institute of Technology (IIT) Roorkee, India, in 2010. He has completed his Ph.D from Electrical Engineering Department of IIT

Roorkee, India. His current research interests include design, modeling and control of DC–DC power converters, photovoltaic integration, and dc microgrid.

**Mukesh Kumar Pathak** received his B.E. degree in Electrical Engineering from the LD Engineering College, Ahmedabad, India in 1986. He obtained his M.Tech and Ph.D. degrees from the IIT Delhi, India. He joined the NIT, Kurukshetra, India as a lecturer in 1987. In 1989, he joined the NIT, Hamirpur,

India, where he served until 2007 as an associate professor. He is currently working as an associate professor in the Electrical Engineering Department of IIT Roorkee, India. His research interests include control of power converters and electrical drives, and power quality improvement using FACT devices.

**Yogesh Vijay Hote** received his B.E. in Electrical Engineering from the Govt. College of Engineering, Amaravati, India, in 1998, his M.E. in Control Systems from the Govt. College of Engineering, Pune, India, in 2000, and his Ph.D. from Delhi University in 2009. He worked at the Netaji Subhas Institute of Technology New Delhi from May 2001 to

February 2011. He is currently working as an assistant professor at the Department of Electrical Engineering of IIT Roorkee, India. His field of research includes robust control, robotics, numerical analysis, and power electronic converters.