# A Study on Deterministic Utilization of Facilities for Allocation in the Semiconductor Manufacturing

Jeong Woo Kim<sup>†</sup>

System Engineering Team, SAMSUNG ELECTRONICS Co., Ltd.

# 반도체 설비의 효율성 제고를 위한 설비 할당 스케줄링 규칙에 관한 연구

김 정 우\*

삼성전자 시스템기술팀

Semiconductor manufacturing has suffered from the complex process behavior of the technology oriented control in the production line. While the technological processes are in charge of the quality and the yield of the product, the operational management is also critical for the productivity of the manufacturing line. The fabrication line in the semiconductor manufacturing is considered as the most complex part because of various kinds of the equipment, re-entrant process routing and various product devices. The efficiency and the productivity of the fabrication line may give a significant impact on the subsequent processes such as the probe line, the assembly line and final test line. In the management of the re-entrant process such as semiconductor fabrication, it is important to keep balanced fabrication line. The Performance measures in the fabrication line are throughput, cycle time, inventory, shortage, etc. In the fabrication, throughput and cycle time are the conflicting performance measures. It is very difficult to achieve two conflicting goal simultaneously in the manufacturing line. The capacity of equipment is important factor in the production planning and scheduling. The production planning consideration of capacity can make the scheduling more realistic. In this paper, an input and scheduling rule are to achieve the balanced operation in semiconductor fabrication line through equipment capacity and workload are proposed and evaluated. New backward projection and scheduling rule consideration of facility capacity are suggested. Scheduling wafers on the appropriate facilities are controlled by available capacity, which are determined by the workload in terms of the meet the production target.

Keywords: Semiconductor Fabrication, Scheduling, Equipment Capacity, Workload

## 1. 서 론

반도체 산업은 복잡한 생산 공정과 다양한 제품종류 및 제조설비 등의 요인으로 생산전반(생산량, 사이클 타

Received 27 October 2015; Finally Revised 18 March 2016;

Accepted 24 March 2016

임, 납기만족 등)을 효율적으로 관리하는 것이 다른 어떤 업종보다 어려운 산업이다[13]. 반도체 생산라인 내에서 제조 주공정인 Fabrication(이하 fab)공정은 수백 개의 장 비를 거치게 되는 200~300개의 공정들로 구성되어 있으 며, fab 공정에서 제품들이 작업되기 위해선 동일한 설비 를 공유하는 유사한 공정들이 통상 20여회 이상 반복되 어 진행된다. 각각의 반복되는 과정을 레이어라 정의하 고 하나의 레이어는 Photolithography(이하 photo)를 중심

ISSN: 2005-0461(print)

ISSN: 2287-7975(online)

<sup>†</sup> Corresponding Author: hero4u30@hotmail.com

으로 구분된다. 반도체 제품을 생산하기 위해서는 레이어라는 일정한 층을  $20\sim30$ 회 이상 반복되어 진행되는 과정으로 이루어져 있고, 각 레이어는 확산, 증착, 사진, 박막, 에칭과 같은  $20\sim40$ 여 개의 세부공정으로 구성된다. 이 과정에서 반도체 제품인 웨이퍼들은 각 레이어에서 서로 설비들을 공유하며 생산된다.

Fab 공정을 복잡하게 만들고 또한 가장 중요하게 관리되어지는 요인으로는 웨이퍼 할당이 있다. 이는 photo 설비에 적정량의 웨이퍼들을 할당하는 작업인데, 적정량의웨이퍼들을 할당함으로써 설비의 효율성을 높이고 대기시간을 감소시켜 웨이퍼의 불량률 감소와 재공재고의 관리가 가능해진다. 반도체 생산라인 내에서 가장 대표적병목공정인 photo 공정은 웨이퍼의 흐름을 관리하는 것이 매우 어려운데, 특정 설비에만 작업 과부하가 걸리는 것을 방지하고 유휴상태에 있는 장비를 최소화할 수 있도록 해야 하기 때문이다. 기존에 제안되었던 연구들은 photo 공정 내 설비의 효율성을 극대화하고 제조 사이클타임을 줄이고자 하는데 적용되었으며, 반도체 생산라인 중에서도 특히 fab 공정을 대상으로 그 중요성이 강조되었다.

제품의 특성에 따라 반도체 산업은 크게 양산형 반도체 (Make-To-Stock)와 주문형 반도체(Make-To-Order)으로 나 뉘어진다[2]. 메모리 제품은 전형적인 양산형 반도체 제 품으로 단일 fab 공정 내에서 제품의 수는 적지만 물량 이 매우 많은 특징을 갖고 있다. 그러나 주문형 반도체 제품은 주문고객에 의한 많은 제품수를 특징으로 한다. 주문형 반도체 생산라인의 경우 통상적으로 100여 개 이 상의 제품들이 동시에 진행되며, 이러한 이유로 주문형 반도체 산업은 양산형 반도체 산업에 비해 생산라인이 매우 복잡하여 병목공정인 photo 설비의 효율성과 제조 사이클 타임을 예측하고 관리하는 것이 매우 어려운 것 이 사실이다. 주문형 반도체 산업에서 주문납기만족을 위한 제품의 투입량 결정은 굉장히 중요한 의사결정 포 인트 중 하나이며, 주문납기만족을 위해 생산라인 내 많 은 수의 제품들이 동시에 같은 설비들을 공유하면서 생 기는 복잡성을 초래하게 된다.

반도체 산업의 경우 동일한 설비를 여러 번 반복하게되는 사이클링 공정(Re-entrant)을 갖고 있으므로 설비에웨이퍼들을 할당하는 문제가 매우 어려운 과제이다. 게다가 웨이퍼들의 묶음인 로트 내의 웨이퍼들은 동일한납기를 갖고 있지만 설비의 다양성과 사이클링 공정의특성으로 인해 서로 나뉘어졌다가 다시 합쳐지기를 반복하게 된다. 따라서 특정주문으로 인한 웨이퍼들은 다양한 작업으로 진행되기 위해 설비에 할당된다. 주문형 반도체 생산라인에서 납기만족을 충족하고 설비의 효율성제고를 위해 웨이퍼 혹은 로트들이 유동적이고 연속적으

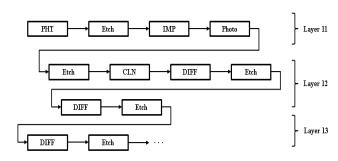

로 흘러가도록 관리가 되어져야 한다. <Figure 1>은 반도 체 공정의 간단한 흐름을 보여주고 있다.

<Figure 1> The Flow of Fabrication Process

반도체 생산 공정에서 일정계획의 평가를 위한 주요 성능지표로는 생산량, 생산투입량, 납기일, 생산주기의 평균 및 분산, 설비이용률, 평균지연시간, 평균재공 등이 있다. 그러나 반도체 fab 공정에서 이러한 성능지표들 사이에는 상치되는 효과를 주는 경우가 대부분이다. 즉 생산량을 증대하기 위하여 공정에 많은 웨이퍼들을 투입하게 되면 생산량은 증가하나 레이어 내 재공재고와 평균생산주기가 늘어나며, 불량률로 인해 수율이 저하된다. 반대로 평균생산주기를 단축시키기 위해 fab 공정에 투입량을 줄이게 되면 생산량은 줄어들게 되어 설비이용률이 감소된다.

본 논문에서는 주문형 반도체 산업의 특성을 반영한 새로운 방법론을 제안하고자 한다. 제 2장에서는 기존 연구현황에 대해 정리하였다. 제 3장에서는 제안하고자하는 역행전진 방법론 및 스케줄링 룰에 대해 서술하였으며, 제 4장에서는 제안된 방법론에 대한 실험결과에대해 평가하고 분석하였다. 마지막으로 제 5장에서는 결론 및 향후 연구방향에 대해 기술하였다.

## 2. 기존 연구현황

반도체 산업에 관한 대부분의 연구는 fab 공정에 집중되어왔다. 이는 반도체 산업이 매우 고부가가치 산업임과 동시에 자본 및 기술 집약형 산업이라는 특징에서 기인하며, 특히 fab 공정은 전체 생산라인 제조공기의 70~80를 차지한다. 반도체 fab 공정의 관리적 관점에 관한연구는 Wein[17]과 Glassey and Resende[4, 5]에 의해 본격화 되었다. Wein[17]은 반도체 생산 공정 중에서 가장복잡한 웨이퍼 가공 공정에 대한 병목공정을 관리함으로서 평균 사이클 타임을 단축하기 위한 작업부하조절(Workload regulating) 투입 규칙을 제시하였고, Glassey and Resende[4, 5]는 병목공정 설비 이용을 극대화하는

재공소진회피(Starvation avoidance) 투입 규칙을 제안하였다. Leachman et al.[10]은 사이클 타임을 감소하고 재고량을 효과적으로 줄일 수 있는 휴리스틱 및 최적화 이론을 발표하였다. 이는 반도체 fab 공정을 대상으로 적용되었으며, 그 우수성을 검증하였다. Spearman et al.[16]이제시한 CONWIP 규칙은 생산라인 전체의 재공을 동시에 제어할 수 있는 규칙으로 알려져 있다. 병목공정을 대상으로 한 기존의 연구들은 크게 최적화 모델에 의한 접근과 발견적 기법인 휴리스틱 룰에 의한 접근으로 나누어진다.

Kim et al.[8]은 재공수준의 목표를 정하고 이에 따른 목표 생산량을 설정한 후 이를 달성할 수 있는 시프트스케줄링을 혼합정수계획법으로 구할 수 있음을 보여주었으며, 이를 짧은 시간 내에 계산할 수 있는 발견적 기법 3가지를 제시하였다. 이 방법론을 통하여 최적해 대비 5% 내에 있음을 실험을 통해 증명하였다. Kang and Lee [6]는 적정재공(Proper WIP) 대비 늦게 진행되고 있는 재공들의 양을 최소화할 수 있도록 선형계획법으로 모델링하여 제안하였다. Carrasco et al.[1]는 병목설비인 photo설비를 기준으로 가동률을 최대함으로서 생산량을 높이는 스케줄링 해를 혼합정수계획법으로 제시하고 간단한모델에 대해 성능을 평가하였다.

반도체 fab 공정에서의 각종 배정규칙의 성능평가를 실시할 때 현장적용은 불가능하여 대개 전산적인 시뮬레 이션을 통해 검증하고 있는데, 실제 fab 크기에 근접한 모델을 이용하여 Lee and Kim[12]에 의해 제안되었다. 이는 전체 공정을 병목공정과 비병목공정으로 구분하고 병목공정에서는 작업 배정에 따라 웨이퍼가 이동하며 비 병목공정 그룹에서는 재공과 공기에 따라 이동하는 형태 의 모델링을 사용하였다. Lee and Kim[12]은 위에서 제 안한 재공흐름모델을 최적화모델을 통해 모델링함으로써 10시프트 이상의 스케줄링을 하나의 모델 내에서 해를 구하여 좀 더 확장된 기간의 시프트 스케줄링 해를 구하 였다. 이를 통하여 하나의 시프트에서는 관찰할 수 없었 던 제조공기 단축과 생산량 극대화라는 두 가지 성능목 표가 동시에 달성될 수 있음을 보여주었다. Lee et al.[14] 은 반도체 fab 공정을 대상으로 손쉽게 스케줄링 및 배 정규칙의 성능을 실험할 수 있는 시뮬레이터를 개발하여 보고하였으며, Kim et al.[9]은 생산공기를 결정짓는 리드 타임의 동적인 변화를 적용하여 생산라인 내 재공의 효 율적인 감소를 보여주었다. Kim[7]은 비정상 가동상태에 서 발생할 수 있는 불량률에 대한 연속적인 감시 하에서 최적의 생산량을 도출해 낼 수 있는 수리 모형을 제안하 였다.

Chang et al.[2]은 양산형 반도체 산업과 주문형 반도 체 산업의 환경을 모두 고려한 휴리스틱 모델을 제안하 였으며, 이를 통해 주문자 납기만족과 제조 사이클 타임을 줄일 수 있음을 보여주었다. Choi[3]는 반도체 생산라인 내 fab 공정을 대상으로 웨이퍼 로트들의 다양한 도착시간을 고려하여 photo 공정의 총 가중작업흐름시간을최소화하기 위한 스케줄링 알고리듬을 제안하고 그 우수성을 검증하였다. Sigrid et al.[15]은 주문형 반도체 산업에서 가장 큰 목표가 될 수 있는 주문자 납기만족을 위해 지연일수를 최소화 할 수 있는 휴리스틱을 제시하였다. 이 휴리스틱은 혼합정수계획법을 이용하여 모델링하였으며, 최적화 모델과의 시험결과 비교를 통해 그 결과를 검증하였다. 이를 통해 휴리스틱의 전략적 측면에서의 성능을 증명해 보였다. Lee and Kim[11]은 반도체 생산라인을 대상으로 각 레이어의 재공들의 긴급도를 평가하여 세 가지 형태의 재공으로 분류하여 스케줄링함으로서 생산량 최대화 및 셋업을 최소화하는 연구를 진행하였다

최적화 모델은 반도체 산업에서 활발하게 연구되었으며 많은 양의 연구 결과가 보고되었다. 그러나 다양한 제약조건을 반영할 수 없다는 단점과, 생산라인의 복잡성으로 인해 실제 반도체 생산현장에 폭넓게 적용되는 데는 한계성을 내포하고 있었다. 본 연구에서 제안하고자하는 휴리스틱 룰은 현장에서 요구되는 제약조건들의 추가반영이 가능하며, 또한 방대한 양의 데이터들을 처리하면서도 최적화 모델에 비해 매우 짧은 연산속도를 갖는다는 장점이 있다.

## 3. 설비 할당을 위한 모형 개발

반도체 생산라인 내 설비들은 생산량을 결정짓는 매우 중요한 관리요소 중 하나이다. 특히 생산계획에 있어설비를 고려한 투입량 결정 및 스케줄링은 최적화 모델접근 방법론에서 단점으로 도출되었던 현장 적용의 어려움에 대한 대안을 제시한다. 생산라인의 기준정보성 데이터들인 설비현황, 가용량 및 사이클 타임을 고려한 생산량 최대화 달성과 주문납기만족을 위한 투입량 결정문제는 효율적 생산계획을 위해 매우 중요하다.

본 논문에서는 설비 가용량과 레이어별 사이클 타임이 고려된 두 단계의 투입량 결정 및 스케줄링 방법론 (Allocation scheduling)을 제안한다. 첫째, 레이어별 설비가용량과 사이클 타임을 고려한 역행전진(Backward projection) 산출 방법이다. 가장 마지막 레이어로부터 수요를 고려하여 첫 레이어까지 수요량 대비 생산량이 최대화 되도록 웨이퍼의 투입량을 결정한다. 둘째, 각 레이어마다 설비의 작업 부하량을 고려하여 각 생산설비에 투입될 웨이퍼들의 스케줄링을 진행한다.

<Table 1> Calculation of Proper Wip based on Due Date

| Layer | Cycle time | Proper wip                                                |

|-------|------------|-----------------------------------------------------------|

| :     | :          | :                                                         |

| :     | :          | :                                                         |

| 28    | 1.0        | 150 wafers                                                |

| 29    | 2.5        | $200 \times (0.5/1 \text{day}) + 250 = 350 \text{wafers}$ |

| 30    | 1.5        | $100+200\times(0.5/1\text{day}) = 200 \text{ wafers}$     |

| Day        | Day 1 | Day 2 | Day 3 | Day 4 | Day 5 |

|------------|-------|-------|-------|-------|-------|

| Target WIP | 100   | 200   | 50    | 200   | 150   |

<Table 1>은 적정재공을 산출하는 과정을 예로 표현한 것이다. 적정재공 산출과정은 마지막 레이어로부터역순으로 계산되어진다. 예를 들어 마지막 레이어의 적정재공 산출은 1일 목표생산량이 100이고 마지막 레이어의 사이클 타임이 1.5일이므로 1일에 해당하는 100장에 나머지 0.5일은 2일 목표생산량 200장의 0.5일분이해당된다. 그러므로 마지막 레이어의 적정재공은 1일분의 100장과 2일 목표생산량 중 0.5일에 해당하는 100장이 더해져 200장이 된다. 그리고 이렇게 산출된 적정재공을 이용하여 밸런스 평가지수를 산출하게 된다.

설비현황을 고려하여 생산 목표량을 달성하기 위해서 는 수요에 따른 투입량 결정이 매우 중요한데, 본 논문에 서는 각 공정별 적정수준의 재공을 유지하고 이를 통해 재공의 효율적 설비 할당이 가능하도록 하는 기존에 연 구되었던 밸런스 평가지수(Balance Index)와 비교하여 그 결과를 검증하였다. 라인 내 재공은 동적이기 때문에 움 직임이 시시각각 변하지만 한 레이어 내에 있는 전체 재 공이 기준값과 동일한 값을 가지고 있을 때 해당 레이어 는 밸런스 상태에 있다고 말할 수 있다. 레이어의 기준값 은 생산량 대비 사이클 타임을 고려한 적정수준의 재공 량이 되는데, 설비에 우선적으로 할당해야 할 각 레이어 의 긴급도를 산출하기위한 방법으로 적정재공 대비 현재 공(Current WIP)의 비율을 계산한다. 이를 통해 산출된 밸런스 지수에 따라 재공을 설비에 할당함으로써 레이어 별 정체되어 있는 재공들에 대한 관리가 가능하며, 동시 에 생산량 극대화 및 설비의 효율성을 높일 수 있다. 레 이어별 밸런스 평가지수는 기준값 대비 현재의 재공을 비교한 값으로 다음과 같이 정의할 수 있다[14].

밸런스평가지수 =

$$\frac{현재공 - 적정재공}{적정재공}$$

(1)

<Table 2>는 밸런스 평가지수를 산출하는 과정을 보여준다. 밸런스 평가지수는 각 레이어의 균형지수이며 적정 재공 대비 초과 재공분의 비율을 의미한다. 즉, 레이어의 균형은 현재 공에서 적정재공을 뺀 양을 적정재공으로 나

누어 준 값으로 정의할 수 있으며 산출된 균형지수는 -1 부터 무한대(+)까지의 값을 가질 수 있다. 레이어 29의 경 우 해당 레이어에 적정 수준으로 존재해야 할 재공의 양 보다 현재공이 더 여유가 있는 케이스이다. 레이어 30의 경우 적정수준의 재공량은 1,418개이지만 현재공은 498 개로 920개의 재공이 부족함을 의미한다. 이와 같은 지수 산출을 통해 수요만족 측면에서 설비에 우선적으로 할당 할 레이어의 재공을 판별하여 스케줄링 하고자 한다.

⟨Table 2⟩ Calculation of Balance Index

| Layer | Proper WIP | Current WIP | Balance Index           |

|-------|------------|-------------|-------------------------|

| 1     | 321        | 24          | (24-321)/321 = -0.92    |

| 2     | 48         | 249         | (249-48)/48 = 4.18      |

| ÷     | :          | :           | :                       |

| 28    | 81         | 167         | (167-81)/81 = 1.60      |

| 29    | 210        | 260         | (260-210)/210 = 0.23    |

| 30    | 1,418      | 498         | (498-1418)/1418 = -0.64 |

### 3.1 역행전진 모델 개발

반도체 생산라인에서 photo 공정은 대표적인 병목공정으로 해당 설비의 가용량에 따라 각 레이어별 생산량이 결정된다. 특히나 여러 종류의 웨이퍼 제품들이 라인에서 복합적(Product-mix)으로 흘러가고 여러 설비를 공유하기 때문에 투입량 결정 및 웨이퍼의 설비 할당문제가 매우 복잡하고 어렵다. 하지만 본 논문에서는 설비군내에 있는 설비들은 모두 동종의 설비로 가정을 한다[8].

| Period<br>(Daily) |        |     |                              | Layer 18<br>(1,000min) | Layer 19<br>(1,000min)             |                                    | Production |

|-------------------|--------|-----|------------------------------|------------------------|------------------------------------|------------------------------------|------------|

|                   | Device | CT: | a: 0.7     b: 1.2     c: 0.9 | ← b:1.2<br>c:0.8 →     | a: 1.2     b: 1.7     c: 1.9     → | a: 0.7     b: 1.2     c: 1.4     → | Target     |

| 1                 | a      |     |                              |                        |                                    |                                    |            |

|                   | b      |     |                              |                        |                                    |                                    |            |

|                   | С      |     |                              |                        |                                    |                                    |            |

|                   | a      |     |                              |                        |                                    |                                    |            |

| :                 | b      |     |                              |                        |                                    |                                    |            |

|                   | С      |     |                              |                        |                                    |                                    |            |

|                   | a      |     |                              |                        |                                    |                                    |            |

| 25                | Ь      |     | 800                          |                        |                                    |                                    |            |

|                   | С      |     | 200 ▶                        |                        |                                    |                                    |            |

|                   | a      |     | 100 🛌                        |                        |                                    |                                    |            |

| 26                | b      |     |                              | 800                    |                                    |                                    |            |

|                   | С      |     | 400 №                        | 200 ←                  | — 200 <sub>k</sub>                 |                                    |            |

|                   | a      |     | 1,000                        | 100                    |                                    |                                    |            |

| 27                | b      |     |                              |                        | \                                  |                                    |            |

|                   | С      |     |                              | 400 ∢                  | — 400 <sub>k</sub>                 | \                                  |            |

|                   | a      |     |                              | 1,000                  |                                    | \                                  |            |

| 28                | Ь      |     |                              |                        | 800                                | \                                  |            |

|                   | С      |     |                              |                        |                                    | 200 .                              |            |

|                   | a      |     |                              |                        | 1,000                              |                                    |            |

| 29                | b      |     |                              |                        |                                    | 800                                |            |

|                   | С      |     |                              |                        |                                    | 400 🛌                              |            |

|                   | a      |     |                              |                        |                                    | 1,100                              | 1,100      |

| 30                | b      |     |                              |                        |                                    |                                    | 800        |

|                   | С      |     |                              |                        |                                    |                                    | 600        |

<Figure 2> Backward Projection for Allocation on Facilities

<Figure 2>는 설비의 가용량 및 사이클 타임을 고려한 마지막 레이어로부터 첫 레이어까지 역행전진으로 각 레 이어의 초기 투입량이 어떻게 계산되어 지는지 보여주고 있다.

가장 마지막 레이어를 지나 최종 생산되어지는 물량이 곧 fab 공정에서 생산되는 생산목표량이 된다. 본 논문에서는 레이어의 수는 20개, 전체 생산수립을 위한일자는 30일 기준으로 정의하였다. 즉, 20번째 레이어가가장 마지막 레이어가 되고 20번째 레이어를 지나 생산된 웨이퍼의 양이 최종 생산 목표량이 되는 것이다. 또한 제품 혼합을 정의하기 위해 각 레이어마다 3개의 제품이 동시에 지나도록 예제를 통해 표현하고 있다. 설비군에 따라 동종의 설비를 가정하였으나, 제품마다 설비에서 생산되어지는 사이클 타임과 설비 가용량은 서로 상이하다. 설비 가용량은 특정 설비에서 생산되어레이어를 지나는 사이클 타임을 고려하여 시간(24시간기준으로 사용 가능한 설비 가용량은 1,440분)으로 표현하였으며, 웨이퍼 장당 1분의 생산시간을 갖는다고 가정하다.

<Figure 2>에서는 생산 목표량으로 a제품 1,100장, b제품 800장 그리고 c제품 600장으로 정의하였으며, a제품 1,100장의 웨이퍼는 20개의 레이어를 지나 30일이 지나모두 생산되어야만 생산 목표량을 맞출 수 있다. 20번째 레이어에서 a제품의 사이클 타임은 0.7일이다. 이는 a제품은 0.7일 만에 20번째 레이어의 설비를 지나 생산이가능함을 의미한다.

같은 예로 b제품은 20번째 레이어를 지나기 위해서는 1.7일이 소요된다. 그리고 20번째 레이어의 위에서 언급 한 바와 같이 동종의 설비이기 때문에 a, b 그리고 c제품 모두를 생산할 수 있으며, 설비 가용량은 1,200분이다. 설 비 가용량을 1,400분이 아니라 1,200분 혹은 1,000분으로 예제를 들어 설명한 이유는 이미 투입되어 있는 웨이퍼 가 있을 수 있으며, 설비의 효율성 등을 고려하여 1,440 분으로 설비가 24시간 가동이 되지 않을 수도 있음을 보 여주기 위함이다. 20번째 레이어를 기준으로 봤을 때, a 제품 1,100장의 웨이퍼는 사이클 타임이 0.7일 이므로 30 일날 투입되어도 정상적으로 30일 이후에 생산 목표량 1.100장을 충족할 수 있으며, 가용량 1.200분 범위 안에 있기 때문에 충분히 생산이 가능하다. 그러나 b제품과 c 제품의 경우에는 각각 1.2일과 1.4일의 사이클 타임을 갖 고 있으므로 30일에 투입되어서는 정상적으로 생산되어 생산목표량을 맞추기 힘들다. 그러므로 29일에 b와 c제 품이 투입되어져야 한다. 그러나 20번째 레이어에서 29 일에 해당하는 설비 가용량의 경우 1,200분 밖에 되지 않 으므로 b제품 800장과 c제품 400장만 투입량(800장+400 장 = 1,200장)으로 결정해 준다. 그리고 c제품 600장중 200장은 28일날 분할 투입을 해준다. b제품 대신 c제품을 분할할여 투입하는 이유는 분할되어질 제품의 목록들 중에서 생산목표량이 가장 큰 제품부터 최대한 할당하여 주고 생산목표량이 적은 순으로 제품을 분할하여 투입함을 원칙으로 하기 때문이다. 즉, 예제의 결과로 20번째 레이어에 투입되어질 웨이퍼양은 30일날 a제품으로 모두를 투입하고 29일날 b제품 800장, c제품 400장을 투입, c제품은 28일에 분할되어진 200장을 투입량으로 결정하여주면 설비의 가용량 및 사이클 타임을 고려하여 생산목표량을 맞출 수가 있다.

## 설비할당을 위한 알고리즘 :

#### First

# Step 1 : 병목목정 내 투입량 결정을 위한 초기단계 Step 1.1

i = 제품, j = 레이어, k = 설비, t = 생산일자(day)

#### Step 1.2

제품의 투입량 i = PT(i), 생산일자 t, 레이어 j, 제품 i의 투입량 = LIT(i, j, t), 레이어 j, 제품 i의 사이클 타임 = LT(i, j), 제품 i의 합 = SLT(i)

#### Step 2 : 사이클 타임, 생산 목표량 정보

Step 2.1 : 최종 생산 목표량 로딩

Step 2.2 : 각 레이어의 사이클 타임 로딩

#### Step 3 : 투입량 결정

Step 3.1 : 제품 초기화, SLT(i, j) = 0

Step 3.2 : 마지막 레이어로부터 역행전진(Backward Projection)을 통해 투입량 결정

Step 3.2.1 : 마지막 레이어부터 투입량 결정  $(SLT(i, j)/Day(t))^{th}$ day, SLT(i, j) = SLT(i, j)+LT(i, j) Day(t) = SLT(i, j)/Day(t), LIT(i, j, t) = PT(i) 만약 레이어가 남아있으면, Go to Step 3.2

Step 3.2.2 : 각 생산일자 및 레이어에 따른 역행 전진

Step 3.2.3 : 첫 번째 레이어의 초기 투입량 결정

Step 4 : 만약 제품이 남아 있다면 Go to Step 3.1, 그렇지 않으면, Step 5

Step 5 : 설비 작업부하를 고려한 할당 우선순위 결정

#### Second

Step 1 : 사이클 타임, 설비 가용량을 고려한 웨이퍼 할 당 결정

**Step 1.1** : 제품 초기화 SLT(i, j) = 0

Step 1.2 : 마지막 레이어로부터 역행전진(Backward Projection)을 통해 투입량 결정

Step 1.2.1 : 마지막 레이어부터 SLT(i, j)를 이용하여 생산일자 Day(t)에 분할된 웨이퍼들의 높은 우선순위에 따라 제품할당, 설비 가용량을 고려하여 LIT(i, j, s) 계산

$(SLT(i, j)/Day(t))^{th}$ day, SLT(i, j) = SLT(i, j)+LT(i, j)Day(t) = SLT(i, j)/Day(t), LIT(i, j, s) = PT(i) $W/T(j, k) = W/T(j, k)-LIT(i, j, t)\times ProcT(i, j)$ 만약 레이어가 남아 있다면, Go to **Step 3.2**

Step 1.2.2 : 분할된 웨이퍼들 각 레이어마다 투 입량 결정

Step 1.2.3 : 각 제품별 초기 투입량 결정

Step 2 : 만약 제품이 남아 있다면 Go to Step 3.1, 그렇지 않으면 Stop

# 3.2 작업 부하량을 고려한 스케줄링 룰

반도체 생산라인 내에서 웨이퍼들은 설비의 작업부하 를 고려하여 스케줄링 된다. 이는 작업부하에 따라 반도 체 설비들의 우선순위가 결정된 후 스케줄링 되어져야 할 웨이퍼들이 할당되어 생산됨을 의미한다. photo 공정 에서는 셋업타임의 관리도 매우 중요하다 할 수 있는데, 일반적으로 photo 공정에서 동일한 제품을 생산할 경우 셋업시간이 필요하지 않다. 하지만 투입될 웨이퍼의 종 류가 변경될 경우 설비에서는 이를 위한 셋업타임이 발 생함으로 인해 생산량 및 수율이 떨어지는 위험이 발생 하기도 한다. 반도체 생산라인에서는 불필요한 셋업을 줄이기 위해 가급적이면 설비에 셋업타임이 발생하지 않 도록 동일한 반도체 제품을 투입시키기 위해 스케줄링 한다. 이에 본 논문에서는 역행전진으로 산출된 초기 투 입량을 셋업 최소화 알고리즘을 이용하여 각 설비에 할 당한다. 우선 특정 레이어에서 사용 가능한 설비들을 검 색한 후 가장 작업 부하량이 작은 설비를 선택한다. 그리 고 이전에 생산되고 있던 제품과 가급적이면 동일한 제 품을 스케줄링한다. 이는 셋업을 최소로 유지하고 설비 의 작업 부하량을 고려하여 최대한 많은 제품을 할당할 수 있도록 알고리즘을 개발하였기 때문이다.

## 작업 부하량을 고려한 스케줄링 알고리즘

Step 1 : 초기단계

Step 1.1 : 데이터 로딩 :

제품, 레이어, 설비, 프로세싱 타임, 작업 가능 설비

#### Step 1.2

i = MHR, j = 레이어, k = 설비, t = 생산일자(day) t기간 동안 설비의 작업 부하량 = WL(k, t), t기간 동안 j 레이어의 제품 i의 투입량 = LIT(i, j, t), 레이어 j의 설비 k에서 생산될 제품 i의 양 = C(i, j, k), t기간 동안 설비 k의 작업 가능 시간 = AV(k, t), 설비 k의 작업 가능 시간 = W/T(k)

Step 1.3 : 역행 전진에 의해 산출된 투입량 데이터 로딩

Step 1.4 : 각 설비의 작업 부하량 계산  $WL(k, t) = LIT(i, j, t)/(C(i, j, k) \times AV(k, t))$

## Step 2 : 작업 부하량 우선순위에 따라 설비 k에 투 입량 할당

Step 2.1 : Muststepper : 동일한 제품이 할당됨에

따라 셋업 타임이 필요하지 않은 설비

Step 2.2 : Possiblestepper : 제품 변동으로 인해 셋 업이 필요한 설비

Step 3 : 만약 스케줄링 되지 않은 *WIP*이 있다면 step 2, 그렇지 않다면 step 4

$(WIP(i, j) \times cycle time(i, j))$

Step 4 : 스케줄링 알고리즘 종료

}

## 4. 실험환경 및 결과

본 논문에서 제안하고자 하는 설비 할당 스케줄링 룰을 평가하기 위하여 실제 반도체 생산 라인을 단순화 하

여 모델링 하였다. 실험 환경은 30개의 레이어에 60대의 설비가 있다고 가정하였으며, 20개의 제품이 흘러간다고 정의하였다.

생산일자 t기간은 총 30일, 하루 동안 설비의 작업 가능시간은 1,440분으로 정의하였으며, 하나의 웨이퍼가생산되어지는 시간은 균등분포(Uniformly distribution)에따라 [1.0, 2.6]분 사이에서 발생하도록 하였다. 각 레이어의 사이클 타임은 [1.25, 1.75]일 사이에서 발생되도록했으며, 모든 레이어를 통과하는데 걸리는 시간은 [30, 45]일 사이에서 가능하도록 했다. 설비에서 생산되는 제품과 다른 제품이 투입될 때 발생하는 셋업타임은 30분으로 정의하였다.

실험은 6개의 케이스를 대상으로 수행되었으며, 케이스 1번부터 3번까지는 평균수요량을 고정시켰고, 나머지경우에는 평균수요량의 2배에 난수를 곱하여 매일의 목표 생산량을 결정하였다. 그리고 케이스 1, 4번의 평균 수요량은 (125, 125, …, 125), 케이스 2, 5번의 평균 수요량은 (200, 200, 200, …, 50, 50, …, 50), 케이스 3, 6번은 (10, 20, 30, …, 200)으로 생성하였다. 적정재공을 산출하는 경우는 향후 일주일간의 목표 생산량의 평균에 사이클 타임을 곱하여 결정했으며, 초기 재공은 향후 일주일간의목표 생산량의 평균에 사이클 타임을 곱하여 결정하였다.

<Table 3>에 사용된 각각의 평가지수들은 Kang and Lee[6]에 의해 제안되었다. 웨이퍼의 생산량은 가장 마지막 레이어에서 생산된 양을 기준으로 하였고 이는 최종생산량과 동일하다. 사이클 타임은 리틀의 법칙을 이용하여 계산하였으며, 재고는 수요량 대비 남아있는 양을 의미한다. 부족분은 수요량에서 재고와 생산된 양을 빼준 부족분이다. 실험 결과는 각 레이어의 재공 상태에 따른설비할당을 위한 밸런스 평가지수와 본 논문에서 제안하고자 하는 스케줄링 방법론을 통해 도출된 생산량을 비교분석하였다. 본 실험은 C++을 기반으로 실제 생산라인과유사하게 모델링하였으며, 설비할당 및 작업 부하량 스케줄링을 프로그래밍 하였다. 인텔 코어 2.4GH 그리고 4G RAM 환경에서 실험이 진행되었으며, 각 케이스별로 1분 내외에서 모두 실험결과가 도출되었다.

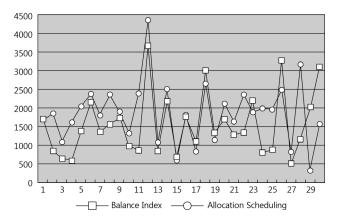

<Table 3>의 각 평가지수 결과에 따르면 설비 할당 스케줄링 룰이 밸런스 평가지수에 비해 더 나은 성능이 나타남을 알 수 있다. 생산량의 경우 작업 부하량을 고려한설비 할당 스케줄링 룰이 밸런스 평가지수보다 약 2%가량 더 생산되었으며, 사이클 타임은 약 9% 개선된 결과를 보여주었다.

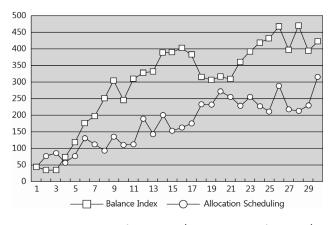

생산품질 및 생산비용 감소의 척도가 될 수 있는 재고 량의 경우에는 밸런스 평가지수 대비 설비할당 스케줄링 룰을 적용하였을 때 약 47%의 감소 효과가 있음을 실험 결과를 통해 도출해 내었다.

<Figure 3> Trend of throughput(the instance of Type 2)

<Figure 4> Trend of Inventory(the instance of Type 2)

<Table 3> The Performances for Scheduling Rules

| Performance |                       | Case 1 | Case 2 | Case 3 | Case 4 | Case 5 | Case 6 | Average |

|-------------|-----------------------|--------|--------|--------|--------|--------|--------|---------|

| Throughput  | Balance Index         | 54,989 | 51,846 | 55,816 | 50,833 | 58,293 | 50,771 | 53,758  |

|             | Allocation Scheduling | 55,772 | 56,534 | 56,768 | 53,128 | 52,742 | 51,142 | 54,348  |

| Cycle time  | Balance Index         | 48.10  | 44.43  | 47.23  | 48.07  | 42.89  | 49.37  | 46.68   |

|             | Allocation Scheduling | 39.09  | 43.81  | 42.61  | 44.86  | 39.77  | 47.33  | 42.91   |

| Shortage    | Balance Index         | 643    | 439    | 338    | 289    | 472    | 297    | 413     |

|             | Allocation Scheduling | 152    | 76     | 200    | 144    | 134    | 208    | 152     |

| Inventory   | Balance Index         | 4,071  | 5,754  | 4,631  | 3,339  | 3,597  | 4,281  | 4,279   |

|             | Allocation Scheduling | 2,054  | 4,048  | 2,113  | 1,786  | 2,195  | 1,332  | 2,255   |

<Figure 3>과 <Figure 4>는 30일 동안의 생산량과 재고량의 추이를 보여주고 있다. 생산량은 설비 할당 스케줄링 룰이 밸런스 평가지수 보다 더 좋은 결과를 나타내고 있으며, 재고량 또한 더 적은 양의 재고량을 보여줌으로써 본 논문에서 제안된 설비 할당 스케줄링 룰이 생산라인 내 설비의 효율성이 더 좋음을 나타내고 있다.

# 5. 결 론

본 논문에서는 설비의 가용량을 고려하여 수요량을 최대한 만족시키도록 역행전진을 통해 웨이퍼들의 투입량을 결정하고 각 레이어마다 셋업을 최소화함과 동시에 생산량을 최대화하기 위한 설비 할당 스케줄링 방법론을 제안하였다. 또한 각 레이어의 재공현황을 가장 적절하게제어하는 밸런스 평가지수와 그 결과 값을 비교하여 실제생산라인에 적용 가능성을 검증하였다. 이는 반도체 생산라인에서 적용해야 할 다양한 제약조건을 반영함으로써빠른 시간 안에 생산계획을 세울 수 있음을 의미한다.

반도체 생산라인에 적용된 연구들은 생산계획의 특성 상 최적화 모델링을 통한 방법론이 주로 진행되어 왔다. 하지만 이전의 생산라인의 특성과는 달리 현재의 반도체 생산라인은 빠른 시간 내에 결과를 산출하고 현장에서 발생하는 다양한 이슈 사항들에 대한 대응이 매우 중요 하다

본 논문에서는 역행전진에 의한 투입량을 결정하고 작업 부하량을 고려한 스케줄링 방법론을 제안하였으나 실제 생산라인에서 발생하는 다양한 제약조건을 모두 반영하지는 못하였다 또한 실험에 사용된 데이터들과 실험환경도 최대한 반도체 생산라인을 묘사하여 모델링하였지만 여전히 한계가 존재한다. 추후 연구 방향으로서 실제반도체 데이터에 가까운 데이터 구성, 다양한 제약조건의 반영 그리고 단순화된 라인 모델링을 실제 라인에 가깝도록 생산 프로세스를 정의함으로써 정확성과 생산라인의 적용 가능성에 대해 검증을 해야 할 것이다.

### References

- [1] Carrasco, J., Alptekin, S.E. and Krumme, L., Mixed Integer Programming Applied to Atepper Scheduling, Proceedings of the International Conference on Semiconductor Manufacturing Operational Modeling and Simulation, 1999, pp. 62-66.

- [2] Chang, S., Pai, P., Yuan, K., Wang, B., and Li, R., Heuristic PAC Model from Hybrid MTO and MTS Production Environment, *International Journal of Pro-*

- duction Economics, 2003, Vol. 85, pp. 347-358.

- [3] Choi, S.W., Scheduling Algorithms for Minimizing Total Weighted Flowtime in Photolithography Workstation of FAB, *Journal of the Society of Korea Industrial and Systems Engineering*, 2012, Vol. 35, No. 1, pp. 79-86.

- [4] Glassey, C.R. and Resende, M.G.C., A Scheduling Rule for Job Release in Demiconductor Fabrication, *Operations Research Letters*, 1998b, Vol. 7, pp. 213-217.

- [5] Glassey, C.R. and Resende, M.G.C., Closed-loop Job Release Control for VLSI Circuit Manufacturing, *IEEE Transactions on Semiconductor Manufacturing*, 1998a, Vol. 1, No. 1, pp. 36-46.

- [6] Kang, K.H. and Lee, Y.H., Make-to-order Scheduling in Foundry Semiconductor Fabrication, *International Journal of Production Research*, 2007, Vol. 45, No. 3, pp. 615-630.

- [7] Kim, C.H., Determination of optimal production lot size when a production system is under constant surveillance, *Journal of the Korean Institute of Plant Engineering*, 2013, Vol. 18, No. 1, pp. 19-26.

- [8] Kim, S., Yea, S.H., and Kim, B., Shift Scheduling for Stepper in the Semiconductor Wafer Fabrication Process, *IIE Transactions*, 2002, Vol. 34, pp. 167-177.

- [9] Kim, S.H., Kim, J.W., and Lee, Y.H., Simulation-Based Optimal Production Planning Model Using Dynamic Lead Time Estimation, *International Journal of Advanced Manufacturing Technology*, 2014, Vol. 75, pp. 1381-1391.

- [10] Leachman R.C., Kang, J.Y., and Lin, V., SLIM: Short Cycle Time and Low Inventory in Manufacturing at Samsung Electronics, *Interfaces*, 2002, Vol. 32, pp. 61-77.

- [11] Lee, Y.H. and Kim, J.W., Daily Stepper Scheduling Rule in the Semiconductor Manufacturing for MTO Products, *International Journal of Advanced Manufacturing Technology*, 2011, Vol. 54, No. 1-4, pp. 323-336.

- [12] Lee, Y.H. and Kim, T., Manufacturing Cycle Time Reduction Using Balance Control in the Semiconductor Fabrication Line, *Production Planning and Control*, 2001, Vol. 13, pp. 529-540.

- [13] Lee, Y.H., Cho, H.M., Park, J.K., and Lee, B.K., Scheduling Simulator for Semiconductor Fabrication Line, *IE Interfaces*, 1999, Vol. 12, No. 3, pp. 437-447.

- [14] Lee, Y.H., Park, J., and Kim, S., Experimental Study on Input and Bttleneck Scheduling for the Semicon-

- ductor Fabrication line, *IIE Transactions*, 2001, Vol. 34, Issue. 2, pp. 179-190.

- [15] Sigrid L.N. and Kai, A.O., Optimal and Heuristic Solutions for a Scheduling Problem Arising in an Foundry, *Computer and Operations Research*, 2005, Vol. 32, pp. 2351-2382.

- [16] Spearman, M.L., Woodruff, D.L., and Hopp, W.J., CON-WIP: A Pull Alternative to Kanban, *International Jour-*

- nal of Prouction Research, 1990, Vol. 28, No. 5, pp. 879-894.

- [17] Wein, L.M., Sheeduing Semiconductor Wafer Fabrication, IEEE Transactions on Semiconductor Manufacturing, 1998, Vol. 1, No. 3, pp. 115-129.

#### **ORCID**

Jeong Woo Kim | http://orcid.org/0000-0003-4538-7029