JPE 16-1-35

http://dx.doi.org/10.6113/JPE.2016.16.1.340 ISSN(Print): 1598-2092 / ISSN(Online): 2093-4718

# A Cascaded Hybrid Multilevel Inverter Incorporating a Reconfiguration Technique for Low Voltage DC Distribution Applications

Surin Khomfoi<sup>†</sup>

<sup>†</sup>Dept. of Electrical Eng., Faculty of Engineering, King Mongkut's Institute of Technology Ladkrabang, Bangkok,

Thailand

#### **Abstract**

A cascaded hybrid multilevel inverter including a reconfiguration technique for low voltage dc distribution applications is proposed in this paper. A PWM generation fault detection and reconfiguration paradigm after an inverter cell fault are developed by using only a single-chip controller. The proposed PWM technique is also modified to reduce switching losses. In addition, the proposed topology can reduce the number of required power switches compared to the conventional cascaded multilevel inverter. The proposed technique is validated by using a 3-kVA prototype. The switching losses of the proposed multilevel inverter are also investigated. The experimental results show that the proposed hybrid inverter can improve system efficiency, reliability and cost effectiveness. The efficiency of proposed system is 97.45% under the tested conditions. The proposed hybrid inverter topology is a promising method for low voltage dc distribution and can be applied for the multiple loads which are required in a data center or telecommunication building.

**Key words:** Cascaded hybrid inverter, Cascaded multilevel inverter, DC microgrid, Low Voltage DC Distribution, PWM paradigm, Reconfiguration technique

# I. Introduction

Data center or telecommunication buildings in Thailand normally consist of large nonlinear electronic loads such as switching router units, personal computers (PC), monitors, lighting, and the adjustable speed drives (ASD) used in air conditioning systems. In Thailand, more than two thousand telecommunication buildings are providing services for both data centers and telecommunication switching units. Moreover, several remote data centers for cell phones and internet services are also operating to meet the needs of customers. Therefore, a fine electrical system for telecommunication buildings is required. Generally, the electrical system used in telecommunications equipment is a low voltage dc system with a dc voltage equal to -48 V. A single phase 220 V, 50 Hz electrical system is used for PCs,

monitors, and lighting; whereas, a three phase 220/380 V, 50Hz system is utilized for air conditioning systems. It is promising that a dc distribution consisting of a photovoltaic panel as a renewable energy source (RES) and a battery as an energy storage (ES) unit can be integrated into the same grid to supply required power. A diesel generator can also be used as a standby source. As a result, a microgrid for a telecommunication building or a data center would be possible.

A microgrid concept is introduced in [1] to provide increased system capacity and control flexibility when several RESs with different electric behaviors are integrated into the same grid. A microgrid also offers extra degrees of freedom to optimize the RESs connected to the utility grid. Additionally, power quality requirements, system reliability and control flexibility can be achieved by using the microgrid concept discussed in [2]. A review of feasible configurations and applications of ac and dc microgrids with distributed energy resources has been described in [3]. The study suggests that it is possible to use the dc microgrid concept as a low voltage dc distribution for the data center applications. A dc microgrid with a superb quality distribution system for

Manuscript received Jan. 24, 2015; accepted Aug. 7, 2015 Recommended for publication by Associate Editor Trillion Q. Zheng.

<sup>&</sup>lt;sup>†</sup>Corresponding Author: kkhsurin@kmitl.ac.th

Tel:+66-2-3298331,King Mongkut's Inst. of Tech. Ladkrabang

<sup>\*</sup>Dept. of Electrical Eng., Faculty of Engineering, King Mongkut's Institute of Technology Ladkrabang, Thailand

residential application has been proposed in [4], and a low voltage distribution system for commercial power systems with sensitive electronic loads has been investigated in [5]. For dc distribution in a data center building, a high power converter (about 100 kW) which can supply both a single phase and a three phase load with a high quality output voltage waveform and high efficiency is required.

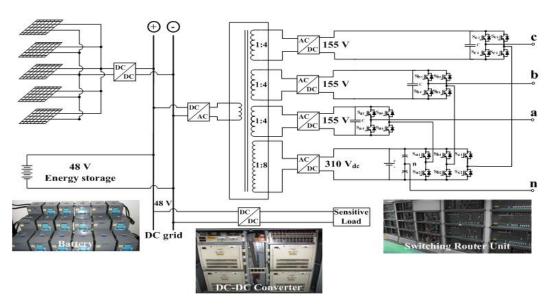

Therefore, multilevel inverter structures are suitable for this application because multilevel inverters can provide high volt-ampere ratings. In multiple energy source applications, a cascaded H-bridge multilevel inverter can be applied to interface a group of batteries, photovoltaic or fuel cells. As explained in [6], a cascaded multilevel inverter may have more potential than other multilevel topologies since the input separated dc sources (SDCS) can be naturally interfaced to a multilevel inverter to provide higher output voltages with high quality waveforms. However, a cascaded multilevel inverter contains many power switches, and the number of power switches depends upon the number of required output voltage levels. Consequently, higher switching losses become a trade off for output voltage quality. Multilevel inverter topologies for stand-alone PV systems have been discussed in [7]. The prototype in [7] shows that a 96% efficiency at 3 kVA for a single phase inverter was achieved. It would be better if it was possible to reduce the number of power switches in a multilevel inverter with the same functionality in order to reduce switching losses and improve inverter efficiency. Therefore, a hybrid multilevel inverter (HMI), also known as an asymmetrical multilevel inverter, is developed for low voltage dc distribution in data center buildings as shown in Fig. 1. The photovoltaic cell (PV solar rooftop) and battery bank can be interfaced with a 48 V dc grid via a dc to dc converter. In addition, a dc sensitive load such as switching routers, modems, and telecommunication devices can be connected to the 48 V dc bus. The energy management between the energy source and the loads are monitored. For instance, if the PV and energy storage system generation did not have adequate power to supply a required load, the energy management system would draw power from the utility grid. It should be noted that both the energy storage system and the dc to dc converter interfaced with the utility grid are generally installed in the data center building for backup energy. Fig. 1 shows that several converters are required for this system to interface with multiple loads, which leads to a total efficiency. Therefore, multiple load terminals are required for this particular application which can provide a better total efficiency. That is why, a HMI is applied in this study. In addition, the studies from [4], [5] suggest that dc distribution could perform better than ac distribution if a low dc voltage 48 V is available such in the data center case. It can be see that the proposed HMI can supply both single phase and three phase electrical systems. As previously mentioned, a three phase 220/380 V is supplied for air conditioning units and a single phase 220 V is supplied for lighting and PC loads. The HMI consists of two types of inverters: a conventional three phase six switches inverter and a single phase four switches H-bridge inverter. A HMI has been proposed with several applications as clearly explained in [8]-[10]. In addition, a new configuration for three-phase asymmetrical multilevel inverters together with a PWM technique with a higher resolution was originally proposed in [11]. In addition, an effective space vector PWM modulation for HMI applications with a low current distortion has been clearly described in [12]. However, so far, the applications for a data center building with 48 V dc distributions are limited. For this reason, a PWM paradigm and reconfiguration technique under fault conditions for a cascaded hybrid multilevel inverter for low voltage dc distribution using only a single chip controller to improve the system efficiency, reliability, and cost effectiveness is the main contribution of this paper. The paper is organized into 5 sections. First the proposed PWM paradigm for a single-chip is explained. Then, the fault detection and reconfiguration technique under the HMI malfunctioning condition is discussed. After that, experimental results and a loss validation of the developed prototype are investigated. Finally, some concluding remarks are presented.

# II. PROPOSED PWM PARADIGM

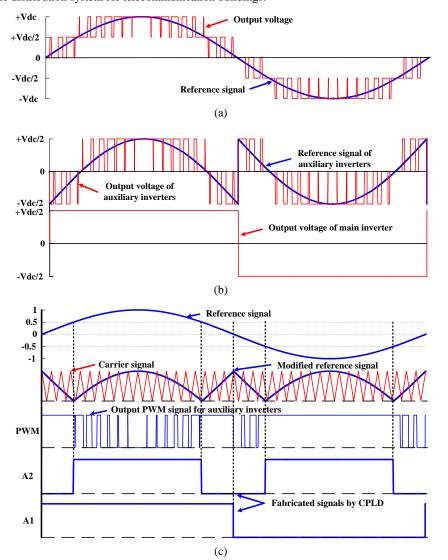

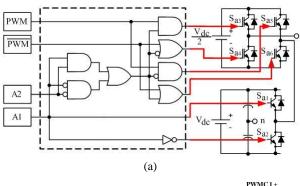

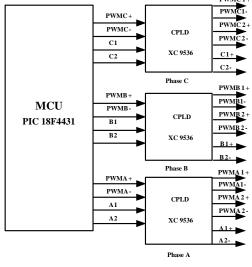

The main inverter refers to the six-switch three phase inverter, and the auxiliary inverter refers to the four-switch H-bridge inverter. Since low switching losses during PWM operation is required, the main inverter will operate in the square wave mode, and the auxiliary inverter will operate in the PWM mode as depicted in Fig. 2. In practice, if a single chip is used to generate the PWM signals, it normally has only one carrier signal with six PWM channels. Nevertheless, the HMI requires 12 PWM channels for both the main and auxiliary inverters. Therefore, the reference signal of the sinusoidal PWM (SPWM) used for the auxiliary inverter is modified using (1)-(4). The multiplexing signals from (3) and (4) are used to synthesize a PWM signal using the logic diagram shown in Table I and Fig. 3. In this particular application, aPIC18F4431 low cost single chip is used to generate the PWM signals. This is incorporated with a CPLD XC9536XL to fabricate the PWM signals for the proposed HMI.

$$f(t) = m_a \cdot \sin(\omega t) \tag{1}$$

$$\frac{T_P}{T_C} = \begin{cases} 2\left(f(t) - \frac{1}{2}\right); \frac{1}{2} \le |f(t)| \le 1\\ 2\left(\frac{1}{2} - f(t)\right); 0 \le |f(t)| \le \frac{1}{2} \end{cases}$$

(2)

$$A_{1} = \begin{cases} 1 & ; f(t) \ge 0 \\ 0 & ; f(t) < 0 \end{cases}$$

(3)

Fig. 1. A low voltage dc distribution system for telecommunication buildings.

Fig. 2. Proposed PWM paradigm: (a) output phase voltage, (b) auxiliary and main inverter output voltages, and (c) modulation signals and fabricated signal of both main and auxiliary inverter.

TABLE I

FABRICATED PWM SIGNAL FOR PROPOSED HMI SYSTEM [13]

| TABRICATED TWIN SIGNAL FOR TROPOSED THAT STSTEM [13] |                                                                              |  |

|------------------------------------------------------|------------------------------------------------------------------------------|--|

| $S_n$                                                | Hybrid PWM mixing operator                                                   |  |

| Sal                                                  | A1                                                                           |  |

| $S_{a2}$                                             | $\overline{A1}$                                                              |  |

| S <sub>a3</sub>                                      | $PWM \bullet ((A2 \bullet A1) + (\overline{A2} \bullet \overline{A1}))$      |  |

| S <sub>a4</sub>                                      | $\overline{PWM} + ((A2 \bullet A1) + (\overline{A2} \bullet \overline{A1}))$ |  |

| S a5                                                 | $PWM \bullet ((A2 \bullet A1) + (\overline{A2} \bullet \overline{A1}))$      |  |

| $S_{a6}$                                             | $\overline{PWM} + ((A2 \bullet A1) + (\overline{A2} \bullet \overline{A1}))$ |  |

Fig. 3. Diagram for PWM generating signal: (a) logic diagram of CPLD and (b) Proposed single-chip controller.

(b)

$$A_{2} = \begin{cases} 1 & ; |f(t)| \ge \frac{1}{2} \\ 0 & ; |f(t)| < \frac{1}{2} \end{cases}$$

(4)

where

f(t) is a reference signal,  $m_a$  is the modulation index (0.0/1.0-1.0/1.0),  $A_I$  is multiplexing signal #1,  $A_2$  is multiplexing signal #2,  $\frac{T_P}{T_C}$  is the pulse width of the PWM (0.0–1.0).

#### III. FAULT DIAGNOSTIC METHODOLOGY

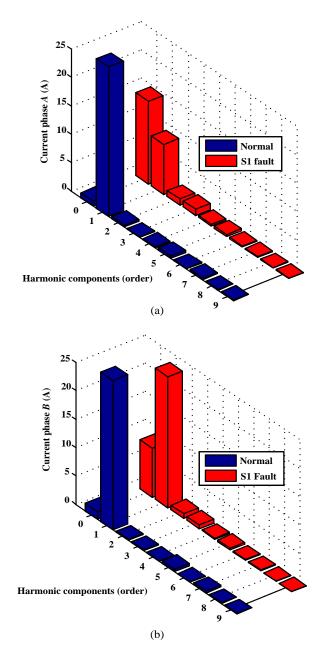

PSIM (Powersim) and MATLAB/Simulink are utilized to create a simulation model. MATLAB/Simulink is used to simulate the control signals and PSIM acts as a hardware prototype. This simulation model offers the simplicity of a changing control scheme and it is simple to transfer the control model from simulation to implementation in a single chip. The fundamental output voltages can be controlled by changing the modulation index  $(m_a)$  of the reference signal. In addition, the fundamental output frequency can be adjusted by changing the frequency of the reference signal as reported in [13]. It is possible that a diagnostic method, namely the normalized dc current method, can be applied for detecting open circuit switch faults as report by [17]. This is done by using the normalized dc current instead of currents transformed to the orthogonal space. The normalized dc current is the ratio between the dc component and the fundamental component. The fault observer is based upon the relationship between the normalized dc currents in each phase. To illustrate this, the current spectrums  $(i_a \text{ and } i_b)$  of an open circuit fault at switch  $S_1$  are shown in Fig. 4. Obviously, the dc component of the currents in both phases is not zero during faults, and the fundamental component of a faulty phase (phase A) is smaller than the fundamental component of a related phase (phase B). Therefore, the properties of the current spectrums can be applied to detect faults and localize faulty switches of a HMI. To achieve this, the recursive DFT algorithm is applied to calculate the fundamental component and dc components of the three-phase line currents. A threshold value of 0.45 is used as a fault indicator. This threshold is derived from experiment on the HMI because equal dc sources are required for HMIs. A fault is detected when the threshold is exceeded (> 0.45) in one phase, while the other phases are below the threshold value (< 0.45) and have reverse polarities with respect to the faulty phase. The decision making rules using binary codes to detect and localize the faults are illustrated in Table I.

As can be seen, two binary bits are used in each phase; the left hand side bit and the right hand side bit. First, the left hand side bit is used to indicate whether a normalized dc current exceeded the threshold or not; "0" is a normalized dc current lower than the threshold, while"1" is normalized dc current greater than the threshold. Second, the right hand side bit is used to determine the polarity of the currents; "0" is a negative current, while "1" is a positive current. The mathematical expression of the recursive DFT is represented as follows:

Fig. 4. Current spectrum of  $i_a$  and  $i_b$ during normal and open circuit fault at  $S_I$ :(a) line current at phase A  $(i_a)$ and (b) line current at phase B  $(i_b)$ .

$$i_{1}(k\tau) = a_{1}\cos(\frac{2\pi}{T} \times k\tau) + b_{1}\sin(\frac{2\pi}{T} \times k\tau),$$

$$a_{1} = \frac{2}{N} \sum_{k=1}^{N} i(k\tau)\cos(\frac{2\pi k}{T}),$$

$$b_{1} = \frac{2}{N} \sum_{k=1}^{N} i(k\tau)\cos(\frac{2\pi k}{T}),$$

$$i_{av}(k\tau) = \frac{1}{N} \sum_{k=1}^{N} i(k\tau),$$

$$(5)$$

where N is the total number of points per period, k is 0,1,2...N-1, and  $\mathcal{T}$  is a sampling period  $(\frac{T}{N})$ .

Fig. 5. "Neutral shift method [14]" for a reconfiguration technique.

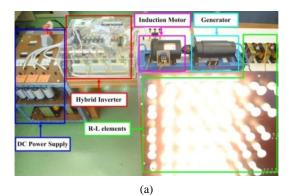

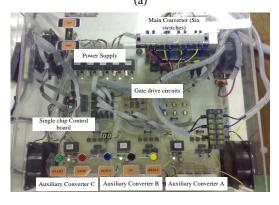

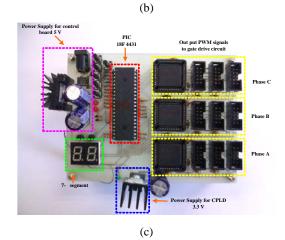

Fig. 6. Experimental setup: (a) connected with load and measurement unit, (b) proposed hybrid multilevel inverter, and (c) proposed single chip technique for the HMI.

The advantage of the normalized dc current method is that the diagnostic variables (normalized dc currents) are independent from the motor load; while the average Park's vector approach is dependent on the motor load. The current components in the orthogonal space will be small when the motor is running at a light load. This might result in incorrect identification of the fault location.

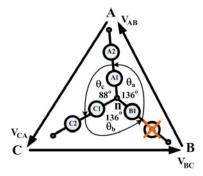

# IV. UTILIZED RECONFIGURATION TECHNIQUE

The neutral shift (NS) technique proposed in [14] can also be applied to a HMI during a fault condition. The essence of the NS technique is the adjustment of the angle of the neutral point of the three phase wye-connection system as shown in Fig. 7. Obviously, the line to neutral voltages (*Van*, *Vbn*, *Vcn*) are not out of phase with each other by 120 degree as usual. However, the line to line voltages (*Vab*, *Vbc*, *Vca*) are balanced even though the auxiliary power cell on phase *B* is malfunctioning. The angles of the reference signals to shift the neutral point under a fault condition at an auxiliary inverter in each phase can be calculated using (6) to (14).

# A. Faulty Auxiliary Cell at Phase a:

$$\theta_a = 60^{\circ} + \cos^{-1} \left( \frac{V_{an} \cdot \sin(30^{\circ})}{V_{bn}} \right)$$

(6)

$$\theta_c = \theta_a \tag{7}$$

$$\theta_b = 360^{\circ} - \theta_a - \theta_c \tag{8}$$

B. Faulty Auxiliary Cell at Phase b:

$$\theta_b = 60^\circ + \cos^{-1} \left( \frac{V_{bn} \cdot \sin(30^\circ)}{V_{cn}} \right) \tag{9}$$

$$\theta_a = \theta_b \tag{10}$$

$$\theta_c = 360^{\circ} - \theta_a - \theta_b \tag{11}$$

C. Faulty Auxiliary Cell at Phase c:

$$\theta_c = 60^\circ + \cos^{-1} \left( \frac{V_{cn} \cdot \sin(30^\circ)}{V_{an}} \right) \tag{12}$$

$$\theta_b = \theta_c \tag{13}$$

$$\theta_a = 360^{\circ} - \theta_b - \theta_c \tag{14}$$

A calculation example of a faulty auxiliary inverter at phase b is provided as follows:

$$\theta_b = 60^{\circ} + \cos^{-1} \left( \frac{120 \cdot \sin(30^{\circ})}{150} \right);$$

$$\theta_b = 136.66^{\circ};$$

$$\theta_a = \theta_b = 136.33^{\circ};$$

$$\theta_c = 360^{\circ} - 136.66^{\circ} - 136.66^{\circ};$$

$$\theta_c = 87.34^{\circ}.$$

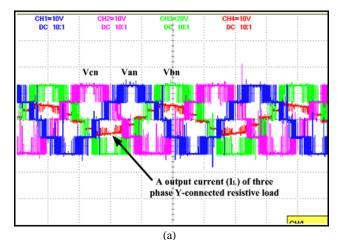

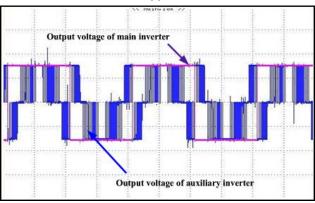

Fig. 7. Experimental results operating at  $m_a = 1.0/1.0$  for the resistive load: (a) output line to neutral voltages and line current, (b) output voltages of main and auxiliary inverter, and (c) waveform quality of output voltage.

It can be seen that the computational process is simple so that this reconfiguration method can be implemented in a single chip. It should be noted that this proposed reconfiguration can only be performed under a fault in the auxiliary inverter. If the fault occurs at the main inverter, all of the auxiliary inverters are bypassed. Then, the fault tolerance technique developed in [15] can be used for a conventional inverter. Of course, operation under a high quality output voltage waveform and full rated power is not possible under this condition. However, the amount of reduction in the rated power and waveform quality that can

be tolerated depends upon the HMI application. Nevertheless, in most cases, a reduction of the converter power is preferable to a complete shutdown. In a data center application, a HMI is used to supply the air conditioning systems. Therefore, reductions in the power operation and waveform quality would be acceptable.

### V. EXPERIMENTAL SETUP AND RESULTS

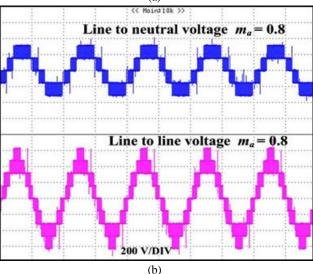

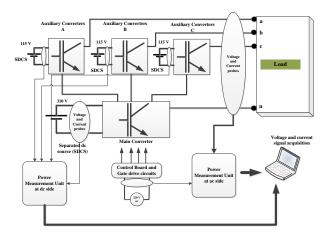

The experimental setup is shown in Fig. 6. The 3-kVA prototype was developed by using an IGBT module (Mitsubishi, CM20TH-24H 1200V 20A) in the main inverter and MOSFETs (Fairchild, IRFP 450, 500 V, 14 A) in the auxiliary inverters. A multiple winding transformer with bidirectional ac-dc converters was used as a SDCS for supplying dc voltages to the HMI. A 2-hp induction motor and R-L elements were used as electric loads to emulate an air conditioning compressor. A Yokogawa oscilloscope incorporated with a PC was used to perform measurements and data acquisition.

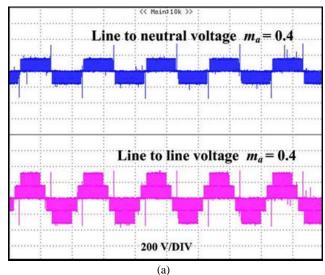

The experimental results illustrated in Fig. 7(a) show the output line to neutral voltage ( $V_{LN}$ ) and the output line current ( $I_L$ ) of the proposed HMI operating at a unity modulation index. As can be seen, the HMI can produce the PWM output voltage and current of a resistive load. The output voltages of the main and auxiliary inverter are depicted in Fig. 7(b). Clearly, the main inverter operates in the square wave mode, but the auxiliary inverter operates in the PWM mode. The output waveform quality in the PWM mode is shown in Fig.7(c). The output voltages of the HMI with different  $m_a$  operations are shown in Fig. 8.It can be seen that the fundamental output voltage can be controlled by adjusting  $m_a$ . This implies that the HMI can also be applied in drive applications requiring the V/f control mode.

Fig. 8 illustrates that HMIs do have a depraved total harmonic voltage distortion (THD<sub>V</sub>) at a low modulation index (< 0.5/1.0) because the HMI is operating the same as a conventional inverter which normally has a quite high THD<sub>V</sub>. However, the output voltage quality will be much better at high  $m_a$  (> 0.6/1.0) as shown in Table III. Table III shows the experimental results of the HMI operating under various load conditions. The results suggest that the HMI should operate at  $m_a$  more than 0.6 out of 1.0 for applications that require high output voltage quality such resistive loads. However, the THD<sub>v</sub> will convey the same effects ask conventional converter. Clearly, the resistive loads in microgrids are generally used for single phase operation at a high  $m_a$ . These HMIs will operate at a multilevel output voltage PWM waveform. In addition, the THD<sub>v</sub> will have smaller impacts on drive applications due to the low pass filter properties of an induction motor.

The efficiency of the proposed HMI is evaluated as illustrated in Fig. 9. Fig. 9 shows the power measurement

Fig. 8. Line to neutral and line to line voltage: (a) operating at  $m_a$  = 0.4, (b) operating at  $m_a$ = 0.8.

TABLE II

DIAGNOSTIC RULES FOR OPEN CIRCUIT FAULTS

|                     | Binary codes for fault diagnosis |            |            |  |

|---------------------|----------------------------------|------------|------------|--|

| Switch<br>locations | $I_{av,A}$                       | $I_{av,B}$ | $I_{av,C}$ |  |

| iocuiions           | $I_{1,A}$                        | $I_{1,B}$  | $I_{1,C}$  |  |

| $S_{al}$            | 1 0                              | 0 1        | 0 1        |  |

| $S_{c2}$            | 0 0                              | 0 0        | 1 1        |  |

| $S_{bI}$            | 0 1                              | 1 0        | 0 1        |  |

| $S_{a2}$            | 1 1                              | 0 0        | 0 0        |  |

| $S_{cI}$            | 0 1                              | 0 1        | 1 0        |  |

| $S_{b2}$            | 0 0                              | 1 1        | 0 0        |  |

${\bf TABLE~III}$  Total Harmonic Voltage Distortion at Various  $M_A$

| Load condition (m <sub>a</sub> ) | %THD $_{\rm V}$ of Phase voltage( ${ m V}_{ m an}$ ) | %THD $_{ m V}$ of line to line voltage( ${ m V}_{ab}$ ) |

|----------------------------------|------------------------------------------------------|---------------------------------------------------------|

| 0.4/1.0                          | 74.36                                                | 65.16                                                   |

| 0.8/1.0                          | 37.15                                                | 26.62                                                   |

| 1.0/1.0                          | 25.81                                                | 24.68                                                   |

Fig. 9. Power measurement units and data acquisition.

TABLE IV EFFICIENCY EVALUATION OF PROPOSED HMIAT $m_a$ =1.0

| Efficience Evaluation of Troposed Invitating 1.0 |                                            |           |                                                  |                                        |

|--------------------------------------------------|--------------------------------------------|-----------|--------------------------------------------------|----------------------------------------|

| Description                                      | dc side                                    |           | ac side                                          | Control<br>board and<br>gate<br>drives |

|                                                  | Main                                       | Auxiliary | Hybrid                                           |                                        |

|                                                  | inverter                                   | inverter  | inverter                                         |                                        |

| Voltage (V)                                      | 306.7                                      | 153.3     | 224.86                                           | 221.13                                 |

| Current (A)                                      | 1.87                                       | 4.52      | 3.95                                             | 0.059                                  |

| Power (W)                                        | 2,652.7<br>(all 4 inputs of SDCS<br>power) |           | 2,597.85<br>(All three<br>phase output<br>power) | 13.09                                  |

| Total losses<br>(W)                              | 67.94                                      |           |                                                  |                                        |

| % losses                                         | 2.55 %                                     |           |                                                  |                                        |

TABLE V EFFICIENCY EVALUATION AT VARIOUS  $m_a$

| Load condition (m <sub>a</sub> ) | Total efficiency |

|----------------------------------|------------------|

| 0.4/1.0                          | 92.57%           |

| 0.8/1.0                          | 95.25%           |

| 1.0/1.0                          | 97.45%           |

setup. All of the voltage and current signals (including the dc inputs, the ac input of the control board, and the ac outputs) were captured using a DL-1540C and a PZ4000 at the same time on both the dc and ac sides by using an external trigger. All of the data was then transferred to a PC to perform an efficiency evaluation. As shown in Fig. 9, the dc side power at the auxiliary inverters and the main inverter together with the ac input power of the control board and the ac output power at the load can be analyzed separately. The dc side power was probed at the separated dc source. Therefore, it does not include a transformer or an ac/dc converter as shown in Fig. 1. This is because the proposed HMI was needed for evaluation. The total power consumption of the HMI operating at a unity modulation index on the dc and ac sides including the control board together with gate drives are

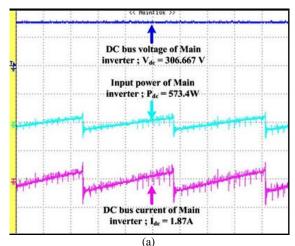

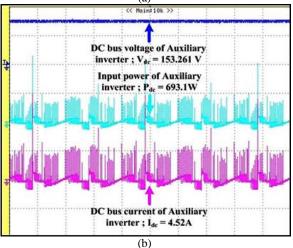

Fig. 10. Voltage, current and power waveforms operating at  $m_a = 1.0/1.0$  on dc sides: (a) main inverter and (b) auxiliary inverter at only phase A.

summarized in Table IV. The results show that the proposed HMI efficiency is 97.45% under this particular load condition. It should be noted that the HMI efficiency varies depending on the load condition. Normally, the efficiency would be lower under the light load condition as shown in Table V. The results suggest that the proposed HMI is a promising topology to apply to renewable energy resources; particularly, when multiple separate dc sources are available. For instance, a battery or fuel cell can interface with a main inverter; while an ultra-capacitor or photovoltaic cell can also connect to auxiliary inverters [16].

The voltage, current, and power waveforms on the dc side are shown in Fig. 10. It should be noted that there are four SDCSs in this HMI system: three SDCSs for the auxiliary inverter (about 115 V) and one SDCS for the main inverter (about 310 V). Fig. 10(a) shows all of the waveforms at the main inverter. Meanwhile, Fig. 10(b) shows the voltage, current and power waveforms of only one phase (Phase A) of the auxiliary inverter. The consumed power should be the same value in each of the phases for a three phase balanced system (an induction motor load). Therefore, the total input

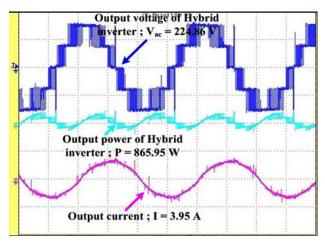

Fig. 11. Voltage, current and single phase power waveforms of proposed HMI operating at  $m_a = 1.0/1.0$  on ac side at phase A.

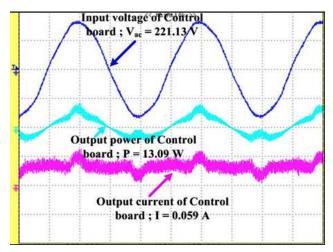

Fig. 12.Voltage, current and power waveforms at the input of the control board.

power is the sum of the consumed power from all of the SDCSs. The total power is about 2,653 watts. On the other hand, the voltage, current, and single phase power waveforms on the ac side are depicted in Fig. 11. The neutral point of the HMI is located at the main inverter as shown in Fig. 1. The phase A power consumption is about 866 watts. Hence, the total power output is about 2,598 watts for all three phases. Additionally, the input ac power of the single chip control board is illustrated in Fig. 12. A simple linear power supply including a diode bridge rectifier and a step down transformer is applied. The consumed power of the control board is about 13 watts. This power consumption can be reduces if a switching power supply is utilized. Therefore, the total losses of the proposed HMI at  $m_a$  1.0/1.0 are less than 3 %. Again, the losses of the HMI can be varied under different load conditions as shown in Table IV. The HMI can provide lower losses compared to a conventional cascaded inverter because the HMI will operate in the square wave mode at the main inverter with a lower number of switches. However, the HMI will operate in the PWM mode at the auxiliary inverters.

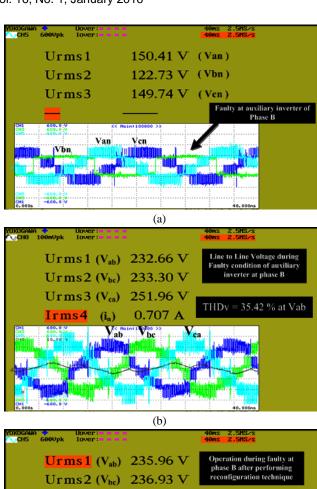

(c) Fig. 13. Voltage and current waveforms showing: (a) Line to neutral voltages during fault occurring at phase *B*, (b) Line to line voltages and neutral current during fault occurring at phase *B*, and (c) Line to line voltages and a line current after performing reconfiguration technique.

0.691

$\Gamma HDv = 28.42 \%$  at Vab

Urms3 (Vca)

Irms4

Therefore, the switching losses at the main inverter, which is operated at the fundamental frequency, is generally less than an inverter operated in the PWM mode compared to the conventional cascaded multilevel inverter case. However, the total efficiency, including a separated winding transformer, needs to be consider which is normally up to 98%. As previously mentioned, the HMI can offer a multiple load system, including single phase and three phase systems, with a fine output waveform quality. The experimental results suggest that the HMI can be an alternative technique for low voltage dc distribution applications. The disadvantage of the proposed HMI for a single phase load is the neutral point

which is connected to the middle point of the capacitors at the dc bus. During the unbalanced load condition, the dc voltage across each capacitor can be unequal which will lead to an unbalanced output voltage. The dc bus capacitors should be carefully designed; and the reference signals of the main inverter should be modified to compensate for unbalanced load conditions as discussed in [9] and [15].

On the other hand, an advantage of the proposed HMI is its fault tolerance capability. The HMI is based upon a cascaded multilevel inverter. Therefore, if a cell of the auxiliary inverters is faulted, the remaining cells can provide extra voltage by increasing  $m_a$  to compensate the line to line voltage. This type of approach is referred to as a neutral shift technique as proposed in [14]-[16]. Neutral shift techniques including fault detection have been clearly explained in [14]-[16]. The HMI system was supplied by an induction motor load for this particular test and the fault condition was created as an open switch fault at Phase B. The HMI was operating at  $m_a = 0.8/1.0$  before the fault occurred. Fig. 15 shows experimental results of the proposed HMI operating under the faulty conditions of an auxiliary inverter at phase B. As can be seen, Fig. 13(a) shows that the waveform quality of both the output line to neutral voltages and the line to line voltages are distorted and unbalanced. The THD, of Vab increases from about 26.6% (See Table III) to 35.42%. This fault can also cause an unbalanced voltage of about 20 volts as depicted in Fig. 13(b). The deteriorated waveform quality and the unbalanced line to line voltages due to a fault occurring at the phase B auxiliary inverter can be solved by using the proposed reconfiguration technique as shown in Fig. 13(c). Obviously, the line to line voltages have a better THD<sub>V</sub> and a balanced voltage after performing reconfiguration technique. However, in this case, the remaining auxiliary inverters increase  $m_a$  to 1.0/1.0 from compensating the lost voltage. As can be seen, the voltage cannot be completely restored to the same level before the fault. Therefore, the HMI needs to operate at under the rated power limit during the fault condition. However, it is better in term of a balanced voltage and continuous operation. In addition, if an open circuit fault occurs at the main inverter in a single switch, the proposed reconfiguration technique can also perform with 50% of the rated power at a faulty phase. Unfortunately, in the end, a short circuit fault and multiple switch faults cause the HMI to shut down the operation. Nevertheless, in several applications, a reduction of the rated power is preferable to a complete shutdown. Additionally, the neutral shift method can convey a common mode voltage during operation under a fault condition which has been addressed in [14].

By utilizing the proposed HMI, a high quality output voltage waveform with a high inverter efficiency and reliability can be achieved. In most cases, the HMIs in data center applications will not require a wide range of modulation indices. However, a wide range modulation index

is needed for drive applications. In addition, the HMI requires a half of the dc input voltage of the main inverter supplying the auxiliary inverter in order to achieve balanced output voltages.

# VI. CONCLUSION

A cascaded hybrid multilevel inverter including a reconfiguration technique application for the low dc voltage distribution systems in data center buildings has been developed. A modified PWM technique fault detection and reconfiguration have also been proposed to reduce switching losses. In addition, the proposed topology can reduce the number of required power switches compared to a traditional cascaded multilevel inverter. Simulation and experimental results verify the proposed techniques. The switching losses of the HMI are less than the conventional multilevel inverters due to the reduced number of required power switches. As a result, the system efficiency can be improved by utilizing the proposed HMI. In addition, a 97.45% inverter efficiency has been achieved based on the tested conditions. A reconfiguration technique for use after a fault condition has also been developed to improve the system reliability. The results show that the proposed HMI topology is a promising method for the low voltage dc distribution systems in data center buildings.

# REFERENCES

- [1] R. Lasseter, "Microgrid," in *Proc. IEEE Power Engineering Society Winter Meeting 2002*, pp. 305-308.

- [2] F. Z. Peng, Y. W. Li, and L. M. Tolbert, "Control and protection of power electronics interfaced distributed generation systems in a customer-driven microgrid," *IEEE Power and Energy Society General Meeting*, pp. 1-8, 2009.

- [3] J. J. Justo, F. Mwasilu, J. Lee, and J. W. Jung, "AC-microgrids versus DC-microgrids with distributed resources: A review," *Renewable and Sustainable Energy Reviews*, pp. 387-405, Vol. 24, Aug. 2013.

- [4] H. Kakigano, Y. Miura, T. Ise, and R. Uchida, "DC micro-grid for super high quality distribution-system configuration and control of distributed generations and energy storage devices," in 37th Annual IEEE Power Electronics Specialists Conference, pp. 1-7, 2006.

- [5] D. Salomonson and A. Sannino, "Low-voltage DC distribution system for commercial power system with sensitive electronic loads," *IEEE Trans. Power Del.*, Vol. 22, No. 3, pp 1620-1627, Jul. 2007.

- [6] S. Khomfoi and L. M. Tolbert, Multilevel Power Converters, Power Electronics Handbook, 2nd Edition Elsevier, Chapter 17, pp. 451-482. 2007.

- [7] S. Daher, J. Schmid, and F. L. M. Antunes, "Multilevel inverter topologies for stand-alone PV systems," *IEEE Trans. Ind. Electron.*, Vol. 55, No. 7,pp. 2703-2711. Jul. 2008

- [8] M. D. Manjrekar, P. Steimer, and T. A. Lipo, "Hybrid multilevel power conversion system: A competitive solution for high power applications," *IEEE Trans. Ind.*

- Appl. Vol. 36, No. 3, pp. 834-841, May/Jun. 2000.

- [9] Z. Du, B. Ozpineci, L. M. Tolbert, and J. N. Chiasson, "A novel inductor-less DC-AC cascaded h-bridge multilevel boost inverter for electric/hybrid electric vehicle applications," in *IEEE Industry Applications Society Annual Meeting*, 2007.

- [10] H. Liu, L. M. Tolbert, B. Ozpineci, and Z. Du, "Comparison of fundamental frequency and PWM methods applied on a hybrid cascaded multilevel inverter," in *IEEE Industrial Electronics Society Annual Conference*, pp. 3233-3237, 2008.

- [11] S. Mariethoz and A. Rufer, "New Configurations for the three-phase asymmetrical multilevel inverter," in *IEEE Industry Applications Society Annual Meeting*, Vol. 2, pp. 828-835, 2004.

- [12] S. Lu, S. Mariethoz, and K. A. Corzine, "Asymmetrical cascade multilevel converters with noninteger or dynamically changing DC voltage ratios: Concepts and modulation techniques," *IEEE Trans. Ind. Electron.*, Vol. 57, No. 7, pp. 2411-2418, Jul. 2010.

- [13] S. Khomfoi and N. Praisuwanna, "A hybrid cascaded multilevel inverter for interfacing with renewable energy resources," in *Proc. the 2010 International Power Electronics Conference (IPEC)*, pp. 2912-2917, Jun. 2010.

- [14] D. Eaton, J. Rama, and P. W. Hammond, "Neutral shift," IEEE Ind. Appl. Mag., pp. 40-49, Nov./Dec. 2003.

- [15] B. A. Welchko, T. A. Lipo, T. M. Jahns, and S. E. Schulz, "Fault tolerant three-phase AC motor drive topologies: A comparison of features, cost, limitations," *IEEE Trans. Power Electron.*, Vol. 19, No. 4,pp. 1108-1116, Jul. 2004.

- [16] S. Khomfoi, N. Praisuwanna, and L. M. Tolbert, "A hybrid cascaded multilevel inverter including a reconfiguration technique application for low voltage DC distribution," in *IEEE Energy Conversion Congress and Exposition*, Sep. 2010.

- [17] S. Abramik, W. Sleszynski, J. Nieznanski, and H. Piquet, "A diagnostic method for on-line fault detection and localization in vsi-fed ac drive," in *Proc. the 2003 EPE* 10th European Conference on Power Electronics and Applications, pp.1-8, 2003.

Surin Khomfoi was born in Thailand. He received his B.Eng. and M.Eng. in Electrical Engineering from the King Mongkut's Institute of Technology Ladkrabang (KMITL), Bangkok, Thailand, in 1996 and 2000, respectively; and his Ph.D. degree in Electrical Engineering at the University of Tennessee, Knoxville, TN, USA, in 2007.

Since December 1997, he has been a Lecturer with the Department of Electrical Engineering, KMITL, where he is currently presently an Associate Professor. His current research interests include multilevel power converters, renewable energy applications, fault diagnosis, power quality and smartgrids. Dr. Khomfoi is a Member of the Eta Kappa Nu Honor Society and a Senior Member of the IEEE. He was a recipient of academic scholarship awards, including full academic scholarship for his B.Eng., M.Eng., and Ph.D. studies from the Energy Policy and Planning Office (EPPO), Ministry of Energy Thailand.