JPE 16-1-16

http://dx.doi.org/10.6113/JPE.2016.16.1.142 ISSN(Print): 1598-2092 / ISSN(Online): 2093-4718

# Carrier Based Common Mode Voltage Reduction Techniques in Neutral Point Clamped Inverter Based AC-DC-AC Drive System

Amit Ojha<sup>†</sup>, Pradyumn Chaturvedi<sup>\*</sup>, Arvind Mittal<sup>\*\*</sup>, and Shailendra Jain<sup>\*\*\*</sup>

†,\*\*\*Department of Electrical Engineering, Maulana Azad National Institute of Technology, Bhopal,India \*Dept. of Electrical and Electronics Eng., Birla Institute of Technology and Science, Pilani, India \*\*Energy Centre, Maulana Azad National Institute of Technology, Bhopal, India

## **Abstract**

Common mode voltage (CMV) generation is a major problem in switching power converter fed induction motor drive systems. CMV is the zero sequence voltage generated due to the switching action of power converters. Even a small magnitude of CMV with a high rate of change may circulate large bearing currents which may damage a machine's bearings and shorten its life. There are several methods of controlling CMV. This paper presents 3-level sinusoidal pulse width modulation based techniques to control the magnitude and rate of change of CMV in multilevel AC-DC-AC drive systems. Simulation and experimental investigations have been presented to validate the performance of proposed technique to control CMV in 3-level neutral point clamped inverter based AC-DC-AC system.

Key words: AC-DC-AC Drives, Common Mode Voltage Control, Neutral Point Clamped Inverter, Switching Converters

# I. INTRODUCTION

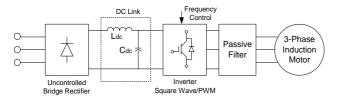

Energy saving has become apriority in industrialized countries nowadays. About 70% of the total generated electric energy is utilized by electrical motors. This fact draws attention for energy saving in AC-DC-AC drive systems. Variable voltage and variable frequency ac supply is required to feed induction motors to achieve energy efficient operation of various industrial applications. At a medium voltage, high power level, AC-DC-AC drive systems face practical problems related to the switching action of converters. Fig. 1 shows a basic block diagram of an AC-DC-AC drive system to generate variable voltage, variable frequency supply to feed a 3-phase induction motor. In such systems, voltage control is achieved at the front end converter

side and frequency control is achieved at the inverter side. Therefore, it is mandatory to use two converters before the power is fed to the induction motor. Conventional 2-level converters suffer from the drawbacks of large dv/dt stresses across devices, more switching losses, large harmonic contents and common mode voltage generation.

The generation of common mode voltage (CMV) can damage the motor winding insulation if not properly controlled or mitigated. It results in motor bearing currents leading to bearing failures. It can also generate motor shaft voltages, bearing currents, and conducted electromagnetic interference [1], [2].

The common mode voltage generated at the front end converter side, inverter side and motor side can be controlled by adding extra hardware circuitry (such as an isolation transformer, zero-sequence impedance/common mode choke, active and passive filters, dual bridge inverter, four-leg inverter, etc.) or by modifying the control strategy [3],[4]. Adding extra hardware to the circuitry results in reduced system reliability, increased cost and a less fault tolerant system. Several authors have presented different modified control strategies based on the sinusoidal pulse width

Manuscript received Apr. 1, 2015; accepted Jun. 29, 2015

Recommended for publication by Associate Editor Lixiang Wei.

<sup>&</sup>lt;sup>†</sup>Corresponding Author: pc220774@gmail.com

Tel: +917732893208, Maulana Azad National Institute of Technology \*Dept. of Electrical and Electronics Eng., Birla Institute of Technology and Science, India

<sup>\*\*\*</sup>Energy Centre, Maulana Azad National Institute of Technology, India

\*\*\*\*Department of Electrical Engineering, Maulana Azad National

Institute of Technology, India

Fig. 1. Voltage and frequency control in AC-DC-AC induction motor drive.

modulation (SPWM) technique [5],[6] and the space vector pulse width modulation (SVPWM) technique. These SVPWM techniques include the nearest three vector selection (NTV) SVPWM, radial state SVPWM, zero common mode voltage SVPWM [7]-[11], etc. However, the SVPWM based CMV reduction techniques require comparatively complex algorithms [2], [9], and [12]-[14]. Simple carrier based techniques such as Phase Disposition (PD), Phase Opposition Disposition (POD) and the addition of offset to the modulating signal have been presented in [15], [16] for controlling CMV in the output of inverter terminals. However, the techniques presented in these papers are used for multilevel inverters (MLI).

This paper investigated the effect of the amount of phase shift between the carriers and modulating signal, and the impact of the modulation index on inverter performance in terms of CMV. The amount of phase shift between the carriers and the modulating signal plays a very important role in determining inverter performance. This paper investigates the effect of the phase shift angle between the carrier and the modulating signal on the inverter output voltage and CMV (in terms of the number of switching per cycle) performance and implements the concept of adding an offset to the modulating signal as presented in [15] to reduce CMV and its rate of change for AC-DC-AC drive systems. The impact of change of the modulation index in terms of CMV is presented which effectively improves the system efficiency.

The paper is organized in five Sections. Section II presents a mathematical model to explain the causes of CMV generation in AC-DC-AC drive systems. It also provides the relation of CMV with leakage current. Section III presents the proposed concept to control CMV and its rate of change along with the effects of phase shift between the carriers and the modulating signal on inverter performance. The simulation performance of the proposed control technique is given in Section IV. Experimental verification of proposed technique is presented in Section V, followed by some conclusions and advice in Section VI.

# II. CAUSES OF COMMON MODE VOLTAGE

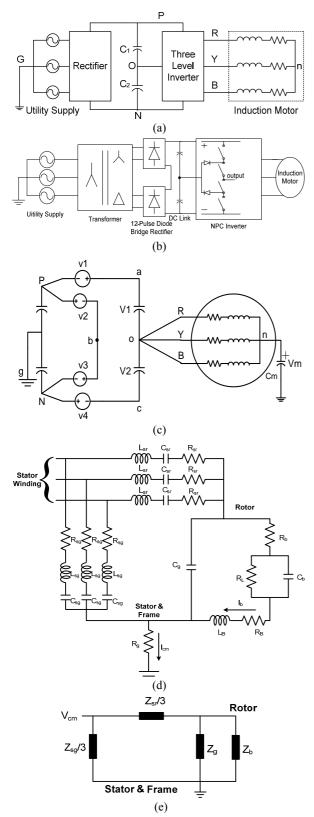

Fig. 2(a) shows a general block diagram of an AC-DC-AC induction motor drive system. The front end converter may be an uncontrolled or controlled voltage source or a current

source rectifier, while the motor side converter can be a conventional two-level or multilevel VSI, CSI. In the VSI fed drive, the DC link capacitor  $C_d$  ( $C_1$  and  $C_2$ ) is sufficiently large and a DC link inductor  $L_d$  is not required, whereas in the CSI fed drive,  $L_d$  is sufficiently large and  $C_d$  is not needed. In Fig. 2(a),

$V_{PG}$ &  $V_{NG}$ : Voltages at the positive and negative

dc link with respect to the ground

$V_{\text{OG}}$ : Common mode voltage produced by

the rectifier

$V_{\text{nO}}$ : Voltage between the neutral of the stator winding and the midpoint of the dc link (common mode voltage produced by the inverter)

The total common mode voltage (i.e. the motor neutral to utility ground voltage,  $V_{nO}$ ) generated by the rectification and inversion process is given by:

$$V_{nG} = V_{cm} = V_{cm} (\text{Re ctifier}) + V_{cm} (Inverter)$$

(1)

where,

$$V_{cm}$$

(Re ctifier) =  $V_{oG} = (V_{PG} + V_{NG})/2$  (2)

$$V_{cm}(Inverter) = V_{no} = (V_{nP} + V_{nN})/2$$

(3)

The total common mode voltage can also be represented as,

$$V_{nG} = V_{no} + V_{oG} \tag{4}$$

The motor line-to-ground voltage is:

$$V_{RG} = V_{Rn} + V_{nG} = V_{Rn} + V_{cm}$$

(5)

Fig. 2(b) shows block diagram of a AC-DC-AC NPC VSI fed ASD with a 12-pulse front end diode bridge rectifier. The input transformer has two secondary with 30° phase shift between them.

The common mode equivalent circuit of a NPC inverter is shown in Fig. 2(c) for common mode voltage analysis. The common mode voltage at motor terminals is,

$$V_{cm} = \frac{V_{Rg} + V_{Yg} + V_{Bg}}{3} \tag{6}$$

where,

$$\begin{cases}

V_{Rg} = V_{Ro} + V_{og} \\

V_{Yg} = V_{Yo} _{Q} - V_{og} \\

V_{Bg} = V_{Bo} + V_{og}

\end{cases}$$

(7)

Therefore,

$$V_{cm} = \frac{V_{Ro} + V_{Yo} + V_{Bo}}{3} + V_{og}$$

(8)

Now  $V_{\text{og}}$  is the common mode voltage at the rectifier terminals, which can be calculated from Fig. 2(c) as,

$$V_{ab} = V_{aP} - V_{bP} \tag{9}$$

$$V_{bc} = V_{bN} - V_{cN} \tag{10}$$

$$V_{ac} = V_{ab} - V_{bc} \tag{11}$$

Fig. 2. (a) General block diagram of AC-DC-AC VSI fed ASD. (b) Block diagram of AC-DC-AC NPC VSI fed ASD with 12-pulse front end diode bridge rectifier. (c) Common mode equivalent circuit of medium voltage NPC inverter fed ASD system. (d) High frequency model of 3-phase induction motor (17). (e) Simplified per phase model of induction motor.

$$V_{ao} = \frac{V_{ac}}{2} = \frac{V_{ab} + V_{bc}}{2} \tag{12}$$

Substituting (9) and (10) into (12) yields,

$$V_{ao} = \frac{V_{aP} - V_{bP} + V_{bN} - V_{cN}}{2} \tag{13}$$

$$V_{Pg} = \frac{V_{Pb} + V_{bN}}{2} \tag{14}$$

$$V_{og} = V_{pg} + V_{aP} - V_{ao} \tag{15}$$

$$V_{og} = \frac{V_{aP} + V_{cN}}{2} \tag{16}$$

This is the common mode voltage at the rectifier terminals. The common mode voltage (CMV) can damage the motor winding insulation if not properly mitigated. In addition, the CMV between the motor neutral and the ground may cause induced shaft voltages, bearing currents and circulating bearing currents.

The relation between the CMV and the leakage current can be deduced considering the high frequency model of a 3phase induction motor shown in Fig.2(d). The distributing parameters representing the HF coupling between the stator and rotor assembly are  $R_{sr}$ ,  $L_{sr}$  and  $C_{sr}$ . Considering the insulation effect of the bearing grease and the electric discharge (EDM) effect between the bearing balls and the races, the capacitance C<sub>b</sub> in parallel to the non-linear resistive circuit (R<sub>I</sub>) and in series with the bearing ball and race contact resistance R<sub>b</sub> can be modelled for the motor bearings. The bearing current Ib flows through the modelled wire impedance used for measuring the bearing current (LB and R<sub>B</sub>). The capacitance between the stator and the motor lamination across the motor air gap is represented by Cg. Rsg,  $L_{sg}$  and  $C_{sg}$  are considered as the couplings between the stator winding and the frame (stator) since it mainly contributes the total leakage current to the ground. The frame is modelled as the resistance of R<sub>g</sub> to the ground.

The shaft voltage can be calculated by considering the simplified per phase model of the induction motor shown in Fig. 2(e).

$$V_{sh} = V_{CM} \times \frac{Z_{rg}}{\frac{Z_{sr}}{3} + Z_{rg}}$$

$$\tag{17}$$

Where  $Z_{sr}$  is the impedance between the stator windings and the rotor, and the impedance between the rotor and the frame  $(Z_{rg})$  is defined as:

$$Z_{rg} = \frac{Z_g \times Z_b}{Z_o + Z_b}, Z_{sr} = R_{sr} + JL_{sr}\omega + \frac{1}{JC_{sr}\omega}$$

(18)

Where Zb and Zg can be calculated as,

$$Z_{b} = \frac{R_{L} \times \frac{1}{JC_{b}\omega}}{R_{L} + \frac{1}{JC_{b}\omega}} + R_{b} + R_{B} + JL_{B}\omega$$

(19)

$$Z_{g} = \frac{1}{JC_{p}\omega} \tag{20}$$

Therefore, the bearing current can be calculated as,

$$I_b = \frac{V_{sh}}{Z_b} \tag{21}$$

As a result, the leakage current can be calculated as,

$$I_{c} = \frac{V_{CM}}{Z_{sg}} + \frac{V_{sh}}{Z_{g}} + \frac{V_{sh}}{Z_{b}}$$

(22)

Where Zsg is the impedance between the stator winding and the ground which is given as,

$$Z_{sg} = R_{sg} + JC_{sg}\omega + \frac{1}{JC_{sg}\omega}$$

(23)

From equation (17) and (22), the following equation is obtained:

$$I_c = V_{cm} Z_T \tag{24}$$

where ZT is given as.

$$Z_{T} = \left[ \frac{\left[ Z_{g} Z_{b} \left( Z_{sr} / A + Z_{rg} \right) + Z_{sg} Z_{rg} \left( Z_{g} + Z_{b} \right) \right]}{Z_{sg} Z_{g} Z_{b} \left( Z_{sr} / A + Z_{rg} \right)} \right]$$

(25)

Equation (24) clearly shows that the smaller the CMV, the smaller the losses and higher the system efficiency.

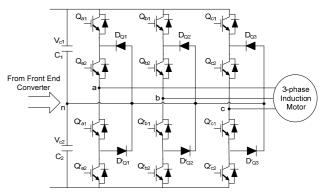

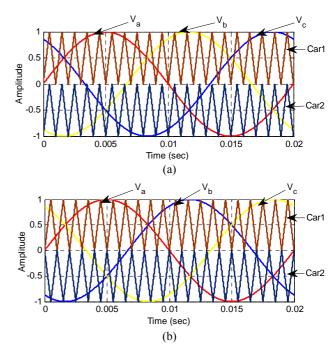

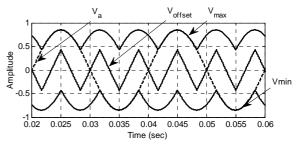

# III. COMMON MODE VOLTAGE (CMV) CONTROL

A schematic of the three-phase, neutral point clamped inverter fed induction motor drive system is shown in Fig. 3. The basic principles of the pulse generation for 3-level PD and POD SPWM techniques are shown in Fig. 4(a) and Fig. 4(b). Fundamental frequency three-phase sinusoidal reference waves  $V_a$ ,  $V_b$  and  $V_c$  are compared with two high frequency triangular carrier waves "Car1" and "Car2." Each intersection gives the control pulses for the switching devices of the inverter. These reference sinusoidal waves  $V_{(a,b,c)}$  can be represented by,

$$V_a = V_m \sin(\omega t)$$

$$V_b = V_m \sin(\omega t - 120^{\circ})$$

$$V_c = V_m \sin(\omega t - 240^{\circ})$$

(26)

The control pulses generated by a comparison of the reference voltage wave with "Car1" are given to the upper switches  $(Q_{a1}, Q_{b1}, Q_{c1})$  of the inverter shown in Fig. 3. The corresponding complementary signals of these pulses are given to  $(Q_{a1}, Q_{b1}, Q_{c1})$ . The control pulses generated by a comparison of the reference voltage wave with "Car2" are given to the switches  $(Q_{a2}, Q_{b2}, Q_{c2})$ . The corresponding complementary signals of these pulses are given to  $(Q_{a2}, Q_{b2}, Q_{c2})$

Fig. 3. Schematic of neutral point clamped inverter fed induction motor drive system.

Fig. 4. (a)Generation of control pulses with PD SPWM technique.(b) Generation of control pulses with POD SPWM technique.

Q<sub>c2</sub>). The modified SPWM based CMV control techniques and the effect of a phase shift between the carriers and the modulating wave are explained in following sections.

# A. Modified SPWM Based CMV Control Technique

The magnitude and rate of change of common mode voltage depend on the control pulse width, the number of commutations and its frequency, which can be modified by adding a variable offset voltage signal to the reference voltage wave [15]. The off-set voltage signal plays an important role in modifying the modulating or reference signal. This section presents the basic concept of calculating and adding the variable offset signal to the PD and POD SPWM techniques as shown in Fig. 5 (a) and Fig. 5 (b). Common mode voltage is essentially the zero sequence voltage in the output voltage of an inverter and can be

represented by,

$$V_{cm} = (V_a + V_b + V_c) / 3 (27)$$

Where  $V_a$ ,  $V_b$  and  $V_c$  are the phase voltages of the inverter. The magnitude of common mode voltage is approximately equal to the DC link voltage in a conventional 2-level inverter and half of the DC link voltage in a 3-level inverter with the PD SPWM technique. To reduce CMV, a variable common mode offset voltage signal is added to the reference voltage signal which can be estimated as.

$$V_{off} = -\left[\min(V_a, V_b, V_c) + \max(V_a, V_b, V_c)\right] / 2$$

(28)

where  $\min(V_a, V_b, V_c)$  and  $\max(V_a, V_b, V_c)$  are the minimum and maximum functions of the reference voltage wave. A new reference or modulating wave can be derived by adding this common mode variable offset voltage signal to the original reference voltage wave as,

$$V^*(a,b,c) = V(a,b,c) + V_{off}$$

(29)

where V(a,b,c) is given by (26). Fig. 5 (a) and Fig. 5 (b) show the 3-phase reference waves as given in (29). The 'max', 'min', one phase voltage  $V_a$ , and off-set voltage signal, as given by (26) to (29), are shown in Fig. 6 for the PD SPWM technique. This common mode voltage off-set signal controls the CMV in the inverter output. The new 3-phase reference waves with the addition of an offset signal for the PD SPWM technique is given in Fig. 5 (a). The new 3-phase reference waves with the addition of an offset signal for the POD SPWM techniques is shown in Fig. 5 (b).

# B. Effect of the Phase Shift between the Carriers and the Modulating Signal

The phase shift angle between the modulation signal and the carrier signals plays an important role in multilevel inverters in terms of the number of switching ( $N_{SW}$ ) within each fundamental cycle. The effect of this phase angle shift on  $N_{SW}$  is being studied in this section for 3-level neutral point clamped inverter. The modulating signal,  $V_a$  of a phase, can be represented by,

$$V_a^* = |V|\cos(\theta - \alpha)$$

(30)

Where, |V| is the magnitude of the phase voltage, and  $\alpha$  is the phase shift angle between the modulating signal and the carrier signal. In 2-level PWM inverters, with a single carrier signal, the number of switching  $N_{SW}$  is 84 for a frequency modulation index of  $m_f = 41$  regardless of the value of  $\alpha$  and for all values of the amplitude modulation index  $m_a < 1$ . In this section, the reduction of  $N_{SW}$  is studied by using the offset voltage signal addition technique as described in subsection A. The techniques presented previously by different authors considered only two cases for study i.e. (i) when the carrier is at its maximum, and the modulating signal is at its minimum, and (ii) when the carrier is at its minimum, and the modulating signal is at its maximum. Other possibilities which are important for exploring the capabilities of the

Fig. 5. (a) Generation of control pulses with addition of variable offset signal in PD SPWM technique.(b) Generation of control pulses with addition of variable offset signal in POD SPWM technique.

Fig. 6. Variable off-set voltage signal generation in PD SPWM technique.

offset signal addition technique have not been covered such as the effect of the phase shift between the carriers and the modulating wave. The value of  $\alpha$  is now varied and the effect of this shift on the total number of switching of the active devices and the output voltage waveform distortion have been observed. Fig. 4 (a) and Fig. 4 (b) show the principle of the generation of pulses for a 3-level NPC with the conventional PD and POD SPWM techniques. The offset addition technique with  $m_f = 41$ ,  $m_a = 1$  is given in Fig. 5 (a) and Fig. 5 (b). It is clear that, in offset addition PWM technique, again of 15 % in output voltage is achieved before going into the over-modulation region.

Total number of switching,  $N_{SW}$  (the active device transition from on-to-off or off-to-on), during a modulation period can vary from 84 to 116 when  $\alpha$  is varied from 0° to 8°. Tables I and II show the total number of switching per modulating cycle with a varying  $\alpha$  with  $m_f = 41$ ,  $m_a = 0.8$  with these techniques. It is clear that the number of switching decreases with the phase shift  $\alpha$  in the offset addition PWM

TABLE I

No. of Main Device Switching per Modulating Cycle for 3Level DCMLI with Conventional SPWM Technique (mf = 41, ma = 0.8)

| Carrier Phase    | No. of Switching per Cycle |                  |          |  |

|------------------|----------------------------|------------------|----------|--|

| Angle $(\alpha)$ | $Q_{a1}, Q_{a1}$           | $Q_{a2}, Q_{a2}$ | $N_{sw}$ |  |

| 0°               | 42                         | 42               | 84       |  |

| 2°               | 46                         | 46               | 92       |  |

| 4°               | 50                         | 50               | 100      |  |

| 6°               | 54                         | 54               | 108      |  |

| 8°               | 58                         | 58               | 116      |  |

**TABLE II**

No. of Main Device Switching per Modulating Cycle for 3-Level DCMLI with SFO-PWM Technique (Mf = 41, Ma = 0.8)

| Carrier Phase      | No. of Switching per Cycle |                  |          |

|--------------------|----------------------------|------------------|----------|

| Angle ( $\alpha$ ) | $Q_{a1}, Q_{a1}$           | $Q_{a2}, Q_{a2}$ | $N_{sw}$ |

| 0°                 | 52                         | 52               | 104      |

| 2°                 | 48                         | 48               | 96       |

| 4°                 | 44                         | 44               | 88       |

| 6°                 | 40                         | 40               | 80       |

| 8°                 | 36                         | 36               | 72       |

technique. At a particular phase shift i.e. 8°, the number of switching is even lesser than that in the conventional SPWM technique.

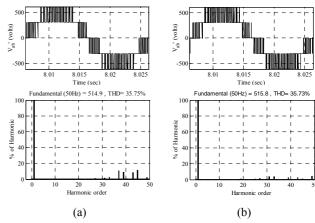

Fig. 7 shows the line voltages with the conventional PD SPWM and with the offset addition PD SPWM techniques. If the individual harmonic contents in the line voltages are investigated, it is determined that the lower order harmonics i.e. 39<sup>th</sup> and 43<sup>th</sup> have been drastically reduced in the offset addition PD SPWM when compared with the conventional PD SPWM technique. Therefore, the offset addition PD SPWM technique introduces the 3<sup>rd</sup> order harmonics in the phase voltage (eliminated from the line voltages), reduces the lower order harmonics from the line voltage and reduces the number of switching within each half of a cycle of inverter voltage, which reduces the switching losses.

# IV. SIMULATION RESULTS

A simulation study of the neutral point clamped inverter fed 3-phase squirrel cage induction motor has been carried out in MATLAB, and the simulation results are presented to validate the mathematical model presented for the CMV control. The simulation parameters for the common mode voltage control are given in Table III.

The CMV in a NPC inverter when compared to a 2-level inverter fed induction motor drive with  $m_f$  = 41 and  $m_a$  = 0.8 is considered in this section.

The inverter line voltage  $(V_{ab})$ , the stator current drawn by the induction motor  $(i_s)$ , and the speed of the machine  $(N_r)$  are shown in Fig. 8.

Fig. 7. Line voltages with (a) conventional PD SPWM and (b) offset addition PD SPWM techniques.

# TABLE III SIMULATION PARAMETERS

| DC Link Parameters |                                    |          |         |  |

|--------------------|------------------------------------|----------|---------|--|

| DC Link Voltage    |                                    | $V_{dc}$ | 620 V   |  |

| DC Link Capa       | DC Link Capacitance                |          | 2200 μF |  |

| Load Parameters    |                                    |          |         |  |

| Load type          | 3-φ, Squirrel Cage Induction Motor |          |         |  |

| Line Voltage       | 400 V                              |          |         |  |

| Speed              | 1440 RPM                           |          |         |  |

| Frequency          | 50 Hz                              |          |         |  |

| Rated Power        | 5 H.P                              |          |         |  |

| Power Factor       | 0.84                               |          |         |  |

Fig. 8. (a) Inverter line voltage  $(V_{ab})$ , (b) stator current  $(i_s)$ , and (c) speed  $(N_r)$ .

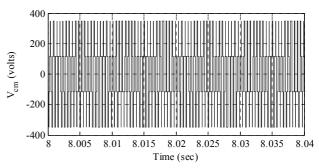

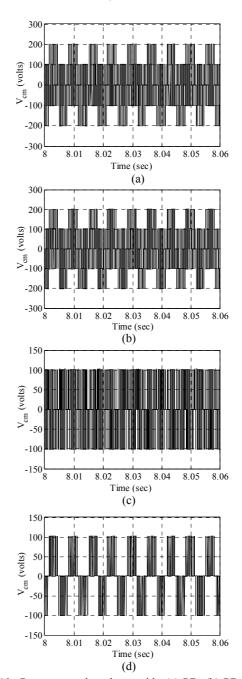

Fig. 9 shows the CMV at the inverter terminals when fed by a 2-level inverter. Fig. 10 presents the CMV with 3-level SPWM techniques such as PD, POD, PD with an offset

signal, and POD with an offset signal as discussed in Section II. It is observed that the magnitude of the CMV is considerably reduced in the NPC 3-level inverter fed induction motor drive when compared with the2-level inverter fed induction motor drive. This is another important feature of the multilevel structure for high power drives applications.

Fig. 11(a) shows the line voltages for the PD and the PD with off-set signal addition techniques. It is observed from these figures that the overall % THD remains almost same. However, it can also be seen that the low order harmonics are reduced considerably when an off-set signal is added to the modulating signal. The % THD in the line voltages is high for the PD and the PD with off-set signal addition techniques. The issue of the higher %THD in the line voltages can be easily handled by incorporating a well-designed LC filter as shown in Fig. 11(b).Fig. 11(b) clearly shows that the % THD is well below the limit of IEEE 519 in both cases.

The line voltage  $V_{ab}$  for the POD and the POD with addition of an off-set signal to the modulating wave without a filter is shown in Fig. 12(a). This clearly shows that the harmonic profile is deteriorated in the POD with an off-set signal with increased harmonics contents around the carrier frequency. Fig. 12(b) shows improved line voltage profiles when a filter is included.

Table IV gives a comparison of these techniques in terms of the rate of change of the CMV (p.u) with its corresponding number of commutations, the magnitude of the CMV and the %THD in the line voltage. The rate of change of the CMV of higher magnitude will obviously have more adverse effects on the motor windings and bearings (equation 24). It can be clearly observed from Table IV that rate of change of the CMV of higher magnitude has been reduced when an offset is added to the PD modulating technique. Meanwhile, when an off-set signal is added to the POD modulating technique the rate of the change of the CMV of higher magnitude becomes zero. Therefore, the POD with the addition off-set signal technique gives better CMV performance for a 3-levelinverter fed induction motor drive but at the cost of an increased %THD in the line voltage which can be easily mitigated with a properly designed LC filter. On the other hand, the PD SPWM with the off-set signal technique gives better line voltage harmonic performance (reduced lower order harmonic) with sharp edges in the CMV when compared to the PD SPWM.

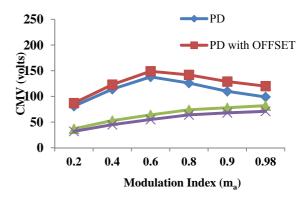

The performance of the system has also been evaluated for different modulation schemes both with and without an offset signal by considering the linear range of the modulation index. The variation of the rms value of the CMV with the modulation index is shown in Fig. 13 with and without an offset signal. It has been observed that the POD with an offset provides a lower rms value of the CMV for the linear

Fig. 9. Common mode voltage with 2-level inverter.

Fig. 10. Common mode voltage with: (a) PD, (b) PD with offset signal, (c) POD, and (d) POD with off-set signal.

Fig. 11. Line voltage without filter  $(V_{ab})$  with (a) PD and (b) PD with off-set signal.

Fig. 12. Line voltage without filter  $(V_{ab})$  with (a) POD and (b) POD with off-set signal.

Fig. 13. Variation of CMV for PD, POD with and without offset considering different values of modulation index.

range of the modulation index as when compared to the conventional modulation schemes i.e. PD and POD.

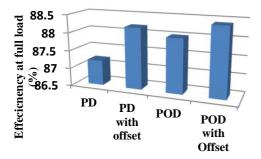

The efficiency of the system decides the relevance of the proposed method used for improved performance.

Therefore, the efficiency has been evaluated for different modulation schemes with and without an offset signal by considering the practical data of the IGBTs ( $R_{on}$ =0.1 ohms) used for experimentation. The effectiveness of the POD with an offset is also observed in terms of the efficiency of the drive system as shown in Fig. 14.

# V. EXPERIMENTAL RESULTS

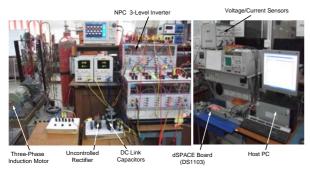

A laboratory prototype has been developed to verify and investigate the control of common mode voltage using the different modulation techniques explain in Section III. The prototype of a NPC 3-level inverter based AC-DC-AC drive system includes twelve STGW30N120KD IGBTs, of 1200 volts, 30 amps rating and six fast recovery diodes (16FM120) with two dc link capacitors of 2200mF, 600 V each at dc link side. The DC supply is obtained through a three-phase, sixpulse uncontrolled diode bridge rectifier. The control algorithm is implemented through the dSPACE real time interface DS1103. The DS1103 real time hardware implementation board is based upon a Texas Instruments TMS320F240, 16 bit fixed point, 250 MHz CPU, 20 MHz clock frequency digital signal processor. Fig. 15 shows the prototype developed in laboratory for experimentation. The parameters used for experiment are given in Table V for the 3-phase squirrel cage induction motor.

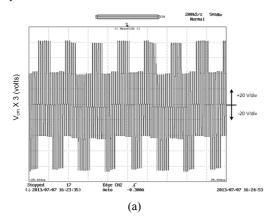

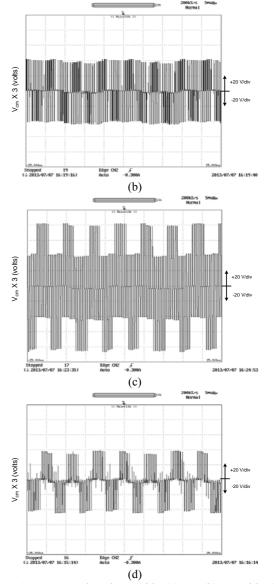

The common mode voltages with the PD, POD, PD with an off-set signal, and POD with an off-set signal techniques are shown in Fig. 16. These experimental results are in agreement with the corresponding simulation results for the effective control of common mode voltage.

The frequency spectrums of the line voltage  $V_{ab}$  with these 3-level SPWM techniques are shown in Fig. 17. The lowest THD contents are obtained with the PD SPWM technique with an off-set signal i.e. 10.1%. The line voltages contain

TABLE IV

COMPARISON OF RATE OF CHANGE OF CMV AND ITS CORRESPONDING NUMBER OF COMMUTATION FOR DIFFERENT 3-LEVEL SPWM

TECHNIQUES

| Modulating<br>Techniques | Rate of change of CMV (in p.u) and its corresponding number of commutation in one cycle |     | RMS Value<br>of                                  | Line<br>Voltage                            | Line<br>Voltage |                                 |                              |

|--------------------------|-----------------------------------------------------------------------------------------|-----|--------------------------------------------------|--------------------------------------------|-----------------|---------------------------------|------------------------------|

| 1 <b>00</b>              | $\lim_{\Delta t \to 0} \frac{\binom{1/2}{2}}{\Delta t} p. \iota$                        |     | $\lim_{\Delta t \to 0} \frac{(1)}{\Delta t} p.u$ | Corresponding<br>number of<br>commutations | CMV<br>(Volts)  | THD<br>Without<br>Filter<br>(%) | THD<br>With<br>Filter<br>(%) |

| PD                       | 80                                                                                      | 120 | 68                                               | 104                                        | 110             | 35.75                           | 0.41                         |

| PD with<br>Off-set       | 42                                                                                      | 126 | 40                                               | 96                                         | 118             | 35.73                           | 0.66                         |

| POD                      | 120                                                                                     | 360 | 40                                               | 60                                         | 78              | 42.59                           | 0.5                          |

| POD with<br>Off-set      | 40                                                                                      | 120 | 0                                                | 0                                          | 68              | 54.61                           | 1.02                         |

Fig. 14. Efficiency (%) at full load for PD, POD with and without offset considering the filter.

Fig. 15. Laboratory prototype of AC-DC-AC induction motor drive system.

Fig. 16. Common mode voltage with: (a) PD, (b) PD with offset signal, (c) POD, and (d) POD with offset signal.

|      | TABLE V             |

|------|---------------------|

| EXPE | RIMENTAL PARAMETERS |

| Line Voltage (RMS)  | $V_{LL}$                          | 60 V    |  |

|---------------------|-----------------------------------|---------|--|

| Source Inductor     | $L_s$                             | 7.73mH  |  |

| AC Link Resistance  | R                                 | 0.4 Ω   |  |

| DC Link Voltage     | $V_{dc}$                          | 80 V    |  |

| DC Link Capacitance | C <sub>1</sub> and C <sub>2</sub> | 2200 μF |  |

| Line Voltage        | 415 V                             |         |  |

| Frequency           | 50 Hz                             |         |  |

| Speed               | 1440 RPM                          |         |  |

| Rated Power         | 1.5 kW                            |         |  |

| Power Factor        | 0.84                              |         |  |

| Carrier Frequency   | 2050 Hz                           |         |  |

(x-axis: time- 5ms/div, y-axis: V<sub>cm</sub> -20 V/div)

Fig. 17. Harmonic spectrums of Line voltages ( $V_{ab}$ ) with: (a) PD, (b) PD with off-set signal, (c) POD, and (d) POD with off-set signal.

increased magnitude of the harmonics around the switching frequency and the THD contents are 34.6% and 47.3% in the POD SPWM and the POD SPWM with an off-set signal, respectively. The comparison of these techniques, as given in Table IV, is also verified experimentally.

# VI. CONCLUSION

This paper explored the opportunities of common mode voltage (CMV) control using simple SPWM techniques for a 3-level diode-clamped inverter. The CMV at the inverter terminal has been obtained with the 3-level PD SPWM and the 3-level POD SPWM techniques and compared that obtained with a 2-level inverter. Further, a method for the reduction of CMV based on the SPWM technique has been derived based on the addition of a variable CMV offset signal

to the original modulating wave. This method can also be applied for a higher number of levels with better performance.

The main contribution of this paper, when compared to [15], is the experimental development of the offset signal addition technique in the SPWM based control of a 3-level inverter for CMV control. The effect of the phase shift between the carriers and the modulating wave on the CMV and the number of commutations per cycle is also investigated. Simulation results show the effectiveness of the CMV control techniques, giving improved performance with a reduction of the magnitude and the number of commutations per cycle in the CMV.

The important conclusion from the obtained results is that the POD SPWM technique with an offset addition gives better CMV performance. It increases the THD in the output line voltage of the inverter. However, the lowest dominant harmonics decreased significantly. The improvement in the efficiency also confirms the results given in Table IV, for a system that has a lower rate of change of the CMV (p.u) with a corresponding number of commutations and a low magnitude of the CMV.

The investigations made in this paper give an idea for the selection of an appropriate modulation technique to control the CMV in AC-DC-AC drive systems for improving the duty life of the bearings of induction motors for critical high performance applications. Further, a technique for SPWM based CMV elimination may be derived. Experimental validation has been obtained and found comparable to simulated results.

### REFERENCES

- [1] S. Chen and T. A. Lipo, "Source of induction motor bearing currents caused by PWM inverters," *IEEE Trans. Energy Convers.*, Vol. 11, No. 1, pp. 25-32, Mar. 1996.

- [2] F. Wang, "Motor shaft voltages and bearing currents and their reduction in multilevel medium-voltage PWM voltagesource-inverter drive applications," *IEEE Trans. Ind. Appl.*, Vol. 36, No.5, pp. 1336-1341, Sep./Oct. 2000.

- [3] C. Klumpner, J.A. Aziz, and J. Clare, "A new buck-type active front end rectifier topology with improved voltage transfer ratio and common mode voltage cancellation," in *Industry Applications Conference*, 2005. Fourtieth IAS Annual Meeting. Conference Record of the 2005, Vol.1,pp.631-638, Oct. 2005.

- [4] J.A. Aziz, C. Klumpner, and J. Clare, "A hybrid approach to improve the robustness against unbalanced voltage supply and cancel the common mode voltage for a 3-ph buck-type rectifier," in *Power Electronics and Motion Control Conference*, 2006. EPE-PEMC 2006. 12th International, pp.653-658, Aug./Sep.2006.

- [5] S. Sedghi, A. Dastfan, and A. Ahmadyfard, "A new multilevel carrier based pulse width modulation method for modular multilevel inverter," in *IEEE 8th International Conference on Power Electronics and ECCE Asia (ICPE & ECCE)*, 2011, pp.1432-1439, May/Jun. 2011.

- [6] A. Videt, P. Moigne, N. Idir, and P. Baudesson, "A new carrier based PWM Providing common mode current

- reduction and DC bus balancing for three-level inverters," *IEEE Trans. Ind. Electron.*, Vol. 54, No. 6, pp. 3001-3011,Dec. 2007.

- [7] J. Rodriguez, J. Pontt, P. Correa, P. Cortes, and S. Cesar, "A new modulation method to reduce common-mode voltages in multilevel inverters," *IEEE Trans. Ind. Electron.*, Vol. 51, No. 4, pp. 834-839, Aug. 2004.

- [8] O. Dordevic, M. Jones, and E. Levi, "A comparison of carrier-based and space vector PWM techniques for threelevel five-phase voltage source inverters," *IEEE Trans. Ind. Informat.*, Vol.9, No.2, pp.609-619, May 2013.

- [9] A. K. Gupta and A. M. Khambadkone, "A space vector modulation scheme to reduce common mode voltage for cascaded multilevel inverters," *IEEE Trans. Power Electron.*, Vol. 22, No.5, pp. 1672-1681, Sep. 2007.

- [10] P. N. Tekwani, R. S. Kanchan, and K. Gopakumar, "A dual five-level inverter-fed induction motor drive with commonmode voltage elimination and dc-link capacitor voltage balancing using only the switching-state redundancy—Part II," *IEEE Trans. Ind. Electron.*, Vol.54, No.5, pp.2600-2608, Oct. 2007.

- [11] C-.C. Hou, C-.C. Shih, P-.T. Cheng, and A. M. Hava, "Common-mode voltage reduction pulse width modulation techniques for three-phase grid-connected converters," *IEEE Trans. Power Electron.*, Vol.28, No.4, pp.1971-1979, Apr. 2013.

- [12] R. S. Kanchan, P. N. Tekwani, and K. Gopakumar, "Three level scheme with common mode voltage elimination and dc link capacitor voltage balancing for an open-end winding induction motor drive," *IEEE Trans. Power Electron.*, Vol. 21, No. 6, pp. 1676-1683, Nov. 2006.

- [13] P. C. Loh, D. G. Holmes, Y. Fukuta, and T. A. Lipo, "A reduced common mode hysteresis current regulation strategy for multilevel inverter," in *IEEE Applied Power Electronics Conf. and Expo.*, 2003, APEC, Vol.1, pp.576-582, Feb. 2003.

- [14] S. Wei, N. Zargari, W. Bin, and S. Rizzo, "Comparison and mitigation of common mode voltage in power converter topologies," in *Conf. Rec. IAS Annual Meeting*, Vol. 3, pp. 1852-1857, Oct. 2004.

- [15] P.K. Chaturvedi, S. Jain, and P. Agarwal, "Carrier-based common mode voltage control techniques in three-level diode-clamped inverter," *Advances in Power Electronics*, Vol. 2012, p.12, Jul. 2012.

- [16] M. R. Mohan and H. M. Survwanshi, "Multilevel inverter to reduce common mode voltage in AC Motor drives using SPWM technique," *Journal of Power Electronics*, Vol. 11, No.1, pp. 21-27, Jan.2011.

- [17] A. Esmaeli and F. Tavassoli, "Suppressing of common-mode voltage, shaft voltage, leakage current and EMI generated by voltage source PWM inverter," *International Electrical Engineering Journal*, Vol. 1, No. 1, pp. 529-535, 2011.

Amit Ojha was born in India, in 1974. He received B.E degree in Electrical Engineering from MACT, Bhopal, India, in 1998. He received M. Tech. and Ph. D. degrees from Maulana Azad National Institute of Technology (MANIT), Bhopal, India, in 2002 and 2013, respectively. He studied multilevel converter fed induction motor

drives while working towards his Ph. D.. He has had more than 14 years of teaching experience and more than 5 years of research experience. He is presently working as an Assistant

Professor in Department of Electrical Engineering, MANIT. His current research interests include electrical machines, power electronics, electric drives, high-power-factor converters, and multilevel converters.

**Pradyumn Chaturvedi** received B.E. degree in Electrical Engineering from Barkatullah University, Bhopal, India, in 1996; M.E. degree in Power Electronics from the Rajiv Gandhi Technical University, Bhopal, India, in 2001; and Ph.D. degree from the National Institute of Technology, Bhopal, India, in 2010. He has had 14 years of teaching

experience. He is presently working as an Assistant Professor in the Department of Electrical and Electronics Engineering, Birla Institute of Technology and Science, Pilani, India. He has published more than 45 research papers in referenced national and international journals and conferences. His current research interests include electrical drives, high-power-factor converters, photovoltaic power conditioning systems, and multilevel inverters.

**Arvind Mittal** obtained B.E. degree in Electrical Engineering from Maulana Azad National Institute of Technology (MANIT), Bhopal, India, in 1991, securing first position in the university (Gold Medallist). He is a post graduated in Power Apparatus and Electrical Drives (PAED) at the Indian Institute of Technology Roorkee, Roorkee,

India, in1993, and obtained Ph.D. degree from Barkatullah University, Bhopal India, in 2002. He is presently an Associate Professor in the Energy Centre, MANIT, Bhopal, India. He has had more than 23 years of experience in teaching undergraduate and postgraduate students. He is a life member of the ISTE and an Associate Member of the Institution of Engineers. He has guided two Ph.D. candidates and published several papers in various national and international conferences and journals. He has also authored seven engineering books.

Shailendra Jain received B. E. degree in Electrical Engineering from Samrat Ashok Technological Institute (SATI), Vidisha, India, in 1990; M.E. degree in Power Electronics from the Shri Govindram Seksaria Institute of Technology and Science, Indore, India, in 1994; Ph.D. degree from the Indian Institute of Technology, Roorkee,

India, in 2003; and Post-Doctoral Fellowship from the University of Western Ontario, London, ON, Canada, in 2007. He is presently a Professor in the Department of Electrical Engineering, National Institute of Technology, Bhopal, India. His current research interests include power electronics and electric drives, power quality improvement, active power filters, high-power-factor converters, and fuel-cell-based distributed generation. Dr. Jain was a recipient of the "Career Award for Young Teachers" from the All India Council for Technical Education (AICTE), New Delhi, India, for the year 2003–2004.