J. Korean Inst. Electr. Electron. Mater. Eng. Vol. 29, No. 3, pp. 181-185 March 2016 DOI: http://dx.doi.org/10.4313/JKEM.2016.29.3.181 ISSN 1226-7945 (Print), 2288-3258 (Online)

# 진공에서 소성 가능한 프릿을 이용한 평판디스플레이 진공실장기술

# 권상직<sup>1</sup>, 유인상<sup>2,a</sup>

1 가천대학교 전자공학과 <sup>2</sup> 가천대학교 화공생명공학과

# Vacuum Sealing Technology of the Flat Panel Display by using the Frit Glass Heatable in Vacuum

Sang Jik Kwon<sup>1</sup> and In Sang Yoo<sup>2,a</sup>

<sup>1</sup> Department of Electronics Engineering, Gachon University, Seongnam 13120, Korea <sup>2</sup> Department of Chemical and Biological Engineering, Gachon University, Seongnam 13120, Korea

(Received February 22, 2016; Revised February 22, 2016; Accepted February 23, 2016)

Abstract: One of the important issues for fabricating the microelectronic display devices such as FED, PDP, and VFD is to obtain a high vacuum level inside the panel. In addition, sustaining the initial high vacuum level permanently is also very important. In the conventional packing technology using a tabulation method, it is not possible to obtain a satisfiable vacuum level for a proper operation. In case of FED, the poor vacuum level results in the increase of operating voltage for electron emission from field emitter tips and an arcing problem, resultantly shortening a life time. Furthermore, the reduction of a sealing process time in the PDP production is very important in respect of commercial product. The most probable method for obtaining the initial high vacuum level inside the space with such a miniature and complex geometry is a vacuum in-line sealing which seals two glass plates within a high vacuum chamber. The critical solution for the vacuum sealing is to develop a frit glass to avoid the bubbling or crack problems during the sealing process at high temperature of about 400°C under the vacuum environment. In this study, the suitable frit power was developed using a mixture of vitreous and crystalline type frit powders, and a vacuum sealed CNT FED with 2 inch diagonal size was fabricated and successfully operated.

Keywords: Vacuum sealing, Frit, FED, PDP

#### 1. 서 론

여러 가지 방식의 평판 디스플레이(flat panel display, FPD)들이 서로 다른 장점과 약점을 소유하고

## a. Corresponding author; isyoo@gachon.ac.kr

Copyright ©2016 KIEEME. All rights reserved. This is an Open-Access article distributed under the terms of the Creative Commons Attribution Non-Commercial License (http://creativecommons.org/licenses/by-nc/3.0) which permits unrestricted non-commercial use, distribution, and reproduction in any medium, provided the original work is properly cited.

있지만 이것들은 모두 몇 가지 공통된 특성을 지니고 있다. 이 공통된 특징의 하나로는 top 혹은 faceplate 에서 bottom glass plate까지 완전한 실장(sealing)을 필요로 한다는 것이다. LCD에 대해서는 sealing 요구 조건이 지나치게 엄격하지는 않고 대략 1/2 기압 정도 이지만, 프라즈마 디스플레이 패널(plasma display panel, PDP)의 경우는 진공이  $10^{-3}$  torr정도 요구되고 전계방출소자(field emission display, FED)의 경우는 10<sup>-6</sup> torr정도가 요구된다. 이와 같이 엄격한 조건이

요구되는 이유는 FPD의 동작방법에 기인하는데, 예를 들면 FEDs는 cathode ray tubes와 다소 유사하게 작 동한다. 부적절한 sealing에 의해 유발되는 진공저하는 여러 가지 문제들을 초래하게 되는데 가장 심각한 것 중의 하나가 display의 불균일한 밝기 현상이다. 이것 은 오염가스들, 특히 형광체 내에 trap되었던 것들이 emitter tip들을 저하시키고 따라서 불균일한 emission 을 유발하는데 기인될 수 있다. 물론 emitter들의 성 능 저하는 display의 수명을 감소시키기도 한다. 또한 PDP의 기존 실장방식의 경우, ITO 및 버스전극을 포 함하는 전면판과 어드레스 전극 및 barrier ribs를 포 함하는 배면판의 유리 기판이 제조된 다음, 450℃이상 의 대기상에서 두 유리판이 frit 실장재에 의해 seal되 고 panel에 부착된 길이 10 cm, 직경 2 mm 정도의 유리 배기관을 통해 가열배기된다. 350℃ 이상의 온도 에서 10시간 이상 동안 가열배기되며 적정 진공도가 확보되면 프라즈마 혼합 가스가 패널로 유입되고 tip-off에 의해 봉입과정이 완료된다.

이와 같이 기존방식은 배기시간이 매우 오래 걸려 제품가격 상승요인이 되며, 고진공도 확보가 어려워 효율저하 및 수명 단축의 심각한 요인이 된다 [1-3]. 대형 고화질 HDTV에 해당하는 PDP나 FED와 같이, 미세 공간영역 및 복잡한 기하학적 구조를 갖는 평판디스플레이 패널 내부 초기 진공을 고진공 상태로 확보할 수 있는 가장 확실한 방법으로 두 장의 유리기판을 진공 챔버 내부에서 실장시키는 '진공 인-라인 실장 (vacuum in-line sealing)' 방법이다 [4,5]. 본 연구에서는 이와 같은 진공 실장기술을 개발하고, 그 응용결과를 소개한다.

#### 2. 실험 방법

## 2.1 진공에서 소성 가능한 프릿(frit) 페이스트 제조

일반적인 실장재료인 프릿을 사용하여 진공상태에서 소성할 경우 leak의 요인이 되는 버블(bubbles)이 심하게 발생한다. 본 연구에서는 ~10<sup>-6</sup> torr범위의 진공중에서도 400℃에서 소성시 bubble들이 거의 발생하지 않는 프릿 재료를 개발하고 가열공정기술을 개발하였다. 즉, 진공 상태에서 프릿재료를 고온 소성시 bubbles와 crack이 발생하지 않도록 하기 위해 가소성 프릿 파우다(vitreous type, SCB4)와 경화성 프릿파우다(crystalline type, SCC1)의 프릿을 적정 비율

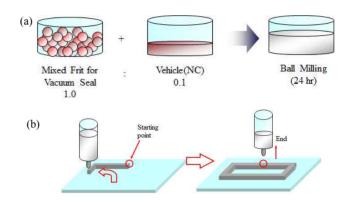

**Fig. 1.** The method of the frit paste for the vacuum sealing. (a) Ball milling, (b) dispensing.

**Table 1.** Component ratio analyzed by ICP-MS for three frits including the developed frit for vacuum sealing.

| Contents<br>Firt Type | PbO  | ZnO  | $B_2O_3$ | SiO <sub>2</sub> | SnO <sub>2</sub> | ВаО  |

|-----------------------|------|------|----------|------------------|------------------|------|

| V-type                | 89.1 | 0.05 | 9.2      | 1.4              | 0.04             | 0.01 |

| C-type                | 72.2 | 15   | 9.8      | 1.9              | 0.9              | 0.1  |

| Vacuum<br>type        | 80.6 | 7.5  | 9.5      | 1.7              | 0.5              | 0.05 |

(60:40)로 섞은 다음, 바인더 및 용제와 혼합하여 페이스트를 만든다. 이때, 경화성 파우다(C-type)의 구성성분을 ICP-MS(inductively coupled plasma mass spectrometer)로 분석한 결과, PbO = 72.26, ZnO = 15.06, SiO<sub>2</sub> = 1.90, B<sub>2</sub>O<sub>3</sub> = 9.83, BaO = 0.08, SnO<sub>2</sub> = 0.87의 wt%로 구성되어 있으며, 가소성 파우다(V-type)는 PbO = 89.15, ZnO = 0.04, SiO<sub>2</sub> = 1.40, B<sub>2</sub>O<sub>3</sub> = 9.16, BaO = 0.01, Fe<sub>2</sub>O<sub>3</sub> = 0.19, SnO<sub>2</sub> = 0.04의 wt%로 구성되어 있는데, 이 두 가지 종류의 프릿 파우더를 40:60에서 60:40 비율로 혼합하였다. 혼합된 프릿 파우다(M-type)의 조성비는 대략 PbO = 78~84, ZnO = 5.0~10.0, SiO<sub>2</sub> = 1.50~1.80, B<sub>2</sub>O<sub>3</sub> = 9.0~10.0, BaO = 0.03~0.06, Fe<sub>2</sub>O<sub>3</sub> = 0.07~0.12, SnO<sub>2</sub> = 0.30~0.60wt%의 범위를 갖는다.

표 1에 ICP-MS를 통해 분석된 프릿 종류별 성분비교 결과가 나타나 있다. 다음 공정으로 프릿 페이스트를 제조하기 위해서는, 프릿 파우다와 vehicle(NC와 BCA가 혼합된 용제)를 6:1에서 12:1 정도의 중량비로혼합하여 ball miller로 수시간 이상 milling시켜 고르게 혼합한다. 혼합된 프릿 페이스트를 dispenser(실린더류)를 이용해 유리판의 가장자리를 따라 도포시킨다. 그림 1은 이와 같은 페이스트의 제조 및 디스펜싱

과정의 설명을 보여주는 그림이다. 마지막으로, 페이스트에 함유되어 있는 솔벤트류를 태워 없애기 위해 도포된유리기판을 전기로 속에서 소성 시키는데, 승온 속도는 4℃/min로 하며, 도달 온도는 380 ~ 400℃이상에서 1시간 가량 진행하였고, 다시 상온까지의 하강속도를 -4℃/min로 하였다.

## 2.2 진공 실장 장치를 이용한 실장 테스트

한쪽 유리기판에 가소(pre-baked)된 프릿을 적용하여 두 장의 유리기판을 진공 챔버 내에서 실장하기 위해서는, 프릿이 형성된 유리 기판과 합착될 유리 기판을 진공 챔버 내로 이송 시킨다. 두 장의 유리기판을 실장 시키기 위해서는 다시, pre-formed 프릿을 녹여야 하는데 이를 위해 유리 기판들을 가열하기 위한 열원의 온도를 상승시킨다. 이때 승온속도는 3-5℃/min정도, 최종 도달 온도는 280℃에서 300℃ 정도이다. 소성 온도에서 진공도가10-6 torr범위로 다시 회복될 때까지 기다린다. 상판 혹은 하판을 수직으로 이동시켜 두 장의 유리판을 실장 시키는데, 충분한 실장을 위해 약간의 압력(press)을 가한다. 그런 다음 온도를 승하 시킨다. 승하속도는 -3℃에서 -5℃ 범위로 한다.

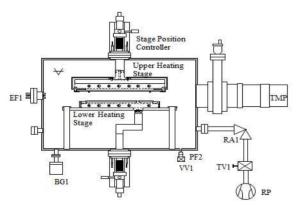

그림 2는 앞에서와 같은 방법으로 제조된 프릿을 이용하여 두 장의 유리기판을 진공 챔버 내에서 실장시키기위해 제작된 실장 장치의 구성도이다. 앞에서 제조된 진공용 프릿 페이스트를 사용하여 제작된 진공 실장장치를 통해 두 장의 유리 기판을 실장하였다.

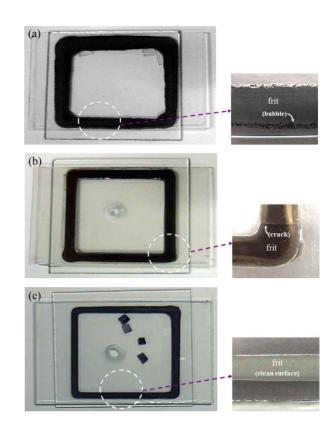

그림 3은 기존의 가소성 프릿과 경화성 프릿을 이용하여 두 장의 유리기판을 실장한 패널과 본 연구에서 개발한 프릿을 사용하여 실장한 패널의 결과를 비교하여 보여주는 카메라 사진(왼쪽 큰 그림)과 전자현미경(오른쪽 작은 그림) 사진들이다. 그림 3(a)에서 보여주는 바와 같이, 가소성 타입(V-type)의 프릿을 사용한

Fig. 2. Configuration of the vacuum sealing system.

**Fig. 3.** Comparisons among the vacuum sealed panels using (a) V-type frit, (b) C-type frit, and (c) the developed frit.

경우는 진공 분위기에서 380℃이상 가열시 심한 버블링이 생기고 그림 3(b)에서와 같이 경화성 타입(C-type)의 프릿을 사용한 경우는 버블링은 발생하지 않으나 crack이 발생함으로 인하여 두 경우 모두 패널실장에 적용하면 leak에 의해 진공이 깨어진다. 반면에, 본 연구에서 개발한 진공용 프릿을 사용하면 그림 3(c)에서와 같이 버블이나 crack이 발생하지 않고 치밀하게 실링된 단면을 보여준다.

#### 3. 결과 및 고찰

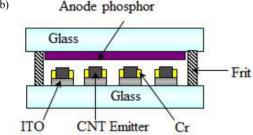

앞에서 개발된 진공용 프릿을 적용하여 실제 패널에 적용하였을 경우 패널 내부가 정상적으로 진공이 유지되는지 확인하기 위하여 2인치 대각선 크기의 카본 나노튜브(carbon nano tube, CNT) 전계방출 에미터를 제작하여 실장 후 전계방출 특성을 측정하여 보았다. 먼저, ITO 전극이 코팅된 소다라임 유리 기판 상에 감광성 CNP 페이스트를 이용하여 CNT 에미터 패턴들을

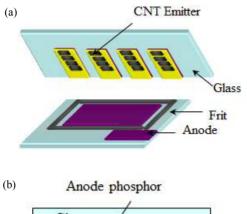

**Fig. 4.** CNT FED panels (a) before sealing and (b) after vacuum sealing.

형성하였다. 전계방출을 균일하게 유도하기 위해 하나의 에미터 픽셀크기는 250×250 mm²로 하였고 하나의 픽셀 안에 CNT 페이스트 dots는 정사각형 모양으로 50×50 mm²로 9개씩 구성되어 있다. 아노드로 사용될다른 유리 기판에는 백색 형광체를 2인치 크기로 도포하여 형성하였다. 형광체가 도포된 어노드(anode) 유리 기판 둘레에 프릿 페이스트를 디스펜싱하고 가소(pre-baking)하여 고상형(solid) 프릿 테두리를 형성한다음 두 장의 유리 기판을 진공 챔버에 장착하여 앞에서 언급된 순서데로 진공실장을 진행하였다. 진공 실장시 챔버 내부 진공도는 10<sup>-6</sup> torr를 확보하였으며, 실장을 위해 기판 온도를 400℃ 까지 상승시키는 동안아웃개싱(outgassing) 등에 의해 챔버 압력도 1×10<sup>-5</sup> torr까지 상승하였다.

그림 4는 CNT FED 패널을 실장하기 전에 구성되는 두 장의 유리기판(아노드 기판, CNT 에미터 기판)과 진공 실장 후의 패널 단면구조를 보여주는 그림이다.

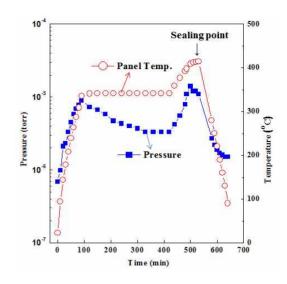

그림 5는 진공 챔버 내에서 두 장의 CNT FED 상, 하 기판을 장착하여 아래 측 어노드 기판 상에 미리 소성된 프릿을 가열시켜 합착 실장하는 동안 온도 변화에 따른 챔버내 진공도의 변화를 보여주는 그래프이다. 이를 통해 실장된 패널 내부의 진공도는 대략  $1\times10^{-5}$  torr정도 확보되었을 것으로 추측된다.

**Fig. 5.** Variance of the pressure depending on the temperature exerted on the panel for vacuum sealing.

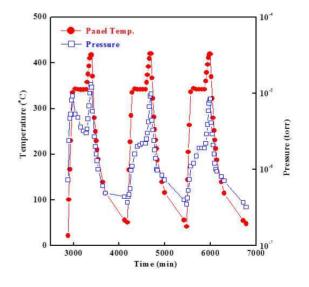

**Fig. 6.** Panel temperature and chamber pressure cycles with the temperature variance by the heater.

그림 5에서 보여진 진공도는 실장을 위해 필요한 소성온도를 인가하였을 때 챔버나 패널을 구성하는 요소들(프릿, CNT, 형광체 등)로 부터의 아웃 개싱(outgassing)에 의한 것이다 [6,7]. 이를 확인하기 위해 외부에서 인가하는 가열 히터의 온도를 의도적으로 변화시켜가며 그에 따른 챔버 내부 진공도 변화를 살펴 보았다. 그 결과 그림 6에서 보여지는 바와 같이, 챔버내부 진공도는 처음 온도가 인가되지 않았을 때

1×10<sup>-6</sup> torr 이하까지 확보 되었지만 온도가 올라가면 챔버 압력도 올라가고 온도를 다시 떨어뜨리면 압력도 다시 낮아지며 진공도가 좋아지는 양상이 반복되는 것을 볼 수 있었다. 따라서, 실장 순간에 최고의 진공도를 확보하기 위해서는 챔버로 부터 아웃개싱이 발생하지 않도록 로드 록(load-lock) 챔버를 구성하는 것이 필요하며, 또한 실장용 메인 챔버에서 최종 실장 시점의 소성 온도(대략 400℃ 근처)가 인가되었을 때, 패널로 부터 아웃개싱이 충분히 이루어질 때 까지 두 유리기판 사이를 일정 간격 유지시킨 상태에서 시간을 유지시키는 것이 필요할 것이다. 이와 같이 진공 실장된 CNT FED 패널이 정상적으로 진공을 유지하는지를 확인하기 위하여 어노드 구조를 갖는 FED 패널에 대한전류-전압 특성을 측정하였다.

그 결과, 그림 7에서 보여주는 바와 같이 진공 내에서의 전형적인 전계방출 특성인 다이오드 전류-전압특성을 보여 주었으며 이 데이터를 통해 '(1/V) 대비  $\log(I/V^2)$ '에 의한 Fowler-Nordheim 그래프를 확인한결과 직성성을 나타내었는데, 이는 아노드와 에미터 간에 누설전류가 전혀 없다는 것을 보여 주는 것으로서 진공이 완전히 유지되고 있음을 말해 준다.

본 실험에서는 연구용 장비로 로드 록 챔버가 구성되지 않았기 때문에, 실장 시점에서의 아웃개싱을 충분히 확보하기 위한 작업만을 적용한 것을 감안하면 실제 상황에서는 이 보다 높은 진공도를 확보할 수 있을 것으로 기대된다.

**Fig. 7.** I-V characteristics of the vacuum sealed CNT FED panel with 2 inch diagonal.

#### 4. 결 론

본 연구는 FED나 PDP에 적용 가능한 진공실장 기술을 개발하였다. 진공실장 기술에서 가장 중요한 진공용 프릿을 제조하였는데, 기존의 가소성 프릿과 열경화성 프릿을 적정 비율로 혼합하여 프릿 페이스트를 제조한 결과,  $10^{-5}$  torr의 고진공 하에서  $400^{\circ}$ C 이상 온도로 소성 시 기존 프릿에서와 같은 버블이나 균열이전혀 발생하지 않고 치밀하게 실장된 결과를 확인할수 있었다. 이렇게 개발된 프릿을 이용하여 실제 2인치 대각선 크기의 CNT FED 패널을 진공 실장한 결과정상적으로 동작하였다. 이는 실장된 패널 내부의 진공도가  $10^{-6}$  torr내외의 고진공 상태가 잘 유지되고 있음을 확인시켜 준다.

#### 감사의 글

본 논문은 산업통상자원부 산업전문인력 역량강화사업 (N0001415, 디스플레이 장비부품 전문인력양성사업)으로 지원되었습니다.

#### **REFERENCES**

- [1] J. A. Castellano, Solid State Tech. 41, 67 (1998).

- [2] B. R. Chalamala, Y. Wei, and B. E. Gnade, *IEEE Spectrum*, **35**, 42 (1998). [DOI: http://dx.doi.org/10.1109/6.666960]

- [3] Roth A., Vacuum technology, Ch., 7, 329 (1978).

- [4] T. Yano, K. Uchida, G. Uchida, T. Shinoda and H. kajiyama, J. of the vacuum society of japan, 55, 125 (2012).

- [5] D. J. Lee, S. I. Moon, Y. H. Lee, J. E. Yoo, J. H. Park, J. Jang, and B. K. Ju, *Vacuum*, **74**, 105 (2004). [DOI: http://dx.doi.org/10.1016/j.vacuum.2003.12.137]

- [6] C. Boffito and E. Sartorio, Vacum Technik, 35, 212 (1986).

- [7] C. W. Oh, C. G. Lee, B. G. Park, J. D. Lee, and J. H. Lee, J. Vac. Sci. Technol. B., 16, 807 (1998).

[DOI: http://dx.doi.org/10.1116/1.589910]