# 위상 샘플방식 DRFM에 적용 가능한 VGPO/I 재밍기법 기술 구현

# Development of VGPO/I Jamming Technique for Phase Sampled DRFM

최영익 · 홍상근 · 이왕용 · 박진태\* · 이창훈\*

Young-Ik Choi · Sang-Guen Hong · Wang-Yong Lee · Jin-tae Park\* · Chang-hoon Lee\*

요 약

현대전에서는 각종 추적 레이다를 이용하여 표적의 위치 추적이 이루어진다. 따라서 적군 레이다를 교란하여 아군 위치 정보 추적을 무력화하는 전자공격인 레이다 재밍 기술의 중요성이 증가하고 있다. 레이다 재밍 기법 중 VGPO/I는 전자전 레이다 재밍 기법의 기본이 되는 기법 중 하나이며, 주로 신호의 펄스 도플러 효과를 이용하여 위치를 추적하는 레이다 대상 재밍 기법 운용이 가능하다. 본 논문은 위상 샘플방식으로 운용되는 DRFM에 적용할 수 있는 위상정보를 이용한 VGPO/I 재밍 기법 기술구현방식을 제안하고, 시뮬레이션을 통해 검증하였다.

#### **Abstract**

In modern warfare, various target tracking radars are used for target location tracking. So, the importance of EA radar jamming technique which disrupt enemy target tracking radar in oder to neutralize tararget location tracking has increased. VGPO/I jamming is a base technique of EA(Electronic Attack), it is possible to operate to pulse-Doppler radar. In this papar, we develop VGPO/I jamming technique that can apply to phase sampled DRFM by using phase information and verifity through simulations.

Key words: Radar Jamming, VGPO/I, Digital Radio Frequency Memory, Electronic Warfare, Electronic Attack

# Ⅰ. 서 론

현대전에서는 각종 추적 레이다를 이용하여 표적의 위치 추적이 이루어진다. 따라서 적 레이다에 아군표적이 추적당하지 않도록 하기 위해 재명 신호를 이용하여 적레이다의 교란을 시도한다. 재명의 기본원리는 레이다에서 표적 추적요소인 거리, 속도 및 각도 정보를 얻지 못하도록 하거나, 오차를 유발하도록 기법변조된 재명 신호를 방사하는 것이다. 재명 신호를 생성하는 소스원은 여러종류가 있으며, DRFM(Digital Radio Frequency Memory)은 Radar 재명에 사용되는 소스원 중하나이다.

DRFM은 입력된 신호를 메모리에 저장하였다가 필요한 시점에 저장된 신호를 복원하여 출력하는 장치이다. 저장된 신호를 복원하여 출력할 때 시간 지연을 통해 RG-PO/I(Range Gate Pull Off/In), 주파수 천이를 이용하여 VGPO/I(Velociy Gate Pull Off/In), 잡음발생을 이용하여 잡음 재밍, CP(Cover Pulse) 등의 기법 변조된 재밍 신호를 방사하여 적 레이다를 교란한다.

입력 신호를 ADC로 샘플링한 후, 진폭 데이터 대신 I 신호(In phase)와 Q 신호(Quadrature phase)로부터 위상 값 을 찾아 저장하는 방식의 DRFM이 위상 샘플방식 DRFM 이다<sup>[1]</sup>

<sup>(</sup>주)LIG넥스원(LIG Nex1 Co., Ltd)

<sup>\*</sup>국방과학연구소(ADD)

<sup>·</sup> Manuscript received September 28, 2016; Revised November 22, 2016; Accepted November 24, 2016. (ID No. 20160928-102)

<sup>·</sup> Corresponding Author: Young-Ik Choi (e-mail: youngik.choi@lignex1.com)

본 논문에서는 위상 샘플방식의 DRFM에 적용할 수 있 도록 위상성분의 산술연산을 통해 1개의 기법변조 소스 원으로 2개의 재밍신호를 방사하는 VGPO/I 재밍 기법 발 생이 가능한 기법 기술 구현 방안을 제시한다.

## Ⅱ. 본 론

#### 2-1 속도기만(Velocity Deception) 개요

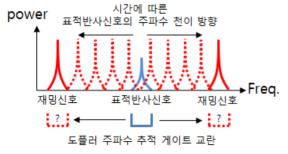

속도기만 재명이란 펄스 도플러 효과를 이용하여 추적하는 레이다 신호에 의한 표적 반사 신호의 주파수를 점차적으로 증가 또는 감소시켜 고출력으로 재명하여 레이다의 추적 게이트를 교란하거나, 재명 신호를 추적하도록유도시켜 실제 표적의 도플러 효과 추적을 차단시키는 재명 기법이다<sup>[2]</sup>. 표적 반사 신호 주파수의 증/감 형태에따라 VGPO(Velocity Gate Pull Off), VGPI(Velocity Gate Pull In), VGPO/I(Velocity Gate Pull Off), 모른 된다. 예시로 VGPO/I 기법에 대한 개념 및 형상은 그림 1과 같다. 시간에 따른 좌/우로 동일한 양의 표적반사신호의 주파수 천이 변조를 통해 도플러 주파수 추적 게이트의 이동을 교란시켜, 실제 타겟의 속도정보 추적을 무력화 또는 기만하는 효과를 줄 수 있다.

## 2-2 위상샘플 DRFM 개요

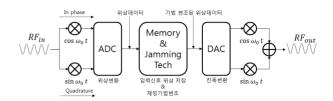

위상 샘플방식 DRFM은 입력된 RF 신호의 위상 값을 저장하며, 필요한 시점에 저장된 위상데이터를 재밍 기법에 따라 가공하여 출력하는 재밍 소스원이다<sup>[1],[3]</sup>.

위상 샘플방식 DRFM은 입력 RF 신호를 I 신호와 Q 신호로 변환한 후, 고속 ADC를 이용하여 고속 샘플링을 한

그림 1. VGPO/I 재밍 기법 개념

Fig. 1. Concept of VGPO/I jamming technique.

그림 2. 위상샘플 DRFM 구조

Fig. 2. Structure of phase sampled DRFM.

후에 위상 데이터를 산출하여 메모리에 저장한다<sup>[4]</sup>. 해당 위상데이터를 추출하기 위해 동기화된 2채널의 ADC 모듈에서 입력신호를 I(In-Phase) 채널과 Q(Quadrature) 채널로 분리하여 각각 샘플링한 후, 아래와 같은 식 (1)에 의해서 위상데이터를 추출하게 된다.

$$\theta(t) = \tan^{-1} \left( \frac{Q(t)}{I(t)} \right) \tag{1}$$

입력신호의 위상 데이터와 기법 변조 된 위상 데이터의 산술연산을 통해 재밍 신호의 위상 데이터를 생성하며, 고속 DAC를 이용하여 재밍 신호의 위상 데이터를 진폭데이터로 변환하여 가공된 재밍 신호를 출력한다. 기본 구성은 그림 2와 같다.

위상 샘플링 방식 DRFM은 저장된 데이터가 위상 값이며, 신호를 출력하는 고속 DAC 모듈 전단까지 위상정보만을 이용하므로, VGP 계열 재명 신호를 생성함에 있어서도 위상 값만을 이용한다<sup>[1]</sup>.

# 2-3 위상정보를 이용한 VGP(Velocity Gate Pull) 계열 재밍기법 생성

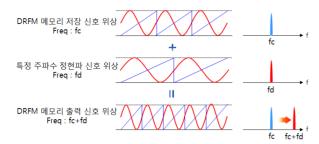

일반적으로 신호의 위상성분은 주파수와 비례하는 관계를 가지고 있다. 따라서 서로 다른 위상 값의 산술연산은 각 위상 값이 나타내는 주파수들을 더하는 것과 같다.

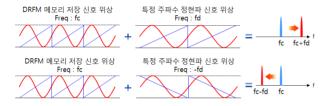

그림 3과 같이 DRFM의 메모리에 저장된 입력 신호의 위상 값과 특정 주파수를 가지는 정현파 신호의 위상 값을 산술 연산할 경우 DRFM 메모리에 저장된 해당 입력 신호를 특정 주파수만큼 천이시키는 효과를 발생할 수 있다. 또한, 그림 4와 같이 특정 주파수를 가지는 정현파신호 위상 값의 상, 하향 모양에 따라서 DRFM 메모리에 저장된 입력 신호 주파수 대비 특정 천이 주파수만큼 상/하향으로 입력 신호를 주파수 천이시킬 수 있다.

그림 3. 주파수 천이 예시

Fig. 3. Example of frequency shift.

그림 4. 주파수 천이 예시(상/하향)

Fig. 4. Example of frequency shift when up/down phase.

위에서 설명한 원리를 활용하면, DRFM 메모리에 저장된 입력 신호의 위상 값과 주파수가 점차적으로 증가하는 정현파 신호의 위상 값을 산술연산하게 되면 표적 반사 신호의 주파수가 점차적으로 증가하게 되는 VGPO (Velocity Gate Pull Off) 재밍 기법 신호가 생성되며, 반대로 주파수가 점차적으로 감소하는 정현파 신호의 위상 값과의 산술연산을 하게 되면 표적 반사 신호의 주파수가 점차적으로 감소하게 되는 VGPI(Velocity Gate Pull In) 재밍 기법 신호를 생성할 수 있다.

VGPO 재밍 기법의 경우에는 추적레이다에게 추적 당하는 표적의 속도가 점점 빨라지는 효과를 줄 수 있으며, 반대로 VGPOI 재밍 기법은 추적 당하는 표적의 속도가 점점 느려지는 효과를 줄 수 있다.

# 2-4 위상정보를 이용한 VGPO/I(Velocity Gate Pull Off/In) 재밍기법 생성 방안

VGPO/I(Velocity Gate Pull Off/In)는 위에서 설명한 VG-PO(Velocity Gate Pull Off)와 VGPI(Velocity Gate Pull In) 를 동시에 수행하는 재밍기법이다. 즉, 그림 1과 같이 표적 반사 신호 주파수 기준 양옆으로 도플러 처이 주파수

가 동시에 점점 증가하거나 감소하는 2개의 재밍 신호를 송신하여 레이다의 추적게이트를 교란한다.

기존 DRFM의 VGPO/I 기법 구현 방식은 기법변조하기 위한 정현파 신호 주파수의 상/하향 위상 데이터를 DR-FM 메모리에 저장된 입력신호의 위상과 고속으로 교번 하여 더해주는 방식이었기 때문에, 한순간에 1개의 재밍신호가 출력될 수 있는 기법 변조 소스원이 생성되는 구조였다. 이는, 시간측면에서 한순간에 1개의 재밍신호만출력하게 되므로 만약 대상 레이다의 PRI(Pulse Repetition Interval)가 위상데이터를 교변하여 더해주는 시간보다 빠른 경우, 시간에 따른 좌/우로 동일한 양의 도플러주파수 변조를 할 수 없기 때문에 대상 레이다의 도플러주파수 추적 게이트 교란효과가 떨어진다.

본 논문에서는 위와 같은 문제점을 해결하고자 천이하고자하는 주파수 2개를 가지는 정현파들의 합성된 위상데이터와 DRFM 메모리에 저장된 입력 신호의 위상데이터와의 산술 연산을 통해 1개의 기법 변조 소스원으로 동시에 2개의 주파수가 서로 다른 재밍 신호를 생성할 수있는 방식을 제안한다.

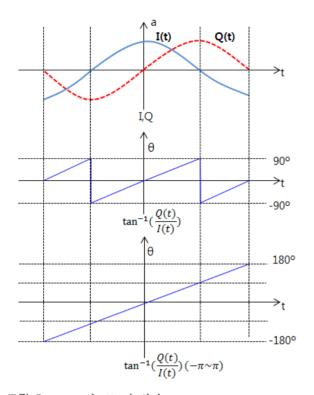

우선, 일반적으로 위상 샘플방식 DRFM 내부에서 처리하는 I/Q 및 위상데이터는 그림 5와 같이 표현된다. I/Q데이터를 이용하여 식 (1)에 의해서 위상 값을 구하고, 식 (2)의 조건식을 적용하여 해당 위상 값 범위를  $-\pi \sim \pi$ 로 변경한다.

①

$$I(t) \ge 0$$

이면,  $\theta(t) = \tan^{-1} \left( \frac{Q(t)}{I(t)} \right)$

②  $I(t) < 0$  &  $\tan^{-1} \left( \frac{Q(t)}{I(t)} \right) > 0$  이면,

$$\theta(t) = \tan^{-1} \left( \frac{Q(t)}{I(t)} \right) - 180$$

③  $I(t) < 0$  &  $\tan^{-1} \left( \frac{Q(t)}{I(t)} \right) \le 0$  이면,

$$\theta(t) = \tan^{-1} \left( \frac{Q(t)}{I(t)} \right) + 180$$

② (2)

다음으로는 DRFM 메모리에 저장된 입력 신호 위상 값과 산술연산 할 천이하고자 하는 주파수 2개를 가지는 정현파들의 합성된 위상에 대해 서술한다. 식 (3), (4)는 주파수가 서로 다른 2개 신호의 I/Q에 대한 복소수 표현 및

그림 5. DRFM의 I/Q 및 위상

Fig. 5. In-phase, quadrature and phase of DRFM.

위상에 대한 정의다.

$$S_1(t) = \cos\theta_1(t) + j\sin\theta_1(t)$$

$$S_2(t) = \cos\theta_2(t) + j\sin\theta_2(t)$$

(3)

이 두 신호의 합은 식 (4)로 표현된다.

$$\begin{split} S_s\left(t\right) &= S_1(t) + S_2(t) \\ &= \cos\theta_1(t) + \cos\theta_2(t) + j\sin\theta_1(t) + j\sin\theta_2(t) \\ &= 2\cos\left(\frac{\theta_1(t) + \theta_2(t)}{2}\right)\cos\left(\frac{\theta_1(t) - \theta_2(t)}{2}\right) \\ &+ j\left(2\sin\left(\frac{\theta_1(t) + \theta_2(t)}{2}\right)\cos\left(\frac{\theta_1(t) - \theta_2(t)}{2}\right)\right) \\ &= I_s(t) + jQ_s(t) \\ \theta_s(t) &= \tan^{-1}\!\left(\frac{Q_s(t)}{I_s(t)}\right) \! = \frac{\theta_1(t) + \theta_2(t)}{2} \end{split} \tag{4}$$

천이하고자 하는 2개의 주파수는 DRFM 메모리에 저장된 입력 신호 주파수 기준으로 양쪽 대칭으로 한정하면, 식 (3), (4)는 식 (5), (6)으로 표현될 수 있다.

$$\begin{aligned} \theta_{2}(t) &= -\theta_{1}(t) \\ S_{1}(t) &= \cos\theta_{1}(t) + j\sin\theta_{1}(t) \\ S_{2}(t) &= \cos\theta_{2}(t) + j\sin\theta_{2}(t) \\ &= \cos\theta_{1}(t) - j\sin\theta_{1}(t) \end{aligned} \tag{5}$$

$$\begin{aligned} S_{s}(t) &= S_{1}(t) + S_{2}(t) \\ &= \cos\theta_{1}(t) + \cos\theta_{1}(t) + j\sin\theta_{1}(t) - j\sin\theta_{1}(t) \\ &= 2\cos\theta_{1}(t) + j0 \\ &= I_{s}(t) + jQ_{s}(t) \\ \theta_{s}(t) &= \tan^{-1}\left(\frac{Q_{s}(t)}{I_{s}(t)}\right) = 0 \end{aligned} \tag{6}$$

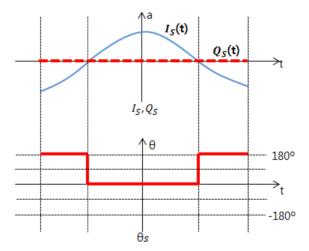

식 (6)에서 구한  $I_s(t)$ ,  $Q_s(t)$ ,  $\theta_s(t)$ 를 식 (2)의 조건식을 반영하여 VGPO/I 기법 변조 소스원의 위상 값을 구하면 그림 6과 같이 표현할 수 있다.

결과적으로 VGPO/I 재밍을 위한 위상 샘플방식 DRFM의 기법변조 소스원인  $\theta_s(t)$ 는 0°와 180°를 교변하는 구형파 형태가 될 것이다. 이 구형파의 주기는 천이시킬 주파수와 비례한다. 따라서 해당 기법 변조 위상데이터를 점점 주기가 짧아지는 구형파 형태로 생성한 뒤, 입력 신호의 위상 값과 산술연산을 취하여 최종 DRFM 출력 위상 데이터를 생성하고, 이 데이터를 DAC를 통해 진폭으로 변환, 동기화된 I/Q 데이터를 생성한 후, RF 재밍 신호를 송신하게 되면 표적 반사 신호 주파수 기준 양옆으로

그림 6. DRFM의 VGPO/I 기법변조 I/Q 및 위상 표현 Fig. 6. In-phase, quadrature and phase for VGPO/I.

그림 7. DRFM의 입력신호 I/Q 및 위상

Fig. 7. In-phase, quadrature and phase of DRFM input signal.

주파수가 동시에 점점 증가하거나 감소하는 재밍 신호를 송신하는 VGPO/I 재밍 기법이 가능하다.

그림 8. VGPO/I 기법변조 신호 I/Q 및 위상

Fig. 8. In-phase, quadrature and phase of VGPO/I tech signal.

# 2-5 위상정보를 이용한 VGPO/I(Velocity Gate Pull Off/In) 재밍기법 시뮬레이션 결과

위상정보를 이용한 VGPO/I 재밍기법 구현 방안을 검증하기 위하여 Matlab을 이용한 시뮬레이션을 수행하였다.

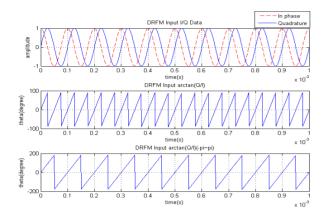

그림 7은 DRFM 메모리에 저장된 입력 신호의 I/Q 및 위상 데이터에 대한 표현이다. 첫 번째 그림은 입력 I/Q 데이터에 대한 표현이며, 두 번째 그림은 식 (1)의 수식에 따른 입력 I/Q 데이터에 대한 위상변환 값 $(-\pi/2 \sim \pi/2)$ 을 나타낸 것이다. 마지막으로 세 번째 그림은 식 (2)의 조건식에 따라 해당 위상변환 값의 범위를  $-\pi \sim \pi$ 로 변경하여 처리한 위상 데이터이다. 해당 신호의 주파수는 10~kHz로 정의했다.

다음으로 그림 8은 식 (5), (6)을 이용하여 VGPO/I 재밍을 위한 기법변조신호의 I/Q 및 위상데이터이다. 식 (2), (6)에 의해서 생성된 최종 기법변조 위상데이터는 0°와

O.5 1 time(s) x 10<sup>-4</sup>

O.5 1 time(s) 1.5 2 2.5

VGPO/I Jamming Tech DRFM Output I/Q x 10<sup>-4</sup>

O.5 1 time(s) 1.5 2 2.5

x 10<sup>-4</sup>

그림 9. DRFM 재밍 출력신호 I/Q 및 위상

Fig. 9. In-phase, quadrature and phase of DRFM output signal.

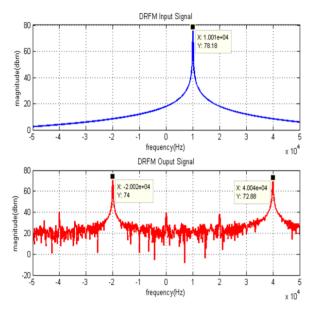

그림 10. DRFM 입력, 최종 출력 신호 Fig. 10. DRFM input, output signal.

180°를 교번하는 구형파 형태로 생성됨을 볼 수 있다. 천 이 주파수는 +/- 30 kHz로 정의했다.

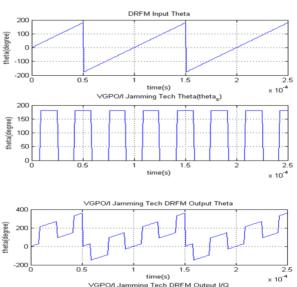

마지막으로 DRFM 입력 신호 위상 데이터와 기법변조 신호의 위상 데이터와의 산술연산한 최종 DRFM 출력 신호에 대한 표현은 그림 9와 같다.

또한, DRFM 최종 출력신호를 주파수 상에서 표현하면 그림 10과 같이 입력 신호 주파수 대비 +/- 30 kHz로 주파수 천이된 2개의 재밍 신호가 생성됨을 볼 수있다.

### Ⅲ. 결 론

본 논문에서는 위상 샘플방식의 DRFM에 적용하기 위하여 위상 정보를 이용한 VGPO/I 재밍 기법 구현방안을 제시하고 시뮬레이션을 통해 검증하였다.

기존 DRFM의 VGPO/I 기법의 경우, 해당 재명신호의도플러 천이 주파수의 상/하향 위상데이터를 고속으로 스위칭하는 방식으로 구현되었다. 이는 한순간에 서로 다른주파수를 가지는 2개의 재명 신호를 발생할 수 없으므로시간측면에서의 재명 효율이 떨어지는 문제점을 가지고있었다. 하지만 본 논문에서 제안한 방법은 기존 방식보다는 비교적 간편한 구현이 가능하며, 1개의 기법변조 소스원으로 2개의 재명 신호를 동시에 생성 및 출력할 수있는 점에서 기존의 VGPO/I의 문제점을 해결할 수 있으며, 다른 재명기법(RVGPO/I, VFT 등)에 적용이 가능하다는 장점을 가진다.

#### References

- [1] 홍상근, 이왕용, 류정호, 신욱현, "위상 샘플링 방식 DRFM 적용 대역폭 제어 잡음 재밍 기법 개발", 한국 전자파학회논문지, pp. 776-783, 2011년 8월.

- [2] 이일근, 레이다 공학과 전자전 응용, 대영사, 2006년

- [3] Philip E, Pace, Advanced Techniques for Digital Receivers, Artech House, 2000.

- [4] 유병석, "디지털 고주파 메모리 구현에 관한 연구", 한 국해양정보통신학회논문지, 14(9), pp. 2164-2170, 2010년.

최 영 익

2013년 2월: 세종대학교 정보통신공학과 (공학사)

2012년 12월~현재: LIG넥스원 전자전연 구센터 선임연구원

[주 관심분야] 전자전 EA 시스템, 디지털 신호처리, 신호분석 알고리즘 홍 상 근

2004년 2월: 고려대학교 전자공학과 (공학 사)

2010년 5월: 성균관대학교 전자공학과 (공 학석사)

2004년 1월~현재: LIG넥스원 전자전연구 센터 수석연구원

[주 관심분야] 전자전 EA 시스템, 재밍 기

법 M&S

### 이 왕 용

집/재밍시스템

1993년 2월: 경북산업대학교 전자공학과 (공학사)

2007년 2월: 아주대학교 정보전자공학과 (공학석사)

1995년 8월~현재: LIG넥스원 전자전연구 센터 수석연구원

[주 관심분야] 전자전 시스템, 신호정보수

### 이 창 훈

1992년 2월: 연세대학교 전기공학과 (공 학사)

2001년 2월: 한국과학기술원 전자전산학 과 (공학석사)

2006년 8월: 한국과학기술원 전자전산학 과 (공학박사)

2008년 2월~현재: 국방과학연구소 선임

연구원

[주 관심분야] 전자전 시스템, 전자전 신호처리 알고리즘

박 진 태

2004년 2월: 금오공과대학교 전자공학과 (공학사)

2006년 2월: 광주과학기술원 정보통신공 학부 (공학석사)

2011년 8월: 광주과학기술원 정보기전공 학부 (공학박사)

2011년 11월~현재: 국방과학연구소 선임

연구원

[주 관심분야] 전자전 신호처리, 전자공격 기법