JPE 16-6-22

http://dx.doi.org/10.6113/JPE.2016.16.6.2212 ISSN(Print): 1598-2092 / ISSN(Online): 2093-4718

# Analysis and Design of a Separate Sampling Adaptive PID Algorithm for Digital DC-DC Converters

Changyuan Chang $^{\dagger}$ , Xin Zhao $^{*}$ , Chunxue Xu $^{*}$ , Yuanye Li $^{*}$ , and Cheng'en Wu $^{*}$

<sup>†,\*</sup>School of Integrated Circuits, Southeast University, Nanjing, China

#### **Abstract**

Based on the conventional PID algorithm and the adaptive PID (AD-PID) algorithm, a separate sampling adaptive PID (SSA-PID) algorithm is proposed to improve the transient response of digitally controlled DC-DC converters. The SSA-PID algorithm, which can be divided into an oversampled adaptive P (AD-P) control and an adaptive ID (AD-ID) control, adopts a higher sampling frequency for AD-P control and a conventional sampling frequency for AD-ID control. In addition, it can also adaptively adjust the PID parameters (i.e.  $K_p$ ,  $K_i$  and  $K_d$ ) based on the system state. Simulation results show that the proposed algorithm has better line transient and load transient responses than the conventional PID and AD-PID algorithms. Compared with the conventional PID and AD-PID algorithms, the experimental results based on a FPGA indicate that the recovery time of the SSA-PID algorithm is reduced by 80% and 67% separately, and that overshoot is decreased by 33% and 12% for a 700mA load step. Moreover, the SSA-PID algorithm can achieve zero overshoot during startup.

Key words: DC-DC converter, digital controller, fast transient response, SSA-PID algorithm

# I. INTRODUCTION

With the rapid development of communication, computer and consumer electronic industries, digitally controlled DC-DC converters have stood out in recent years. Compared with analog control, digital control has significant advantages in terms of online programmability, advanced control algorithms, efficiency optimization, high operation precision and reliability [1]-[4]. Meanwhile, the digital PID algorithms is one of the most widely used control methods in discrete systems [5]-[8].

Research in the PID control field has developed rapidly in recent years. D. Trevisan et.al from Udine built a model of a voltage-mode controlled converter that included a PID controller [9]. K.-W. Seo from Dongguk University designed a precise fuzzy PID controller for DC-DC converters in 2012, where a precise matrix model was used to adjust the PID parameters [10]. However, the relatively high complexity and

extra hardware and software costs are their drawbacks. Meanwhile, unexpected output oscillations can be introduced by these techniques [11]-[15]. To overcome the above mentioned limitations, this paper proposed a separate sampling adaptive PID (SSA-PID) algorithm to reduce the recovery time and overshoot/undershoot during the transient process. In addition, the proposed algorithm is easy to implement.

The following section introduces the SSA-PID control algorithm. In addition, it gives a description of the differences between the adaptive PID (AD-PID) and the SSA-PID control. Section III briefly describes the simulation process of a digital DC-DC Buck converter using MATLAB/Simulink. This section also presents simulation results. Section IV elaborates on the process of FPGA implementation and presents an experimental comparison between the PID, AD-PID and SSA-PID controllers. Finally, some conclusions are given in Section V.

Manuscript received Jan. 28, 2016; accepted Jun. 14, 2016 Recommended for publication by Associate Editor Sung-Jin Choi.

<sup>†</sup>Corresponding Author: ccyycc@seu.edu.cn Tel: +86-130-0253-5267, Southeast University

#### II. PRINCIPLE OF THE SSA-PID ALGORITHM

# A. AD-PID Algorithm

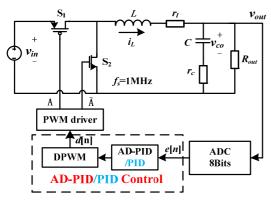

A system diagram of an AD-PID /PID controlled DC-DC

<sup>\*</sup>School of Integrated Circuits, Southeast University, China

Fig. 1. System diagram of an AD-PID/PID controlled Buck converter.

Buck converter is presented in Fig. 1. In addition, the transfer function of a digital PID algorithm can be described as:

$$G_{PID}(z) = K_p + K_i / (1 - z^{-1}) + K_d (1 - z^{-1})$$

(1)

where  $K_p$ ,  $K_i$  and  $K_d$  are the constant coefficients of the proportional gain, integral term and derivative term, respectively.

Considering the A/D converter, PID compensator and digital pulse width modulator (DPWM), the open-loop transfer function of a Buck converter can be written as Equ. (2).

$$G_o(s) = \frac{1}{U_m} \frac{V_{out}}{D} \frac{(1 + sCr_c)(K_i + K_p s + K_d s^2)}{s + s^2 \left[\frac{L + CR_{out}r_l}{R_{out} + r_l} + Cr_c\right] + s^3 LC \frac{R_{out} + r_c}{R_{out} + r_l}}$$

(2)

where L,  $R_{\rm out}$  and C represent the inductor value, load resistance and capacitor value, respectively.  $r_1$  and  $r_{\rm c}$  are the DCR of the inductor and the ESR of the capacitor, separately.  $V_{\rm out}$  and D represent the mean value of the output voltage and duty ratio, respectively.  $U_m$  is the amplitude of a saw-tooth wave in the DPWM module, which is equal to 1 in the proposed design.

In general, under the premise of system stabilization, the greater the loop bandwidth, the better the transient performance of the closed-loop system. Actually, the loop bandwidth is often designed at about 1/10 of the switching frequency. Nevertheless, the dynamic performance of the system can be improved by appropriately increasing the bandwidth during the transient process. Meanwhile, the steady-state accuracy of the system can also be effectively improved with a moderate increase in the low-frequency gain. Table I shows the variation trend of the system performance when the PID parameters are changed.

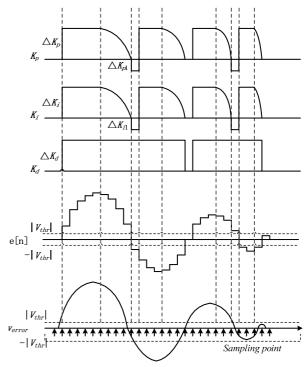

Fig. 2. Operational waveforms of AD-PID controller.

TABLE I

RELATIONSHIPS BETWEEN SYSTEM CHARACTERISTICS AND PID

PARAMETERS

| Variation<br>Trend of<br>Parameters | Low-frequency<br>Gain | Bandwidth | Phase<br>Margin |

|-------------------------------------|-----------------------|-----------|-----------------|

| $K_p$ increase                      | Constant              | Increase  | Reduce          |

| $K_i$ increase                      | Increase              | Constant  | Reduce          |

| $K_d$ increase                      | Constant              | Increase  | Increase        |

The AD-PID algorithm allows the PID parameters to adaptively adjust as needed in different situations. Thus, effectively depressing overshoot/undershoot and reducing the output voltage deviation as well as the recovery time. Therefore, the AD-PID algorithm should maintain an appropriate bandwidth to stabilize the system in the steady state, while a larger bandwidth and low-frequency gain in transient process are helpful to reduce the recovery time and output voltage deviation. The transfer function of the AD-PID compensator in the z domain is:

$$G_{AD-PID}(z) = (K_p + \alpha) + \frac{K_i + \beta}{1 - z^{-1}} + (K_d + \gamma) * (1 - z^{-1})$$

(3)

$$\alpha = \begin{cases} 0, & |v_{error}(n)| < |V_{thr}| \\ \Delta K_{p}, & |v_{error}(n-1)| \le |v_{error}(n)| \\ \frac{|v_{error}(n)|}{|V_{error-peak}|} * \Delta K_{p}, & |v_{error}(n-1)| > |v_{error}(n)| \\ \Delta K_{p1}, & v_{error}(n) * v_{error}(n-1) \le 0 \end{cases} |v_{error}(n) | \ge |V_{thr}|$$

$$(4)$$

where  $\alpha$ ,  $\beta$  and  $\gamma$  are set to zero in the steady state. However, they can change adaptively according to the error signal  $v_{error}$  in transient process.

Operational waveforms of the AD-PID compensator are shown in Fig. 2. The basic procedure is outlined as follows. Firstly, the present error signal  $v_{error}(n)$  is compared with the threshold voltage  $V_{thr}$ . If  $v_{error}(n)$  is no more than  $V_{thr}$ , the system is identified as being in the steady state. At the same time,  $\alpha$ ,  $\beta$  and  $\gamma$  are set to 0 to ensure the stability of the system. If  $v_{error}(n)$  is greater than  $V_{thr}$ , the system is considered to be in the transient state. Meanwhile,  $\alpha$ ,  $\beta$  and  $\gamma$  change quickly to increase the loop bandwidth. This in turn, accelerates the transient response of the system. Eqns. (4)-(6) summarize the selection rules of  $\alpha$ ,  $\beta$  and  $\gamma$  in different states.

$\Delta K_p$ ,  $\Delta K_{pl}$ ,  $\Delta K_i$ ,  $\Delta K_{il}$  and  $\Delta K_d$  are the adaptive variable coefficients of the proportional gain, integral term and derivative term, respectively.

# B. SSA-PID Algorithm

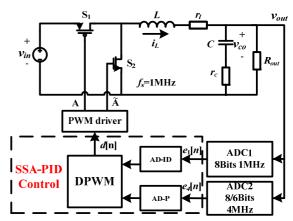

One of the key points of digital control is to accelerate the transient response. However, the conversion time of an A/D converter and the computation time of a digital compensator may have bad effects on the transient performance. In order to solve this problem, a SSA-PID algorithm is proposed on the basis of an AD-PID algorithm, which divides the AD-PID control into an oversampled adaptive P (AD-P) control and an adaptive ID (AD-ID) control. Regarding the AD-P control, the system uses a high-speed but low-resolution A/D converter for rapid detection and correction. Meanwhile, a high-resolution but low-speed A/D converter for precise adjustment is adopted in the AD-ID control. The sampling frequency of the AD-ID control is the same as that of the AD-PID control, while the AD-P control is oversampled. A system diagram of a SSA-PID controlled Buck converter is shown in Fig. 3.

In Fig. 3,  $v_{in}$  is the input voltage and  $v_{out}$  is the output voltage,  $S_1$  and  $S_2$  are MOSFETs, and  $f_s$  is the switching frequency, which is equal to 1MHz in this design. It can be seen from Fig. 3 that the two control loops are parallel, and that oversampling is only adopted in the AD-P control for a trade-off between performance and cost.

Based on the above analysis, the SSA-PID control algorithm can be expressed as Equ. (7):

Fig. 3. System diagram of a SSA-PID controlled Buck converter.

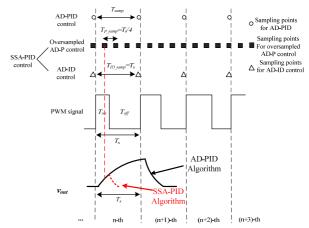

Fig. 4. The comparison of sampling methods between the two algorithms.

$$H(s) = \hat{H}_{p} e^{-s\tau_{1}} + (\frac{\hat{H}_{i}}{s} + s \hat{H}_{d})e^{-s\tau_{2}}$$

(7)

where  $\hat{H}_p$ ,  $\hat{H}_i$  and  $\hat{H}_d$  are the self-adaptive gains of the proportional term, integral term and differential term, respectively. Usually, the delay time  $\tau_2$  is equal to the switching period  $T_{s}$ , while  $\tau_1$  is reduced to  $T_{s}/4$ .

A comparison of the sampling points between the AD-PID algorithm and the SSA-PID algorithm can be seen from Fig. 4, where  $T_{samp}$ ,  $T_{ID\_samp}$  and  $T_{P\_samp}$  are the sampling periods of the AD-PID control, AD-ID control and oversampled AD-P control, respectively. In the AD-PID algorithm, the output voltage is sampled once in a switching cycle  $T_s$ . In terms of the SSA-PID algorithm, the sampling frequency of the

$$\beta = \begin{cases} 0, & |v_{error}(n)| < |V_{thr}| \\ \Delta K_i, & |v_{error}(n-1)| \le |v_{error}(n)| \\ \frac{|v_{error}(k)|}{|V_{error-peak}|} * \Delta K_i, |v_{error}(n-1)| > |v_{error}(n)| \end{cases} v_{error}(n) * v_{error}(n-1) > 0 \\ \Delta K_{i1}, & v_{error}(n) * v_{error}(n-1) \le 0 \end{cases} |v_{error}(n)| \ge |V_{thr}|$$

$$\gamma = \begin{cases} 0, & |v_{error}(n)| < |V_{thr}| \\ \Delta K_d, & |v_{error}(n)| \ge |V_{thr}| \end{cases}$$

(6)

TABLE II

DESIGN SPECIFICATIONS FOR THE BUCK CONVERTER

| Parameter                          | Value | Unit |

|------------------------------------|-------|------|

| Input voltage $(v_{in})$           | 5     | V    |

| Output voltage (v <sub>out</sub> ) | 1.8   | V    |

| Inductor (L)                       | 4.7   | μН   |

| DCR of Inductor ( <u>r_l</u> )     | 80    | mΩ   |

| Output capacitor (C)               | 10    | μF   |

| ESR of Capacitor $(r_c)$           | 70    | mΩ   |

| Switching frequency $(f_s)$        | 1     | MHz  |

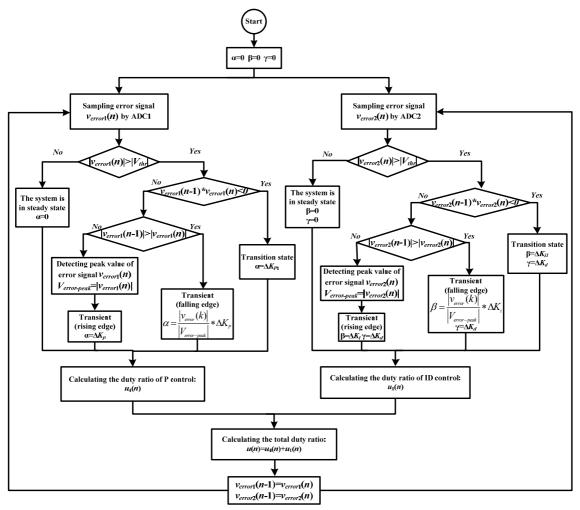

AD-ID control is the same as the switching frequency, while the output voltage is sampled four times in a switching cycle for the AD-P control. Meanwhile, the SSA-PID algorithm has the advantage of the AD-PID algorithm that the control parameters ( $K_p$ ,  $K_i$  and  $K_d$ ) change adaptively according to the system state. It is obvious that output voltage errors will be detected more quickly because of the oversampled AD-P control, and the feedback control loop will work immediately to reduce the recovery time and overshoot/undershoot, which is why the SSA-PID algorithm possesses better transient performance than the AD-PID algorithm. Fig. 5 shows an implementation diagram of the SSA-PID algorithm.

# III. SIMULATION OF THE SSA-PID ALGORITHM

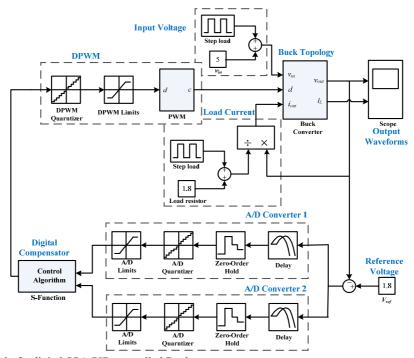

The integrated DC-DC converter is composed of a Buck topology, an A/D converter, a digital compensator and a DPWM. Fig. 6 shows a Simulink model of the whole system, where the Buck topology is constructed by using the state space averaging method. In addition, the design specifications of the Buck converter are shown in Table II.

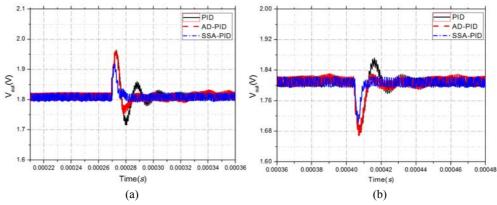

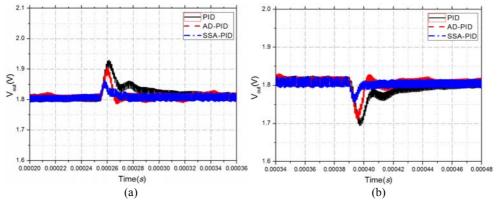

Simulation data from the conventional PID, AD-PID and SSA-PID control algorithms are imported into the Origin software for comparison. Figs. 7-8 indicate that SSA-PID algorithm possesses a shorter recovery time and less overshoot/undershoot compared with the PID algorithm or the AD-PID algorithm.

# IV. EXPERIMENTAL RESULTS OF THE SSA-PID ALGORITHM

In order to observe the effects of these three compensation algorithms in an actual power system, a prototype of a FPGA-based digital Buck converter is built (see Fig. 9). The integrated power MOSFET transistor is a  $\mu$ PA2791, and the driver chip is a UCC27524. An Altera Cyclone II device (EP2C5Q208C8) is used to implement the SSA-PID compensator and DPWM. The input voltage is  $v_{in} = 5V$  and the output voltage is  $v_{out} = 1.8V$ .

The duty ratio signal of the conventional PID algorithm or the AD-PID algorithm is as follows:

$$d[n] = d[n-1] + (K_p + K_i + K_d) * e[n]$$

$$-(K_p + 2K_d) * e[n-1] + K_d * e[n-2]$$

$$= d[n-1] + a * e[n] - b * e[n-1] + c * e[n-2]$$

$$= d[n-1] + \Delta d[n]$$

(8)

where d[n-1] is the duty ratio signal of the previous cycle, and d[n] is the present duty ratio signal.  $K_p$ ,  $K_i$  and  $K_d$  are the constant coefficients of the PID algorithm or the adaptive gain coefficients of the AD-PID algorithm.

The SSA-PID algorithm uses a separate sampling structure, and its duty ratio signal can be described as:

$$d[n] = d_4[n] + d_1[n]$$

(9)

$$d_{1}[n] = d_{1}[n-1] + K_{i} * e_{1}[n]$$

$$+ K_{d} * (e_{1}[n] - 2e_{1}[n-1] + e_{1}[n-2])$$

$$= d_{1}[n-1] + (K_{i} + K_{d}) * e_{1}[n] - 2K_{d} * e_{1}[n-1]$$

$$+ K_{d} * e_{1}[n-2]$$

$$= d_{1}[n-1] + a * e_{1}[n] - b * e_{1}[n-1] + c * e_{1}[n-2]$$

$$d_{4}[n] = d_{4}[n-1] + K_{n} * (e_{4}[n] - e_{4}[n-1])$$

$$(11)$$

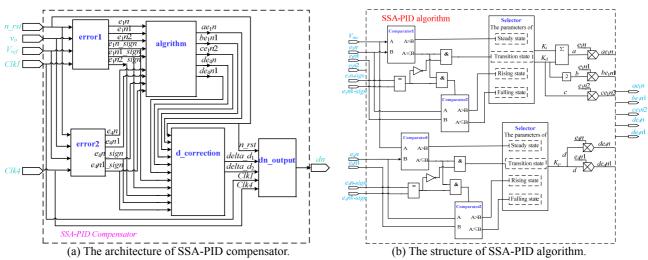

Fig. 10 shows an implementation diagram of the SSA-PID algorithm. The two sampling channels are calculated separately in the SSA-PID algorithm. The output voltage, sampled at 1MHz, is compared with the reference voltage in the error 1 module to obtain the present error signal  $e_1n$ , the previous moment error signal  $e_1n1$ , the error signal of two cycles ago  $e_1n^2$  as well as their corresponding sign bits  $e_1n$ -sign,  $e_1n1$ -sign and  $e_1n2$ -sign. Meanwhile, the output voltage sampled at 4MHz is compared with the reference voltage in the error2 module to obtain the present error signal  $e_{A}n$ , the previous moment error signal  $e_{A}n1$ , and the corresponding sign bits  $e_4n$ -sign and  $e_4n1$ -sign. Next, the values of  $|a^*e_1n|$ ,  $|b^*e_1n1|$ ,  $|c^*e_1n2|$ ,  $|d^*e_4n|$  and  $|d^*e_4n1|$  are calculated by the corresponding algorithm. Then, the d correction module calculates the values of delta  $d_1$  $(=a*e_1n-b*e_1n1+c*e_1n2)$  and delta  $d_2$   $(=d*e_4n-d*e_4n1)$  based on the sign bits and the error signals. Finally, the duty ratio command signal dn (= $d_1n+d_4n$ ) can be calculated by the dn output module, where  $d_1n=d_1n$  last+delta  $d_1$  $d_4n=d_4n$  last+ delta  $d_4$ .

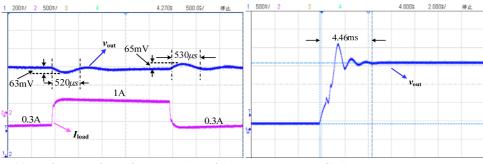

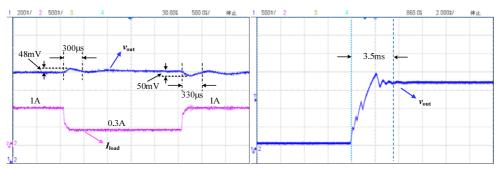

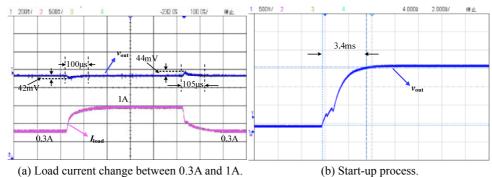

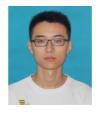

Figs. 11-13 show experimental results of the transient response of the three control algorithms, including the start-up process and load transient response. It can be seen that the transient performance of the conventional PID algorithm, AD-PID algorithm and SSA-PID algorithm are successively getting better and better. The start-up time of the SSA-PID algorithm is significantly reduced compared with the conventional PID algorithm, and the overshoot is eliminated in the proposed algorithm. This provides excellent start-up protection for the power system. In addition, compared with the PID and AD-PID algorithm, the recovery time and overshot/undershoot of the SSA-PID algorithm are effectively improved.

Fig. 5. The flowchart of SSA-PID algorithm.

Fig. 6. The Simulink model of a digital SSA-PID controlled Buck converter.

Fig. 7. Load transient response for 500mA load step ( (a) overshoot, (b) undershoot).

Fig. 8. Line transient response for 1V input voltage step ( (a) overshoot, (b) undershoot).

Fig. 9. The verification platform of a digital Buck converter.

Fig. 10. Implementation of the SSA-PID algorithm.

(a) Load current change between 0.3A and 1A.

(b) Start-up process.

Fig. 11. Transient response of conventional PID algorithm.

(a) Load current change between 0.3A and 1A.

(b) Start-up process.

Fig. 12. Transient response of AD-PID algorithm.

(b) Start-up process.

Fig. 13. Transient response of SSA-PID algorithm.

TABLE III TRANSIENT RESPONSE COMPARISON OF THE THREE ALGORITHMS

| Algorithm | Line transient response (1V) | Load transient response  |                          |  |

|-----------|------------------------------|--------------------------|--------------------------|--|

|           |                              | Simulation<br>(500mA)    | Experiment (700mA)       |  |

|           | Overshoot/<br>undershoot     | Overshoot/<br>undershoot | Overshoot/<br>undershoot |  |

| PID       | 40μs (80mV)/                 | 30μs (140mV)/            | 530μs (65mV)/            |  |

|           | 60μs (75mV)                  | 20μs (130mV)             | 520μs (63mV)             |  |

| AD-PID    | 15μs (80mV)/                 | 15μs (140mV)/            | 300μs (48mV)/            |  |

|           | 15μs (90mV)                  | 10μs (130mV)             | 330μs (50mV)             |  |

| SSA-PID   | 10μs (40mV)/                 | 10μs (100mV)/            | 105μs (44mV)/            |  |

|           | 11μs (45mV)                  | 5μs (95mV)               | 100μs (42mV)             |  |

Table III summarizes a comparison of the simulation and experimental results among the three algorithms, where the time before a bracket represents the recovery time and the value in a bracket means the overshoot/undershoot voltage. It

is obvious that the SSA-PID algorithm shows better transient performance than the PID and AD-PID algorithms.

Table IV summarizes a comparison of the hardware resource occupancy between the conventional PID, AD-PID and SSA-PID algorithms. It can be seen that the number of used logic elements of the SSA-PID algorithm is the lowest. However, the number of pins is the highest. Unlike the AD-PID algorithm, the SSA-PID algorithm and the conventional PID algorithm do not require embedded 9-bit-multiplier elements. Therefore, the SSA-PID algorithm can achieve better transient performance and less resource consumption compared with the AD-PID algorithm.

A comparison between the proposed SSA-PID algorithm and prior arts is summarized in Table V. According to this table, the SSA-PID algorithm has advantages in terms of hardware cost and transient response compared with the controllers in references [16], [17] and the LTC3530 chip.

TABLE IV

COMPARISON OF HARDWARE RESOURCE OCCUPANCY

| Resource                           |             | Control Scheme |              |

|------------------------------------|-------------|----------------|--------------|

| (EP2C5Q208C8)                      | PID         | AD-PID         | SSA-PID      |

| Logic elements                     | 1089/4608   | 1104/4608      | 961/4608     |

| Logic elements                     | (24%)       | (24%)          | (21%)        |

| Combinational                      | 808/4608    | 849/4608       | 688/4608     |

| functions                          | (18%)       | (18%)          | (15%)        |

| Dedicated logic                    | 599/4608    | 637/4608       | 654/4608     |

| registers                          | (13%)       | (14%)          | (14%)        |

| Pins                               | 12/142 (8%) | 12/142 (8%)    | 20/142 (14%) |

| Bits of memory                     | 2176/119808 | 2176/119808    | 2176/119808  |

| Dits of memory                     | (2%)        | (2%)           | (2%)         |

| Embedded 9-bit multiplier elements | 0/26 (0%)   | 7/26 (27%)     | 0/26 (0%)    |

| PLLs                               | 1/2 (50%)   | 1/2 (50%)      | 1/2 (50%)    |

TABLE V

COMPARISON BETWEEN THE PROPOSED SSA-PID CONTROL

ALGORITHM AND PRIOR ARTS

|                     | ALGURI          | HM AND FRIOR                  | CAKIS                         |             |

|---------------------|-----------------|-------------------------------|-------------------------------|-------------|

|                     | This paper      | [16]                          | [17]                          | LTC3530     |

| Control type        | Digital         | Digital                       | Digital                       | Analog      |

| Control algorithm   | SSA-PID         | Improved digital peak current | First-order<br>digital filter | N/A         |

| Switching frequency | 1MHz            | 50kHz                         | 3.125MHz                      | 1MHz        |

| Input<br>voltage    | 3.6-5V          | 5V                            | 0-3.3V                        | 1.8-5.5V    |

| Output<br>voltage   | 1.8V            | 1.5V                          | 0.1-3.3V                      | 3.3V        |

| Maximum current     | 1A              | 2A                            | N/A                           | 500mA       |

| Filter<br>inductor  | 4.7μΗ           | 20μΗ                          | 2.2μΗ                         | 4.7μΗ       |

| Filter capacitor    | 10μF            | 1420μF                        | 10μF                          | 22μF        |

| Number of<br>A/D    | 2               | 2                             | 1                             | 0           |

| Digits of<br>A/D    | 6bits/8bits     | 8bits                         | 10bits                        | N/A         |

| Digits of<br>DPWM   | 10bits          | 10bits                        | >10bits                       | N/A         |

| Load Step           | $0.15 \mu s/mA$ | $1.24 \mu s/mA$               | $2\mu s/mA$                   | $1\mu s/mA$ |

| Response            | 0.06V/A         | 0.07V/A                       | 0.08V/A                       | 0.33V/A     |

### V. CONCLUSIONS

A Separate Sampling Adaptive PID algorithm for digitally controlled DC-DC converters is proposed in this paper. The proposed algorithm exploits the oversampled AD-P control and the AD-ID control to improve the transient response of the system. In addition, simulation results based on MATLAB/Simulink software and experimental verification

based on a FPGA are presented. Both the simulation and experimental results indicate that the proposed control algorithm possesses better startup and transient performance compared with the conventional PID and AD-PID algorithms, while the hardware occupancy is kept at an appropriate level. The proposed algorithm provides useful guidance on the design of digital controllers for DC-DC converters.

#### ACKNOWLEDGMENT

The authors would like to thank the National Natural Science Foundation of China (Grant No. 61376029), the Fundamental Research Funds for the Central Universities, China, and the College Graduate Research and Innovation Program of Jiangsu Province, China (Grant No. SJLX15 0092) for supporting this research.

#### REFERENCES

- [1] P. Zumel, C. Fernandez, M. Sanz, A. Lazaro, and A. Barrado, "Step-by-step design of an FPGA-based digital compensator for DC/DC converters oriented to an introductory course," *IEEE Trans. Educ.*, Vol. 54, No. 4, pp. 599-609, Nov. 2011.

- [2] W. Huang and J. A. A. Qahouq, "Tuning of a digital proportional-integral compensator for DC-DC power converter," in *Proc. APEC*, pp. 270-275, 2013.

- [3] J. A. A. Qahouq and V. Arikatla, "Online closed-loop autotuning digital controller for switching power converters," *IEEE Trans. Ind. Electron.*, Vol. 60, No. 5, pp. 1747-1758, May 2013.

- [4] Y. F. Liu, E. Meyer, and X. D. Liu, "Recent developments in digital control strategies for DC/DC switching power converters," *IEEE Trans. Power Electron.*, Vol. 24, No. 11, pp. 2567-2577, Nov. 2009.

- [5] E. R. C. S. Madhukiran, P. S. Thota, B. Sridhar, and K. Dileesh, "Control of Buck converter by Polynomial, PID and PD controllers," in *Proc. PRIMEASIA*, pp. 94-99, 2012.

- [6] S. Lee and J. Burm, "A DC-DC buck converter with using a digital PID regulator based on a simple control algorithm," in *Proc. ISSCS*, pp. 355-358, 2011.

- [7] M. Mahdavian, M. B. Poudeh, and N. Wattanapongsakorn, "Improving the efficiency of power supplies with an adaptive control method," in *Proc. ECTI-CON*, pp. 1-4, 2013.

- [8] V. Arikatla and J. A. A. Qahouq, "DC-DC power converter with digital PID controller," in *Proc. APEC*, pp. 327-330, 2011.

- [9] D. Trevisan, W. Stefanutti, P. Mattavelli, and P. Tenti, "FPGA control of SIMO dc-dc converters using load current estimation," in *Proc. IECON*, pp. 2243-2248, 2005.

- [10] K.-W. Seo and H. H. Choi, "Simple fuzzy PID controllers for DC-DC converters," *Journal of Electrical Engineering* & *Technology*, Vol. 7, No. 5, pp. 724-729, Sep. 2012.

- [11] A. T. L. Lee, J. K. O. Sin, and P. C. H. Chan, "Adaptive high-bandwidth digitally controlled buck converter with improved line and load transient response," *IET Power Electron.*, Vol. 7, No. 3, pp. 515-526, Mar. 2014.

- [12] Q. Wang, N. Chen, S. Xu, W. Sun, and L. Shi, "Trajectory prediction control for digital control DC-DC converters with fast transient response," *Microelectronics Journal*, Vol. 45, No. 6, pp. 767-774, Jun. 2014.

- [13] V. Yousefzadeh, A. Babazadeh, B. Ramachandran, E. Alarcon, L. Pao, and D. Maksimovic, "Proximate time-optimal digital control for synchronous buck DC-DC converters', *IEEE Trans. Power Electron.*, Vol. 23, No. 4, pp. 2018-2026, Jul. 2008.

- [14] C. E. Carrejo, E. Vidal-Idiarte, R. Giral, and L. Martinez-Salamero, "Predictive digital interpolation current control for DC-DC power converters," *IET Power Electron.*, Vol. 2, No. 5, pp. 545-554, Sep. 2009.

- [15] J.-T. Su, D.-M. Liu, C.-W. Liu, and C.-W. Hung, "An adaptive control method for two-phase DC/DC Converter," in *Proc. PEDS*, pp. 288-293, 2009.

- [16] G. Zhou, J. Xu, and Y. Jin, "Improved digital peak current predictive control for switching DC-DC converters," *IET Power Electron.*, Vol. 4, No. 2, pp. 227-234, Feb. 2011.

- [17] E. G. Soenen, A. Roth, J. Shi, M. Kinyua, J. Gaither, and E. Ortynska, "A robust digital dc-dc converter with rail-to-rail output range in 40nm CMOS," in *Proc. ISSCC*, pp. 198-199, 2010.

Xin Zhao received his B.S. degree from the Chengxian College of Southeast University, Nanjing, China, in 2014. He is presently working towards his M.S. degree in IC Engineering at Southeast University, Nanjing, China. His current research interests include switch-mode power supplies and dc-dc converters.

Chunxue Xu received her B.S. degree from Jiangsu Normal University, Xuzhou, China, in 2014. She is presently working towards her M.S. degree in IC Engineering at Southeast University, Nanjing, China. Her current research interests include flicker-free AC-DC LED drivers.

circuits, power converters.

Yuanye Li was born in Jiangsu, China, in 1991. He received his B.S. degree from the Chongqing University of Posts and Telecommunications, Chongqing, China, in 2014. He is presently working towards his M.S. degree in Microelectronics at Southeast University, Nanjing, China. His current research interests include analog integrated electronics and high-efficiency AC-DC

Changyuan Chang received his M.S. and Ph.D. degrees in Electronic Engineering from Southeast University, Nanjing, China, in 1990 and 2000, respectively. He is presently working as an Associate Professor in the School of Integrated Circuits, Southeast University. His current research interests include analog-controlled and

digitally-controlled IC designs for power-management.

Cheng`en Wu received his B.S. degree from the Shanghai University of Electric Power, Shanghai, China, in 2013. He is presently working towards his M.S. degree in IC Engineering at Southeast University, Nanjing, China. His current research interests include nonlinear modeling and the design of power converters.