논문 2016-53-12-6

# UHD 영상을 지원하는 HEVC 및 H.264 멀티 디코더 용 인트라 예측 회로 설계

(Design of Intra Prediction Circuit for HEVC and H.264 Multi-decoder Supporting UHD Images)

유 상 현\*, 조 경 순\*\*

(Sanghyun Yu and Kyeongsoon Cho)

요 약

이 논문은 UHD 영상을 지원하는 멀티 디코더 용 인트라 예측 회로의 구조와 설계를 제안하고 있다. 제안된 회로는 가장 최신의 비디오 압축 표준인 HEVC뿐만 아니라 H.264도 지원한다. 이 회로는 기본적인 인트라 예측 기능이외에 추가적으로 H.264 표준에 정의되어 있는 참조 샘플 필터 연산과 HEVC 표준에 정의되어 있는 약한 참조 샘플 필터 및 강한 참조 샘플 필터 연산을 처리하는 기능도 갖고 있다. 공통적인 연산부와 내부 저장소를 공유함으로써 회로의 크기를 감소시켰으며, 병렬 연산을 통하여 성능을 향상시켰다. 제안된 회로는 Verilog HDL(Hardware Description Language)을 이용하여 RTL(Register Transfer Level)로 기술하였으며, Cadence의 NC-Verilog를 이용하여 기능을 검증하였다. RTL 회로를 Synopsys의 Design Compiler 및 130nm 표준 셀 라이브러리를 이용하여 합성하였다. 합성된 게이트 수준 회로는 69,694개의 게이트로 구성되며, 최대 동작주파수 157MHz에서 4K-UHD HEVC 영상을 초당 100 ~ 280 프레임의 속도로 처리한다.

#### Abstract

This paper proposes the architecture and design of intra prediction circuit for a multi-decoder supporting UHD images. The proposed circuit supports not only the latest video compression standard HEVC but also H.264. In addition to the basic function of performing intra prediction, this circuit has the capability of performing the reference sample filter operation defined in the H.264 standard, and the smoothing and strong sample filter operations defined in the HEVC standard. We reduced the circuit size by sharing the circuit blocks for common operations and internal storage, and improved the circuit performance by parallel processing. The proposed circuit was described at RTL using Verilog HDL and its functionality was verified by using NC-Verilog of Cadence. The RTL circuit was synthesized by using Design Compiler of Synopsys and 130nm standard cell library. The synthesized gate-level circuit consists of 69,694 gates and processes 100  $^{\sim}$  280 frames per second for 4K-UHD HEVC images at the maximum operation frequency of 157MHz.

Keywords: Intra Prediction, Multi-decoder, HEVC, H.264, UHD

### I. 서 론

정보화 기술이 발전함에 따라 다양한 종류의 영상 부 호화 표준이 제정, 활용되고 있다. 이러한 영상 부호화 표준들은 현재 널리 이용하고 있는 디지털 TV 케이블 방송, Youtube, 인터넷 전화, 웹브라우저 등과 같은 다양한 멀티미디어 서비스들에 사용되고 있으며, 이를 지원하는 인코더 및 디코더에 대한 연구가 활발히 진행되고 있다. 특히 가장 최근에 발표된 HEVC(High Efficiency Video Coding)<sup>[1]</sup>와 현재 널리 보급되어 있는 H.264<sup>[2]</sup>를 지원하는 멀티 디코더에 대한 연구의 필요성이 높아지고 있다.

영상 부호화 기술 중 인트라 예측은 화면 내 인접한 화소들 간의 유사성을 이용하여 공간적 중복성을 제거 하는 것으로 HEVC와 H.264에서 사용하는 중요한 영상

Received; October 17, 2016 Revised; October 19, 2016

Accepted; November 22, 2016

<sup>\*</sup> 정회원, \*\* 평생회원, 한국외국어대학교 전자공학과 (Department of Electronics Engineering, Hankuk University of Foreign Studies)

<sup>©</sup> Corresponding Author (E-mail: kscho@hufs.ac.kr)

<sup>※</sup> 이 논문은 2016년도 한국외국어대학교 교내학술연구 비의 지원에 의한 것임.

| 모드 번호 | 예측 모드 이름                  |

|-------|---------------------------|

| 0     | Intra_Vertical            |

| 1     | Intra_Horizontal          |

| 2     | Intra_DC                  |

| 3     | Intra_Diagonal_Down_Left  |

| 4     | Intra_Diagonal_Down_Right |

| 5     | Intra_Vertical_Right      |

| 6     | Intra_Horizontal_Down     |

| 7     | Intra_Vertica1_Left       |

| 8     | Intra_Horizontal_Up       |

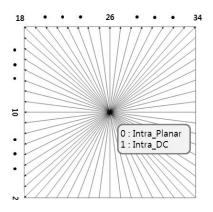

그림 1. H.264의 휘도 4x4, 8x8 인트라 예측모드 Fig. 1. Luma 4x4, 8x8 intra prediction modes of H.264.

부호화 기술 중 하나이다. 인트라 예측을 위해서는 주변의 참조 데이터를 이용하여 여러 가지 예측모드 연산을 통해 예측 데이터를 생성하는데, 각각의 화소마다예측모드 연산을 진행하여야 하므로 많은 연산량을 필요로 한다. 따라서 원하는 성능을 얻기 위해서는 인트라 예측 기능을 회로로 구현하는 것이 필요하다<sup>[3]</sup>. 본논문에서는 4K-UHD(3,840x2,160) 영상을 실시간으로처리하는 HEVC 및 H.264 통합 멀티 디코더 용 인트라예측 회로 구조를 제안한다.

본 논문의 II장에서는 H.264와 HEVC의 인트라 예측 방법에 대해 설명하고, III장에서는 인트라 예측 회로의 구조를 제안한다. IV장에서는 실험 결과를 기술하고, V 장에서 결론을 제시한다.

# Ⅱ. H.264와 HEVC의 인트라 예측 방법

### 1. H.264의 인트라 예측

H.264의 인트라 예측은 휘도 예측과 색차 예측으로 이루어진다. 휘도 예측에 사용되는 블록은 4x4 블록과 8x8 블록, 16x16 블록이며, 색차 예측에 사용되는 블록은 8x8 블록이다. H.264에서 휘도 4x4 인트라 예측과 휘도 8x8 인트라 예측은 유사한 예측모드 연산을 수행하고, 휘도 16x16 인트라 예측과 색차 8x8 인트라 예측은 유사한 예측모드 연산을 수행한다.

그림 1에서 볼 수 있듯이, 휘도 4x4 인트라 예측과 8x8 인트라 예측은 8가지의 방향성을 지닌 예측모드와 평균값 예측인 Intra\_DC 모드로 이루어진다. 휘도 16x16 인트라 예측과 색차 8x8 인트라 예측은 휘도 4x4 인트라 예측에서 사용하는 Intra\_Vertical, Intra\_Horizontal, Intra\_DC 모드 이외에 Intra\_Plane 모드를 포함한다. 예측모드 연산을 수행하기 전 참조 샘플 필터 연산을 진행하고, 이를 이용하여 예측모드 연산을 진행한다. 이때 참조 샘플 필터 연산은 참조 샘플 간의 평활화 연산으로 이루어진다.

그림 2. HEVC의 인트라 예측모드 Fig. 2. Intra prediction modes of HEVC.

#### 2. HEVC의 인트라 예측

H.264의 인트라 예측에서는 최대 9개의 예측모드를 사용하였으나, HEVC의 인트라 예측은 그림 2와 같이 총 33가지 방향성 예측모드와 2가지의 무 방향성 예측모드(Intra\_Planar, Intra\_DC)를 지원한다. HEVC에서는 H.264에서 사용한 블록이라는 개념을 PU(Prediction Unit)와 같이 유닛 개념으로 표현한다. HEVC 인트라 예측에서 사용하는 PU 크기는 5가지로 4x4, 8x8, 16x16, 32x32, 64x64이고, 64x64 PU의 경우 32x32 PU 4개로 분할하여 인트라 예측을 수행하므로, 실질적인 HEVC 인트라 예측에서 사용하는 PU는 4x4, 8x8, 16x16, 32x32이며, 각각의 PU 마다 35가지의 예측모드를 지원한다.

HEVC에서는 인트라 예측을 하기 전에 준비 과정으로 참조 샘플 패딩 작업을 먼저 수행하고, 예측모드에따라 참조 샘플 필터 연산을 수행한다. HEVC의 참조샘플 필터는 약한 참조 샘플 필터와 강한 참조 샘플 필터로 이루어져 있으며, PU의 크기와 예측모드에 따라적용되는 필터 연산의 유무가 결정된다. 약한 참조 샘플 필터는 H.264의 참조 샘플 필터 연산과 유사한 평활화 연산을 수행하며, 강한 참조 샘플 필터는 양선형 필터로서 32x32 PU에만 적용된다. 참조 샘플 준비 단계를 거친 참조 샘플들을 이용하여 예측모드 연산을 통해예측 데이터가 생성된다.

## Ⅲ. HEVC/H.264 통합 인트라 예측 회로

### 1. 통합 인트라 예측 회로 구조

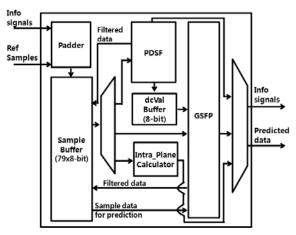

그림 3은 제안하는 통합 인트라 예측 회로 구조를 나타낸다. 연산량 및 연산기 수를 감소시키기 위해 유사한 연산을 수행하는 부분들을 통합하는 과정을 거쳐 전

그림 3. 제안하는 회로 구조

Fig. 3. Proposed circuit architecture.

체적인 회로 구조를 결정하였다. 또한 저장 공간을 줄이기 위해 내부적으로 사용하는 버퍼들을 재사용할 수 있도록 통합하였다.

H.264의 참조 샘플 필터 연산, HEVC의 약한 참조샘플 필터 연산, Intra\_DC 모드의 dcVal 연산과 H.264의 예측모드 연산의 공통 수식을 공유하는 통합 연산기인 PDSF(Predmode, Dcval and Smoothing Filter) 블록을 설계하였다. HEVC의 강한 참조 샘플 필터 연산과 HEVC의 모든 예측모드 연산을 공유하는 통합 연산기인 SFP(Strong Filter and Predmode) 블록을 설계하고, 이를 병렬로 16개 연결하여 GSFP(Group of SFP's) 블록을 설계하였다.

Intra\_Plane Calculator는 Intra\_Plane 모드 예측 데이터를 계산하는 블록이고, Padder는 필요에 따라 패딩작업을 수행하는 블록이다. Sample Buffer는 예측모드연산에 필요한 참조 샘플 데이터를 저장하며, dcVal Buffer는 PDSF, dcVal 값을 저장한다.

#### 2. PDSF

제안하는 PDSF는 H.264의 참조 샘플 필터 연산, HEVC의 약한 참조 샘플 필터 연산, Intra\_DC 모드의 dcVal 연산과 H.264의 예측모드 연산에서 발생한 공통 수식을 공유하는 연산기이다. 표준에 정의된 H.264의 참조 샘플 필터 연산과 HEVC의 약한 참조 샘플 필터 연산은 식 (1)과 식 (2)와 같이 인접한 화소 간의 가중치가 고려된 합으로 표현된다. 식 (1)과 식 (2)는 식 (3)과 식 (4)로 변형 가능하며, 식 (3)과 식 (4)에서 알 수 있듯이 b+c+1이 중복 연산됨을 알 수 있다.

$$Z_1 = (a+2b+c+2) \gg 2 \tag{1}$$

그림 4 PDSF를 위한 공통 연산 회로

Fig. 4. Common operation circuit for PDSF.

$$Z_2 = (b+2c+d+2) \gg 2$$

(2)

$$Z_1 = (a+b+1+b+c+1) \gg 2 \tag{3}$$

$$Z_{2} = (b+c+1+c+d+1) \gg 2 \tag{4}$$

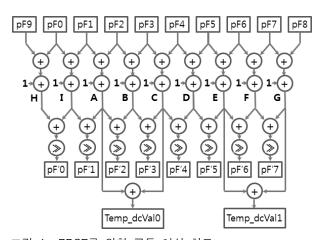

식(5)와 식(6)은 HEVC의 약한 참조 샘플 필터 중 일부를 나타내며, pF'은 약한 참조 샘플 필터링을 수행한 참조 샘플, pF는 약한 참조 샘플 필터링을 수행하기 전참조 샘플을 의미한다. 식 (7)의 A, B, C를 이용하여 식(8)과 식(9)와 같이 나타낼 수 있으며, 식(8)과 식(9)는 B 연산을 공유하고 있음을 알 수 있다. 이와 같은 현상은 H.264의 참조 샘플 필터 연산, Intra\_DC 모드의 dcVal 연산, H.264의 예측모드 연산에서 자주 발생한다. 이에 착안하여 그림 4와 같은 PDSF를 위한 공통 연산회로를 설계하였다. 이 회로는 28개의 덧셈 연산기, 8개의 시프트 연산기로 이루어져 있다.

$$pF'[2,-1] = (pF[1,-1] + 2pF[2,-1] + pF[3,-1] + 2) \gg 2$$

(5)

$$pF'[3,-1] = (pF[2,-1] + 2pF[3,-1] + pF[4,-1] + 2) \gg 2$$

(6)

$$A = pF[1,-1] + pF[2,-1] + 1$$

$$B = pF[2,-1] + pF[3,-1] + 1$$

$$C = pF[3,-1] + pF[4,-1] + 1$$

(7)

$$pF'[2,-1] = (A+B) \gg 2$$

(8)

$$pF'[3,-1] = (B+C) \gg 2$$

(9)

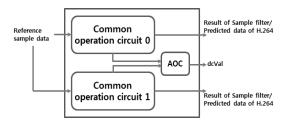

회로 성능을 향상시키기 위해 그림 4의 공통 연산 회로 2개를 병렬로 사용하고, dcVal 계산을 위한 보조 연산기 AOC(Auxiliary Operation Circuit)를 포함하여 그림 5와 같이 전체적인 PDSF 회로를 완성하였다. PDSF는 참조 샘플 필터 연산을 수행할 때, 사이클당 필터링된 참조 샘플 데이터 16개를 출력하며, 8x8 PU의 경우 1사이클, 16x16 PU의 경우 2사이클, 32x32 PU의 경우 4사이클이 소요된다. dcVal 연산을 수행할 때, 4x4 PU

그림 5. PDSF 회로 구조 Fig. 5. PDSF circuit architecture.

의 경우 1사이클, 8x8 PU의 경우 1사이클, 16x16 PU의 경우 2사이클, 32x32 PU의 경우 4사이클이 소요된다.

#### 3. GSFP

제안하는 GSFP는 HEVC의 모든 인트라 예측모드 연산과 강한 참조 샘플 필터 연산에서 발생한 공통 수 식을 공유하는 연산기이다. 표준에 정의된 HEVC의 강 한 참조 샘플 필터 연산과 Intra\_Angular 예측모드 연 산은 식 (10)과 같이 2개의 곱셈 연산, 3개의 덧셈 연산, 1개의 시프트 연산으로 표현된다.

$$Z_{i} = \{ (\beta - \alpha) \times A + \alpha \times B + \gamma \} \gg \delta$$

(10)

$$Z_3 = \{ \alpha \times (B - A) + \gamma \} \gg \delta + A \tag{11}$$

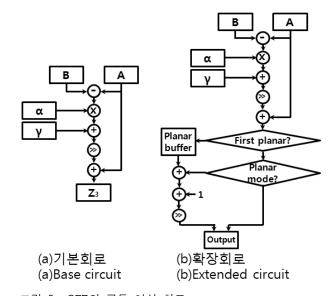

곱셈기의 크기는 덧셈기나 시프트 연산기에 비해 크므로 저면적 회로 설계를 위해서는 곱셈 연산의 최소화가 필요하다. 식 (10)의 β는 1<<6 이므로 식 (11)과 같이 2개의 곱셈 연산을 1개의 곱셈 연산으로 줄일 수 있다. 이와 같은 방법을 이용하여 그림 6의 (a)와 같은 SFP의 기본회로를 구현하였다. SFP의 기본회로는 1개의 곱셈 연산기, 3개의 덧셈 연산기, 1개의 시프트 연산기로 이루어져 있다.

표준에 정의된 HEVC의 Intra\_Planar 모드 연산의 경우, 식 (12)와 같이 4개의 곱셈 연산으로 이루어지는 4화소간의 식으로 표현된다. 식 (12)는 식 (13)으로 변형가능하며, 식 (12)에서 사용한 4개의 곱셈 연산을 식 (13)과 같이 2개의 곱셈 연산으로 줄일 수 있다. 또한식 (13)은 식 (11)의 연산 구조가 2번 반복됨을 알 수있다. 그러므로 SFP의 기본회로를 2번 사용하여 Intra\_Planar 모드 연산 수행이 가능하다.

$$\begin{split} Z_p &= \{ (\beta_{p1} - \alpha_{p1}) \times A_{p1} + \alpha_{p1} \times B_{p1} + \\ &\quad (\beta_{p2} - \alpha_{p2}) \times A_{p2} + \alpha_{p2} \times B_{p2} + \gamma_p \} \gg (\delta_p + 1) \end{split} \tag{12}$$

$$\begin{split} Z_p &= [\{\alpha_{p1} \times (B_{p1} - A_{p1})\} \gg \delta_p + A_{p1} + \\ \{\alpha_{p2} \times (B_{p2} - A_{p2})\} \gg \delta_p + A_{p2} + 1] \gg 1 \end{split} \tag{13}$$

이와 같은 방법을 이용하여 그림 6의 (b)와 같은 SFP 공통 연산 회로를 구현하였다. SFP는 1개의 곱셈

그림 6. SFP의 공통 연산 회로 Fig. 6. Common operation circuit of SFP.

연산기, 4개의 덧셈 연산기, 2개의 시프트 연산기로 이루어져 있다. Intra\_Planar 모드의 경우, 예측 데이터 생성에 2사이클이 소요되고, 나머지 예측모드 연산과 강한 참조 샘플 필터 연산의 경우 1사이클이 소요된다.

성능을 향상시키기 위해 SFP 공통 연산 회로 16개를 병렬로 사용하여 GSFP 회로를 설계하였다. GSFP는 강 한 참조 샘플 필터를 거치는 경우 사이클 당 필터링된 참조 샘플 데이터를 16개 출력하고, HEVC의 Intra\_Planar 모드 연산의 경우 2사이클 당 16개의 예측 데이터를 출력한다. 그 밖의 HEVC 예측모드 연산의 경우 사이클 당 16개의 예측 데이터를 출력한다.

#### 4. 효율적인 내부 버퍼 사용과 Intra\_Plane 연산

H.264의 경우 33x8-bit, HEVC의 경우 67x8-bit의 입력 참조 샘플 데이터 저장 공간이 필요하다. 참조 샘플 필터의 결과도 저장해야 하므로 전체적으로 필요한 저장 공간은 2배가 된다. 이를 그대로 구현하면 총 200x8-bit의 저장 공간이 필요하다. 하지만 멀티 디코더에서 H.264 인트라 예측과 HEVC 인트라 예측이 동시에 진행될 수 없고, 참조 샘플 필터를 거치기 전의 데이터는 참조 샘플 필터를 거친 후 더 이상 필요가 없다. 따라서 본 논문에서는 효율적인 저장 공간 활용을 위하여 참조 샘플 필터링 전후의 데이터를 저장하는 79x8-bit 크기의 Sample Buffer(그림 3)를 사용한다.

H.264의 Intra\_Plane 모드의 경우, 다른 예측모드 연 산과는 다르게 예측 데이터를 생성하기 전 표준에 정의 된 H, V, a, b, c에 대한 연산<sup>[2]</sup>을 미리 수행해야 한다.

표 1. 블록 크기별 소요 사이클

Table 1. Required cycles for various block sizes.

(P: Intra\_Planar or Intra\_Plane mode)

| (  |       |     |    |      |    |     |      |     |     |      |

|----|-------|-----|----|------|----|-----|------|-----|-----|------|

| 구  | 블록    | 데이터 | 참조 | 스샘플  | 예측 | 두 데 | 이터   | ą   | 는 소 | 요    |

|    |       |     | 필' | 터링   |    | 생성  |      | 사이클 |     |      |

| 분  | 크기    | 입력  | DC | Else | DC | Р   | Else | DC  | Р   | Else |

| H. | 4x4   | 1   | 1  | 0    | 1  | -   | 1    | 3   | -   | 2    |

| 2  | 휘도8x8 | 1   | 2  | 1    | 4  | _   | 4    | 7   | _   | 6    |

| 6  | 16x16 | 1   | 2  | 0    | 16 | 67  | 16   | 19  | 68  | 17   |

| 4  | 색차8x8 | 1   | 1  | 0    | 19 | 19  | 4    | 6   | 21  | 5    |

| Н  | 4x4   | 1   | 1  | 0    | 2  | 2   | 1    | 3   | 3   | 2    |

| Е  | 8x8   | 1   | 1  | 1    | 4  | 8   | 4    | 6   | 10  | 6    |

| V  | 16x16 | 1   | 2  | 2    | 16 | 32  | 16   | 19  | 35  | 19   |

| С  | 32x32 | 1   | 4  | 4    | 64 | 128 | 64   | 69  | 133 | 69   |

H와 V, b와 c는 각각 동일한 연산 구조를 지니고 있다. 따라서 본 논문에서는 H와 V의 연산기를 공유하고, b와 c의 연산기를 공유한다. Intra\_Plane 모드 연산은 초기 3사이클 동안 H, V, a, b, c 연산을 수행하고 4번째 사이클부터 사이클마다 4개의 예측 데이터를 생성한다.

## Ⅳ. 실험 결과

본 논문에서 제안한 H.264/HEVC 통합 인트라 예측 회로는 Verilog HDL(Hardware Description Language)을 이용하여 RTL(Register Transfer Level)로 설계하였다. Cadence사의 NC-veilog를 사용하여 기능을 검증하였고, Synopsys사의 Design Compiler와 130nm 표준셀 라이브러리를 이용하여 게이트 수준의 회로로 합성하였다. 게이트 수준 회로로 합성된 통합 인트라 예측회로는 참조 샘플 패딩, 약한 참조 샘플 필터 연산, 강한 참조 샘플 필터 연산, H.264의 예측모드 연산, HEVC의 예측모드 연산 기능을 모두 포함하여 69,694 게이트이고, 최대 동작 주파수는 157MHz이다.

제안하는 회로는 H.264, HEVC의 블록별로 표 1에서 표시한 만큼의 사이클을 필요로 한다. H.264에서는 색차 8x8 Intra\_Plane 모드의 처리 속도가 가장 떨어지고, HEVC에서는 4x4 인트라 예측 Intra\_Planar 모드의 처리 속도가 가장 떨어지는 것을 알 수 있다.

H.264의 경우 Full HD(1,920x1,080) 영상 처리 속도 가 100 fps 이상이므로 Full HD 영상을 실시간으로 처리할 수 있다. 또한 HEVC의 경우 4K-UHD 급 영상처리 속도가 100~280 fps 이므로 제안하는 회로는 4K-UHD 영상을 실시간으로 처리할 수 있다.

표 2. 합성 결과 비교

Table 2. Comparison of synthesis results.

| 구분       | 논문 <sup>[4]</sup> | 논문 <sup>[5]</sup> | 논문 <sup>[6]</sup> | 제안하는 회로     |  |

|----------|-------------------|-------------------|-------------------|-------------|--|

| 지원하는 표준  | HEVC              | HEVC              | HEVC              | H.264, HEVC |  |

| 게이트 수    | 40,500            | 43,200            | 70,300            | 69,694      |  |

| SRAM     | 무                 | 4.9KB             | 무                 | 무           |  |

| 약한 필터    | 유                 | 유                 | 유                 | 유           |  |

| 강한 필터    | 무                 | 무                 | =                 | 유           |  |

| 공정       | 130nm             | 90nm              | 65nm              | 130nm       |  |

| 최대 동작    | 164MHz            | 200MHz            | 9F0MII.           | 157MHz      |  |

| 주파수      | 104MHZ            | ZUUNIHZ           | 250MHz            |             |  |

| 초당 프레임   | 70 for            | 10 fra a          | 241~482           | 100~200 for |  |

| (4K-UHD) | 79 fps            | 48 fps            | fps               | 100~280 fps |  |

표 3. 참조 샘플 필터와 합성 결과

Table 3. Synthesis results with reference sample filter.

| 구분            | 논문 <sup>[7]</sup> | 논문 <sup>[8]</sup> | 논문 <sup>[9]</sup> | 제안하는<br>회로  |  |

|---------------|-------------------|-------------------|-------------------|-------------|--|

| 지원하는 표준       | H.264             | H.264             | H.264             | H.264, HEVC |  |

| 참조 샘플 필터      | 무                 | 무                 | 무                 | 유           |  |

| 지원하는<br>블록 크기 | 휘도:4x4,           | 휘도:4x4,           | 휘도:4x4,           | 휘도:4x4,     |  |

|               | 16x16             | 16x16             | 16x16             | 8x8, 16x16  |  |

|               | 색차:8x8            | 색차:8x8            | 색차:8x8            | 색차:8x8      |  |

| 공정            | 130nm             | 130nm             | 180nm             | 130nm       |  |

| 게이트 수         | 26,607            | 9,464             | 21,000            | 69,694      |  |

| 초당 프레임        | CO from           | 00 f              | 570 for           | 230 fps     |  |

| (Full HD)     | 60 fps            | 38 fps            | 578 fps           |             |  |

표 2는 제안하는 회로의 합성 결과를 비교한 것이다. 표 2에 나타나 있듯이, 제안하는 회로는 논문<sup>[4]</sup>보다 성능이 26.5% 증가하였음을 볼 수 있다. 또한 논문<sup>[5]</sup>보다 성능이 2배 이상 향상, 논문<sup>[6]</sup>보다 2배 정도 감소된 것으로 볼 수 있다. 그러나 제안하는 회로에서 사용한 130nm 공정이 아닌 각각 90nm 공정, 65nm 공정을 사용한 결과이므로 직접적인 비교가 불가능하며, 공정의차이를 고려할 경우 성능 감소가 크지 않을 것으로 추정된다.

표 3은 제안하는 회로와 논문<sup>[7]</sup>, 논문<sup>[8]</sup>, 논문<sup>[9]</sup>를 비교한 것이다. 표 3에 나타나 있듯이, 제안하는 회로는 비교 논문들 보다 대부분 성능이 우수하고 크기는 증가하였음을 알 수 있다. 하지만 제안하는 회로는 H.264와 HEVC를 동시에 지원하고, 비교 논문들은 H.264만 지원하기 때문에 단순 비교를 하는 것은 어렵다.

제안하는 회로 크기는 논문 $^{[4]}$ , 논문 $^{[5]}$ 에 비해 크고, 논문 $^{[6]}$ 과 비슷하다. 하지만 이 논문들은  $\mathrm{H.264}$ 를 포함하지

표 4. 회로 크기에 대한 추정치 비교 Table 4. Comparison of estimated circuit sizes.

| 7 11 | 논문 <sup>[4]</sup>  | 논문 <sup>[4]</sup>  | 논문 <sup>[4]</sup>  | 제안하는   |  |

|------|--------------------|--------------------|--------------------|--------|--|

| 구분   | +논문 <sup>[7]</sup> | +논문 <sup>[8]</sup> | +논문 <sup>[9]</sup> | 회로     |  |

| 지원하는 | H.264,             | H.264,             | H.264,             | HEVC,  |  |

| 표준   | HEVC               | HEVC               | HEVC               | H.264  |  |

| 게이트  | 100,131            | 82,988             | 94,524             | 60.604 |  |

| 수    | (추정)               | (추정)               | (추정)               | 69,694 |  |

않을 뿐만 아니라 HEVC의 강한 참조 샘플 필터를 포함하지 않았다. 강한 참조 샘플 필터 연산기 하나 당 약 1,032 게이트로 구현 가능하므로, 논문<sup>[4]</sup>, 논문<sup>[5]</sup>, 논문<sup>[6]</sup>에서 제시하는 연산 속도에 지장을 주지 않기 위해서는 각각 32개, 8개, 16개의 강한 참조 샘플 필터 연산기를 병렬로 사용하여야 한다. 표 4는 합성에 사용한 공정의 종류, 강한 참조 샘플 필터의 크기, H.264와 HEVC의지원 여부를 고려하여 추정한 회로의 크기와 제안하는 회로를 비교한 결과이다. 표 4에서 볼 수 있듯이 제안하는 회로의 면적은 논문<sup>[4]</sup>+논문<sup>[7]</sup>보다 약 30%, 논문<sup>[4]</sup>+ 논문<sup>[8]</sup>보다 약 16%, 논문<sup>[4]</sup>+ 논문<sup>[9]</sup>보다 약 26% 감소한 것을 알 수 있다.

# V. 결 론

본 논문에서 제안한 회로는 현재 가장 주목을 받고 있는 비디오 압축 표준인 HEVC와 H.264를 동시에 지 원할 수 있는 멀티 디코더 용 인트라 예측 회로이다. H.264와 HEVC의 참조 샘플 데이터 연산과 dcVal 연 산, 예측 데이터 생성 연산을 분석하여 공통적으로 사 용되는 연산기들을 공유함으로써 PDSF 회로를 설계하 였다. 또한 HEVC의 강한 참조 샘플 필터 연산과 모든 예측 데이터 생성 연산을 분석하여 공통적으로 사용되 는 연산기들을 공유함으로써 GSFP 회로를 설계하였다. 이와 같이 PDSF 회로와 GSFP 회로를 설계하여 활용 함으로써 인트라 예측 회로 전체의 크기를 줄일 수 있 었다. 또한 내부 버퍼를 재사용하고 Intra\_Plane 연산에 서의 공통 연산을 공유함으로써 회로의 크기를 더욱 감 소시켰다. 회로의 동작 속도를 향상시키기 위해 필요한 연산기들을 병렬로 사용하여 4K-UHD 영상을 실시간 으로 처리할 수 있도록 하였다. 제안한 회로의 크기는 69,694 게이트이며, 최대 동작주파수는 157MHz이다. 4K-UHD HEVC 영상을 초당 100 ~ 280 프레임까지 처 리할 수 있고. Full HD H.264 영상은 초당 230 프레임 까지 처리할 수 있다.

#### **REFERENCES**

- [1] B. Bross, W. J. Han, J. R. Ohm, G. J. Sullivan, Y. K. Wang and T. Wiegand, "High Efficiency Video Coding (HEVC) Text Specification Draft 10 (for FDIS & Last Call)," The Joint Collaborative Team on Video Coding (JCT-VC), JCTVC-L1003\_v34, January, 2013.

- [2] ITU-T, "Recommendation and International Standard of Joint Video Specification," ITU-T Recommendation H.264/ISO/IEC 14496-10 AVC, October, 2004.

- [3] Bong-Hee Bae, Jin-Hyeung Kong, "A Design of Pipelined-parallel CABAC Decoder Adaptive to HEVC Syntax Elements," Journal of the Institute of Electronics and Information Engineers, vol.52, no.5, pp.155-164, May, 2015.

- [4] Hongkyun Jung, Kwangki Ryoo, "An Intra Prediction Hardware Architecture Design for Computational Complexity Reduction of HEVC Decoder," Journal of Korea Institue of Information and Communication Engineering, vol.17, no.5, pp.1203–1212, January, 2013.

- [5] Chao-Tsung Huang, Mehul Tikekar, Anantha P.Chandrakasan, "Memory-Hierarchical Mode-Adaptive **HEVC** Intra Prediction Architecture for Quad Full HD Video Decoding," IEEE Transactions on Very Large Scale Integration Systems, vol. 22, Issue.7, pp.1515-1525, August, 2013.

- [6] Choi Seunghwan, "Hardware Architecture Design for HEVC Decoder Using Parallel Process: Intra Prediction and Inter Prediction," Master's Thesis of Myongji University, 2015.

- [7] Jihey Yoo, Seonyoung Lee, Kyeongsoon Cho, "Design of High-Performance Intra Prediction Circuit for H.264 Video Decoder," in Proc. of IEEK Conf. on 2009 SoC Conference, pp.1952-1955, Jeonju, Republic of Korea, May, 2009

- [8] Jaeoh Shim, Seonyoung Lee, Kyeongsoon Cho, "Design of Intra Prediction Circuit for H.264 Decoder Sharing Common Operations Unit," Journal of the Institute of Electronics and Information Engineers, vol.45, SD, no.9, pp.103-109, May, 2009.

- [9] Muhammad Nadeem, Stephan Wong, Georgi Kuzmanov, "An Efficient Hardware Design for Intra-prediction in H.264/AVC Decoder," Saudi International Electronics Communications and Photonics Conference, pp.1-6, April, 2011.

----- 저 자 소 개 -----

유 상 현(정회원)

2013년 2월 한국외국어대학교

전자공학과 학사 졸업.

2016년 8월 한국외국어대학교

전자공학과 석사 졸업.

조 경 순(평생회원) 전자공학회논문지 제 51권 제 11호 참조

<주관심분야 : SoC 설계>