# Accurate Tunable-Gain 1/x Circuit Using Capacitor Charging Scheme

Byung-Do Yang and Seo Weon Heo

This paper proposes an accurate tunable-gain 1/x circuit. The output voltage of the 1/x circuit is generated by using a capacitor charging time that is inversely proportional to the input voltage. The output voltage is independent of the process parameters, because the output voltage depends on the ratios of the capacitors, resistors, and current mirrors. The voltage gain of the 1/x circuit is tuned by a 10-bit digital code. The 1/x circuit was fabricated using a 0.18 µm CMOS process. Its core area is 0.011 mm<sup>2</sup> (144 µm × 78 µm), and it consumes 278 µW at  $V_{DD} = 1.8$  V and  $f_{CLK} = 1$  MHz. Its error is within 1.7% at  $V_{IN} = 0.05$  V to 1 V.

Keywords: 1 over *x*, analog divider, process independent, capacitor charging, tunable gain.

### I. Introduction

The analog 1/x circuit is used in analog dividers, filters, fuzzy control, neural networks, and A/D converters [1]–[6]. Several circuits for the 1/x function have been proposed. A voltage-mode analog divider is accurate, but it needs a highly accurate wide-range voltage controlled oscillator [1]. A current-mode 1/x circuit using weak-inversion MOSFETs has low accuracy due to very low reference and input currents, which are only under a few nanoamperes [2]. A voltage-mode analog divider [3], voltage-mode 1/x circuit [4], and current-mode analog divider [5] have good accuracy; however, their outputs significantly change due to device parameters and temperature.

In this paper, an accurate tunable-gain 1/x circuit is proposed. The output voltage of the 1/x circuit is generated by using a capacitor charging time that is inversely proportional to the input voltage. The output voltage is independent of process parameters, because all variations from active and passive devices are canceled out. In addition, the voltage gain of the 1/x circuit is tuned by a 10-bit digital input code.

The rest of this paper is organized as follows. Section II describes the proposed tunable-gain 1/x circuit. Section III shows the measurement results of the fabricated chip. Finally, conclusions are drawn in Section IV.

#### II. Proposed 1/x Circuit

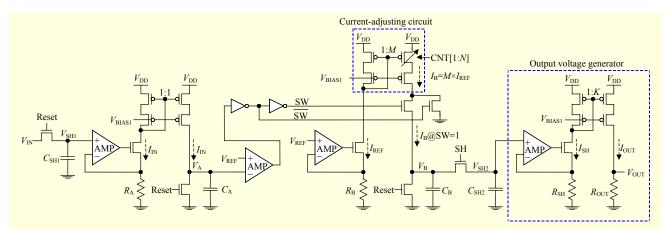

The proposed 1/x circuit generates an output voltage  $(V_{\text{OUT}})$  that is inversely proportional to the input voltage  $(V_{\text{IN}})$ . Figures 1 and 2 show the schematic and operation of the 1/x circuit, respectively. Initially, the capacitor  $C_{\text{SH1}}$  samples and holds  $V_{\text{IN}}$  by the reset signal so that the voltage of  $C_{\text{SH1}}$  ( $V_{\text{SH1}}$ ) is updated to  $V_{\text{IN}}$ . The reset signal also discharges the capacitors

Manuscript received May 13, 2014; revised Dec. 28, 2014; accepted Jan. 2, 2015.

This research was supported by the Basic Science Research Program through the National Research Foundation of Korea (NRF) funded by the Ministry of Education, Science and Technology (2015R1D1A3A01017756). The chip fabrication was supported by the IC Design Education Center (IDEC).

Byung-Do Yang (bdyang@cbnu.ac.kr) is with the Department of Electronics Engineering, Chungbuk National University, Cheongju, Rep. of Korea.

Seo Weon Heo (corresponding author, seoweon.heo@hongik.ac.kr) is with the School of Electronic & Electrical Engineering, Hongik University, Seoul, Rep. of Korea.

Fig. 1. Schematic of proposed 1/x circuit.

Fig. 2. Operation of proposed 1/x circuit.

$C_{\rm A}$  and  $C_{\rm B}$  to the ground. The input voltage  $V_{\rm IN}$  is converted to a current  $I_{\rm IN}$  by an operational amplifier, a resistor  $R_{\rm A}$ , and a current mirror. The current  $I_{\rm IN}$  charges capacitor  $C_{\rm A}$  during the capacitor charging time ( $T_{\rm CHG}$ ) until the voltage of  $C_{\rm A}$  ( $V_{\rm A}$ ) reaches the reference voltage ( $V_{\rm REF}$ ). When  $V_{\rm A} = V_{\rm REF}$ , the charge stored in  $C_{\rm A}$  ( $Q_{\rm A} = C_{\rm A} \times V_{\rm REF}$ ) is equal to the product of  $I_{\rm IN}$  and  $T_{\rm CHG}$ .

$$V_{\rm SH1} = V_{\rm IN},\tag{1}$$

ETRI Journal, Volume 37, Number 5, October 2015 http://dx.doi.org/10.4218/etrij.15.0114.0577

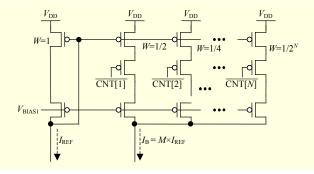

Fig. 3. Current-adjusting circuit.

$$I_{\rm IN} = V_{\rm SH1} / R_{\rm A} = V_{\rm IN} / R_{\rm A}, \qquad (2)$$

$$Q_{\rm A} = C_{\rm A} \times V_{\rm REF} = I_{\rm IN} \times T_{\rm CHG}.$$

(3)

From equations (2) and (3), the capacitor charging time ( $T_{CHG}$ ) is expressed as follows:

$$T_{\rm CHG} = \frac{C_{\rm A} \times V_{\rm REF}}{I_{\rm IN}} = \frac{R_{\rm A} \times C_{\rm A} \times V_{\rm REF}}{V_{\rm IN}}.$$

(4)

A reference current ( $I_{\text{REF}} = V_{\text{REF}}/R_{\text{B}}$ ) is generated from the reference voltage ( $V_{\text{REF}}$ ) by an operational amplifier and a resistor  $R_{\text{B}}$ . In the current-adjusting circuit in Fig. 3, the reference current ( $I_{\text{REF}}$ ) is multiplied by M for a current  $I_{\text{B}}$  (=  $M \times I_{\text{REF}}$ ) using a binary weighted current mirror and N-bit digital control code (CNT[1:N]).

$$I_{\rm B} = M \times I_{\rm REF} = M \times \frac{V_{\rm REF}}{R_{\rm B}}, \text{ where } M = \sum_{1}^{N} \frac{1}{2^{K}} \text{CNT}[K]. (5)$$

During  $T_{\text{CHG}}$ , the switch (SW) turns on, and the current  $I_{\text{B}}$  charges capacitor  $C_{\text{B}}$  such that the charge stored in  $C_{\text{B}}$  ( $Q_{\text{B}} = C_{\text{B}} \times V_{\text{B}_{-}\text{MAX}}$ ) becomes the product of  $I_{\text{B}}$  and  $T_{\text{CHG}}$ , where  $V_{\text{B}_{-}\text{MAX}}$  is the maximum voltage of  $C_{\text{B}}$  after the capacitor charging operation.

$$Q_{\rm B} = I_{\rm B} \times T_{\rm CHG} = C_{\rm B} \times V_{\rm B_{-MAX}}.$$

(6)

From equations (4), (5), and (6),  $V_{B_MAX}$  is expressed as follows:

$$V_{\rm B_MAX} = \frac{I_{\rm B} \times T_{\rm CHG}}{C_{\rm B}} = M \times \frac{R_{\rm A}}{R_{\rm B}} \times \frac{C_{\rm A}}{C_{\rm B}} \times \frac{V_{\rm REF}^2}{V_{\rm IN}},$$

(7)

where  $R_A = R_B$  and  $C_A = C_B$ ;  $V_{B_MAX}$  can be simplified as follows:

$$V_{\rm B_MAX} = M \times \frac{V_{\rm REF}^2}{V_{\rm IN}}.$$

(8)

Here,  $V_{\text{B}_{\text{MAX}}}$  is inversely proportional to  $V_{\text{IN}}$ , which is a function of 1/x. The tunable-gain 1/x circuit is achieved by changing the value of *M* of the current-adjusting circuit.

Although  $V_{B_MAX}$  is inversely proportional to  $V_{IN}$ ,  $V_B$  changes during the capacitor charging operation. A sampling circuit composed of a sampling switch and a capacitor is used for the continuous output voltage of the 1/x function. After every capacitor charging operation, the capacitor  $C_{SH2}$  samples and holds  $V_{B_MAX}$  by the SH (sample-and-hold) signal. If  $C_{SH2}$  is much smaller than  $C_B$ , then the voltage of  $C_{SH2}$  ( $V_{SH2}$ ) becomes  $V_{B_MAX}$ .

$$V_{\rm SH2} = V_{\rm B MAX}.$$

(9)

An output-voltage generator with an operational amplifier, a current mirror, and two resistors ( $R_{\text{SH}}$  and  $R_{\text{OUT}}$ ) is designed, because the minimum output voltage of the 1/x circuit is 0 V. The designed output-voltage generator makes 0 V easily by reducing the current going through the resistor  $R_{\text{OUT}}$ . The output current ( $I_{\text{OUT}}$ ) is K-times larger than  $I_{\text{SH}} (= V_{\text{SH2}}/R_{\text{SH}})$ . The output voltage ( $V_{\text{OUT}}$ ) is expressed as follows:

$$V_{\rm OUT} = K \times \frac{R_{\rm OUT}}{R_{\rm SH}} \times V_{\rm SH2}.$$

(10)

From equations (8), (9), and (10),  $V_{OUT}$  is simplified as follows:

$$V_{\text{OUT}} = M \times \frac{V_{\text{REF}}^2}{V_{\text{IN}}}, \text{ where } R_{\text{SH}} = K \times R_{\text{OUT}}.$$

(11)

When a resistive load is connected to the output node,  $V_{OUT}$  changes in such a way that an additional voltage buffer is required. However, in many applications, the 1/x circuit has a high-impedance output; thus, no voltage buffer is required, because the 1/x circuit drives the other circuits in the same chip.

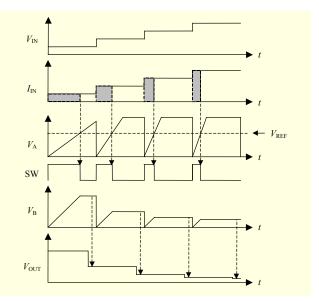

Figure 4 shows the waveforms of the 1/x circuit when the input voltage ( $V_{\rm IN}$ ) changes. The current  $I_{\rm IN}$  charging the capacitor  $C_{\rm A}$  is proportional to  $V_{\rm IN}$  such that the charging time ( $T_{\rm CHG}$ ) is inversely proportional to  $V_{\rm IN}$  when the voltage of  $C_{\rm A}$  ( $V_{\rm A}$ ) reaches  $V_{\rm REF}$ . Therefore, the maximum voltage of  $C_{\rm B}$  ( $V_{\rm B,MAX}$ ) is also inversely proportional to  $V_{\rm IN}$ , because  $C_{\rm B}$  is

Fig. 4. Waveforms of 1/x circuit.

Table 1. Design and adjustable parameters of 1/x circuit.

|                       | $C_{\rm A}$ =1 pF, $C_{\rm B}$ =1 pF, $C_{\rm SH}$ =0.1 pF                 |  |  |

|-----------------------|----------------------------------------------------------------------------|--|--|

| Design parameters     | $R_{\rm A}$ =40 kΩ, $R_{\rm B}$ =160 kΩ                                    |  |  |

|                       | $K=5, R_{\text{OUT}}=10 \text{ k}\Omega, R_{\text{SH}}=50 \text{ k}\Omega$ |  |  |

| Adjustable parameters | <i>M</i> =0–1 for CNT[1:8]                                                 |  |  |

|                       | $V_{\rm REF} = 0.1  {\rm V} - 1  {\rm V}$                                  |  |  |

| Gain                  | 0–1                                                                        |  |  |

|                       |                                                                            |  |  |

charged with a constant current  $I_{\rm B}$  during  $T_{\rm CHG}$ . The output voltage ( $V_{\rm OUT}$ ) becomes a continuous voltage that is inversely proportional to  $V_{\rm IN}$  by sampling  $V_{\rm B MAX}$  every clock cycle.

From equations (7), (9), and (10), the output voltage of the 1/x circuit is expressed as follows:

$$V_{\rm OUT} = M \times K \times \frac{R_{\rm OUT}}{R_{\rm SH}} \times \frac{R_{\rm A}}{R_{\rm B}} \times \frac{C_{\rm A}}{C_{\rm B}} \times \frac{V_{\rm REF}^2}{V_{\rm IN}}.$$

(12)

The 1/x circuit was implemented with a 0.18 µm CMOS process at  $V_{\text{DD}} = 1.8$  V. By applying the design parameters in Table 1, (12) can be simplified as follows:

$$V_{\text{OUT}} = \frac{\text{Gain}}{V_{\text{IN}}}, \text{ where Gain} = \frac{M}{4} \times V_{\text{REF}}^2.$$

(13)

The gain is controlled by the parameters M and  $V_{\text{REF}}$ . The parameter M can be changed between "0" and "1" by the 10-bit digital control code (CNT[1:10]), and the reference voltage  $V_{\text{REF}}$  can be changed between 0.1 V and 1 V. Therefore, the allowable range of the gain of the 1/x circuit is from "0" to "1."

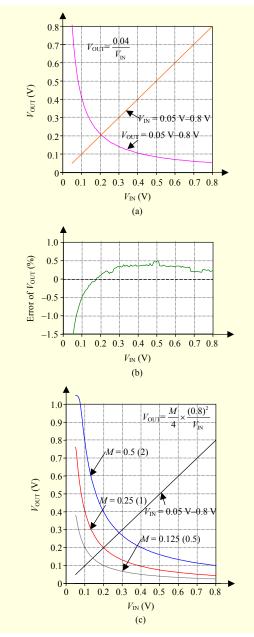

Fig. 5. Simulation results of 1/x circuit at M = 0.25 and  $V_{\text{REF}} = 0.8 \text{ V}$ : (a)  $V_{\text{OUT}}$  vs.  $V_{\text{IN}}$ , (b) accuracy of  $V_{\text{OUT}}$ , and (c)  $V_{\text{OUT}}$  vs. M.

Figures 5(a) and 5(b) show the simulation results of the 1/x circuit at M = 0.25 and  $V_{\text{REF}} = 0.8$  V. The 1/x circuit has errors less than 0.5% and 1.5% for  $V_{\text{IN}} = 0.1$  V to 0.8 V and  $V_{\text{IN}} = 0.05$  V to 0.8 V, respectively. The error increases when  $V_{\text{IN}}$  is under 0.1 V, because the offset voltages of the amplifiers become the more dominant factors as  $V_{\text{IN}}$  decreases. Figure 5(c) shows the gain variations of the 1/x circuit according to M at  $V_{\text{REF}} = 0.8$  V. The simulation results in Table 2 show the high accuracy and wide input and output ranges of the 1/x circuit.

In (12), the output of the proposed 1/x circuit is independent

| Table | 2. | Simulation | results | of | 1/x | circuit. |

|-------|----|------------|---------|----|-----|----------|

|-------|----|------------|---------|----|-----|----------|

| Process                       | 0.18 µm CMOS                                                      |

|-------------------------------|-------------------------------------------------------------------|

| Supply voltage $(V_{DD})$     | 1.8 V                                                             |

| Clock frequency ( $f_{CLK}$ ) | 1 MHz                                                             |

| Input voltage ( $V_{IN}$ )    | 0.05 V–0.8 V                                                      |

| Output voltage ( $V_{OUT}$ )  | 0 V–1 V                                                           |

| Accuracy of VOUT              | $-0.5\%$ < Error < 0.5% for $V_{\rm IN}$ = 0.1 V–0.8 V            |

|                               | $-1.5\%$ < Error < 0.5% for $V_{\rm IN}$ = 0.05 V–0.8 V           |

| Simulation conditions         | $V_{\rm OUT} = 0.04 / V_{\rm IN} @ M = 0.25, V_{\rm REF} = 0.8 V$ |

Table 3. Error sources of 1/x circuit.

| Source                      | Number | Standard deviation ( $\sigma$ )         |

|-----------------------------|--------|-----------------------------------------|

| Offset voltage of amplifier | 4      | 0.7%<br>(1.4 mV @ $V_{\rm IN} = 0.2$ V) |

| Mismatch of current mirror  | 3      | 0.18%                                   |

| Resistor mismatch           | 2      | 0.07%                                   |

| Capacitor mismatch          | 1      | 0.07%                                   |

| Total error                 | N/A    | 1.45%                                   |

of the process parameters. However, the output is still affected by the mismatches of the devices. The main error sources are the offset voltages of amplifiers (AMPs), the mismatches of current mirrors, resistor mismatches ( $R_A$  and  $R_B$ ,  $R_{OUT}$  and  $R_{SH}$ ), and capacitor mismatches ( $C_A$  and  $C_B$ ). In addition, the output is affected by the reference voltage ( $V_{REF}$ ). The reference voltage comes from either an internal bandgap reference (BGR) circuit or an external voltage source. In this design,  $V_{REF}$ comes from an external voltage source so as to exhibit the variations of the 1/x circuit exactly. Table 3 shows the Monte Carlo simulation results of the error sources in the implemented 1/x circuit with a 0.18 µm CMOS process. The standard deviation ( $\sigma$ ) of the total error is 1.45%. The largest error comes from the AMPs ( $\sigma$ =0.7%).

The maximum clock frequency ( $f_{CLK}$ ) for the voltage conversion of the 1/x circuit is determined by the capacitor charging time ( $T_{CHG} = R_A \times C_A \times V_{REF}/V_{IN}$ ) in (4). When  $R_A =$ 40 kΩ,  $C_A = 1$  pF, and  $V_{REF} = 0.8$  V, the maximum capacitor charging time becomes 0.64 µs for the lowest allowable input voltage ( $V_{IN} = 0.05$  V). In the simulations and experiments, a clock frequency of 1 MHz was used to cover the 0.64 µs capacitor charging time. A higher clock frequency can be used by reducing the maximum capacitor charging time with the parameters  $R_A$ ,  $C_A$ , and  $V_{REF}$ . A lower clock frequency is recommended to save power consumption, because power consumption is proportional to the conversion frequency. The small capacitors ( $C_A = 1$  pF,  $C_B = 1$  pF, and  $C_{SH} = 0.1$  pF) are implemented to reduce power consumption and chip area, but they are weak from leakage currents and noises, which increase the error of the 1/x circuit. The larger capacitors,  $C_A$ ,  $C_B$ , and  $C_{SH}$ , can improve the accuracy of the 1/x circuit.

#### III. Measurement Results

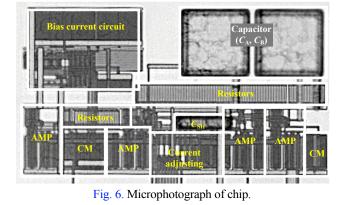

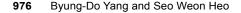

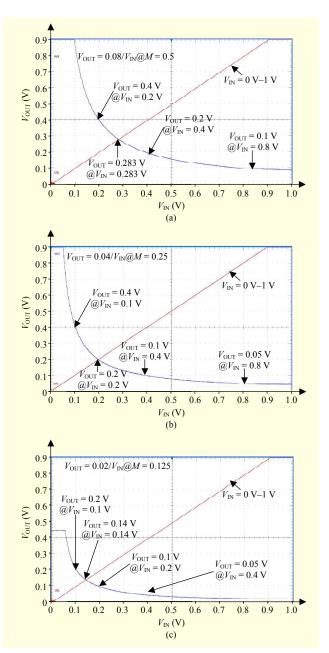

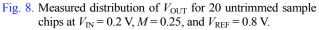

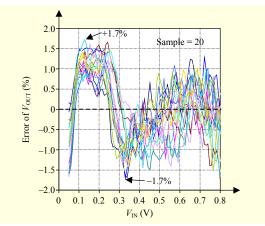

The proposed 1/x circuit was fabricated using a 0.18 µm CMOS process. Figure 6 shows a microphotograph of the chip. The chip occupies an area of 0.011 mm<sup>2</sup> (144  $\mu$ m × 78  $\mu$ m) and consumes 278  $\mu$ W at  $V_{DD}$  = 1.8 V and  $f_{CLK}$  = 1 MHz. Figure 7 shows the measured waveforms of  $V_{OUT}$  according to  $V_{\rm IN}$  (= 0 V to 1 V) at  $V_{\rm REF}$  = 0.8 V and M = 0.5, 0.25, and 0.125. The function of the proposed 1/x circuit does not have any process parameters theoretically, but the output voltage of the proposed 1/x circuit is affected by process variations, such as the offset voltages of the AMPs; the switching delays of the AMPs; and the mismatches in capacitors, resistors, and current mirrors. Figure 8 shows the measured distribution of  $V_{OUT}$  for 20 untrimmed sample chips at  $V_{IN} = 0.2$  V, M = 0.25, and  $V_{REF}$ = 0.8 V. The  $V_{\text{OUT}}$  of each chip is measured at  $V_{\text{IN}}$  = 0.2 V to show the distribution of  $V_{OUT}$  according to process variations. Theoretically,  $V_{\text{OUT}} = 0.2 \text{ V}$  at  $V_{\text{IN}} = 0.2 \text{ V}$ , because the function of the 1/x circuit is  $V_{\text{OUT}} = 0.04/V_{\text{IN}}$  at M = 0.25 and  $V_{\text{REF}} =$ 0.8 V. The mean ( $\mu$ ) and standard deviation ( $\sigma$ ) of  $V_{OUT}$  for 20 samples were 200 mV and 3.21 mV (1.61%), respectively. The measured 20 sample chips showed a maximum and minimum  $V_{\rm OUT}$  of 205.7 mV and 194.7 mV, respectively. Therefore, the maximum difference of  $V_{\text{OUT}}$  ( $\Delta V_{\text{OUT}}$ ) was 11 mV (5.48%). The change in  $V_{\text{OUT}}$  due to the process variations can be trimmed by the current-adjusting circuit. Figure 9 shows the measured accuracies of  $V_{OUT}$  for 20 trimmed sample chips at M = 0.25 and  $V_{\text{REF}}$  = 0.8 V. The 20 trimmed 1/x circuits have errors between +1.7% and -1.7% for  $V_{IN} = 0.05$  V to 0.8 V.

Various 1/x circuit chips are compared in Table 4. The proposed 1/x circuit has a larger normalized input/output range

Fig. 7. Measured waveforms of  $V_{OUT}$  vs.  $V_{IN}$  (= 0 V to 1 V) at  $V_{REF}$  = 0.8 V: (a) M = 0.5, (b) M = 0.25, and (c) M = 0.125.

of 1 to 20 compared to other 1/x circuits (from 1 to 2.67 to 1 to 14). The normalized input/output range is the lowest value among the input and output ranges normalized with their minimum values. The previous 1/x circuits [3]–[5] have smaller errors of 1.7%. However, all previous 1/x circuits [3]–[6] have additional linearity errors due to PVT (process parameters, supply voltage, temperature) variations, as shown in Table 5. The additional linearity errors come from the parameters  $K (= \mu C_{OX} W/L)$ ,  $g_m (= \sqrt{2KI_p})$ , and  $V_T$  of the

|                               | JSSC 1995 [3] | IEICE 2003 [4] | TCAS-II 2005 [5] | MWCAS 2012 [6]  | This work    |

|-------------------------------|---------------|----------------|------------------|-----------------|--------------|

| Process                       | 2 µm CMOS     | 0.5 μm CMOS    | 0.5 µm CMOS      | 0.5 µm CMOS     | 0.18 µm CMOS |

| $V_{\rm DD}({ m V})$          | 5             | 1.5            | 1.5              | 1.5             | 1.8          |

| $V_{\rm SS}({ m V})$          | -5            | -1.5           | -1.5             | -1.5            | 0            |

| Power (µW)                    | N/A           | 240            | 220              | 80              | 278          |

| Area (mm <sup>2</sup> )       | N/A           | N/A            | N/A              | 0.032           | 0.011        |

| $V_{\rm IN}({ m V})$          | 0.3–0.8       | 0.1–1.5        | -                | -0.4-0.4        | 0.05–1       |

| $V_{\rm OUT}(V)$              | 0.1–0.3       | 0.2–1.5        | 0.1–1.4          | -0.2-0.2 (sim.) | 0–0.9        |

| $I_{\rm IN}(\mu A)$           | _             | -              | 1–70             | -               | -            |

| $I_{\rm OUT}(\mu A)$          | _             | -              | _                | -50-50          | -            |

| Bandwidth                     | 9 MHz (sim.)  | N/A            | 100 MHz          | 175 kHz (sim.)  | 0.5 MHz*     |

| Sampling frequency            | -             | -              | -                | -               | 1 MHz        |

| Normalized input/output range | 1–2.667       | 1–7.5          | 1–14             | N/A             | 1–20         |

| Number of samples             | 1             | 1              | 1                | 1               | 20           |

| Linearity errors              | ±1% (sim.)    | ±1%            | ±0.85%           | N/A             | ±1.7%        |

Table 4. Performance comparisons of various 1/x circuit chips.

\* Maximum bandwidth is equal to half of the sampling frequency, according to Nyquist theorem.

Fig. 9. Measured accuracies of  $V_{OUT}$  for 20 trimmed sample chips at M = 0.25 and  $V_{REF} = 0.8$  V.

Table 5. Linearity error sources of PVT variations.

|                     | Function                                                                                          | Measurement conditions                        | Linearity<br>error sources                         |

|---------------------|---------------------------------------------------------------------------------------------------|-----------------------------------------------|----------------------------------------------------|

| JSSC<br>1995 [3]    | $V_{\rm OUT} = \frac{g_{\rm m} V_{\rm C}}{4K_{\rm A} V_{\rm IN}}$                                 | $V_{\rm C} = 0.5  {\rm V}$                    | $K_{\rm A}(21\%)$<br>$g_{\rm m}(10\%)$             |

| IEICE<br>2003 [4]   | $V_{\rm OUT} = \frac{I_{\rm C}}{K_{\rm N}V_{\rm IN}}$                                             | <i>I</i> <sub>C</sub> =<br>10 μΑ–20 μΑ        | <i>K</i> <sub>N</sub> (21%)                        |

| TCAS-II<br>2005 [5] | $V_{\rm OUT} = \frac{2K_{\rm P}}{K_{\rm N}} \frac{(V_{\rm DD} - V_{\rm T})I_{\rm N}}{I_{\rm IN}}$ | <i>I</i> <sub>N</sub> =<br>0 μΑ–30 μΑ         | $K_{ m P}(21\%) \ K_{ m N}(21\%) \ V_{ m T}(20\%)$ |

| MWCAS<br>2012 [6]   | $V_{\rm OUT} \approx \frac{\Delta V_{\rm N}}{K_{\rm N} \Delta V_{\rm IN}}$                        | $\Delta V_{\rm N} = 0.3$                      | <i>K</i> <sub>N</sub> (21%)                        |

| This work           | $V_{\rm OUT} = M  \frac{V_{\rm REF}^2}{V_{\rm IN}}$                                               | M = 0.25,<br>$V_{\text{REF}} = 0.8 \text{ V}$ | -                                                  |

\*  $K (= \mu C_{OX} W/L)$  and  $g_m (= \sqrt{2KI_D})$  are the transconductance parameters of MOSFET, and  $V_T$  is the threshold voltage of MOSFET.

MOSFET. In the 0.18 µm CMOS process, the maximum process variations of K,  $g_m$ , and  $V_T$  are 21%, 10%, and 20%, respectively. But, theoretically, the proposed 1/x circuit is not affected by the parameters (K,  $g_m$ , and  $V_T$ ) because all parameters are removed from the equation of its function. Therefore, the additional linearity errors with PVT variations in [3]–[6] will be much larger than the linearity errors (±1.7%) of the proposed 1/x circuit.

The proposed 1/x circuit is slower than previous circuits [3] and [5], because its operation is based on the signal sampling

and the charge integration on capacitors. Its bandwidth (0.5 MHz) is considered to be half of the sampling frequency (1 MHz), according to Nyquist theorem. The bandwidth under 0.5 MHz is adequate for low-speed applications using the 1/x function. The analog dividers used in most instrumentation and control applications need a bandwidth of under 1 kHz [1]. A hearing-aid system [2] needs a bandwidth of 16 kHz.

## **IV.** Conclusion

An accurate tunable-gain 1/x circuit was proposed. The output voltage of the 1/x circuit is generated using a capacitor charging time that is inversely proportional to the input voltage. The output voltage is independent of process parameters, because the output voltage depends on the ratios of the capacitors, resistors, and current mirrors. The 1/x circuit achieved low linearity errors and wide input and output voltages by using low offset amplifiers and by matching the capacitors, resistors, and current mirrors well. The voltage gain of the 1/x circuit is tuned by a 10-bit digital code. The 1/x circuit was fabricated using a 0.18 µm CMOS process. Its core area is 0.011 mm<sup>2</sup> (144 µm × 78 µm), and it consumes 278 µW at  $V_{DD} = 1.8$  V and  $f_{CLK} = 1$  MHz. Its linearity error is within 1.7% at  $V_{IN} = 0.05$  V to 1 V.

## References

- T.L. Laopoulos and C.A. Karybakas, "A Simple Analog Division Scheme," *IEEE Trans. Instrum. Meas.*, vol. 40, no. 4, Aug. 1991, pp. 779–782.

- [2] M. van de Gevel and J.C. Kuenen, "Simple Low-Voltage Weak Inversion MOS 1/x Circuit," *Electron. Lett.*, vol. 30, no. 20, Sept. 1994, pp. 1639–1640.

- [3] S.-I. Liu and C.-C. Chang, "CMOS Analog Divider and Four-Quadrant Multiplier Using Pool Circuits," *IEEE J. Solid-State Circuits*, vol. 30, no. 9, Sept. 1995, pp. 1025–1029.

- [4] W. Liu and S.-I. Liu, "CMOS Tunable 1/x Circuit and its Applications," *IEICE Trans. Fundam. Electron. Commun. Comput. Sci.*, vol. E86-A, no. 7, July 2003, pp. 1896–1899.

- [5] W. Liu, S.-I. Liu, and S.-K. Wei, "CMOS Current-Mode Divider and its Applications," *IEEE Trans. Circuits Syst. II: Exp. Briefs*, vol. 52, no. 3, Mar. 2005, pp. 145–148.

- [6] I. Padilla-Cantoya, "Compact Low-Voltage CMOS Analog Divider Using a Four-Quadrant Multiplier and Biasing Control Circuit," *IEEE Int. Midwest Symp. Circuits Syst.*, Boise, ID, USA, Aug. 5–8, 2012, pp. 502–505.

**Byung-Do Yang** received his BS, MS, and PhD degrees in electrical engineering and computer science from the Korea Advanced Institute of Science and Technology, Daejeon, Rep. of Korea, in 1999, 2001, and 2005, respectively. He was a senior engineer at the Memory Division, Samsung Electronics,

Hwaseong, Rep. of Korea, in 2005, where he was involved in the design of DRAM. Since 2006, he has been at Chungbuk National University, Cheongju, Rep. of Korea, where he is now an associate professor. His research interests include analog circuits, memory circuits, and power IC designs.

Seo Weon Heo received his BS and MS degrees in electronic engineering from Seoul National University, Rep. of Korea, in 1990 and 1992, respectively, and his PhD degree in electrical engineering from Purdue University, West Lafayette, IN, USA, in 2001. From 1992 to 1998, he was with the Digital Media

Research Laboratory, LG Electronics Co., Ltd., Seoul, Rep. of Korea. From 2001 to 2006, he worked at the Telecommunication R&D Center, Samsung Electronics Co., Ltd., Hwaseong, Rep. of Korea. Since 2006, he has been an associate professor with the School of Electronic and Electrical Engineering, Hongik University, Seoul, Rep. of Korea. His current research interests include signal processing, wireless communication, and embedded system design.