# 역상분 전류 주입을 적용한 3상 인버터 기반 BESS의 단독 운전 검출 방법

Anti-islanding Detection Method for BESS Based on 3 Phase Inverter Using Negative-Sequence Current Injection

신 은 석\*·김 현 준\*·한 병 문<sup>†</sup> (Eun-Suk Sin·Hyun-Jun Kim·Byung-Moon Han)

Abstract - This paper proposes an active islanding detection method for the BESS (Battery Energy Storage System) with 3-phase inverter which is connected to the AC grid. The proposed method adopts the DDSRF (Decoupled Double Synchronous Reference Frame) PLL (Phase Locked-Loop) so that the independent control of positive-sequence and negative-sequence current is successfully carried out using the detected phase angle information. The islanding state can be detected by sensing the variation of negative-sequence voltage at the PCC (Point of Common Connection) due to the injection of 2-3% negative-sequence current from the BESS. The proposed method provides a secure and rapid detection under the variation of negative-sequence voltage due to the sag and swell. The feasibility of proposed method was verified by computer simulations with PSCAD/EMTDC and experimental analyses with 5kW hardware prototype for the benchmark circuit of islanding detection suggested by IEEE 1547 and UL1741. The proposed method would be applicable for the secure detection of islanding state in the grid-tied Microgrid.

**Key Words**: BESS(Battery energy storage system), Negative sequence current, Islanding\_detection, DDSRF\_PLL(Decoupled double synchronous reference frame PLL)

#### 1. 서 론

분산전원에서 단독 운전은 전력계통 작업자에게 인명 피해를 유발하고 국부적으로 주파수 상승 또는 하강을 초래하여 품질 저 하를 야기한다. 따라서 단독운전의 상태를 신속히 검출하여 연계 계통으로부터 분산전원을 분리시키는 것은 분산전원의 보호체계 를 확립하는데 대단히 중요하다.

BESS의 경우 특히 부하의 안정적인 전력 공급을 위해 대부분 단독 운전 발생시 계통과 분리 되어 전류제어에서 전압제어의 모드전환이 신속히 이뤄져야 한다. 하지만 확실한 단독운전 검출이 이루어지지 않는다면 연계된 부하와 배터리에 심각한 손상을 초래할 수 있다. 신속한 단독 운전 검출을 수행하기 위해서 우리나라 계통 운영자인 한국 전력에서 제시한 규정에서는 0.5초 이내, 해외의 경우 IEEE1547과 UL1741에서는 2초 이내에 단독 운전을 검출 하도록 요구한다.

분산전원의 단독 운전을 판별하는 방법에는 수동기법과 능동

† Corresponding Author: Dept. of Electrical Engineering, Myongji University, Korea

E-mail: erichan@mju.ac.kr

\* Dept. of Electrical Engineering, Myongji University, Korea Received: June 6, 2015; Accepted: August 9, 2015 기법이 존재한다. 분산전원이 연계된 지점의 계통정보만을 이용하여 단독운전 여부를 판단하는 수동기법은 분산전원의 출력이부하의 크기와 유사한 경우 판별이 어렵다. 그 이유는 수동기법은 계통조건에 대한 의존도가 크기 때문이다. 따라서 전압, 전류, 무효전력 등을 불연속 적으로 계통에 주입하여 주파수 편이를 측정하여 판별하는 능동 기법에 대한 연구가 다양하게 진행되어왔다[1-3].

대부분의 수동 기법들은 구현이 용이하지만 계통 조건에 대한 의존도가 상당히 크기 때문에 검출 불가능한 영역인 NDZ(Non Detection Zone)이 능동기법에 비해 상대적으로 넓다. 따라서 대부분 능동 기법이 적용되어 사용 된다. 능동 기법들은 임피던스측정기법, 고조과 검출 기법, 주과수 바이어스 기법, SFS (Sandia Frequency Shift)기법, SVS(Sandia Voltage Shift)기법, 주과수점프 기법 등이 있다[4-6]. 능동기법중 주과수 바이어스 기법은현재 활발히 보급되고 있는 태양광 계통 연계 인버터에 실 적용되고 있으며 그 성능 또한 우수성을 확보하고 있다. 하지만 이방식은 주입하는 전압, 전류, 무효전력 등을 불연속적으로 주입하는 방식이므로 계통 전압의 고조과가 발생되고 그로 인하여전력품질이 저하될 뿐만 아니라 전력설비의 수명단축을 야기할수 있다.

이러한 문제점은 주기적으로 수%전류를 주입하거나, 고조파를 주입하는 방식 등에서도 야기되고 있다[7]. 또한 기존에 제시된 역상분 전류 주입 방법은 계통의 전압이 평형일 경우를 가정하고 진행되었으며 단독운전 및 순간적인 Sag나 Swell에 대한 구분을 할 수 없는 단점을 가지고 있다. 또한 역상분 전압 주입방법의 경우  $2\sim3\%$ 의 역상분 전압을 형성하여 단독 운전을 검출 신호로 이용 하지만 공급되는 부하 전압에 불평형을 발생시키는 문제를 초래할 수 있다[8-10].

이러한 문제를 해결하기 위해 본 논문에서는 계통에 연계된 3 상 전압원 인버터 기반 BESS를 통한 능동 단독 운전 검출 방법을 제안한다. 약 2~3%의 역상분 전류를 주입하여 단독 운전 발생시 계통과의 접속점 PCC(Point of Common Coupling)에서 역상분 전압의 크기 변화를 측정하여 검출하는 방법이다. 기존의고조파 주입 방식에서 문제시 되었던 공진주파수 문제를 해결할수 있으며, DDSRF\_PLL을 적용하여 계통전압의 불평형에서도 빠르게 단독운전을 검출할 수 있다.

제안된 단독운전 검출 방법은 UL1741[11] 및 IEEE1547[12] 의 시험 조건하에서 PSCAD/EMTDC소프트웨어를 통한 모의실험 과 5kW 프로토타입 하드웨어 장치를 통해 검증하였다.

#### 2. 제안된 단독 운전 검출 방법

### 2.1 단독 운전 검출 시험 장치

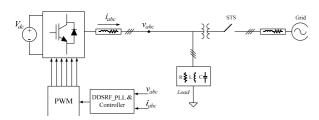

그림 1 UL1741 기준 시험 회로

Fig. 1 Schematic diagram of UL1741 standard test

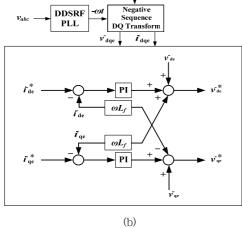

단독 운전 검출 시험 장치의 경우 UL1741또는 IEEE1547에서 기준 시험 장치를 제시한다. 이러한 기준 시험 장치는 서로 매우 유사하기 때문에 본 논문에서는 UL1741의 시험 요구 조건을 적용했다. 그림 1은 UL1741 단독운전시험에 대한 도식을 보여준다. 그림 1에서 보이는 것처럼 계통과 분산전원 그리고 부하는 RLC 병렬 구성을 이용한 집중 정수 모델(Lumped parameter model)로 가정한다.

$R_{\rm f}$  와  $L_{\rm f}$ 는 직렬 고조파 필터를 나타내며 변압기는 PCC단에서 분산전원을 계통과 연계한다. 각 규정에서는 부하의 공진 주 파수를 계통 주파수인  $60{\rm Hz}$ 로 명시한다. 이때 RLC부하는 유도성무효전력과 용량성 무효전력이 동일하게 되어 순수 저항성 부하로 보이게 된다.

#### 2.2 역상분 전류를 통한 단독 운전 검출 방법

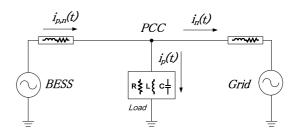

그림 2는 본 논문에서 제안된 계통연계형 BESS와 고조파 필터를 거쳐 변압기를 통해 계통과 연결된 시스템의 도식을 나타낸

것이다[13].

그림 2 정상분, 역상분 전류 주입 등가회로

Fig. 2 Schematic diagram of the test system illustrating positive and negative sequence current injection

$i_p(t)$ 는 60Hz의 정상분 전류를 나타내고  $i_n(t)$ 는 역상분 전류를 나타낸다. BESS를 통해 역상분 전류를 주입할시 계통의 임피던스는 부하의 임피던스보다 상대적으로 적게 보이기 때문에 역상분 전류  $i_n(t)$ 는 모두 계통으로 흐른다. 이를 정상분 등가회로 와 역상분 등가회로로 나타내면 그림 3, 4와 같다.

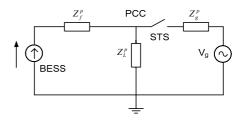

그림 3 정상분 등가회로

Fig. 3 Positive sequence circuit

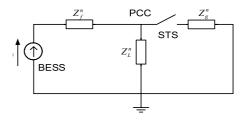

그림 4 역상분 등가회로

Fig. 4 Negative sequence circuit

여기서 BESS는 전류원으로 등가할 수 있고, 계통은 전압원  $V_g$ 로 나타낸다.  $Z_f^r$ ,  $Z_f^r$ 는 정상분과 역상분 고조파 필터 등가 임 피던스,  $Z_L^r$ ,  $Z_L^r$  는 부하와 PCC단사이의 정상분과 역상분 등가 임피던스,  $Z_g^r$ ,  $Z_g^r$  는 PCC와 계통사이의 정상분과 역상분 등가 임피던스를 나타낸다.

BESS가 계통에 연계된 경우 PCC단에 걸린 정상분 전압과 역상분 전압은 수식 (1), (2)와 같이 나타낼 수 있으며 이때  $Z_{g}^{r}$ ,  $Z_{g}^{r}$ 의 값이  $Z_{L}^{r}$ ,  $Z_{L}^{r}$  에 비해 적은 값을 갖고 3상의 전압이 평형상태라면 수식 (3)과 같이 나타낼 수 있게 되어 PCC단에서 역상

분 전압은 보이지 않게 된다.

$$V_{pcc}^{p} = Z_{L}^{p} \frac{V_{g} + I_{p} Z_{g}^{p}}{Z_{L}^{p} + Z_{g}^{p}}$$

(1)

$$V_{pcc}^{n} = I_{n} \frac{Z_{L}^{n} Z_{g}^{n}}{Z_{L}^{n} + Z_{g}^{n}} \tag{2}$$

$$V_{pcc}^p = V_g, \quad V_{pcc}^n = 0 \tag{3}$$

하지만 STS가 개방되어 단독운전 상태로 전환 된다면 PCC단의 정상분과 역상분 전압은 (4), (5)에 의해 주어진다.

$$V_{pcc}^{p} = I_{p}Z_{L}^{p} \tag{4}$$

$$V_{pcc}^{n} = I_{n} Z_{L}^{n} \tag{5}$$

$I_p$ 과 $I_n$ 은 각각 BESS에 의해 주입된 역상분과 정상분 전류의 벡터 크기이다. 따라서 위의 수식처럼 역상분 전류  $I_n$ 는 RLC부하에 걸리게 되어 PCC단에서는 역상분 전압이 보이게 된다. 따라서 제안된 단독 운전 검출 방법은 주입된 역상분 전류 만큼의 정해진 불평형율을 넘게 된다면 단독운전이 발생되었다고 판단한다. 전압 불평형율(VI : Voltage Imbalance)은 다음과 같이 정의된다[14].

$$VI = \frac{V_n}{V_p} \times 100\% \tag{6}$$

여기서 abc좌표계상에서 Vp와 Vn은 각각 순시 정상분과 역상 분 전압의 크기이다. STS가 개방되어 단독운전이 발생시 정상분, 역상분 전압과 전류는 비례하여 수식 (7)과 같이 나타낼 수 있다.

$$VI = \frac{V_n}{V_p} \times 100\% = \frac{I_n}{I_p} \times 100\%$$

(7)

#### 2.3 역상분 전류 주입을 위한 BESS 제어

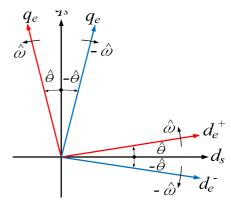

BESS내의 전류 제어기를 통해 역상분 전류를 주입하기 위해서는 기존 PI전류제어기를 확장하여 정상분 전류 제어기와 역상분 전류제어기로 각각 구성해야 한다. 그림 5와 같이 계통 위상각에 동기화된 정상분 동기 좌표계와 역상분 동기 좌표계를 사용하여 구현할 수 있다. 따라서 본 논문에서는 계통전압의 불평형이 존재 하여도 정확히 계통의 위상각을 추종할 수 있는 DDSRF\_PLL방식[15]을 적용하여 정상분,역상분 전류제어기를 구성하여 역상분 전류를 주입하였다.

계통의 전압이 3상 평형이 아니라면 dq정지좌표변환에 의해 수식 (8)과 같이 영상분 전압을 제거한 기본파 성분을 정상분과 역상분 성분으로 나타낼 수 있다. 이때  $v_{dqs}^+$ ,  $v_{dqs}^-$ 는 dq정지좌표

그림 5 정상분, 역상분 동기 기준 회전 좌표계

Fig. 5 Positive and negative sequence synchronous reference frame

변환된 정상분,역상분 순시 유, 무효전압이며  $V_{dq}^+$ 와  $V_{dq}^-$ 는 정상분,역상분 유무효전압 크기의 최댓값을 나타낸다. 그리고  $\phi^+,\phi^-$ 는 정상분과 역상분의 초기 위상각이다.

$$\mathbf{v}_{dqs} = \begin{bmatrix} \mathbf{v}_{ds} \\ \mathbf{v}_{qs} \end{bmatrix} = \mathbf{v}_{dqs}^{+} + \mathbf{v}_{dqs}^{-}$$

$$= V_{dq}^{+} \begin{bmatrix} \cos(\omega t + \phi^{+}) \\ \sin(\omega t + \phi^{+}) \end{bmatrix} + V_{dq}^{-} \begin{bmatrix} \cos(-\omega t + \phi^{-}) \\ \sin(-\omega t + \phi^{-}) \end{bmatrix}$$

(8)

PLL에 의해 동기화( $\omega t = \theta$ )가 이루어지고 동기 회전 좌표 변환을 하게 되면 수식 (8)은 다음과 같이 수식 (9), (10)으로 표현이 가능하다.

$$v_{dqe}^{+} = \begin{bmatrix} v_{de}^{+} \\ v_{qe}^{+} \end{bmatrix}$$

$$= V_{dq}^{+} \begin{bmatrix} \cos(\phi^{+}) \\ \sin(\phi^{+}) \end{bmatrix} + V_{dq}^{-} \cos(\phi^{-}) \begin{bmatrix} \cos 2\omega t \\ -\sin 2\omega t \end{bmatrix}$$

$$+ V_{dq}^{-} \sin(\phi^{-}) \begin{bmatrix} \sin 2\omega t \\ \cos 2\omega t \end{bmatrix}$$

(9)

$$\mathbf{v}_{dqe}^{-} = \begin{bmatrix} \mathbf{v}_{de}^{-} \\ \mathbf{v}_{qe}^{-} \end{bmatrix} \\

= V_{dq}^{-} \begin{bmatrix} \cos(\phi^{-}) \\ \sin(\phi^{-}) \end{bmatrix} + V_{dq}^{+} \cos(\phi^{+}) \begin{bmatrix} \cos 2\omega t \\ \sin 2\omega t \end{bmatrix} \\

+ V_{dq}^{+} \sin(\phi^{+}) \begin{bmatrix} -\sin 2\omega t \\ \cos 2\omega t \end{bmatrix} \tag{10}$$

수식 (9), (10)에서 볼 수 있듯이, dq동기 회전 좌표 변환을 수행하면 정상분과 역상분 DC전압 성분에 서로 2ω의 주파수 성 분이 커플링 되어 있다. 따라서 2고조파 커플링 성분을 제거하여 디커플링 한다면 정상분과 역상분 전압 크기를 구할 수 있다. 이렇듯 2고조파 성분을 제거하여 사용하는 PLL방식을 DDSRF\_PLL (Decoupled Double Synchronous Reference Frame PLL) 이라한다. 따라서 본 논문에서는 전압의 불평형에서도 정확한 위상각을 추종하여 안정적인 전류 제어기를 구성하였다.

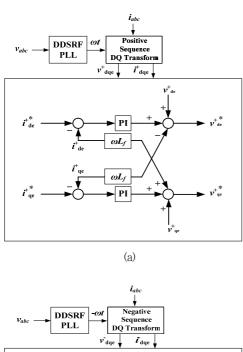

그림 6 (a) 정상분 전류 제어기 블록도 (b) 역상분 전류 제어기 블록도

Fig. 6 Block diagrams of (a) positive-sequence current controller and (b) negative-sequence current controller.

DDSRF\_PLL에서 구해진  $\omega t = \theta$  정보를 사용하여  $v_{abc}$   $i_{abc}$  순시 전압, 전류를 정상분, 역상분 dq동기 회전 좌표 변환을 통해 정상분, 역상분 각각의 유·무효전압, 전류로 나타낼 수 있다. 그림 6(a), (b)는 역상분, 정상분 전류제어기의 전체 제어 블록도를 보여준다.  $i_{de}^{+*}$ ,  $i_{qe}^{+*}$ 의 경우 BESS의 충, 방전 및 역률제어에 필요한 전류제어를 수행하게 되고 역상분 전류제어기의  $i_{ae}^{-*}$ 를 통해

3%의 역상분 전류를 주입하게 된다. 이때 dq동기 회전 좌표 변환에 의해 디커플링 성분이 발생하게 되지만 이와 함께 전압 성분을 전향 보상하여 각각의 전류 제어기의 최종 신호는 PWM신호를 발생시키기 위한 정상분 역상분의 기준 전압을 독립적으로 생성하게 된다.

#### 3. 모의 실험 결과

#### 3.1 시스템 구성

그림 7 시뮬레이션 및 실험을 위한 시스템 구성

Fig. 7 System configuration for simulation and experiment

제안된 단독 운전 검출 방법을 검증하기 위해 PSCAD/EMTDC 소프트웨어를 통하여 모의실험을 진행하였다. 시스템의 구성은 UL1741의 단독 운전 기준 시험 회로와 동일하게 그림 7과 같이 구성 하였으며 시스템 상수는 표 1에 나타내었다.

표 1 시스템 상수

Table 1 System parameters

| Rated Power      | 5kW        | Qf    | 2.0     |

|------------------|------------|-------|---------|

| DC_link          |            |       |         |

| (lithium-polymer | 336~470.4V | fgrid | 60Hz    |

| Battery)         |            |       |         |

| Vgrid            | 220Vrms    | fsw   | 10kHz   |

| Filter Lf        | 3mh        | Rload | 9.68Ω   |

| Filter Cf        | 15uF       | Lload | 10.27mH |

| Rf               | 0.1Ω       | Cload | 685.1uF |

#### 3.2 UL1741 시험 조건의 단독 운전 검출

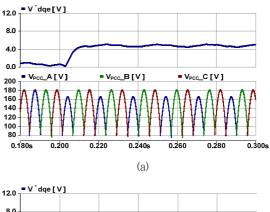

그림 8은 PSCAD/EMTDC 소프트웨어를 이용한 단독 운전 검출 모의 상황에 대한 계통 주파수, 정상분 전압 크기, 역상분 전압크기, 계통 전류, 단독 운전 검출 신호와 STS 상태를 보여준다. BESS에서 공급하는 전력량과 부하의 소비전력량을 같게 두었으며 0.8s에 단독운전이 발생했다고 가정하고 STS를 개방하였다.

단독운전이 발생되는 시점인 0.8s에서 주파수의 변동이 미비하기 때문에 주파수만을 사용하여 단독운전 검출을 할 수 없게 된다. 또한 계통의 전압이 평형이기 때문에 단독발생 전후 정상분전압의 크기는 220 Vrms의 한상의 전압 최대치인 180V가 되게된다.

그림 8 UL1741 기준 시험회로를 통한 시뮬레이션

Fig. 8 Simulation under UL1741 test conditions

BESS 내의 역상분 전류 제어기에 의해 3%의 역상분 전류가 주입되고 있지만 부하의 임피던스 보다 계통의 임피던스가 적기때문에 STS가 개방되는 0.8s 이전에는 PCC단의 역상분 전압이보이지 않게 된다. 하지만 0.8s 후에는 계통으로 흐르던 3%의 역상분 전류가 부하로 흐르기 때문에 역상분 전압의 크기가 급격히상승한다. 이를 통해 단독 운전 발생시 규정된 시간 안에 충분히만족할 수 있는 단독 운전 검출을 수행할 수 있다.

#### 3.3 계통 불평형 전압에 대한 분석

실제 계통에서는 전압이 평형이 아닌 경우가 항상 존재 한다. BESS가 계통에 연계되어 운전될 때 계통 전압이 3상 평형이 아 닐 경우 PCC단에서는 역상분 전압이 나타나게 된다.

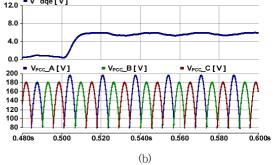

그림 9(a), (b)는 1상 전압이 순간 sag나 swell을 발생하여 3상 계통 전압이 순간적인 불평형을 이루었을 때 3상 전압 파형과 이때 발생하는 역상분 전압의 크기 변화를 보여준다. 순간 sag나 swell에 대한 전압 불평형율은 최악의 경우로 설정하여 3%로 두었다. 이는 단독운전이 발생시 PCC단에서 검출되는 역상분 전압의 크기와 동일하기 때문에 전압의 불평형이 발생할 경우 BESS는 이를 단독운전으로 검출 하는 오동작을 일으킬 수 있다.

하지만 전압의 불평형이 발생한다면 역상분 전압뿐만 아니라 정상분 전압의 크기도 변하게 된다. 따라서 정상분 전압의 크기 가 변화 한다면 단독 운전 검출 신호를 발생시키지 않는다.

그림 10은 계통의 불평형이 발생한 경우의 단독운전 검출 모의실험 파형이다. t = 0.2s 일 때 1상 전압를 임의로 5 Cycle 정도 sag를 발생시켜 역상분 전압이 PCC단에서 약 3%가 되도록

그림 9 Sag, Swell에 대한 시뮬레이션 (a) Sag 발생시 역상분전 압 & 3상 PCC전압 (b) Swell 발생시 역상분전압 & 3상 PCC전압

Fig. 9 Simulation under 1phase sag, swell conditions (a)

Negative Voltage & 3phase PCC Voltage under sag

conditions (b) Negative Voltage & 3phase PCC

Voltage under swell conditions

그림 10 계통 불평형 조건하에서 시뮬레이션 파형

Fig. 10 Simulation under grid imbalance conditions

하였다. 그리고 t = 0.5s일 때 1상 전압을 임의로 5Cycle 정도 swell을 발생시킨다.

1상 전압의 순간 sag와 swell 발생시 PCC단의 정상분 전압의 크기는 역상분 전압의 변동분과 거의 동일하게 변하게 된다. 하지만 단독운전 검출이 발생되는 t=0.8s에서는 역상분 전압 크기만 변하게 되고 BESS에서 정상분 전류 제어기로 인해 충방전 제어를 수행하기 때문에 부하에 걸리는 전압은 기본파 1상의 최대치인 180V가 된다. 이를 통해 계통 전압의 순간적인 불평형이발생할 지라도 이를 정확하게 BESS에서 판단하여 단독 운전 검출을 수행할 수 있음을 확인하였다.

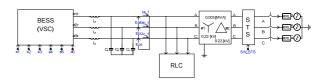

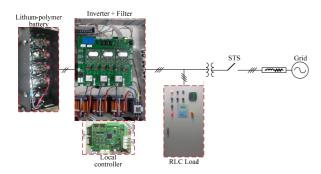

# 4. 하드웨어 실험 결과

그림 11은 제안한 단독 운전 검출 방법을 실험적으로 검증하기 위해 제작한 하드웨어 시뮬레이터를 나타낸 것이다. 전체 시스템의 구성은 에너지저장장치 역할을 수행하는 5 kwh lithium-polymer Battery와 로컬 제어기, RLC부하를 사용하였다. 그리고 5kVA 용량의 전력변환기로 시스템이 구성되어 있다. 본 실험에서의 모든 조건은 시뮬레이션의 타당성을 검증하기 위하여 표 1과 동일하게 수행하였다.

그림 11 단독 운전 검출 시험을 위한 시스템 구성

Fig. 11 Test configuration for islanding test

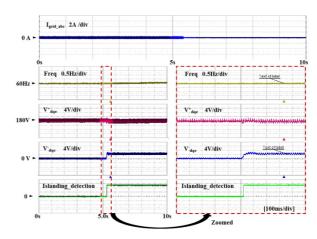

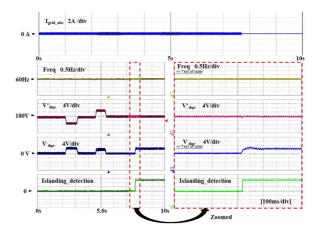

그림 12는 계통전원의 평형 상태에서 4.8s에 STS를 개방하여 단독운전모의를 수행하였다. 단독운전 발생 전 부하의 소모량과 BESS에서 공급하는 전력량이 동일하기 때문에 계통에는 적은 양 의 전류가 흐르게 된다. 하지만 단독운전 발생 직후 3%의 역상 분 전류가 주입됨으로써 계통 차단과 동시에 PCC단에서 측정된 역상분 전압의 크기가 상승한다.

그림 13의 경우 1상의 계통 전압이 순간적인 sag나 swell이 발생하였을 때 이를 단독운전과 구분할 수 있음을 보여준다.

계통의 불평형이 발생한다면 역상분 전압의 크기가 BESS에서 공급하는 역상분 전류와 무관하게 PCC단에서 나타나게 되어 단독 운전 검출의 오동작이 발생할 수 있다. 따라서 정상분 전압의 크기도 같이 고려하여 단독 운전 검출 신호로 이용하여 판별한다. 따라서 더욱 신뢰성 있고 안정적으로 시스템을 유지할수 있다.

그림 12 평형 계통 조건에서의 단독 운전 방지 실험 결과

Fig. 12 Anti Islanding test results under grid balance conditions

그림 13 불평형 계통 조건에서의 단독 운전 방지 실험 결과

Fig. 13 Anti Islanding test results under grid imbalance conditions

하드웨어 실험은 2.2s에서 a상 전압의 3%의 역상분 전압이 발생하도록 1초 동안의 sag발생을 유지하고 복구 시켰다. 이때 역상분 전압은 3%로 상승하게 되지만 정상분 전압의 변동이 발생하여 이는 단독 운전 검출 신호를 발생하지 않게 된다. 4.6s에서는 1상의 전압에 swell를 발생시켰을 때의 파형을 나타낸다. 이때도 마찬가지로 정상분 전압의 변동으로 인해 단독 운전 검출신호로 사용하지 않지만 8.6s에서 STS를 개방하였을 시 정상분전류제어를 수행하고 있는 컨버터에 의하여 정상분 전압은 일정하게 유지되고 역상분 전압의 변동만 발생하여 단독운전 검출을 정확히 판별할 수 있게 된다.

#### 5. 결 론

본 논문에서는 역상분 전류 주입을 통해 BESS의 단독 운전을

안정적이고 신속하게 검출할 수 있는 방법을 제안하였다. BESS에서 약 3% 역상분 전류를 계통에 주입함으로써 단독운전 발생시 PCC단에 걸리는 역상분 전압의 크기를 측정 하여 단독 운전발생 여부를 판단 한다.

IEEE1547과 UL1741에서 제시하는 기준에 모두 만족을 하였으며 DDSRF\_PLL을 적용하여 계통의 순간적인 sag나 swell 발생시에도 정상분과 역상분 전압의 크기 변화를 통해 전압의 불평형시 발생되는 역상분 전압 변동과 단독운전시 발생되는 역상분 전압 변동을 정확하게 구별할 수 있음 또한 확인 하였다. 따라서 BESS의 신속하고 정확한 단독 운전 검출을 수행하여 부하에 안정적이고 고품질 전력을 수행 할 수 있을 뿐더러 BESS의 모드 전환 시 과도상태성능도 향상될 수 있을 것이다.

PSCAD/EMTDC를 이용하여 모의실험을 하였으며 또한 5kw 프로토타입 하드웨어 장치를 통해 타당성을 검증 하였다.

#### 감사의 글

본 연구는 2013년도 산업통상자원부의 재원으로 한국에 너지기술평가원(KETEP)의 지원을 받아 수행한 연구 과제입 니다. (No. 20132010101880), (No. 20133010021790)

#### References

- [1] Thomas R. Sims, Robert A. Jones, and Ali F. Imece, "Investigation of Potential Islanding Problems of a Line-Commutated Static Power Converter in Photovoltaic Systems." IEEE Trans. on Energy Conversion, Vol. 5, No. 3, September 1990.

- [2] K. Takigawa and H. Kobayashi, "A Development of Compact and Reliable Protective Control Unit for Grid Connected Small Residential PV systems." IEEE, No. CH3365-4/94/0000-1081, 1994.

- [3] Sung-Il Jang and Kwang-Ho Kim, "Development of a Logical Rule-Based Islanding Detection Method for Distributed Resources, "IEEE Power Engineering Society 2002 Winter Meeting, New York USA, January 27-31, 2002.

- [3] J. Stevens, R. Bonn, J. Ginn, S. Gonzalez, and G. Kern, Development and Testing of an Approach to Anti-Islanding in Utility-Interconnected Photovoltaic Sys- tems Sandia National Laboratories, Albuquerque, NM, Sandia Nat. Lab Rep. SAND 2000-1939, Aug. 2000.

- [5] Ropp, ME., Begovic, M., and Rogatgi, A.: "Analysis

- and performance assessment of the active frequency drift method of islanding prevention", IEEE Trans. Energy Convers., 1999, 14, (3), pp. 810-816.

- [6] L. A. C. Lopes and H. Sun, "Performance assessment of active frequency drifting islanding detection methods," IEEE Trans. Energy Convers., vol. 21, no. 1, pp. 171– 180, Mar. 2006.

- [7] Hung, G.K., Chang, C.C., and Chem, C.L.: "Automatic phase-shift method for islanding detection of grid-connected photovoltaic inverters", IEEE Trans, Energy Convers., 2003, 18, (1), pp. 169-173.

- [8] Tuyen, Nguyen Duc; Fujita, Goro, "Negative-sequence Current Injection of Dispersed Generation for Islanding Detection and Unbalanced Fault Ride-through," Universities' Power Engineering Conference (UPEC), Proceedings of 2011 46th International, vol., no., pp.1,6, 5-8 Sept. 2011.

- [9] Zhihui Dai; Zhiqiang Chong; Xuan Liu; Chuan Li, "Active islanding detection method based on gridconnected photovoltaic inverter and negative sequence current injection," Power System Technology (POWERCON), 2014 International Conference on, vol., no., pp. 1685,1690, 20-22 Oct. 2014.

- [10] Byeong-Heon Kim; Seung-Ki Sul; Chun-Ho Lim, "Anti-islanding detection method using Negative Sequence Voltage," Power Electronics and Motion Control Conference (IPEMC), 2012 7th International, vol.1, no., pp.604,608, 2-5 June 2012.

- [11] Inverters, Converters, and Controllers for Use in Independent Power Systems, UL STD 1741, 2002.

- [12] IEEE Standard for Interconnecting Distributed Resources With Electric Power Systems, IEEE STD 1547, 2003.

- [13] H. Karimi, A. Yazdani and R. Iravani, "Negative-Sequence Current Injection for Fast Islanding Detection of a Distributed Resources," IEEE Trans. Power Electron, Vol. 23, No. 1, Jan. 2008.

- [14] J. Driesen and T. Van Craenenbroeck, "Voltage disturbances, introduction to unbalance," Power Qual. Appl. Guide, Copper Develop. Assoc., pp. 1-11, May 2002.

- [15] P. Rodriguez, J. Pou, J. Bergas, J. I. Candela, R. P. Burgos and D. Boroyevich "Decoupled double synchronous reference framePLL for power converters control", IEEE Trans.Power Electron., vol. 22, no. 2, pp. 584-592 2007.

# 저 자 소 개

신 은 석 (Eun-Suk Sin)

1989년 7월 4일생. 2014년 명지대 전기공학 과 졸업. 2014년  $\tilde{}$  현재 동 대학원 전기공학 과 석사과정

E-mail: sinunsuk@naver.com

김 현 준 (Hyun-Jun Kim)

1985년 11월 12일생. 2011년 명지대 전기공 학과 졸업. 2011년  $^{\sim}$  현재 동 대학원 전기공 학과 석·박사과정 통합과정

E-mail: inverter1112@naver.com

# 한 병 문 (Byung-Moon Han)

1976년 서울대 전기공학과 졸업. 1988년 미 아리조나주립대 대학원 전기공학과 졸업(석 사). 1992년 동 대학원 전기공학과 졸업(공 박). 미 Westinghouse중앙연구소선임연구원. 현재 명지대 전기공학과 교수.

E-mail: erichan@mju.ac.kr