IEIE Transactions on Smart Processing and Computing

# Output Noise Reduction Technique Based on Frequency Hopping in a DC-DC Converter for BLE Applications

Ju-Hyun Park, Sung Jin Kim, Joo Young Lee, Sang Hyeon Park, Ju Ri Lee, Sang Yun Kim, Hong Jin Kim, and Kang-Yoon Lee\*

College of Information and Communication Engineering, Sungkyunkwan University / Suwon, South Korea {hanpiece, sun107ks, jooguri, psh001, juri, ksy0501, squarejj, klee}@skku.edu

\* Corresponding Author: Kang-Yoon Lee

Received July 21, 2015; Revised September 3, 2015; Accepted September 29, 2015; Published October 31, 2015

\* Regular Paper

Abstract: In this paper, a different type of pulse width modulation (PWM) control scheme for a buck converter is introduced. The proposed buck converter uses PWM with frequency hopping and a low quiescent—current low dropout (LDO) voltage regulator with a power supply rejection ratio enhancer to reduce high spurs, harmonics and output voltage ripples. The low quiescent—current LDO voltage regulator is not described in this paper. A three-bit binary-to-thermometer decoder scheme and voltage ripple controller (VRC) is implemented to achieve low voltage ripple less than 3mV to increase the efficiency of the buck converter. An internal clock that is synchronized to the internal switching frequency is used to set the hopping rate. A center frequency of 2.5MHz was chosen because of the bluetooth low energy (BLE) application. This proposed DC-DC buck converter is available for low-current noise-sensitive loads such as BLE and radio frequency loads in portable communications devices. Thus, a high-efficiency and low-voltage ripple is required. This results in a less than 2% drop in the regulator's efficiency, and a less than 3mV voltage ripple, with -26 dBm peak spur reduction operating in the buck converter.

Keywords: Buck converter, Frequency hopping, Thermometer decoder, Pulse width modulation, Spurious noise

# 1. Introduction

DC-DC converters are widely used for generating lowvoltage power supply applications, such as analog and radio frequency circuits. However, pulse width modulation (PWM) in a DC-DC buck converter creates switching noise and voltage ripple. PWM is usually a square wave with a constant frequency (f<sub>c</sub>) and variable duty cycle (D = t<sub>on</sub>/T), as explained by Balcells et al. [1]. Because of these, the most serious interference and cross-mixing with electric circuits are at the fundamental switching frequency and its harmonics. Thus, control sawtooth wave signals having a spectrum with lower peak amplitude than the conventional constant frequency square signal are used to reduce main interference. There are many methods to reduce output noise, such as a spread spectrum clock generator (SSCG) [1], sigma delta modulation (SDM) [2], frequency hopping [3], frequency stepping [9] and a pseudo-noise coded constant off time (PNC-COT) controlled switching regulator (SWR) [8] have already

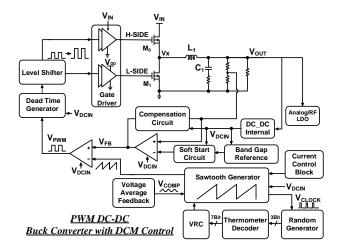

been introduced. However, a frequency hopping technique would seem to be the best candidate for spur reduction. Thus, this paper proposes a DC-DC converter using frequency hopping with a thermometer decoder (FHTD) to reduce output noise and current consumption for highperformance radio frequency circuits. Fig. 1 shows the proposed DC-DC buck converter top block diagram composed of an internal low dropout (LDO) voltage regulator, a compensation circuit, band gap reference (BGR), soft start, a sawtooth generator, dead time generator, gate driver and dead time generator. The level shifter and gate driver get power from a lithium-ion battery, 2.2V~5V. Other circuits use 1.2V (V<sub>DCIN</sub>) generated from an internal LDO voltage regulator. So a level shifter is mandatory to increase the voltage to the V<sub>OUT</sub> level. BGR and soft start are temporarily used while the circuit is not saturated. A dead time generator is very efficiency at reducing leakage current and improving the efficiency of the DC-DC converter by generating a non-overlap pulse. A sawooth generator is a switching regulator to control M<sub>0</sub>

Fig. 1. Top block diagram of a PWM-controlled buck converter.

(PMOS) and  $M_1$  (NMOS). It affects the switching frequency. This paper controls the switching frequency using frequency hopping and a thermometer decoder.

# 2. Frequency Hopping with Thermometer Decoder

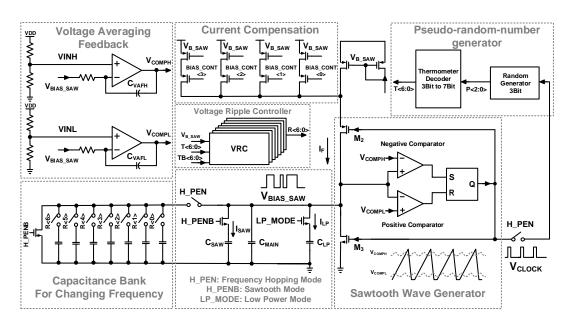

The general buck converter suffers from switching noise, which appears as spurs and harmonics due to the periodic switching of the buck converter. Therefore, the use of frequency hopping with thermometer decoder control to reduce spurs in the output spectrum of the buck converter is explained using the conceptual implementation shown in Fig. 2. The source current IF is used to charge sawtooth generator capacitance  $C_{SAW}$ , while a much larger sink current,  $I_{SAW}$ , is used to discharge it. A sawtooth generator, two comparators, an SR latch and two

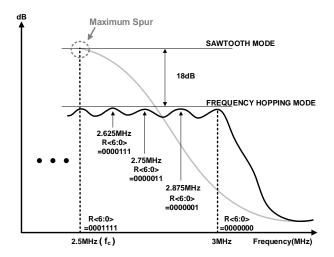

reference voltages from voltage average feedback, V<sub>COMPH</sub> and  $V_{COMPL}$ , are used to generate  $V_{CLOCK}$ , which indicates the charging and discharging points of M<sub>2</sub>(PMOS) and M<sub>3</sub>(NMOS). V<sub>CLOCK</sub> goes to a random generator to make three-bit random code (P<2:0>). If a period of the random code is quite short, the switching frequency will create more sub-harmonics. Therefore, a long period code is mandatory. The thermometer decoder extends the code to seven bits (T<6:0>). Theoretically, the magnitude of each spur is reduced by a factor of 1/hopping rate, or 20x log (hopping rate) dB from the single frequency. This proposed frequency hopping employs eight hopping frequencies, as illustrated in Fig. 3. This is the maximum, because 16 hopping frequencies does not follow the equation 20 x log 16 24dB, which results in 19.4dB. The 16 hopping frequencies occupy a large area and generate high glitches on output for the fast hopping rate. Therefore, we use eight frequencies between 2MHz and 3MHz to avoid operation frequency interference in the block linear equalizer (BLE) application. The main frequency, f<sub>c</sub> was set to 2.5MHz (450ns), spacing the frequencies 125KHz (80ns) apart. This achieves an 18dB reduction in output spurs compared to the traditional single-frequency scenario, and significantly suppresses maximum spur and harmonics without the cost of increasing the capacitance (C1) or inductance (L<sub>1</sub>) of the buck output LC filter. On the other hand, the noise floor is slightly increased to spread the spectrum over the harmonics. Changing the switching frequency disturbs the steady-state duty cycle of the converter. It causes pulse swallowing or significant instantaneous error in the duty cycle. So, to avoid these problems, synchronization between the hopping rate and internal switching frequencies of the converter must be ensured, such that hopping always takes place at the end of the hopping clock in order to maintain the same steadystate switching duty cycle. Thus, hopping from one frequency to another only occurs exactly at the end of the hopping rate for one frequency and at the beginning of the

Fig. 2. The implementation of Frequency hopping with thermometer decoder.

Fig. 3. Spectral analysis of a frequency hopped regulator with eight hopping frequencies.

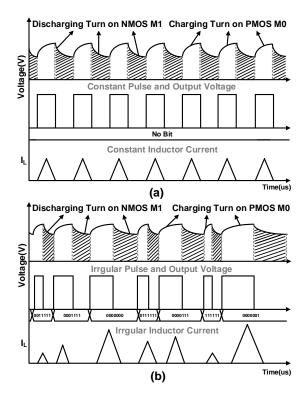

Fig. 4. Pulse-width modulated square wave output (a) Sawtooth mode, (b) FHTD mode.

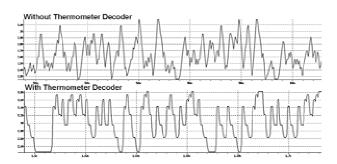

hopping clock of the next frequency. However, V<sub>BIAS\_SAW</sub> amplitude is not kept constant, because the charging and discharging current, I<sub>E</sub>, is fixed, as illustrated in Figs. 4(a) and (b), and is determined only by the reference voltages V<sub>COMPH</sub> and V<sub>COMPL</sub>. It reduces buck converter efficiency a little. Figs. 4 and 5 show comparisons of the sawtooth mode and frequency hopping mode. Fig. 4 uses the time domain to compare the two modes' switching on H\_PEN or H\_PENB to show how much the pulse duty differs. The pulse duty of the sawtooth mode is always constant from using a single frequency. On the other hand, eight different pulse duties at frequencies from 2MHz(500ns) ~ 3MHz (333ns) randomly operate. Output voltage distribution of sawtooth mode and frequency hopping mode were implemented for Fig. 5. The output voltage ripple is mainly affected by the frequency and inductor current. The

Fig. 5. The output ripple voltage wave from (a) Sawtooth mode, (b) FHTD mode.

inductor current ripples abruptly on switching frequency hops. The variation in the current ripple passes through the LC output filter and results in transient glitches in the output voltage for several switching periods. The transient glitches are generated whenever the switching frequency hops to control Mo and M1, with each MOS located in front of  $L_1$  and  $C_1$ . When PWM output pulse is low, NMOS  $M_1$  is turned on, so that  $L_1$  and  $C_1$  start charging, which increases the voltage level. Then, the PWM pulse goes up, PMOS  $M_0$  is turned off, NMOS is turned on, and  $L_1$  and  $C_1$  are discharged. Figs. 5(a) and (b) show the mechanisms of sawtooth mode and FHTD mode. Sawtooth mode has constant pulse width to make a half-duty cycle, so that charging and discharging times are equal. It generates the same voltage ripple in the output voltage. However, FHTD mode changes the pulse duty all the time and has irregular output voltage ripple from shifting frequency by frequency hopping. This voltage ripple in the frequency domain at 2~3MHz seems small, but the transient voltage ripples are larger in the time domain. It degrades modulation accuracy. Thus, the voltage ripple controller (VRC) is adapted to reduce glitches.

The proposed VRC [6] is composed of an RC filter and a transmission gate. The VRC input signal is based on the seven bits from the three-bit binary-to-thermometer decoder, and others that are inverted. It triggers seven-bit signals to smoothly control transmission gates in front of switching capacitance, in order to hold the voltage that controls the converter's switching frequency, and decreases the output voltage ripple by about 10%~20%. The waveforms in Fig. 5 illustrate the results of the output voltage ripple of the buck converter.

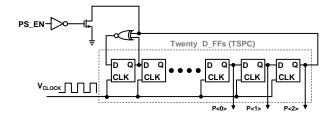

Fig. 6. Pseudo-random-number generator.

#### 2.1 Sawtooth Wave Generator

The sawtooth wave generator is composed of an SR latch and two hysteresis comparators [7]. Output voltage is  $V_{BIAS\ SAW}$ , switch  $M_1$  turns on when low voltage is applied, and switch M<sub>2</sub> turns on when high voltage is applied. As an initial condition,  $V_{BIAS\_SAW} = 0$ , output of the pulse comparator is low, and that of negative comparator is high, and the output of the SR latch is low. Because switch M<sub>1</sub> turns on and switch M2 turns off, capacitor CSAW is charged by current source IF, and the output voltage is founded on VBIAS =  $(I_F/C_{SAW})$ \*t. When  $V_{BIAS\ SAW}$  becomes V<sub>HIGH</sub>, the output of the negative comparator becomes high, and the output of the positive comparator becomes low, so that the output of the SR latch becomes high. Then, switch M<sub>1</sub> turns off, and switch M<sub>2</sub> turns on; charging  $C_{SAW}$  is finished, and discharging  $C_{SAW}$  starts. The charging/ discharging process is repeated continually until I<sub>F</sub> is cut. The sawtooth wave generator creates a single frequency related to current I<sub>F</sub> and C<sub>SAW</sub> sizes through the charging/discharging process.

#### 2.2 Pseudo-Random-Number Generator

A pseudo-random-number generator (PSNR) is used to make three-bit random digital code, as explained by Tao et al. [3]. The PSNR is basically a set of shift registers connected in series, with the output of some of the shift registers combined in an exclusive-OR configuration to provide a feedback mechanism. When the input of the register is fed with a seed value, and the PSNR is clocked, it generates a pseudo-random pattern of 1's and 0's. The clock comes from the output of the SR latch. Fig. 6 shows a 20-stage PSNR. A 20-stage shift resister can produce maximal code with a length of  $2^{20} - 1 = 1,048,575$  bits. This is large enough for the sequence to appear random. To eliminate the PSNR, the PS\_EN signal is used during startup to set the output of last flip-flop to 0, and then release it afterwards [3]. The three-bit random code created by the PSNR goes to the thermometer decoder.

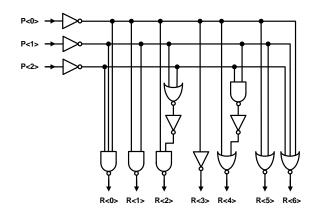

# 2.3 Three-bit Binary-to-Thermometer Decoder

The three-to-seven-bit binary-to-thermometer decoder implemented in frequency hopping is shown in Fig. 7. The three-bit binary code is decoded to digital thermometer code in order to reduce glitches. The control logic of the switches causes voltage spikes and affects the output

Fig. 7. Three-bit binary-to-thermometer decoder.

Fig. 8. Time-domain representation of the change-frequency operation.

voltage ripple of the buck converter. The three-to-sevenbit binary-to-thermometer decoder has better performance and less voltage ripple, compared with a three-to-eight-bit decoder and a gray code decoder. Because the converters are based on thermometer decoder code, they promise to be monotonic and do not change seven-bit code without changing MSB to LSB. The seven-bit code immediately controls capacitance bank switches in front of capacitance to vary the frequency, and maximizes the hopping rate so it is as fast as the regulator's switching frequencies when a PEN switch is turned on. In order to change frequency, the thermometer decoder spaces the frequencies at 125KHz (80ns) apart, and turns a transmission gate on or off through the VRC. If PSNR code goes directly to the control transmission gate, it generates change from MSB to LSB frequently, compared to using a thermometer decoder. This is illustrated in Fig. 8. Using a thermometer decoder is a better process than others. It more smoothly changes the frequency in the time domain, and does not frequently generate glitches.

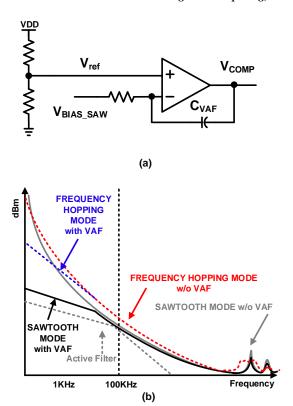

# 2.4 Voltage Averaging Feedback (VAF)

Voltage averaging feedback (VAF) is used to reduce flicker noise [4]. Flicker noise mainly comes from comparators that are in the sawtooth wave generator. The basic solution to efficiently reduce flicker noise is enlarging the size of transistors that impact noise. However, the large size of the gate increases the ratio of gate parasitic capacitors and increases current consumption.

Fig. 9. Voltage averaging feedback (a) structure, (b) VAF operation in the power module.

This does not match our motivation for low current consumption. Thus, the structure in Fig. 9(a) considers the dominant noise source first, and noise generated from the active filter in the VAF loop and the phase noise from the sawtooth wave generator second. The total phase noise is a summation of thermal noise applied in the closed loop transfer function. This function changes voltage to phase, phase to frequency, and frequency to averaged voltage, as explained by Tokunaga et al. [4]. Each VAF and sawtooth wave generator is operated as a low pass filter and a high pass filter for phase noise and summation phase noise [4]. The amplifier in Fig. 9(a) is used by the rail-to-rail amplifier to get enough phase margin. VAF is constantly fed by V<sub>BIAS\_SAW</sub>. V<sub>ref</sub> and V<sub>BIAS\_SAW</sub> are virtually shorted in a low-frequency domain defined by time constants R<sub>VAF</sub> and C<sub>VAF</sub>. Fig. 9(b) is the result of the phase noise spectrum at V<sub>COMP</sub>. It means that phase noise at a low offset frequency is dominated by the VAF. This affects low frequencies below 100KHz because of active filtering. However, spurious noise is dominated by switching frequency changing current or capacitance in the signal generator. Thus, VAF is hardly affected in the buck output spectrum. Nevertheless, it helps the BLE application because the most important frequency band in the BLE application is below 1MHz. Therefore, low noise in the low-frequency domain is the dominant area.

### 3. Experimental Result

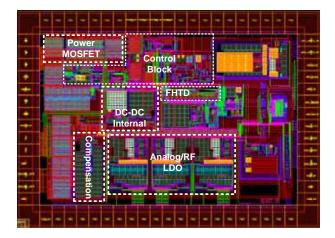

The measured result and layout for FHTD are

Fig. 10. Top Layout of the proposed regulator.

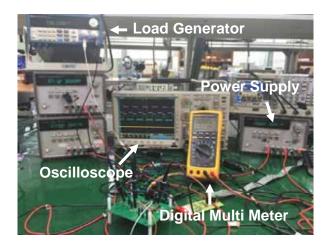

Fig. 11. The performance measurement environment.

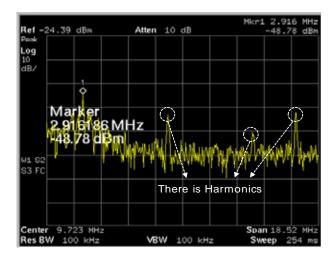

implemented in this section. Fig. 10 shows the top layout of the buck converter, and Table 1 compares the converter's key parameters in the buck converter. The total active area, including pads, is 1900 \* 1400 µm2 with FHTD. FHTD is a relatively small part of the whole process. Only 10% of this area is consumed by the additional circuitry required to implement the FHTD scheme. The DC-DC buck converter is measured using power supply and an oscilloscope, with the SPI PC, electric load generator and digital multi-meter. Fig. 11 shows how to make the measurement environment. The single switching frequency of 2.5MHz, which is sawtooth mode, is implemented, and changing switching frequency from 2MHz to 3MHz, which is the FHTD, is also implemented. Frequency hopping uses eight frequencies to spread the spectrum by spacing frequencies at 125KHz, chosen to maximize the spread and avoid the BLE application operation point. It reduces spurious noise up to -64dBm. All measurements were made at 1.7V output (VOUT) and 1~20mA load current. The output spectrum of the regulator was measured using a real-time spectrum analyzer with a resolution bandwidth of 500MHz. The output spectrum shows up to 20MHz in sawtooth mode and FHTD mode. Fig. 12 shows the output spectrum of DC-DC out (Vout) in sawtooth mode. The maximum spur

| Parameters                   | This Work                                                                  | [9]                     | [3]                                          | [8]                                    | [2]                                             | [1]               |

|------------------------------|----------------------------------------------------------------------------|-------------------------|----------------------------------------------|----------------------------------------|-------------------------------------------------|-------------------|

| Technology                   | 0.13 μm                                                                    | 0.18 μm                 | 0.35 μm                                      | 40 nm                                  | 0.35 μm                                         | N/A               |

| Control<br>Methodology       | PWM+Frequency<br>hopping &Thermometer<br>decoder +LDO with<br>PSR enhancer | Frequency<br>Stepping   | PWM+Frequency<br>hopping & phase<br>chopping | PNT-COT<br>controlled SWR<br>with SSFC | 3 <sup>rd</sup> CT-Sigma<br>Delta<br>Mdoulation | SSCG              |

| Spread Spectrum<br>Operation | Hard<br>Switching                                                          | Hard<br>Swiching        | Hard<br>Switching                            | Soft<br>Switching                      | Soft<br>Switching                               | Hard<br>Switching |

| Number of Frequencies        | 8                                                                          | 64                      | 8                                            | N/A                                    | N/A                                             | N/A               |

| Switching Frequney (MHz)     | 2~3                                                                        | 2.2~4.4                 | 3~6.5                                        | 0.5~8                                  | 8                                               | 0.1~1             |

| Output voltage ripple        | 2.2~3.4 mV                                                                 | N/A                     | N/A                                          | 35 mV                                  | Below 17 mV                                     | N/A               |

| Peak Noise Floor             | -64dBm/Hz                                                                  | -56dBm/Hz               | -90dBm/Hz                                    | -72dBm/Hz                              | -53.2dBm/Hz                                     | N/A               |

| Active area                  | 320*120 μm <sup>2</sup>                                                    | 250*100 μm <sup>2</sup> | 0.36 mm²                                     | 680*700 μm <sup>2</sup>                | 1.4 mm²                                         | N/A               |

| DC-DC efficiency             | 86%                                                                        | 92%                     | N/A                                          | 92%                                    | 78~92%                                          | N/A               |

Table 1. Comparison of spread spectrum operation in DC-DC switching power modulator.

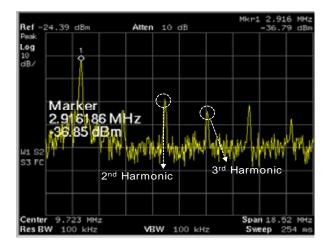

Fig. 12. The DC-DC output spectrum measured

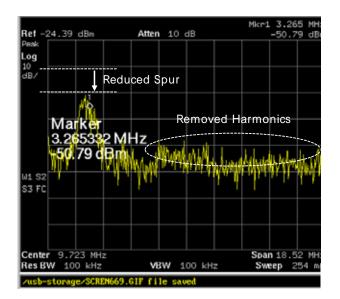

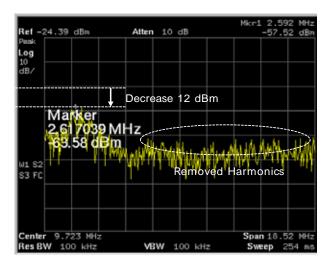

Fig. 13. The DC-DC output spectrum measured result in FHTD mode

Fig. 14. The LDO voltage regulator output spectrum's measured result in sawtooth mode

is -36dBm, and there are second and third harmonics. FHTD mode is shown in Fig. 13 using eight frequencies.

The harmonics were removed, but increasing the noise floor was affected by spread spectrum. Average reduced spur is almost 15~16dBm. There is a difference between the theoretical value and the measured value due to parasitic capacitance and resistance in a bond wire. LDO with PSR enhancement, which is not presented in this paper, affects spurious noise degradation by almost 12dBm, adjusting the enhancer frequency at 2.5MHz. Figs. 14 and 15 show the results of each mode.

The output spectrum of the LDO voltage regulator reduces spurs and the noise floor. The total output noise reduction is an almost 26dBm degradation. Operated hopping to the frequency worsens the output voltage ripple. Output voltage ripple was already shown in Fig. 5, and output voltage ripple is consistently at 3mV in sawtooth mode, whereas it varies between 2.2mV and 3.4mV in FHTD mode. It is very important to note that hopping between one switching frequency to another does not

Fig. 15. The LDO voltage regulator output spectrum's measured result in FHTD mode

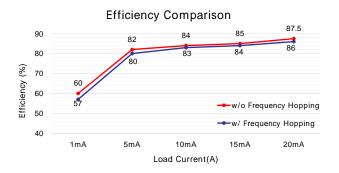

Fig. 16. The efficiency of the DC-DC buck converter with FHTP or without FHTP

produce large transients in buck output [5]. This ripple loss reduces the efficiency of the buck converter by less than 2% in Fig. 16. Each load current creates different efficiencies. The highest efficiency of the DC-DC converter is at 20mA load current.

### 4. Conclusion

In this paper, the proposed buck converter, combining frequency hopping with a thermometer decoder in 0.13 CMOS technology with a 3.3V Li-ion battery and a 1.2V internal LDO voltage regulator supply voltage is fully analyzed and implemented. The buck converter uses synchronous frequency hopping with eight hopping frequencies to achieve up to -26dB reduction in output spurs with a 125KHz hopping rate. It is a very attractive circuit for designing generic low-noise power supplies for spur-sensitive loads, as well as for loads that are sensitive to the random noise floor without post-line regulation, extra passive filtering, or customization for each load [3]. It occupies 10% of the overall system area and consumes just 20uA. Besides, the overall efficiency of the buck converter is not sacrificed much below 1.1%. This circuit is more useful than others [1-3, 8, 9]. Additionally, it is easily incorporated with an already existing PWM controller by adding a pseudo-random-number generator and capacitance bank.

## **Acknowledgement**

This research was supported by the Ministry of Science, ICT and Future Planning (MSIP), Korea, under the Information Technology Research Center (ITRC) support program (IITP-2015-H8501-15-1010) supervised by the Institute for Information & Communications Technology Promotion (IITP).

This work was also supported by IDEC (IPC, EDA Tool, and MPW).

#### References

- [1] J. Balcells et al., "EMI Reduction in Switched Power Converters Using Frequency Modulation Techniques," *IEEE Trans. Electromagn. Compat.*, vol.47, no. 3, Aug., 2005. <u>Article (CrossRef Link)</u>

- [2] W. Yan et al., "A noise-shaped Buck DC-DC converter With Improved Light-Load Efficiency and Fast Transient Response" *IEEE Trans. Power Electron.*, vol. 26, no. 12, Dec., 2011. <a href="Article (CrossRef Link">Article (CrossRef Link)</a>)

- [3] C. Tao et al., "PWM Control Architecture With Constant Cycle Frequency Hopping and Phase Chopping for Spur-Free Operation in Buck Regulators" *IEEE Trans. VLSI System*, vol. 21, no. 9, Sep., 2013. Article (CrossRef Link)

- [4] Y. Tokunaga et al., "An On-Chip CMOS Relaxation Oscillator With Voltage Averaging Feedback" *IEEE J. Solid-State Circuits*, vol. 45, no. 6, June 2010. Article (CrossRef Link)

- [5] C. Tao et al., "A Low-Noise PFM-Controlled Buck Converter for Low-Power Applications" *IEEE Trans. Circuit Syst.* I, Reg. Papers, vol. 59, no. 12, Dec. 2012. Article (CrossRef Link)

- [6] P. J. Jiu et al., "Spur-Reduction Design of Frequency-Hopping DC-DC Converters" *IEEE Trans. Power Electron.*, vol. 27, no.11 Nov. 2012. <u>Article (CrossRef Link)</u>

- [7] Kun-Chun Chang et al., "A Fast Hysteretic Buck DC-DC converter with Start-up Overshoot Suppression technique" 2012 Asia Pacific Conference on Postgraduate research in Microelectronics and Electronics (PrimeAsia), pp. 56-60, Dec. 2012. Article (CrossRef Link)

- [8] Y. P. Su et al., "A Pseudo-Noise Coded Constant-off-time(PNT-COT) Control Switching Converter with Maximum 18.7dBm Peak Spur Reduction and 92% Efficiency in 40nm CMOS" 2013 Symposium on VLSI Circuits Digest of Technical Papers, pp. c170-c171, Jun. 2013. <a href="https://example.com/Article/Article/Article/Article/Article/Article/Article/Article/Article/Article/Article/Article/Article/Article/Article/Article/Article/Article/Article/Article/Article/Article/Article/Article/Article/Article/Article/Article/Article/Article/Article/Article/Article/Article/Article/Article/Article/Article/Article/Article/Article/Article/Article/Article/Article/Article/Article/Article/Article/Article/Article/Article/Article/Article/Article/Article/Article/Article/Article/Article/Article/Article/Article/Article/Article/Article/Article/Article/Article/Article/Article/Article/Article/Article/Article/Article/Article/Article/Article/Article/Article/Article/Article/Article/Article/Article/Article/Article/Article/Article/Article/Article/Article/Article/Article/Article/Article/Article/Article/Article/Article/Article/Article/Article/Article/Article/Article/Article/Article/Article/Article/Article/Article/Article/Article/Article/Article/Article/Article/Article/Article/Article/Article/Article/Article/Article/Article/Article/Article/Article/Article/Article/Article/Article/Article/Article/Article/Article/Article/Article/Article/Article/Article/Article/Article/Article/Article/Article/Article/Article/Article/Article/Article/Article/Article/Article/Article/Article/Article/Article/Article/Article/Article/Article/Article/Article/Article/Article/Article/Article/Article/Article/Article/Article/Article/Article/Article/Article/Article/Article/Article/Article/Article/Article/Article/Article/Article/Article/Article/Article/Article/Article/Article/Article/Article/Article/Article/Article/Article/Article/Article/Article/Article/Article/Article/Article/Article/Article/Article/Article/Article/Article/Article/Article/Article/Article/Article/Article/Article/Arti

- [9] E. J. Kim et al., "Spurious Noise Reduction by Modulating Switching Frequency in DC-to-DC Converter for RF Power Amplifier" *IEEE RFIC Symposium*, pp.43-46, May. 2010. <u>Article (CrossRef Link)</u>

**Ju-Hyun Park** received his B.Sc from the Department of Electronic Engineering at Hankuk University of Foreign Studies (HUFS), Gyeonggi-Do, Korea, in 2013. He is currently working toward an MSc in the School of Information and Communication Engineering at Sungkyunkwan University.

His research interests include Power Management ICs and CMOS RF transceivers.

Sang Yun Kim received his BSc from the Department of Electronic Engineering at Konkuk University, Seoul, Korea, in 2013. He is currently working toward a combined PhD & MSc in the School of Information and Communication Engineering at Sungkyunkwan University. His research inter-

ests include high-speed interface ICs and CMOS RF transceivers.

Sung Jin Kim received his BSc from the Department of Electronic Engineering at Inje University, Kimhea, Korea, in 2014. He is currently working toward a combined PhD & MSc in the School of Information and Communication Engineering at Sungkyunkwan University. His research interests in-

clude CMOS RF transceivers and wireless power transfer systems

Hong Jin Kim received his BSc from the Department of Electronic Engineering at Chungju University, Chungju, Korea, in 2010. He is currently working toward a PhD in the College of Information and Communication Engineering at Sungkyunkwan University. His research interests include

CMOS RF transceivers, power management ICs and mixed signal integrated circuits.

Joo Young Lee received his BSc from the Department of Electronic Engineering at Incheon National University, Incheon, Korea, in 2014. He is currently working on an MSc in the School of Information and Communication Engineering at Sungkyunkwan University. His research interests include

power management ICs

Kang-Yoon Lee was born in Jeongup, Korea, in 1972. He received his BSc, MSc and PhD in the School of Electrical Engineering at Seoul National University, Seoul, Korea, in 1996, 1998, and 2003, respectively. From 2003 to 2005, he was with GCT Semiconductor Inc., San Jose, CA,

where he was a Manager of the Analog Division and worked on the design of CMOS frequency synthesizers for CDMA/PCS/PDC and single-chip CMOS RF for W-CDMA, WLAN, and PHS chip sets. From 2005 to 2011, he was with the Department of Electronics Engineering, Konkuk University as an Associate Professor. Since 2012, he has been with School of Information and Communication Engineering, Sungkyunkwan University, where he is currently an Associate Professor. His research interests include implementation of power integrated circuits, CMOS RF transceivers, analog integrated circuits, and analog/digital mixed-mode VLSI systems.

Sang Hyeon Park received his BSc from the Department of Electronic Engineering at Myongji University, Yongin, Gyeonggi-Do, Korea, in 2013. He is currently working toward an MSc in the School of Information and Communication Engineering at Sungkyunkwan University. His research

interests include power ICs and CMOS RF transceivers.

**Ju Ri Lee** received her BSc from the Department of Electronic Engineering at Konkuk University, Seoul, Korea, in 2013. She is currently working toward a combined PhD & MSc in the School of Information and Communication Engineering, Sungkyunkwan University. Her research interests include

VCSEL drivers and CMOS RF transceivers.