JPE 15-4-10

http://dx.doi.org/10.6113/JPE.2015.15.4.964 ISSN(Print): 1598-2092 / ISSN(Online): 2093-4718

# Generalized Selective Harmonic Elimination Modulation for Transistor-Clamped H-Bridge Multilevel Inverter

Wahidah Abd. Halim<sup>†,\*,\*\*\*</sup>, Nasrudin Abd. Rahim<sup>\*</sup>, and Maaspaliza Azri<sup>\*\*</sup>

†\*\*Faculty of Electrical Engineering, Universiti Teknikal Malaysia Melaka, Melaka, Malaysia \*UM Power Energy Dedicated Advanced Centre (UMPEDAC), University of Malaya, Kuala Lumpur, Malaysia \*\*\*Department of Electrical Engineering, Faculty of Engineering, University of Malaya, Kuala Lumpur, Malaysia

#### Abstract

This paper presents a simple approach for the selective harmonic elimination (SHE) of multilevel inverter based on the transistor-clamped H-bridge (TCHB) family. The SHE modulation is derived from the sinusoidal voltage-angle equal criteria corresponding to the optimized switching angles. The switching angles are computed offline by solving transcendental non-linear equations characterizing the harmonic contents using the Newton-Raphson method to produce an optimum stepped output. Simulation and experimental tests are conducted for verification of the analytical solutions. An Altera DE2 field-programmable gate array (FPGA) board is used as the digital controller device in order to verify the proposed SHE modulation in real-time applications. An analysis of the voltage total harmonic distortion (THD) has been obtained for multiple output voltage cases. In terms of the THD, the results showed that the higher the number of output levels, the lower the THD due to an increase number of harmonic orders being eliminated.

**Key words:** Harmonic elimination, Multilevel inverter, Pulse-width modulation (PWM), Single-phase inverter, Total harmonic distortion (THD)

# I. INTRODUCTION

Recently, the demand for medium-voltage, higher power converters that are capable of producing high quality waveforms, while utilizing low voltage devices and reduced switching frequencies have led to increases in multilevel inverter development. Over the years, several multilevel inverter topologies have been developed as alternatives for medium voltage and high power applications, and they offer advantages over the single switch and series connection approaches [1]. Multilevel inverters have been shown to have the following advantages: reduce common-mode voltage,

lower switching stress, lower total harmonic distortion (THD), improve output voltage/current quality, etc. [2]-[4].

The most common multilevel inverter topologies include the diode clamped or neutral point clamped (NPC), capacitor clamped or flying capacitor (FC), and cascaded H-bridge (CHB) inverters [3]-[8]. It is absolutely necessary to produce an effective and innovative power converter design, from the perspective of cost and efficiency, for optimizing output power with significantly fewer losses. The requirements for the maximum voltage and current total harmonic distortions (THDs), as specified in IEEE Std.519-1992, must be fulfilled by the multilevel inverter [9]. Some researchers have overcome the complexity of the multilevel inverter circuit by rearranging the switches and DC voltage sources [10]. This produces a new breed of multilevel topologies: the active NPC (ANPC) [11], modular multilevel converter (MMC) [12] transistor-clamped converter (TCC) [13], [14].

To obtain a good output voltage, various modulation algorithms have been developed for multilevel inverters. They are classified according to their switching frequency. Each has

Manuscript received Jan. 7, 2015; accepted Mar. 21, 2015

Recommended for publication by Associate Editor Liqiang Yuan.

<sup>&</sup>lt;sup>†</sup>Corresponding Author: wahidahhalim@utem.edu.my

Tel: +606-555 2345, Fax: +606-555 2266, Universiti Teknikal Malaysia Melaka

<sup>\*</sup>UM Power Energy Dedicated Advanced Centre (UMPEDAC), University of Malaya, Malaysia

<sup>\*\*</sup>Fac. of Electrical Eng., Univ. Teknikal Malaysia Melaka, Malaysia

<sup>\*\*\*\*</sup>Dept. of Electrical Eng., Fac. of Eng., University of Malaya, Malaysia

unique advantages and drawbacks and their selection is made according to the application and the inverter topology. When the high switching frequency exceeds 1 kHz [3], the schemes involve multireference/multicarrier pulse-width modulation (PWM) [2],[13],[15] and space-vector modulation (SVM) [7]. Although the acoustic noise is low and in some cases the output filter size is also reduced, the high switching frequency technique increases the switching losses and is complicated in eliminating low-order harmonics. Another modulation algorithm for multilevel inverters running on the low (or fundamental) switching frequency [16]-[23] is selective harmonic elimination (SHE). There are two different aims when using the low switching frequency modulation technique: 1) to eliminate the specific lowest order harmonics of the inverter output voltage; and 2) to minimize the inverter voltage THD. Such a scheme lets the power semiconductors have very few commutations per output cycle. This has the advantages of reducing the switching losses, eliminating the low-order harmonics, and allowing for a smaller size filter if necessary [16].

To address the SHE problems, the determination of the optimized switching angles is essential through solving a set of non-linear transcendental equations. The transcendental equations, which are defined as SHE equations, characterize the harmonic components with respect to the fundamental voltage component based on the Fourier series expansion. As these equations increase, solving them becomes a challenge. One of the most widely used techniques is the Newton-Raphson (NR) method [17], [18]. This is an iterative method to find complex roots in polynomials and roots of equations with several variables. Another approach for the SHE method, based on optimization algorithms utilizing genetic algorithm (GA), has been proposed to calculate the optimum angles for CHB multilevel inverters [18]-[20]. A particle swarm optimization (PSO) technique has been used to calculate the switching angles of an 11-level inverter with equal and unequal DC source cases in [18], [21], [22]. Although optimization methods based on GA and PSO are frequently proposed in reducing calculation time, the harmonic elimination will be difficult to implement owing to the advanced control and the urge to use advanced mathematical algorithms.

To date, most of the low switching frequency modulations have been realized for the CHB topology, either in single-phase or three-phase systems. However, the CHB topology has some drawbacks since it requires a higher number of switching devices and isolated DC power supplies as the number of output levels is increased. Recently, the authors in [23] have proposed the harmonic distortion minimization method, with or without the elimination of the lowest order harmonics for a higher number of voltage level (i.e. 5-level up to 13-level). Although the proposed method in [23] may achieve the minimum voltage THD, it necessitates the use of a larger AC

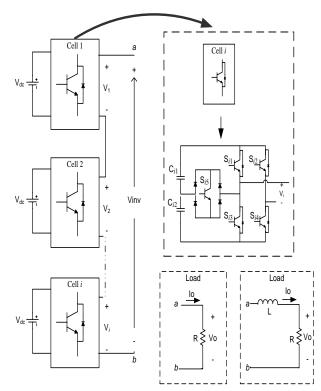

Fig. 1. The TCHB based cascaded multilevel inverter topology.

output filter, as pointed out in [16]. Moreover, the implementation results for 11- to 13-level cases have been excluded in [23]. Therefore, in this paper, the real implementation of SHE modulation for up to 13-level inverter output is demonstrated.

The evaluation of different output voltage levels and THD performance of single-phase transistor-clamped H-bridge (TCHB) multilevel inverters using SHE modulation has never been reported before. Therefore, a generalized SHE modulation scheme is presented to investigate the performance of a family of TCHB based on cascaded multilevel inverter. The SHE scheme is used in order to eliminate the low-order harmonic components while minimizing the output voltage THD of the adopted inverter. To verify the effectiveness of the proposed SHE modulation, an inverter prototype is built by utilizing a field-programmable gate array (FPGA) as the digital controller. The analytical, simulation and experimental results are presented in this paper.

# II. THE TCHB MULTILEVEL INVERTER CONFIGURATION

Fig. 1 depicts the general configuration of the single-phase TCHB inverter topology [13],[24]. Each TCHB inverter unit is added with one bidirectional switch comprised of one transistor with four diodes together with a conventional H-bridge inverter. Table I lists the five modes of operation of the adopted inverter. A five-level voltage output  $(0, \pm \frac{1}{2}V_{dc} \text{ and } \pm V_{dc})$  is produced in a single unit of the TCHB inverter. Half of the output voltages

TABLE I GENERAL SWITCHING STATES AND THE VOLTAGE LEVELS OF 5-LEVEL TCHB INVERTER

| Mode | Switches ON            | Voltage level        |

|------|------------------------|----------------------|

| 1    | $S_{i1}, S_{i4}$       | $+V_{dc}$            |

| 2    | $S_{i4}, S_{i5}$       | $+\frac{1}{2}V_{dc}$ |

| 3    | $S_{i1}, S_{i2}$       | 0                    |

|      | (or $S_{i3}, S_{i4}$ ) |                      |

| 4    | $S_{i2}, S_{i5}$       | -1/2 $V_{dc}$        |

| 5    | $S_{i2}, S_{i3}$       | $-V_{dc}$            |

TABLE II

GENERAL COMPARISONS FOR VARIOUS SINGLE-PHASE

N-LEVEL INVERTER TOPOLOGIES

| Criteria    | TCHB  | NPC   | FC                                                        | СНВ   |

|-------------|-------|-------|-----------------------------------------------------------|-------|

| Number of   | n     | n     | n                                                         | n     |

| level       |       |       |                                                           |       |

| Power       | 1.25* | 2*    | 2*                                                        | 2*    |

| switches    | (n-1) | (n-1) | (n-1)                                                     | (n-1) |

| Power       | n-1   | 2*    | -                                                         | -     |

| diodes      |       | (n-3) |                                                           |       |

| DC bus      | n-1   | n-1   | n-1                                                       | n-1   |

| capacitors  |       | 2     |                                                           | 2     |

| Balancing   | -     | -     | $\lceil (n-1) \rceil$                                     | -     |

| capacitors  |       |       | $2\left\lfloor \left(\frac{n-1}{2}\right)-1\right\rfloor$ |       |

| Isolated DC | n-1   | 1     | 1                                                         | n-1   |

| supplies    | 4     |       |                                                           | 2     |

are produced through the proper switching of  $S_{i5}$  and  $S_{i2}$  or  $S_{i4}$ , where i is the number of TCHB cells. Through combinations of the "on" state of the switches ( $S_{i1}$ - $S_{i5}$ ), the cell output voltage  $V_i$  is given by:

$$V_i = V_{dc}(S_{i4} - S_{i2}) \left\{ \frac{1}{2} S_{i5} + \left| S_{i1} - S_{i2} \right| \cdot \left| S_{i3} - S_{i4} \right| \right\}$$

(1)

This arrangement enables a higher output voltage, owing to the fact that the synthesized AC output voltage is the sum of individual inverter voltages. Note that when the TCHB cells are connected in cascade, the total inverter output voltage  $V_{\it inv}$  is given by:

$$V_{inv} = V_1 + V_2 + \dots + V_i \tag{2}$$

Generally, the adopted topology has 4i + 1 output levels (where i is the number of TCHB cells). Connecting two units of the TCHB inverter in series will produce a 9-level output. Meanwhile, if three units of the TCHB inverter are in series, a maximum of 13-level output is produced.

Table II shows a general comparison between the adopted TCHB topology and the conventional NPC, FC, and CHB multilevel inverter topologies. It is clear that, for the same number of output levels (*n*-level), the adopted TCHB inverter has a lower number of power switches and isolated DC sources when compared to the conventional multilevel inverter topologies. However, under certain circumstances, such as during a sudden large disturbance or transient conditions, the DC-link capacitor voltages in the TCHB inverter may become unbalanced [24]. Therefore, as discussed in [25], a voltage-balancing technique, either by hardware or software, is

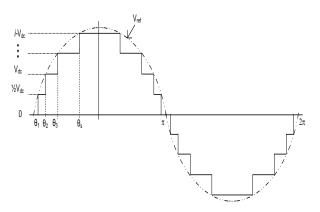

Fig. 2. The inverter output voltage  $V_{inv}$  waveform.

required to prevent capacitor voltage imbalances. The simplest approach is to use a larger value for the capacitance [13], [24]. This method is adopted in this paper.

### III. BACKGROUND OF SHE MODULATION

The intention of this paper is to produce an output waveform for a single-phase system with the capability to dispose of specific low-order harmonics while maintaining its fundamental voltage. It is possible to determine the switching angle through the Newton-Raphson (NR) method. The NR method is one of the most widely used methods for root-finding. It starts with an initial approximation, and then converges on a good initial guess. In general, the Fourier series of the inverter output voltage  $V_{inv}$  (see Fig. 2) is given by:

$$V_{inv}(\omega t) = a_0 + \sum_{n=1}^{\infty} \left[ a_n \cos(n\omega t) + b_n \sin(n\omega t) \right]$$

(3)

As the Fourier series contains only a sine term, the coefficients  $a_0$  and  $a_n$  are zero for all of the n harmonics. All of the even harmonics are zero. Therefore, the inverter output voltage  $V_{inv}$  waveform can be expressed as [2]:

$$V_{inv}(\omega t) = \frac{2V_{dc}}{n\pi} \sum_{n=1,2,5}^{\infty} [\cos(n\theta_1) + \dots + \cos(n\theta_s)] \sin(n\omega t)$$

(4)

where  $\theta_1 - \theta_s$  are the switching angles at each level in the first quarter waveform. They need to satisfy the following condition:

$$0 < \theta_1 < \theta_2 < \dots < \theta_s < \pi/2 \tag{5}$$

From (4), the expression of the fundamental voltage  $V_1$  is given by:

$$\frac{2V_{dc}}{\pi}[\cos(\theta_1) + \cos(\theta_2) + .... + \cos(\theta_s)] = V_1$$

(6)

The modulation index M can be defined from (6) as:

$$M = \frac{\pi V_1}{2sV_{DC}} \quad (0 \le M \le 1) \tag{7}$$

where s is the number of positive steps in a quarter waveform.

The switching angles of the adopted inverter in a single-phase system can be obtained by solving the following

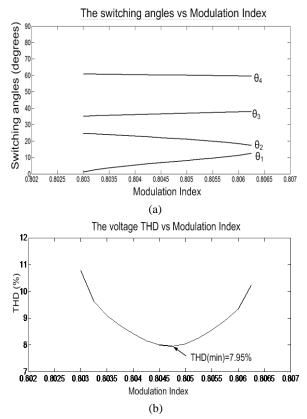

Fig. 3. The solutions for 9-level inverter. (a) The switching angles. (b) The voltage THD.

transcendental equations:

$$\cos(\theta_1) + \cos(\theta_2) + \dots + \cos(\theta_s) = sM$$

$$\cos(3\theta_1) + \cos(3\theta_2) + \dots + \cos(3\theta_s) = 0$$

$$\cos(5\theta_1) + \cos(5\theta_2) + \dots + \cos(5\theta_s) = 0$$

$$\vdots$$

$$\cos(n\theta_1) + \cos(n\theta_2) + \dots + \cos(n\theta_s) = 0$$

(8)

In this group of equations, the first equation guarantees the desired fundamental component, while the remaining equations ensure the elimination of specific low-order harmonics as they dominate the THD. The set of switching angles is then examined for its THD to select the best solution, the one with the lowest THD. The computed voltage THD is defined by:

$$THD_{\mathbf{V}} = \frac{\sqrt{\sum_{n=2}^{\infty} V_n^2}}{V_1} \tag{9}$$

The following steps are executed to implement the proposed SHE modulation:

- Calculation of the switching angles is performed in Matlab via the NR method. The solution is computed with an arbitrary initial guess for the switching angles as M is varied from 0 to 1 in steps of 0.001.

- By utilizing the voltage-angle equal criteria of a sinusoidal reference waveform, the threshold voltages corresponding to the calculated switching angles are

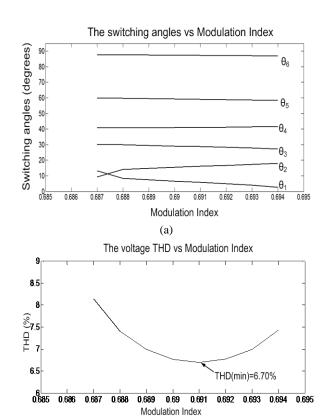

(b) Fig. 4. The solutions for 13-level inverter. (a) The switching angles. (b) The voltage THD.

recognized.

The gating signals are produced from a correlation of the voltage reference with respect to the threshold voltages and some combinational logics.

# A. The SHE Modulation for a 9-level TCHB Inverter

The solution sets of switching angles to cancel the 3rd, 5th and 7th harmonics for a single-phase 9-level TCHB inverter in some of the modulation indices range are depicted in Fig. 3(a). The minimum THD values of these angles is 7.95%. This is calculated according to (9), as shown in Fig. 3(b).

### B. The SHE Modulation for a 13-level TCHB Inverter

Either of the switching angles set in Fig. 4(a) can be used in a 13-level TCHB inverter to eliminate the 3rd, 5th, 7th, 9th, and 11th harmonics. Fig. 4(b) shows a 6.7% minimum THD in a single-phase 13-level TCHB inverter.

# IV. THE GENERALIZED SHE MODULATION AND ITS IMPLEMENTATION

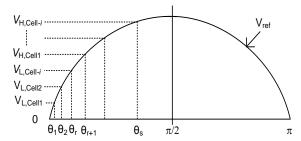

The generalized SHE modulation for the TCHB inverter family is derived from one sinusoidal reference signal and several triggered voltage levels ( $V_L$  and  $V_H$ ) as illustrated in Fig. 5. The two voltages  $V_L$  and  $V_H$  are classified as the triggered voltage levels, which correspond to the switching angles of the related cell. For the developed SHE technique, only a

Fig. 5. The generalized reference signal and triggered voltages.

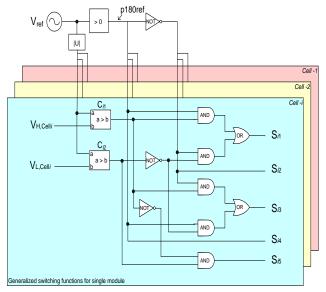

Fig. 6. Generalized SHE scheme for TCHB multilevel inverter.

half-wave diagram is illustrated. According to Fig. 5, the reference voltage  $V_{ref}$  is defined as:

$$V_{ref} = V_m \sin \omega \ t \tag{10}$$

where  $V_m$  is an arbitrary (peak) value.

The relationships between the switching angles and the triggered voltage levels in one TCHB cell are provided in the following equations:

$$V_{L,Cell i} = \sin(\theta_r \times \pi/180) \times V_m$$

$$V_{H,Cell i} = \sin(\theta_s \times \pi/180) \times V_m$$

$$(11)$$

where *i* is the number of TCHB cells, r = 1, 2, ... i, and s = r + i.

To perform SHE modulation for the adopted 9-level TCHB inverter topology, a simple calculation for the triggered voltage levels is derived from the calculated switching angles  $(\theta_1 - \theta_4)$  by using the voltage-angle equal criteria. There are four voltage levels  $(V_{L,Cell1}, V_{L,Cell2}, V_{H,Cell1})$  and  $V_{H,Cell2})$  during the positive half-cycle of the modulating signal. These triggered voltage level calculations are based on the angle measurement in radians. Hence, the voltage levels can be computed as follows:

$$V_{L,Cell\ 1} = \sin(\theta_1 \times \pi/180) \times V_m$$

$$V_{L,Cell\ 2} = \sin(\theta_2 \times \pi/180) \times V_m$$

$$V_{H,Cell\ 1} = \sin(\theta_3 \times \pi/180) \times V_m$$

$$V_{H,Cell\ 2} = \sin(\theta_4 \times \pi/180) \times V_m$$

(12)

TABLE III SWITCHING ANGLES FOR 9-LEVEL AND 13-LEVEL TCHB INVERTERS

| No. | Case     | Switching Angles (°)                |

|-----|----------|-------------------------------------|

| 1   | 9-level  | [7.5, 21.6, 36.8, 60.2]             |

| 2   | 13-level | [4.9, 16.8, 28.3, 41.2, 58.9, 87.2] |

The sequence is chosen so that cell 1 operates at the angles  $\theta_1$  &  $\theta_3$ , and cell 2 operates at the angles  $\theta_2$  &  $\theta_4$ , in order to avoid over-burdening any particular cell. Moreover, similar approaches can be applied to any angle, any number of voltage levels and any type of multilevel inverter topology.

The proposed SHE modulation requires the two main modules of the sine-wave generator and the combinational logics as illustrated in Fig. 6. The modulus operation of a sinusoidal waveform has been included since the steps of the output voltage in other regions are sequential. The SHE control scheme can be extended to any number of TCHB cells. The switches  $S_{i1}$ ,  $S_{i3}$ , and  $S_{i5}$  (where i is the number of TCHB cells) operate by comparing the reference signal with the triggered voltage levels and through the combinational logic gates, while  $S_{i2}$  and  $S_{i4}$  operate complementarily in the half cycle of the reference signal. The general logic expressions (using AND, OR and NOT gates) for the gating signals are given as follows:

$$S_{i1} = (C_{i1} \cdot p180 \ ref) + (\overline{C_{i2}} \cdot \overline{p180 \ ref})$$

$$S_{i2} = \overline{p180 \ ref}$$

$$S_{i3} = (C_{i1} \cdot \overline{p180 \ ref}) + (\overline{C_{i2}} \cdot p180 \ ref)$$

$$S_{i4} = p180 \ ref$$

$$S_{i5} = \overline{C_{i1}} \cdot C_{i2}$$

$$(13)$$

where  $C_{i1}$  and  $C_{i2}$  are the outputs of the comparators and the p180ref signal is the  $180^{\circ}$  reference based on the frequency of the reference signal, which is also identified as the  $S_{i4}$  signal.

#### V. SIMULATION AND EXPERIMENTAL RESULTS

#### A. Simulation Results

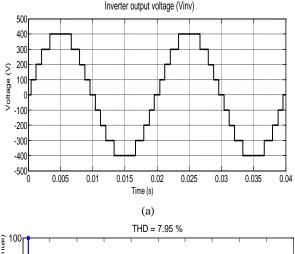

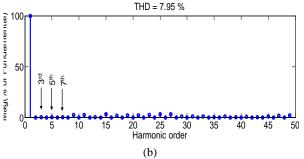

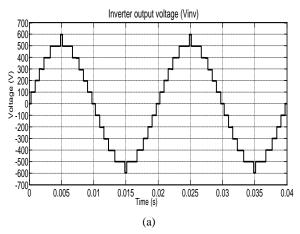

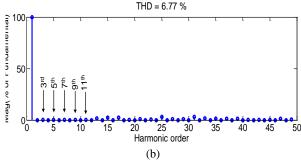

In order to verify the proposed SHE modulation, the adopted inverter is simulated using Matlab/Simulink. Two types of simulation tests are carried out to produce 9-level and 13-level output waveforms. An equal DC voltage input of 200 V was considered for each of the 5-level TCHB inverter modules. The frequency of the inverter was set at 50 Hz. The inverter circuit arrangement was similar to that in Fig. 1. In both configurations, the generated inverter outputs were triggered at the points of the switching angle. The set of switching angles in Table III was selected at the point of minimum THD, from the solution sets plotted in Figs. 3(a) and 4(a) for the 9-level and 13-level TCHB inverters, respectively.

The 9-level TCHB inverter arrangement incorporates two TCHB inverter units and two equal isolated DC sources. The simulation for the 9-level TCHB inverter produced Figs. 7(a) and 7(b). The 9-level inverter's 7.95% voltage THD was

Fig. 7. Simulation results of 9-level TCHB inverter. (a) The inverter output voltage. (b) The voltage THD.

Fig. 8. Simulation results of 13-level TCHB inverter. (a) The inverter output voltage. (b) The voltage THD.

similar to the calculated value [see Fig. 3(b)], and only the 3rd, 5th and 7th harmonics were eliminated.

Fig. 9. The overall experimental setup.

# TABLE IV THE EXPERIMENT SPECIFICATIONS

| Parameter                                | Values     |

|------------------------------------------|------------|

| DC source for each TCHB module, $V_{dc}$ | 120 V      |

| DC-link capacitors                       | 3300 μF    |

| IGBT                                     | IRG4PC50UD |

| Diode                                    | 30CPF12PBF |

| Load resistance, R                       | 130 ohm    |

| Load inductor, L                         | 81 mH      |

The 13-level TCHB inverter it is built with three TCHB inverter units and three equal isolated DC supplies. The simulation results for the 13-level TCHB inverter are shown in Figs. 8(a) and 8(b). The 13-level inverter's 6.77% voltage THD paralleled the calculated value [see Fig. 4(b)], and the 3rd, 5th, 7th, 9th, and 11th harmonics were eliminated.

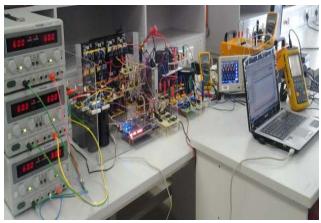

#### B. Experiment Results

To demonstrate the validity of the proposed SHE control algorithm, a DE2 Altera FPGA board was used as the digital controller. It is a cost-effective board that incorporates a Cyclone II 2C35 FPGA device. The SHE controller was designed by using Verilog high-level description language (HDL) code and schematic design entries in Quartus II software. The corresponding voltages are stored in the FPGA memory and the switching patterns were formed through some combinational logics for real-time application.

A single-phase TCHB inverter prototype has been constructed as depicted in Fig. 9. The experimental parameters for the adopted TCHB multilevel inverter are listed in Table IV. The inverter was supplied by GW Instek (GPC6030D) isolated DC sources with  $V_{dc}=120~\rm V$  for each of the cells. The prototype uses IGBTs (IRG4PC50UD) as the switching devices and power diodes (30CPF12PBF) as part of the bidirectional switch element. Each of the TCHB units uses two 3300  $\mu$ F electrolyte capacitors as the DC-link capacitors. A large capacitance is used to reduce the effects of the voltage imbalance [13], [24] so that the voltage across each capacitor is maintained at approximately  $\frac{1}{2}V_{dc}$  throughout the course of the experiment. Two types of loads were set, i.e., a highly resistive load that uses only a resistor  $R=130~\Omega$ ; while the later for an

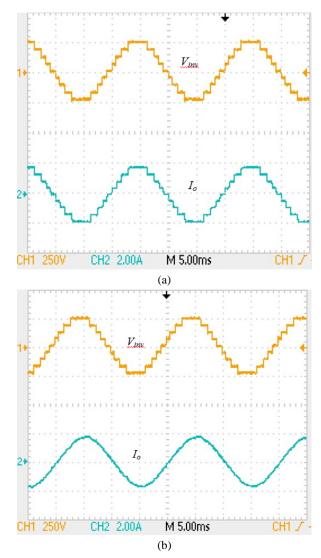

Fig. 10. The inverter output voltage and load current for 9-level TCHB inverter. (a)With a resistive load. (b) With an *RL* load.

RL load, L=81 mH is added in series to the resistor. A Tektronix TDS2002 digital oscilloscope was used to measure the voltage and current waveforms. Related data such as the total harmonic distortion (THD), power and power factor are measured using a FLUKE 43B power quality analyzer. The measured voltage THD was recorded for interharmonics up to the 50th harmonic order.

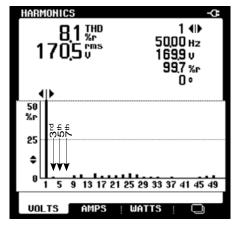

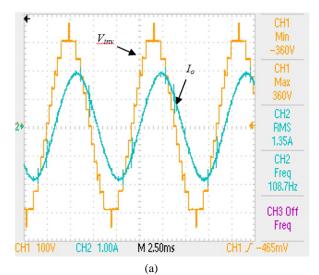

The first experimental setup was constructed for a 9-level TCHB inverter. Figs. 10(a) and 10(b) show the output waveforms of the proposed SHE scheme when tested with a highly resistive load and an RL load, respectively. Fig. 11 shows a 8.1% voltage THD where the 3rd, 5th and 7th harmonics were eliminated in the inverter output voltage  $V_{inv}$  of the 9-level TCHB inverter topology regardless of the load type.

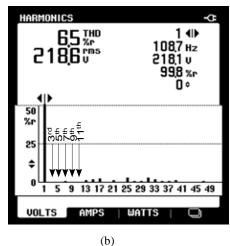

Another experiment was carried out with a 13-level TCHB inverter. To examine the inverter performance with a higher frequency of 110 Hz, the output waveform for the same *RL* load is illustrated in Fig. 12(a). An inverter output voltage THD

Fig. 11. The voltage THD of 9-level TCHB inverter.

Fig. 12. The 13-level TCHB inverter with an *RL* load. (a) The inverter output voltage and load current (b) The voltage THD.

of 6.5% is shown in Fig. 12(b). The 13-level TCHB topology produced a much lower voltage THD and enabled the inverter to eliminate more harmonic components than did the 9-level TCHB. Whatever the load or frequency, five harmonic orders were eliminated (the 3rd, 5th, 7th, 9th and 11th orders) in the

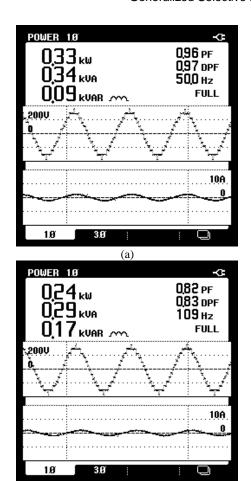

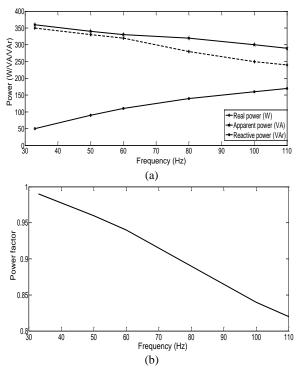

(b) Fig. 13. Measured 13-level inverter output power and power factor for different frequencies (a) 50 Hz (b) 110 Hz.

Fig. 14. The 13-level TCHB inverter (a) Power distribution against frequency (b) Power factor against frequency.

13-level TCHB inverter topology. The power distribution and power factor for different frequencies (50 Hz and 110 Hz) in the 13-level TCHB inverter with the same RL load parameters are shown in Figs. 13(a) and 13(b). The relationships between the power distribution and the power factor with the changes in frequency appear in Figs. 14(a) and 14(b), respectively. The results indicated that the real power and apparent power decrease with respect to the increase in frequency. However, the reactive power differed. It increased in proportion to the increase in frequency. Meanwhile, the load power factor decreased to become a more lagging pf when the frequency increased.

Both of the inverters produced a consistent stepped-waveform driven at an optimum point of the minimum THD corresponding to the analytical and simulation results. Specific low-order harmonics in the inverter output voltage  $V_{inv}$  were eliminated. In the case of a highly resistive load, the load current  $I_o$  had a similar stepped waveform as the inverter output voltage  $V_{inv}$ . In addition, with the RL load, the load current  $I_o$  was sinusoidal.

#### VI. CONCLUSION

This paper presented a generalized SHE modulation for a family of TCHB-based cascaded multilevel inverter. The SHE scheme was derived based on the Newton-Raphson method. Both simulation and experimental results verified the effectiveness of the SHE modulation for the TCHB inverter topology. It resulted in a dramatic decrease in the THD of the output voltage when there was an increase in the number of steps output. The proposed SHE scheme can be extended to other multilevel inverter topologies, via manipulating the application of the reference signal, the threshold voltage and the combinational logics. This method is precise in terms of harmonics elimination and also simple for practical implementation. Future work using the presented SHE can be carried out for a TCHB inverter with a single DC input source by employing several transformers at the inverter output.

# ACKNOWLEDGMENT

The authors would like to thank the Ministry of Higher Education of Malaysia, the University of Malaya, and the Universiti Teknikal Malaysia Melaka for providing the funding and sponsorship for this research.

### REFERENCES

- [1] A. M. Massoud, S. J. Finney, and B. W. Williams, "High-power, high-voltage IGBT applications: series connection of IGBTs or multilevel converters?" *Int. J. Electron.*, Vol. 90, No. 11-12, pp. 763-778, Nov./Dec. 2003

- [2] N. A. Rahim, J. Selvaraj, and C. Krismadinata, "Five-level inverter with dual reference modulation technique for

- grid-connected PV system," *Renewable Energy*. Vol. 35, No. 3, pp. 712-720, Mar. 2010.

- [3] J. Rodriguez, L. G. Franquelo, S. Kouro, J. I. Leon, R. C. Portillo, M. A. M. Prats, and M. A. Perez, "Multilevel converters: An enabling technology for high-power applications," in *Proc. IEEE*. Vol. 97, No. 11, pp. 1786-1817, 2009.

- [4] S. Kouro, M. Malinowski, K. Gopakumar, J. Pou, L. G. Franquelo, W. Bin, J. Rodriguez, M. A. Perez, and J. I. Leon, "Recent advances and industrial applications of multilevel converters," *IEEE Trans. Ind. Electron.* Vol. 57, No. 8, pp. 2553-2580, Aug. 2010.

- [5] A. Nabae, I. Takahashi, and H. Akagi, "A new neutral-point-clamped PWM inverter," *IEEE Trans. Ind. Appl.* Vol. IA-17, No. 5, pp. 518-523, Sep./Oct. 1981.

- [6] E. Ozdemir, S. Ozdemir, and L. M. Tolbert, "Fundamental-frequency-modulated six-level diodeclamped multilevel inverter for three-phase stand-alone photovoltaic system," *IEEE Trans. Ind. Electron.* Vol. 56, No. 11, pp. 4407-4415, Nov. 2009.

- [7] M. F. Escalante, J. C. Vannier, and A. Arzande, "Flying capacitor multilevel inverters and DTC motor drive applications," *IEEE Trans. Ind. Electron.* Vol. 49, No. 4, pp. 809-815, Aug. 2002.

- [8] M. Malinowski, K. Gopakumar, J. Rodriguez, and M. A. Perez, "A survey on cascaded multilevel inverters," *IEEE Trans. Ind. Electron.* Vol. 57, No. 7, pp. 2197-2206, Jul. 2010.

- [9] J. Pontt, J. Rodriguez, and R. Huerta, "Mitigation of noneliminated harmonics of SHEPWM three-level multipulse three-phase active front end converters with low switching frequency for meeting standard IEEE-519-92," *IEEE Trans. Power Electron.* Vol. 19, No. 6, pp. 1594-1600, Nov. 2004.

- [10] E. Babaei, S. Sheermohammadzadeh, and M. Sabahi, "Improvement of Multilevel Inverters Topology Using Series and Parallel Connections of DC Voltage Sources," *Arab. J. Sci. Eng.* Vol. 39, No. 2, pp. 1117-1127, Feb. 2014

- [11] D. Andler, R. Alvarez, S. Bernet, and J. Rodriguez, "Experimental investigation of the commutations of a 3L-ANPC phase leg using 4.5-kV-5.5-kA IGCTs," *IEEE Trans. Ind. Electron.* Vol. 60, No. 11, pp. 4820-4830, Nov. 2013.

- [12] L. Angquist, A. Antonopoulos, D. Siemaszko, K. Ilves, M. Vasiladiotis, and H. P. Nee, "Open-loop control of modular multilevel converters using estimation of stored energy," *IEEE Trans. Ind. Appl.* Vol. 47, No. 6, pp. 2516-2524, Nov./Dec. 2011.

- [13] S. J. Park, F. S. Kang, M. H. Lee, and C. U. Kim, "A new single-phase five-level PWM inverter employing a deadbeat control scheme," *IEEE Trans. Power Electron.* Vol. 18, No. 3, pp. 831-843, May 2003.

- [14] M. Schweizer and J. W. Kolar, "High efficiency drive system with 3-level T-type inverter," in: 14th European Conference Power Electronics and Applications, pp. 1-10, 2011.

- [15] M. Calais, L. J. Borle, and V. G. Agelidis, "Analysis of multicarrier PWM methods for a single-phase five level inverter," in: *Proc. PESC*, pp. 1351-1356, 2001.

- [16] M. Ghasem Hosseini Aghdam, S. Hamid Fathi, and Gevorg B. Gharehpetian, "Harmonic optimization techniques in multi-level voltage-source inverter with unequal DC sources," *Journal of Power Electronics*, Vol. 8, No. 2, pp. 171-180, Apr. 2008.

- [17] S. Sirisukprasert, L. Jih-Sheng, and L. Tian-Hua, "Optimum harmonic reduction with a wide range of modulation indexes for multilevel converters," *IEEE Trans. Ind. Electron.* Vol. 49, No. 4, pp. 875-881, Aug. 2002.

- [18] J. M. Vesapogu, S. Peddakotla, and S. R. A. Kuppa, "Harmonic analysis and FPGA implementation of SHE controlled three phase CHB 11-level inverter in MV drives using deterministic and stochastic optimization techniques," *SpringerPlus*, Vol. 2, No. 1, pp. 1-16, Aug. 2013.

- [19] M. S. A. Dahidah and V. G. Agelidis, "Selective harmonic elimination PWM control for cascaded multilevel voltage source converters: a generalized formula," *IEEE Trans. Power Electron.*, Vol. 23, No. 4, pp. 1620-1630, Jul. 2008.

- [20] B. Ozpineci, L. M. Tolbert, and J. N. Chiasson, "Harmonic optimization of multilevel converters using genetic algorithms," *IEEE Power Electron. Lett.*, Vol. 3, No. 3, pp. 92-95, Sep. 2005.

- [21] H. Taghizadeh and M. T. Hagh, "Harmonic elimination of cascade multilevel inverters with nonequal dc sources using particle swarm optimization," *IEEE Trans. Ind. Electron.*, Vol. 57, No. 11, pp. 3678-3684, Nov. 2010.

- [22] R. N. Ray, D. Chatterjee, and S. K. Goswami, "Harmonics elimination in a multilevel inverter using the particle swarm optimisation technique," *IET Power Electron.*, Vol. 2, No. 6, pp. 646-652, Nov. 2009.

- [23] B. Diong, H. Sepahvand, and K. A. Corzine, "Harmonic distortion optimization of cascaded H-bridge inverters considering device voltage drops and noninteger DC voltage ratios," *IEEE Trans. Ind. Electron.*, Vol. 60, No. 8, pp. 3106-3114, Aug. 2013.

- [24] N. A. Rahim, M. F. M. Elias, and H. W. Ping, "Transistor-clamped H-bridge based cascaded multilevel inverter with new method of capacitor voltage balancing," *IEEE Trans. Ind. Electron.*, Vol. 60, No. 8, pp. 2943-2956, Aug. 2013.

- [25] H. A. Hotait, A. M. Massoud, S. J. Finney, and B. W. Williams, "Capacitor voltage balancing using redundant states of space vector modulation for five-level diode clamped inverters," *IET Power Electron*, Vol. 3, No. 2, pp. 292-313, Mar. 2010.

Wahidah Abd. Halim was born in Kuala Lumpur, Malaysia, in 1977. She received her B.Eng. degree (with Honors) in Electrical Engineering from the Universiti Teknologi Malaysia, Johor, Malaysia, in 2001, and her M.Sc. degree in Electrical Power Engineering from the Universiti Putra Malaysia, Selangor, Malaysia, in 2005. She is presently working

towards her Ph.D. degree at the University of Malaya, Kuala Lumpur, Malaysia. She is a Lecturer in the Department of Power Electronics and Drives, Faculty of Electrical Engineering, Universiti Teknikal Malaysia Melaka (UTeM), Melaka, Malaysia. Her current research interests include power electronic converters and FPGA applications.

Nasrudin Abd. Rahim received his B.Sc. (Hons.) and M.Sc. degrees from the University of Strathclyde, Glasgow, UK, and his Ph.D. degree from Heriot–Watt University, Edinburgh, UK, in 1995. He is presently working as a Professor with the University of Malaya, Kuala Lumpur, Malaysia, where he is also the Director of the

UM Power Energy Dedicated Advanced Centre (UMPEDAC). His current research interests include power electronics, solar PV and wind technologies, real-time control systems, and electrical drives. Professor N. A. Rahim is a Fellow of the Institution of Engineering and Technology, UK, and the Academy of Sciences Malaysia. He is also a Senior Member of the IEEE, and a Chartered Engineer (UK).

Maaspaliza Azri was born in Malacca, Malaysia, in 1977. She received her B.Eng. degree (with Honors) in Electrical Engineering from the Universiti Teknologi Mara, Shah Alam, Malaysia, in 2001, her M.Sc. degree in Electrical Power Engineering from the Universiti Putra Malaysia, Serdang, Malaysia, in 2004, and her Ph.D. degree from

the University of Malaya, Kuala Lumpur, Malaysia, in 2014. She is presently working as a Lecturer in the Department of Power Electronics and Drives, Faculty of Electrical Engineering, Universiti Teknikal Malaysia Melaka (UTeM), Melaka, Malaysia.