JPE 15-4-5

http://dx.doi.org/10.6113/JPE.2015.15.4.910 ISSN(Print): 1598-2092 / ISSN(Online): 2093-4718

# A Dual Buck Three-Level PV Grid-Connected Inverter

Baojian Ji<sup>†</sup>, Feng Hong<sup>\*</sup>, Jianhua Wang<sup>\*\*</sup>, and Shengming Huang<sup>\*\*\*</sup>

†\*\*\*\*College of Automation and Electrical Engineering, Nanjing Tech University, Nanjing, China \*College of Electronic and Information Eng., Nanjing University of Aeronautics and Astronautics, Nanjing, China \*\*School of Electrical Engineering, Southeast University, Nanjing, China

#### **Abstract**

The use of a PV grid-connected inverter with non-isolated topology and without a transformer is good for improving conversion efficiency; however, this inverter has become increasingly complicated for eliminating leakage current. To simplify the complicated architecture of traditional three-level dual buck inverters, a new dual Buck three-level PV grid-connected inverter topology is proposed. In the proposed topology, the voltage on the grounding stray capacitor is clamped by large input capacitors and is equal to half of the bus voltage; thus, leakage current can be eliminated. Unlike in the traditional topology, the current in the proposed topology passes through few elements and does not flow through the body diodes of MOSFET switches, resulting in increased efficiency. Additionally, a multi-loop control method that includes voltage-balancing control is proposed and analyzed. Both simulation and experimental results are demonstrated to verify the proposed structure and control method.

Key words: Grid-connected inverter, Leakage current, Non-isolated topology, Photovoltaic

#### I. INTRODUCTION

Photovoltaic grid-connected inverter systems usually have a line frequency transformer, the reasons for which are as follows. 1) Voltage requirement can be easily matched. Most existing inverter topologies are of the buck type and cannot work under the condition where photovoltaic voltage is lower than the DC bus voltage; the transformer is required to boost voltage level. 2) The transformer is used to achieve electrical isolation, to improve reliability, and to meet safety requirements. However, the presence of a transformer has an adverse impact on system efficiency, which is a key aspect of grid-connected inverters. Line frequency photovoltaic transformers are normally bulky, cumbersome, energy-consuming; and high frequency transformer isolation schemes make systems more complicated than they already are. Hence, non-isolated structures have been increasingly

employed in photovoltaic grid-connected systems. However, without electrical isolation, this topology suffers from several new issues such as leakage current problems, which degrade system safety.

Grounding parasitic capacitors are relatively large due to the large area of photovoltaic arrays [1]. In the presence of electrical isolation, the parasitic capacitor is separated from the line side and has an insignificant impact. Once the transformer is removed, the parasitic capacitor is directly connected to the line side, and a closed loop is formed in the inverter circuit system, from the parasitic capacitor to the grid. The voltage on the parasitic capacitor can be regarded as a common-mode output voltage. Due to the high amplitude of common-mode voltage (at least half of input high voltage for a classic full bridge circuit), which varies with switching frequency, a large leakage current (also called common-mode current) is generated in the parasitic capacitor, endangering personal safety and becoming a crucial issue of non-isolated photovoltaic grid-connected inverters.

Nowadays, single phase low power (below 5 kW) photovoltaic grid-connected devices are mainly employed in residential applications. Thus, research on leakage problems is mainly focused on single phase power systems. As expressed in [2], if the unipolar-modulating method is employed, a

Manuscript received Nov. 7, 2014; accepted Mar. 24, 2015

Recommended for publication by Associate Editor Honnyong Cha.

<sup>&</sup>lt;sup>†</sup>Corresponding Author: jibaojian@njtech.edu.cn

Tel: +86-025-58139514, Nanjing Tech University

<sup>\*</sup>College of Electronic and Information Engineering, Nanjing University of Aeronautics and Astronautics, China

<sup>\*\*</sup>School of Electrical Engineering, Southeast University, China

<sup>\*\*\*\*</sup>College of Automation & Electrical Eng., Nanjing Tech Univ., China

full-bridge inverter system would have a common-mode voltage that varies with switching frequency; whereas, when the bipolar-modulating method is used, the common-mode voltage is constant and is equal to half of the bus voltage. In half-bridge inverters, the voltage of grounding parasitic capacitance is clamped at half of the bus voltage by large capacitors in a capacitive voltage divider at the input and is almost stable. Hence, in terms of removing leakage current, a half-bridge inverter, or a full-bridge inverter operating under a bipolar-modulating model, would suffice. For increasing efficiency, reducing voltage stress of devices, and minimizing filters, however, the differential mode output voltage waveform at the bridge middle point must usually follow a unipolar modulation. Thus, improvement of the bridge structure for a full-bridge inverter is necessary; and a few new topologies have been proposed. The new techniques used in [3]-[11] can be summarized as follows. By adding active devices or a circuit as auxiliary switches to modify the structure in a full-bridge inverter where the main switches still operate under bipolar modulating condition, the solar panel in an inverter system can be separated from the grid. This is achieved by the change of current path via the action of auxiliary switches. The output voltage at the bridge middle point is a three-level voltage. By introducing a capacitive voltage divider to the modulating circuit structure in a full-bridge inverter, the common-mode output voltage is only half of the bus voltage. A half-bridge inverter with three voltage levels was proposed in [2] and [12]. That architecture maintained a constant voltage on the grounding parasitic capacitor in a half-bridge inverter, while multilevel voltage technology was used to reduce voltage stress and to improve the output of the bridge middle point.

Leakage current can be effectively eliminated in all these proposed architectures. However, hardware cost in those architectures is somewhat increased. Although the H5 structure [3] has the minimum number of devices, the current flows through too many devices, especially through the body diode of switches at free-wheeling stage, resulting in severe reverse-recovery problems. Furthermore, independent control with a high-frequency switch mode is required for the additional device. These requirements lead to increased complexity of the system and have a negative effect on system efficiency and reliability. Other topologies have similar issues. Large capacitors in a capacitive voltage divider at the input were employed in the half-bridge topologies in [5], [8], [11], and [13]; however, the control method for voltage balancing was not stated therein. Therefore, further study on non-isolated photovoltaic grid-connected inverters without leakage current is required.

All the aforementioned studies in existing literature are based on bridge circuits. The dual Buck inverter (DBI) is a new inverter structure which has appeared in recent years [14]-[19]. Due to the combination of two bucks and a

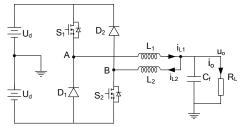

Fig. 1. Dual buck half-bridge inverter.

unidirectional direct converter (parallel connected at the output side and similar to the half-bridge inverter at the input side), as in unidirectional direct converters, the DBI has no direct conducting path on the bridge circuit and has no involvement in the operation of the body diode. Although the DBI is similar to the half-bridge inverter in that it requires high-input voltage and has a bipolar output voltage at the bridge middle point, the DBI remains to be a good candidate as a highly reliable and efficient inverter. Hence, researchers have proposed some improved multilevel dual Buck structures for further study. In the present paper, a new dual buck three-level grid-connected inverter is proposed and a comprehensive control strategy that includes maximum power point tracking (MPPT) and voltage balancing is presented. Both simulation and experimental results are given to verify this new inverter architecture and to compare it with the other aforementioned topologies.

# II. PROPOSED DUAL BUCK THREE-LEVEL PV GRID-CONNECTED INVERTER WITHOUT LEAKAGE CURRENT

#### A. Topology Analysis

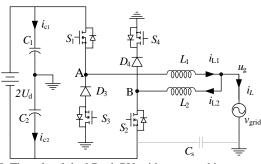

Fig. 1 shows the DBI circuit topology, which adopts half-load cycle-period operation modes (i.e. during the positive half load cycle period of the output current, switch  $S_1$ , freewheeling diode  $D_1$ , filter inductor  $L_1$ , and filter capacitor  $C_f$  form buck circuit 1; during the negative half load cycle period of the output current, switch  $S_2$ , freewheeling diode  $D_2$ , filter inductor  $L_2$ , and filter capacitor  $C_f$  operate as buck circuit 2, while buck circuit 1 is not operational). As shown in Fig. 1,  $u_o$  is output voltage;  $i_L$  is inductor current, which is  $i_{L1}$  for the current of inductor  $L_1$  in the positive half load cycle period and  $i_{L2}$  for the current of inductor  $L_2$  in the negative half load cycle period;  $u_A$  is the bridge-arm output voltage of buck circuit 1 at node A; and  $u_B$  is the bridge-arm output voltage of buck circuit 2 at node B.

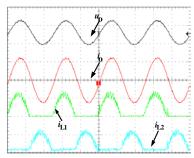

The operation waveforms of the DBI are shown in Fig. 2. The current cannot possibly flow through the bridge arm, and the body-diodes of switches  $S_1$  and  $S_2$  are not involved in the operation. However, the power switch of the DBI suffers from high-voltage stress. We assume that  $U_d$  is the input dc-bus voltage; thus, the voltage across power devices is  $2U_d$ . The output voltage waveform is bipolar and contains many harmonics.

Fig. 2. Operation waveforms of the DBI.

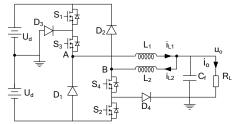

Fig. 3. Topology I of the dual buck three-level inverter.

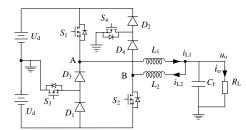

Fig. 4. Topology II of the dual buck three-level inverter

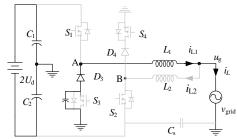

Fig. 5. Three-level dual Buck PV grid-connected inverter

Stated in [16] is the dual buck three-level inverter topology illustrated in Fig. 3. In this structure, switches  $S_1$  and  $S_2$  of the DBI are replaced by the combined switch circuits,  $S_1\&S_3\&D_3$  and  $S_4\&S_2\&D_4$ , respectively. Shown in Fig. 4 is another dual buck three-level topology presented in [17], wherein the diodes  $D_1$  and  $D_2$  of the DBI are replaced by the combined switch circuits,  $D_1\&D_3\&S_3$  and  $D_4\&D_2\&S_4$ , respectively. The half load-cycle operation mode of the DBI is retained in the proposed architecture in that, buck circuit 1 works with inductor current  $i_L$  in the positive half load cycle period and buck circuit 2 works under negative inductor current  $i_L$  in the half load cycle period. The operation modes of three-level topology I and three-level topology II are detailed in Tables I and II, respectively. Both topologies implement a three-level output with the same number of devices used.

For grid-connected applications, the dual buck three-level

$\label{eq:table_interpolation} TABLE\ I$  Operation Modes of Dual Buck Three-Level Inverter Topology I

| Operation M                         | Iodes     | Modes | $S_1$ | $S_3$ | $S_2$ | $S_4$ | $D_1$ | $D_3$ | $D_2$ | $D_4$ | $i_{ m L}$                    | Bridge<br>output         | Output<br>level |

|-------------------------------------|-----------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------------------------------|--------------------------|-----------------|

| $i_{\rm L} = i_{\rm Ll} > 0$ Buck 1 | $u_0 > 0$ | I     | on    | on    | off   | off   | off   | off   | off   | off   | $i_{\rm L1} \uparrow$         | $u_{\rm A} = +U_{\rm d}$ | +1              |

|                                     |           | II    | off   | on    | off   | off   | off   | on    | off   | off   | $i_{\mathrm{L}1}\!\downarrow$ | $u_{A} = +0$             | +0              |

|                                     | $u_0 < 0$ | III   | off   | on    | off   | off   | off   | on    | off   | off   | $i_{\mathrm{Ll}} \uparrow$    | $u_A = -0$               | -0              |

|                                     |           | IV    | off   | off   | off   | off   | on    | off   | off   | off   | $i_{\mathrm{L}1}\!\downarrow$ | $u_{\rm A} = -U_{\rm d}$ | -1              |

|                                     | 0         | V     | off   | off   | on    | on    | off   | off   | off   | off   | $i_{\mathrm{L2}} \uparrow$    | $u_{\rm B} = -U_{\rm d}$ | -1              |

| $i_{\rm L} = -i_{\rm L2} < 0$       | $u_0 < 0$ | VI    | off   | off   | off   | on    | off   | off   | off   | on    | $i_{L2} \downarrow$           | $u_{\rm B} = -0$         | -0              |

| Buck 2                              | $u_0 > 0$ | VII   | off   | off   | off   | on    | off   | off   | off   | on    | $i_{\mathrm{L2}} \uparrow$    | $u_{\rm B} = +0$         | +0              |

| и                                   |           | VIII  | off   | off   | off   | off   | off   | off   | on    | off   | $i_{12}$                      | $u_D = +U_A$             | +1              |

TABLE II OPERATION MODES OF DUAL BUCK THREE-LEVEL INVERTER TOPOLOGY II

| Operation Modes           |                 | Modes | $S_1$ | $S_3$ | $S_2$ | $S_4$ | $D_1$ | $D_3$ | $D_2$ | $D_4$ | $i_{ m L}$                    | Bridge<br>output         | Output<br>level |

|---------------------------|-----------------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------------------------------|--------------------------|-----------------|

|                           |                 | I     | on    | off   | i <sub>L1</sub> ↑             | $u_{\rm A} = +U_{\rm d}$ | +1              |

| $i_{\rm L}=i_{\rm L1}>0$  | $u_{\rm o} > 0$ | II    | off   | on    | off   | off   | off   | on    | off   | off   | $i_{\mathrm{L}1}\!\downarrow$ | $u_{A} = +0$             | +0              |

| Buck 1                    | . 0             | III   | off   | on    | off   | off   | off   | on    | off   | off   | i <sub>L1</sub> ↑             | $u_{A} = -0$             | -0              |

|                           | $u_{\rm o} < 0$ | IV    | off   | off   | off   | off   | on    | on    | off   | off   | $i_{\mathrm{L}1}\!\downarrow$ | $u_{\rm A} = -U_{\rm d}$ | -1              |

|                           | . 0             | V     | off   | off   | on    | off   | off   | off   | off   | off   | $i_{\mathrm{L2}} \uparrow$    | $u_{\rm B} = -U_{\rm d}$ | -1              |

| $i_{\rm L}=-i_{\rm L2}<0$ | $u_0 < 0$       | VI    | off   | off   | off   | on    | off   | off   | off   | on    | $i_{\mathrm{L2}}\!\downarrow$ | $u_{\rm B} = -0$         | -0              |

| Buck 2                    | $u_0 > 0$       | VII   | off   | off   | off   | on    | off   | off   | off   | on    | $i_{\mathrm{L2}} \uparrow$    | $u_{\rm B} = +0$         | +0              |

|                           |                 | VIII  | off   | off   | off   | off   | off   | off   | on    | on    | $i_{\mathrm{L2}}\!\downarrow$ | $u_{\rm B} = +U_{\rm d}$ | +1              |

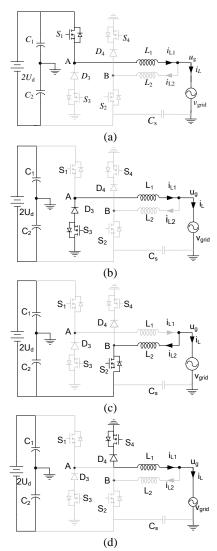

Fig. 6. Operation modes. (a) Mode I. (b) Mode II. (c) Mode III. (d) Mode IV.

inverter topology always has  $i_L = i_{L1} > 0$ ,  $u_o > 0$ , or  $i_L = -i_{L2} < 0$  during normal operation and does not require the operating modes, III, IV, VII, and VIII in Tables 1 and 2. Thus, diodes  $D_1$  and  $D_2$  can be removed, simplifying the dual buck three-level grid-connected inverter. With the removal of diodes  $D_1$  and  $D_2$ , Topology I (Fig. 3) can be a dual buck three-level structure applicable under grid-connected situations. Similarly, as Fig. 4 illustrates, another grid-connected dual Buck three-level structure based on topology II can be obtained; this structure, illustrated in Fig. 5, is the new topology proposed and presented in this paper. The line cycle has four main modes of operation.

**Model I:** As shown in Fig. 6(a);  $S_1$  is turned on and the output of bridge arm A is  $+U_d$ ; inductor current  $i_{L1}$  increases and no current flows in the  $S_3$ ,  $D_3$  branch;  $C_1$  is discharged,  $u_{C1}$  declines, and  $u_{C2}$  rises because  $u_{C2}=2U_d-u_{C1}$ .

**Model II**: As shown in Fig. 6(b);  $S_1$  is turned off, freewheeling current  $i_{L1}$  flows through  $S_3$ ,  $D_3$  and the output of

Fig. 7. Zero-crossing distortion.

bridge arm A is clamped at 0;  $u_{C1}$  and  $u_{C2}$  do not change.

**Model III**: As shown in Fig. 6(c); S2 is turned on, the output of bridge arm B is -Ud, and iL2 increases; no current flows in branch S4, D4; C2 is discharged, uC2 declines, and uC1 rises because uC1=2Ud-uC2.

**Model IV**: As shown in Fig. 6(d); S1 is turned off, iL2 flows from S4, D4; the output of bridge arm B is 0; uC1 and uC2 do not change.

## B. Analysis of Zero-Crossing Distortion

As shown in the preceding analysis, the switches work at half cycle mode. In the actual circuits, the driving signals of  $S_1$  and  $S_2$  are not completely ideal, and dead time can be observed. For example, in the positive half cycle, when both  $S_1$  and  $S_3$  are turned-off, switches  $S_2$  and  $S_4$  are not turned-on, and the inductor current does not decrease to zero, the inductor current will flow through the parasitic capacitors of the devices (Fig. 7), causing LC resonance and leading to zero-crossing distortion. However, only two zero-crossing points can be observed and the dead time can be shortened to the largest amount possible. In addition, the zero-crossing current is minimal; thus, the zero-crossing distortion is not very serious, the influence of which can be ignored.

# C. Analysis of Input Capacitors

The variety rate of  $2U_d$  is significantly less than the variety rate of  $u_{C1}$  and  $u_{C2}$ , which are related to the switching frequency; thus, the equation,  $i_{C1}+i_{C2}\,C_1/C_2=0$ , can be approximated. In accordance with Kirchhoff's current law,  $i_{C1}+i_L=i_{C2}$  can be obtained; thus, currents of capacitors  $C_1$  and  $C_2$  are

$$i_{\rm CI} = \frac{-C_{\rm I}}{C_{\rm I} + C_{\rm 2}} i_{\rm L} \tag{1}$$

$$i_{\rm C2} = \frac{C_2}{C_1 + C_2} i_{\rm L} \tag{2}$$

where  $i_L = \sqrt{2}I_L \sin(\omega t + \theta)$ , and the voltage on C<sub>2</sub> can be obtained as:

$$u_{\rm C2} = \frac{1}{C_2} \int_0^t i_{\rm C2} d\tau + U_{\rm C20} = \frac{\sqrt{2}I_L}{\omega(C_1 + C_2)} [\cos\theta - \cos(\omega t + \theta)] + U_{\rm C20}$$

(3)

# D. Analysis of Leakage Current

Given the photovoltaic array output voltage, 2U<sub>d</sub>, the

Fig. 8. Control block diagram.

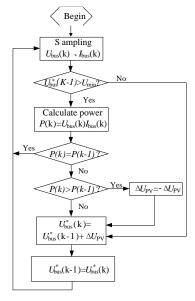

Fig. 9. Control algorithm of MPPT.

grounding parasitic capacitor  $C_s$  of the photovoltaic array exists between the negative bus and the ground. The current of grounding parasitic capacitance is also the leakage current:

$$i_{\rm CS} = C_{\rm S} \frac{\Delta u_{\rm CS}}{\Delta t} \tag{4}$$

where  $u_{CS}$  is the voltage across  $C_S$ . As shown in Fig. 5, the voltage across  $C_S$  is also the voltage across output capacitor  $C_2$ .

$$u_{\text{CS}} = u_{\text{C2}} = \frac{1}{C_2} \int_0^t i_{\text{C2}} d\tau + U_{\text{C20}}$$

$$= \frac{\sqrt{2}I_L}{\omega(C_1 + C_2)} [\cos \theta - \cos(\omega t + \theta)] + U_{\text{C20}}$$

(5)

Using equations (4) and (5), the leakage current can be obtained as:

$$i_{\rm CS} = \frac{\sqrt{2}I_L C_{\rm S}}{(C_1 + C_2)} \sin(\omega t + \theta)$$

(6)

As demonstrated, the proposed topology is similar to that of the half-bridge inverter, and the voltage of grounding parasitic capacitance is clamped by large input capacitors. As shown in equation (6), the leakage current is related to the input capacitors, the grounding parasitic capacitor, and inductor current; the capacitance of the grounding parasitic capacitor can get as high as approximately 200 nF/kW in inferior environments such as rainy and damp environments [18] capacitance that is much less than that of the input capacitor. Therefore, the leakage current is insignificant and can be ignored.

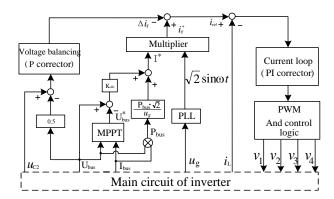

## III. CONTROL STRATEGY

Fig. 8 shows the inverter control block diagram, designed to simultaneously implement grid connection, MPPT, and voltage balancing functions, which is composed of three parts—the voltage balancing loop, current loop, and current reference circuit.

From equation (1), the average voltage on capacitors  $C_1$  and  $C_2$  can be obtained from integration and can be expressed as

$$\overline{u}_{C1} = U_{C10} - \frac{\sqrt{2}I_{L}}{\omega(C_{1} + C_{2})}\cos\theta$$

(7)

$$\overline{u}_{C2} = U_{C20} + \frac{\sqrt{2}I_{L}}{\omega(C_{1} + C_{2})}\cos\theta \tag{8}$$

where  $U_{C10}$  and  $U_{C20}$  are the initial voltages of capacitor  $C_1$  and  $C_2$ , respectively. Assuming  $U_{C10} = U_{C20} = U_d$ , we then obtain voltage deviation as

$$\Delta \overline{u} = \overline{u}_{C2} - \overline{u}_{C1} = \frac{2\sqrt{2}I_L}{\omega(C_1 + C_2)}\cos\theta \tag{9}$$

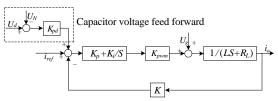

The voltage balancing loop is the outer loop. In accordance with the mechanism for unbalancing input voltage generation [19], [20], the capacitor voltage feed forward scheme is introduced (Fig. 8). As shown in equation (9), the unbalanced voltage is related with the grid current and, to a certain extent, has a proportional relationship with the sum of the two capacitances. As indicated by the input capacitor voltage deviation, the current loop not only regulates the inductor current but also solves the voltage unbalancing problem (Fig. 8).

The number of solar panels in the string is based on ensuring that dc voltage is higher than the ac voltage peak at all times; thus, the used solar-panels consists of sixteen PV panels [21]. The perturbation and observation algorithm is adopted to implement MPPT (Fig. 9). Evidently, the input bus voltage changes within a wide range and will not be less than  $U_{min}$  (which is set as 350 V). Additionally, the power feed-forward scheme is adopted to generate the reference current. Using the input power feed-forward scheme, we improve the dynamic of the PV system. The dc voltage controller ensures a quick response of the PV system under a sudden change in the input power.

# IV. KEY PARAMETERS DESIGN

# A. Filter Inductor Design

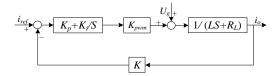

Fig. 10. Control block diagram of the proposed inverter.

From equation (9),  $C_1$  and  $C_2$  can be determined if the allowable voltage difference on capacitors is known. Moreover, this allowable value is also required for defining inductance in the output filter. As indicated in the analysis, the two inductors of the three-level dual buck photovoltaic grid-connected inverter work symmetrically, one in the positive half load cycle period and the other in the negative half load cycle period. The operation in the positive half load cycle period is investigated in detail. In a high-frequency switching cycle, grid voltage is nearly constant; and inductor current can be expressed as:

$$U_{\rm d} - u_{\rm g}(K) = L_{\rm l} \frac{\Delta i_{\rm Ll}}{DT_{\rm c}} \tag{10}$$

where D is the high-frequency duty cycle and  $u_g(K)$  is grid voltage at the switching period. Given that

$$\frac{u_{\rm g}(K)}{U_{\rm d}} = D \tag{11}$$

Thus,

$$\Delta i_{L1} = \frac{(U_{d} - u_{g}(K))u_{g}(K)T_{s}}{L_{l}U_{d}}$$

(12)

and the possible maximum current ripple value can be expressed as

$$\Delta i_{\rm L1\,max} = \frac{U_{\rm d}T_{\rm s}}{4L_{\rm l}} \tag{13}$$

By considering the magnetic component's volume size, weight, losses, and other factors, current ripple can be set at 10%-20% of the rated output current and the inductance value of  $L_1$  can be calculated. Similarly, choke inductor  $L_2$ , working at negative half load cycle period, can also be determined. In addition, the LCL filter can be applied in the proposed inverter, which will minimize its inductors.

# B. Input Capacitor Design

As shown in equation (5), the fluctuation of  $u_{C1}$  and  $u_{C2}$  are equal and can be obtained as:

$$\Delta u_{\rm C1} = \Delta u_{\rm C2} = \frac{2\sqrt{2}I_L}{\omega(C_1 + C_2)}$$

(14)

Input capacitors are usually connected with equal capacitance, and the voltage ripple is set at less than 5% of the input voltage; thus, the values of  $C_1$  and  $C_2$  can be calculated.

# C. Control Parameter Design

In the common grid-connected inverter, the single current loop control is adopted to track the reference current and to maintain the stability of the system; the block diagram of the current loop control for the proposed inverter is shown in Fig.

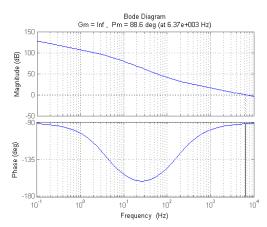

Fig. 11. Bode diagram of the proposed inverter.

Fig. 12. The improved control block diagram of the proposed inverter.

10. The feedback coefficient of the output current is K, and  $K_{nwm}$  is the equivalent proportionality constant.

To make the transient system work properly with minimal overshoot and ringing, we designed the parameters of the current loop PI controller as follows:  $K_p=1$ ,  $K_i=10000$ , and the bode diagram of the proposed inverter is as shown in Fig. 11. As indicated in Fig. 10, the system is stable.

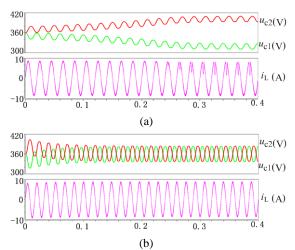

However, in accordance with the analysis (Part III), the capacitance voltage feed forward scheme is adopted to solve the voltage unbalancing problem (Fig. 12). Fig. 13(a) indicates a voltage unbalancing problem and shows that, without the capacitor voltage feed forward control, the inductor current will be finally malformed. Thus, the capacitor voltage feed forward scheme is added and  $K_{pd}$  is set as 0.1, contributing to the normal operation of the system, as indicated in the simulation results shown in Fig. 13(b).

# V. SIMULATION AND EXPERIMENTAL VERIFICATION

To verify the proposed topology and control scheme, we herein present the simulation and experimental results. The parameters of the prototype used in the simulations are as follows: input capacitors  $C_1 = C_2 = 1100 \ \mu F$ ; output filtering inductor  $L_1 = L_2 = 750 \ \mu H$ ; output voltage  $u_o = 220 \ VAC/50 \ Hz$ ; DC input voltage  $U_d = 720 \ VDC$ , and thus  $u_{C1} = u_{C2} = 360 \ VDC$  at steady-state; output power  $P_o = 1 \ kW$ ; switching frequency  $f_s = 100 \ kHz$ . MOSFET switches used are IPW65R037C6 models, and diodes used are DSEI30-06A models.

Fig. 13. Test results. (a) Without capacitor voltage feed forward control. (b) With capacitor voltage feed forward control.

Fig. 14. Simulation waveforms.

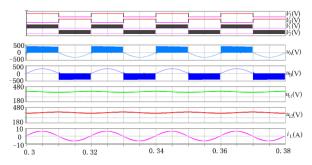

Simulation results are illustrated in Fig. 14, where  $u_{\rm g}$  is the grid voltage; inductor current  $i_{\rm L}=i_{\rm L1}+i_{\rm L2};\,u_{\rm C1}$  and  $u_{\rm C2}$  are the input voltages on capacitors  $C_1$  and  $C_2$ , respectively;  $u_{\rm A}$  and  $u_{\rm B}$  are the voltages at the bridge arm middle points A and B, respectively; and  $v_1-v_4$  are the driving signals for switches  $S_1-S_4$ , respectively.

When  $i_L=i_{L1}>0$ , Buck circuit 1 operates in the positive half load cycle period, and  $u_A$  is the modulated SPWM voltage waveform,  $S_2$  and  $S_4$  are in the off state, Buck circuit 2 is separated from the grid,  $i_{L2}=0$ , and  $u_B=u_g$ . When  $i_L=i_{L2}<0$ , Buck circuit 2 operates in the negative half load cycle period,  $u_B$  is the modulated SPWM modulated voltage waveform,  $S_1$  and  $S_3$  are in off state, Buck circuit 1 is separated from the grid,  $i_{L1}=0$ , and  $u_A=u_g$ . Therefore, the inverter completes the DC/AC conversion and the input voltage balancing control in the closed-loop. The voltages across the input capacitors  $C_1$  and  $C_2$  are stable.

Under the same output conditions, the proposed inverter is compared with other inverters such as 3L-NPC and DBHBI [22] (Table III).

As shown in Table III, the proposed inverter has more inductors than the 3L-NPC; however, the proposed inverter has no shoot-through problems. Shoot-through problems have significant negative impact on reliability, wherein dead time needs to be set, which will cause distortion of the output. In

TABLE III

COMPARISON OF THE PROPOSED INVERTER WITH OTHER INVERTERS

| Comminatori                  | COMPARISON OF THE FROI OSED INVERTER WITH OTHER INVERTER. |        |        |                      |  |  |  |  |  |

|------------------------------|-----------------------------------------------------------|--------|--------|----------------------|--|--|--|--|--|

| Items                        |                                                           | 3L-NPC | DBHBI  | Proposed<br>Inverter |  |  |  |  |  |

|                              | Number                                                    | 2      | 2      | 2                    |  |  |  |  |  |

| High-frequency               | $U_{\mathrm{DS}}(\mathrm{max})$                           | 360 V  | 720 V  | 360 V                |  |  |  |  |  |

| Switches                     | $I_{\rm D}({ m max})$                                     | 6.42 A | 6.42 A | 6.42 A               |  |  |  |  |  |

|                              | Number                                                    | 2      | 0      | 2                    |  |  |  |  |  |

| Low-frequency                | $U_{\mathrm{DS}}(\mathrm{max})$                           | 360 V  | N/A    | 360 V                |  |  |  |  |  |

| Switches                     | $I_{\mathrm{D}}(\mathrm{max})$                            | A      | N/A    | 6.42 A               |  |  |  |  |  |

|                              | Number                                                    | 2      | 2      | 2                    |  |  |  |  |  |

| Independent freewheeling     | U <sub>KA</sub> (max                                      | 360 V  | 720 V  | 360 V                |  |  |  |  |  |

| diodes                       | $I_{\rm A}({ m max})$                                     | 6.42 A | 6.42 A | 6.42 A               |  |  |  |  |  |

| Filter inductors             | Number                                                    | 1      | 2      | 2                    |  |  |  |  |  |

| Filter inductors             | L(µH)                                                     | 750    | 750    | 750                  |  |  |  |  |  |

| T .                          | Number                                                    | 2      | 2      | 2                    |  |  |  |  |  |

| Input capacitors             | C(µF)                                                     | 1100   | 1100   | 1100                 |  |  |  |  |  |

| Shoot-through problem?       |                                                           | Yes    | No     | No                   |  |  |  |  |  |

| Current through body diodes? |                                                           | Yes    | No     | No                   |  |  |  |  |  |

TABLE IV

Comparison with Other Non-Isolated Grid-Connected

Inverters

| Iter                      | ns      | Н5    | HERIC | Н6    | Proposed inverter |

|---------------------------|---------|-------|-------|-------|-------------------|

| Number of Hi<br>Swite     |         | 3     | 3 4 4 |       | 2                 |

| Number of Lo<br>Swite     | 1 .     | 2     | 2     | 2     | 2                 |

| Number of I<br>Freewheeli | 0       | 2     | 2     | 2     |                   |

| Filter                    | number  | 2     | 2     | 2     | 2                 |

| inductors                 | L(mH)   | 3     | 3     | 3     | 0.75              |

| Switching free            | 20      | 20    | 20    | 100   |                   |

| Rate pov                  | ver (W) | 1000  | 1000  | 1000  | 1000              |

| Effici                    | 96.7%   | 96.8% | 96.9% | 96.7% |                   |

addition, during dead time, the inductor current flows through the body diode, causing increased loss. The aforementioned analysis indicates that the proposed inverter is in a good position in terms of reliability and efficiency. Moreover, although the proposed inverter has more switches than the DBHBI, the two inverters have an equal number of high-frequency switches; and the voltage stress of the switches and diodes in the proposed inverter is half of that in the DBHBI.

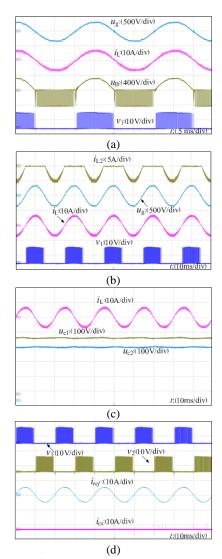

Experimental results are shown in Fig. 15. Fig. 15(a) shows the voltage waveforms  $u_B$  at the bridge arm middle point, grid voltage  $u_g$ , inductor current  $i_L$ , and the driving signal  $v_1$  of  $S_1$ . Fig. 15(b) shows inductor current  $i_{L2}$ . Fig. 15(c) shows inductor current  $i_L$ , voltage  $u_{C1}$  of  $C_1$ , and voltage  $u_{C2}$  of  $C_2$ . Fig. 15(e) demonstrates reference current  $i_{ref}$ , driving signal  $v_1$  of  $S_1$ ,

Fig. 15. Test results.

driving signal  $v_2$  of  $S_2$ , and leakage current  $i_{CS}$ . The aforementioned values match the theoretical analysis and the simulation results well. As indicated in Fig. 15(c), the average voltages of  $C_1$  and  $C_2$  are the same, proving that the capacitor voltage feed forward scheme works. In addition, the voltage ripple is a sinusoidal wave and is consistent with that theorized in the analysis. Fig. 15(d) demonstrates that the voltage of input capacitance is stable, which is due to the effective voltage balancing scheme, and does not vary in the high switching frequency. Furthermore, no leakage current is generated.

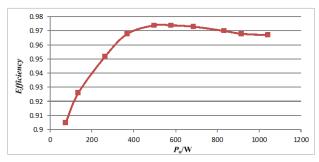

The tested efficiency curve is shown in Fig. 16. As clearly shown, high conversion efficiency is achieved. For non-isolated grid-connected inverters, leakage currents cannot be ignored and reduce the reliability and security of the inverters. Many modified topologies based on the bridge-type inverter are proposed to eliminate leakage current by adding devices, which will increase losses. The efficiency results, as compared with other non-isolated grid-connected inverters (H5, HERIC, and H6 [23]), are summarized in

Fig. 16. Efficiency curve.

Table IV. The proposed inverter has only two high-frequency switches, meaning that it has low switching loss. The inductor of the proposed inverter is much less than that of the H5, HERIC, and H6, because of the high switching frequency; however, the efficiencies of all the inverters are almost equal. We can reasonably estimate that when the switching frequency is reduced and the low on-resistance switches are used, the switching loss and conduction loss will be decreased and efficiency will be further increased.

#### VI. CONCLUSION

A novel three-level Dual Buck photovoltaic grid-connected inverter is proposed. The output voltage at the bridge arm of the inverter has a unipolar modulated waveform; the voltage on the grounding parasitic capacitor is clamped by large input voltage balancing capacitors and varies slightly in line frequency rather than in high switching frequency. Thus, leakage current is effectively eliminated. Unlike in traditional topologies, current in the proposed typology passes through fewer elements and does not go through the body diodes of MOSFET switches, resulting in higher efficiency. Furthermore, a multi-loop control method that includes voltage-balancing control is proposed and analyzed. Both demonstrated simulation and experimental results are demonstrated to verify the proposed structure and the control method.

#### ACKNOWLEDGMENT

This work was supported in part by the Natural Science Foundation of Jiangsu Province under Grant BK20140944.

# REFERENCES

- [1] P. Pairodamonchai, S. Suwankawin, and S. Sangwongwanich, "Design and implementation of a hybrid output EMI filter for high-frequency common-mode voltage compensation in PWM inverters," *IEEE Trans. Ind. Appl.*, Vol. 45, No. 3, pp. 1647-1659, Sep./Oct. 2009.

- [2] X. Guo, M. C. Cavalcanti, A. M. Farias, and J. M. Guerrero, "Single-carrier modulation for neutral-point-clamped inverters in three-phase transformerless photovoltaic systems," *IEEE Trans. Power Electron.*, Vol. 28, No. 6, pp. 2635-2637, Jun. 2013.

- [3] M. Victor, F. Greizer, S. Bremicker, and U. Hubler, "Method of converting a direct current voltage from a source of direct current voltage, more specifically from a photovoltaic source of direct current voltage, into a alternating current voltage," U.S. Patent: 7 411 802 B2, 2008

- [4] R. Gonzalez, J. López, P. Sanchis, and L. Marroyo, "Transformerless inverter for single-phase photovoltaic systems," *IEEE Trans. Power Electron.*, Vol. 22, No. 2, pp. 693-697, Mar. 2007.

- [5] R. Gonzalez, E. Gubia, J. Lopez, and L. Marroyo, "Transformerless single-phase multilevel-based photovoltaic inverter," *IEEE Trans. Ind. Electron.*, Vol. 55, No. 7, pp. 2694-2702, Jun. 2008.

- [6] Y. Bo, W. Li, Y. Deng, X.He, S. Lambert, and V. Pickert, "A novel single-phase transformerless photovoltaic inverter connected to grid," in *Proc. IEEE Power Electronics Machines and Drives Conference*, pp. 1-6, 2010.

- [7] W. Yu, J. S. Lai, H. Qian, C. Hutchens, J. Zhang, G. Lisi, A. Djabbari, G. Smith, and T. Hegarty, "High-efficiency inverter with H6-type configuration for photovoltaic non-isolated AC module applications," in *Proc. IEEE Applied Power Electronics Conference*, pp. 1971-1977, 2010.

- [8] T. Kerekes, R.. Teodorescu, and P. Rodríguez, G. Vazquez, and E. Aldabas, "A new hhigh-efficiency single-phase transformerless PV inverter topology," *IEEE Trans. Ind. Electron.*, Vol. 58, No. 1, pp. 184-191, Jan. 2011.

- [9] B. Ji, J. Wang, and J. Zhao, "High efficiency single phase transformerless PV H6 inverter with hybrid modulation method," *IEEE Trans. Ind. Electron.*, Vol. 60, No. 5, pp. 2104-2115, May 2013.

- [10] B. Gu, J. Dominic, J.-S. Lai, C.-L. Chen, T. LaBella, and B. Chen, "High reliability and efficiency single-phase transformerless inverter for grid-connected photovoltaic systems," *IEEE Trans. Power Electron.*, Vol. 28, No. 5, pp. 2235-2245, May 2013.

- [11] L. Zhang and K. Sun, L. Feng, H. Wu, and Y. Xing, "A family of neutral point clamped full-bridge topologies for transformerless photovoltaic grid-tied inverters," *IEEE Trans. Power Electron.*, Vol. 28, No. 2, pp. 730-738, Feb. 2013.

- [12] R. Gonzalez, E. Gubia, J. Lopez, and L. Marroyo, "Transformerless single-phase multilevel-based photovoltaic inverter," *IEEE Trans. Ind. Electron.*, Vol. 55, No. 7, pp. 2694-2702, Jul. 2008.

- [13] Y. Wang and F. Wang, "Novel three-phase three-level-stacked neutral point clamped grid-tied solar inverter with a split phase controller," *IEEE Trans. Power Electron.*, Vol. 28, No. 6, pp. 2856-2865, Jun. 2013.

- [14] S. K. Gudey and R. Gupta, "Sliding mode control of dual-buck full-bridge inverter," in *Proc. 2012 IEEE 5th India International Conference on Power Electronics (IICPE)*, pp. 1-6, 2012.

- [15] P. Sun, C. Liu, J. S. Lai, C. L. Chen, and N. Kees, "Three-phase dual-buck inverter with unified pulse width modulation," *IEEE Trans. Power Electron.*, Vol. 27, No. 3, pp. 1159-1167, Jul. 2012.

- [16] F. Hong, P. Ying, and C. Wang, "Decoupling control of input voltage balance for diode-clamped dual buck three-level inverter," in *Proc. 28th Annual IEEE Applied Power Electronics Conference and Exposition*, pp.

- 482-488, 2013.

- [17] L. Zhang, J. Dominic, B. Gu, J. S. Lai, and C. L. Chen, "A dual-buck based equalizer operating in burst-mode for split phase inverter," in *Proc. 1st International. IEEE Future Energy Electronics Conference (IFEEC)*, pp. 524-529, 2013.

- [18] R. González, J. López, P. Sanchis, and L. Marroyo, "Transformerless inverter for single-phase photovoltaic systems," *IEEE Trans. Power Electron.*, Vol. 22, No. 2, pp. 693-697, Mar. 2007.

- [19] B. Chen, B. Gu, J. S. Lai, W. Yu, C. Y. Lin, and C. Zheng, "Current distortion correction in dual buck photovoltaic inverter with a novel PWM modulation and control method," in *Proc. 28th IEEE Applied Power Electronics* Conference and Exposition, pp. 727-731, 2013.

- [20] M. Liu, F. Hong, and C. Wang, "A novel flying-capacitor dual buck three-level inverter," in *Proc. 28th Annual IEEE Applied Power Electronics Conference and Exposition*, pp. 502-506, 2013.

- [21] M. Ciobotaru, R. Teodorescu, and F. Blaabjerg, "Control of single-stage single-phase PV inverter," in *Proc.* European Conference on Power Electronics and Applications, pp. 1-10, 2005.

- [22] J. Liu and Y. Yan, "Reliable hysteresis current controlled dual buck half bridge inverter," *Transactions on Nanjing University of Aeronautics & Astronautics*, Vol. 20, No. 1, pp. 67-72, 2003.

- [23] L. Zhang, K. Sun, Y. Xing, and M. Xing, "H6 transformerless full-bridge PV grid-tied inverters," *IEEE Trans. Power Electron.*, Vol. 29, No. 3, pp. 1229-1238, Mar. 2014.

Baojian Ji received his B.S. degree in automation engineering from Nanjing Normal University, Nanjing, China, in 2002, and his M.S. degree in electrical engineering from Nanjing University of Aeronautics and Astronautics, Nanjing, in 2007. He received his Ph.D. degree from Southeast University, Nanjing, in 2012. In 2007, he was a lecturer

at Nanjing Tech University, where also, he is currently head of the Department of Electrical Engineering. He has more than 20 technical papers published. His research interests include digital control techniques and the development of grid-tied inverters for renewable energy applications.

**Feng Hong** was born in Anhui, China, in 1979. He received his B.S., M.S., and Ph.D. degrees in power electronics and power transmission from the Nanjing University of Aeronautics and Astronautics (NUAA), Nanjing, China, in 2001, 2004, and 2008, respectively. In 2008, he joined the College of Electronic and Information Engineering,

NUAA, where he is currently an associate professor. His current research interests include renewable energy generation systems, high-frequency power conversion, and multi-level power conversion. He has over 30 journal articles published and accepted and 18 China patents awarded.

**Jianhua Wang** received his B.S. and Ph.D. degrees in electrical engineering from Nanjing University of Aeronautics and Astronautics, Nanjing, China, in 2004 and 2010, respectively. In 2010, he joined the faculty of the School of Electrical Engineering in Southeast University, Nanjing, where he is currently a lecturer. He has more

than 20 technical papers published. He is the holder of two China patents. His main research interests are power electronics system integration, general power electronic circuit topologies, modeling and control, high performance power conversion for shipboard, aerospace, and renewable energy applications.

Shengming Huang received his B.S. degree from Hefei University of Technology, Hefei, China, in 1985, and his Ph.D. degree from University of Cambridge, Cambridge, England, in 2001. In 2012, he was a distinguished professor of Jiangsu province, at Nanjing Tech University. He has more than 30 technical papers published and is the

holder of 11 China and U.S.A. patents. His main research interests are power electronics system integration and renewable energy applications.