http://dx.doi.org/10.6113/TKPE.2015.20.4.363

# HVDC 시스템의 SCR 사이리스터 밸브 시험을 위한 Full-Bridge Converter 방식의 개선된 전류원 회로

정재헌 $^{1}$ , 조한제 $^{2}$ , 구법진 $^{2}$ , 노의철 $^{\dagger}$ , 정용호 $^{2}$ , 백승택 $^{2}$

Improved Current Source using Full-Bridge Converter Type for Thyristor Valve Test of HVDC System

Jae-Hun Jung<sup>1</sup>, Han-Je Cho<sup>2</sup>, Beob-Jin Goo<sup>2</sup>, Eui-Cheol Nho<sup>†</sup>, Yong-Ho Chung<sup>2</sup>, and Seung-Taek Baek<sup>2</sup>

### **Abstract**

This paper deals with an improved current source using full-bridge converter type for thyristor valve test of HVDC system. The conventional high-current and low-voltage source of synthetic test circuit requires additional auxiliary power supply to provide the reverse voltage for the auxiliary thyristor valve during turn-off process. The proposed circuit diagram to provide the reverse voltage is extremely simple because no additional component is required. The reverse voltage can be obtained from the input DC voltage of the high-current and low-voltage power supply. The operation principle and design method of the proposed system are described. Simulation and experimental results in scaled down STC of 200 V, 30 A demonstrate the validity of the proposed scheme.

Key words: Full bridge converter, HVDC (High Voltage Direct Current), STC (Synthetic Test Circuit)

## 1. 서 론

최근 장거리 전력전송 시스템에 있어 기존의 교류 송전과 비교하여 효율이 높고 무효 전력 성분이 없다는 장점을 가진 HVDC (High Voltage Direct Current)에 대한 연구가 활발히 수행되고 있다. 일반적으로 HVDC 시스템은 SCR 사이리스터로 구성된 전류형 타입과 IGBT로 구성된 전압형 타입으로 구분할 수 있는데 전류형 HVDC 시스템은 1980년대 초반부터 상용으로 설치되어왔으며 그 용량이 계속 증가하는 추세에 있고 전압형 HVDC 시스템은 현재 실증 단계에 있다. HVDC 시스템을 구성하는 전력 변환 장치는 수십~수백 [kV]의 고전압 환경에서 운전 된다. 하지만 현재까지 상용화된 전

력 반도체 소자의 전압 정격은 약 수[kV]로서 HVDC 시스템의 높은 전압 환경을 견디기 위하여 수~수십 개의 전력 반도체 소자를 직렬로 연결한 밸브를 이용하 여 시스템을 구성한다. HVDC 시스템을 구성하는 밸브 는 HVDC 시스템 제작 이전에 실제 시스템의 운전과 유사한 조건으로 성능 시험을 해야 한다. 실제 시스템을 제작하고 정격 부하 조건에서 밸브를 시험하는 방법이 바람직하지만 시험설비의 비용과 크기가 매우 커지고 큰 전력이 소모되며 안정상의 문제가 있기 때문에 일반 적으로 고전압-저전류원 회로와 대전류-저전압원 회로 를 이용하여 밸브에 시험 전압과 시험 전류를 인가하는 방법이 사용되고 있다. ABB, 합성시험 Alstorm과 같은 선진사들은 전류형 HVDC의 밸브 시험 을 위한 독자적인 합성시험회로를 개발하여 자체적으로 밸브 시험을 수행하고 있으며 6-pulse 사이리스터 컨버 터를 기반으로 한 대전류-저전압원 회로를 사용하고 있 다<sup>[1-3]</sup>. 또한 2-phase 쵸퍼 형태의 새로운 전류원 회로를 이용한 합성시험회로<sup>[4,5]</sup>가 제안되었으며 현재 300[A] 급의 실증 테스트를 완료한 상태이다.

본 논문은 SCR 사이리스터 밸브의 합성시험을 위한 새로운 전류원 회로에 대한 것이다. 제안하는 전류원회

Paper number: TKPE-2015-20-4-10

Print ISSN: 1229-2214 Online ISSN: 2288-6281

<sup>†</sup> Corresponding author: nhoec@pknu.ac.kr, Dept. of Electrical Eng., Pukyong National University

Tel: +82-51-629-6317 Fax: +82-51-629-6305

Dept. of Electrical Eng., Pukyong National University

<sup>&</sup>lt;sup>2</sup> HVDC Research Group, LS Industrial Systems Manuscript received May 21, 2015; revised Jun. 16, 2015; accepted July 16, 2015

로는 full-bridge 회로를 이용하였으며 입력 전원의 필터 커패시터 전압을 보조 밸브에 역으로 인가하여 보조 밸브의 턴-오프 타임을 확보하였다. 이를 통하여 기존에 제안된 전류원 회로<sup>[45]</sup>의 보조 전원 회로를 제거 하였고 인덕터의 개수도 줄였다. 제안하는 전류원 회로에 대하여 200[V], 30[A]급 축소모델을 설계하여 시뮬레이션과 실험을 통하여 제안하는 전류원 회로의 유효성을 입증하였다.

# 2. 제안한 방식의 전류원 회로

#### 2.1 합성시험회로 개요

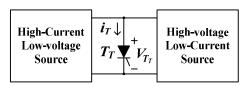

그림 1은 전류형 HVDC 시스템의 SCR 사이리스터 밸브 시험을 위한 일반적인 합성시험회로의 블럭다이어 그램 및 밸브 인가 전압과 밸브 도통 전류에 대한 일반적인 파형을 나타낸 것이다.

대전류-저전압 전원부는 시험 밸브(Tr)의 턴-온 신호에 따라 시험 전류(ir)를 제공하고, 고전압-저전류 전원부는 시험 밸브의 턴-오프 시 밸브 전압( $V_{T_T}$ )을 인가한다. 그런데 이 두개의 전원부는 상호 독립되어 있으므로 각 전원장치에서 공급하는 전력이 최소화 되므로시스템 전체의 비용이 절감되고 장치도 소형화되는 장점이 있다.

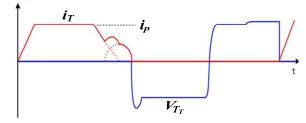

그림 2는 기존 STC 중 하나를 나타낸 것인데 그림 1의 대전류-저전압 전원부를 구성하고 있는 부품들은 6-pulse 사이리스터 컨버터, 3상 다이오드 정류기, 4개의 IGBT (S1  $\sim$  S4), 2개의 다이오드(D1, D2), 2개의 인덕터( $L_a$ ,  $L_b$ ), 보조 커패시터  $C_{Aux}$ , 그리고 보조 사이리스터 밸브  $T_{Aux}$ 로 이루어져 있다.

본 논문에서는 그림 1의 대전류-저전압 전원부에 대한 새로운 방식의 회로를 제시하였으며 고전압-저전류전원부는 기존에 제안된 회로와 구조 및 동작 원리가동일하다. 따라서 전류원 회로에 대한 구조와 동작 원리를 중심으로 기술하고자 한다.

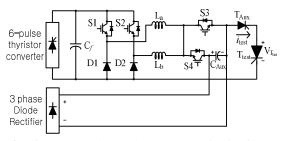

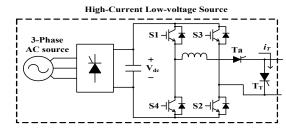

# 2.2 회로 구성

그림 3은 본 논문에서 제안하는 합성시험을 위한 전류원 회로 구성도이며 그림 1에 나타낸 블럭 다이어그램의 왼쪽 부분을 상세히 나타낸 것으로서 그림 2의 전류원 회로보다 매우 간단하다는 것을 알 수 있다. 6-pulse 사이리스터 컨버터를 이용하여 교류 전원을 직류 전원 Vac로 변환한 후 full-bridge 컨버터를 이용하여 SCR 사이리스터 밸브에 흐르는 시험 전류 ir를 제공하도록 되어있다. 보조 밸브 Ta는 전류원 회로의 동작이 완료된 후 고전압-저전류원 회로에서 발생하는 시험 전압이 전류원 회로에 영향을 미치지 않도록 하기위하여 삽입되었으며 저전압-대전류 전원부를 고전압으로부터 보호하는 기능을 한다. Ta의 전압 정격은 Tr의 전압정격과 동일하다.

(a) Bolck diagram of synthetic test circuit

(b) Typical valve voltage and current waveform Fig. 1. Block diagram and typical waveform of STC.

Fig. 2. High-current low-voltage source circuit diagram of conventional STC.

Fig. 3. Proposed circuit diagram of high-current low-voltage source.

#### 2.3 동작 원리

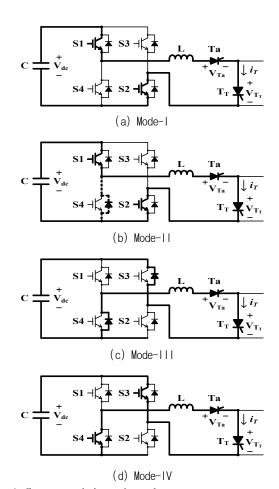

그림 4에 본 논문에서 제안하는 대전류-저전압원 회로의 모드별 전류 흐름도를 나타내었으며 그림 5에 시험밸브 Tr에 흐르는 전류, 인가되는 전압, 그리고 스위칭 신호를 나타내었다. 그림 4에서 굵은 선은 전류가 흐르는 경로이며 시험 전류 ir의 기준 방향은 화살표로표시하였다. 각 모드별 동작을 설명하면 다음과 같다.

#### Mode-I ( $t_0 \sim t_1$ )

Mode-I 은 S1, S2,  $T_a$ , 그리고 Tr를 턴-온 하면 시작되며 시험 밸브에 흐르는 전류를 상승시키는 구간이다. Mode-I 의  $to \sim t_1$ 구간은 실제 HVDC 시스템의 SCR 사이리스터의 커뮤테이션 시 발생하는 중복각 구간에 해당하며 ir가 그림 1-(b)에 나타낸  $i_p$ 까지 도달하는데 걸리는 시간이다.

Fig. 4. Current path in each mode.

Fig. 5. Voltage and current waveforms of test valve and switching signals.

이는 입력 전원의 임피던스와 전원과 HVDC 컨버터를 연결하는 선로의 임피던스 성분을 합한 임피던스의 크기에 영향을 받는다. 스위치의 전압강하와 저항 성분을 무시하면 ir는 식 (1)로 나타낼 수 있으며 전류는 C-S1 - L -  $T_a$  - Tr - S2 를 따라 흐른다.

$$i_T = \frac{1}{L} \times V_{dc} \times t \tag{1}$$

## Mode-II ( $t_1 \sim t_2$ )

Mode-II는 중복각을 지난 후 전류를 유지하는 구간이다. 전류원 회로는 단상 쵸퍼 동작을 하며 S2는 온 상태를 유지하고 S1의 듀티를 이용하여 플랫탑(*ip*) 전류를 제어한다. S1이 온 상태인 경우 전류는 Mode-I과 동일한 경로로 흐르며 S1이 오프 상태인 경우 전류는 Diode (S4) - *L* - *Ta* - *Tr* - S2를 통하여 흐른다.

#### Mode-III ( $t_2 \sim t_3$ )

S1과 S2를 턴-오프 하면 Mode-III 이 시작되며 시험 밸브에 흐르는 전류가 감소한다. 실제 HVDC 시스템에서 중복각에 해당하며 Mode-I 구간과 유지 시간이 유사하다. 반도체 소자의 전압강하와 저항 성분을 무시하면이 구간에서의 ir는 식 (2)와 같이 나타낼 수 있다. 전류는 C - Diode (S4) - L -  $T_a$  -  $T_r$  - Diode (S3) 의 경로로흐른다.

$$i_T = i_{T(t_2)} + \frac{1}{L}(-V_{dc}) \times (t - t_2)$$

(2)

# Mode-IV ( $t_3 \sim t_4$ )

Mode-III 에서 전류가 영 (Zero) 이 된 시점 (ts) 에 S3 과 S4를 턴-온하면 Mode-IV 가 시작된다. Mode-IV 는 보조 사이리스터 밸브  $T_a$ 에 역전압을 인가하여 보조 사 이리스터 밸브의 턴-오프 타임을 확보하도록 하기 위하 여 마련된다.  $T_a$ 에 인가되는 역전압의 크기는  $V_{dc}$ 와 같 고 전류는 흐르지 않으며 전압이 인가되는 경로는  $V_{dc}$ -S3 - Tr - Ta - L - S4 이다. 그런데 이 때 고전압-저전류 전원부로부터 공급되는 전류가 Tr를 통해 흐르기 때문 에  $T_T$ 에 인가되는 전압은 영(Zero)에 가깝다.  $T_T$ 의 전류가 영이 되기 전에  $T_a$ 는 완전히 오프하게 되고  $T_T$ 의 전류가 영이 되면  $T_T$ 에는 고전압-저전류 전원부에 서 공급하는 고전압이 역전압으로 인가된다. 이 역전압 은 S2 - C(Vac) - S1 - L - Ta 의 경로를 통해 대전류-저 전압 전원부에도 인가되지만  $T_a$ 의 전압 정격과  $T_T$ 의 전압 정격이 동일하여 대부분의 전압이  $T_a$ 에 인가되기 때문에 대전류 전원부는 고전압으로부터 안전하게 된다.

Mode-IV 이후 전압원 회로의 동작이 완료되면 다시 Mode-I 이 시작되며 시험 밸브에 반복적인 전류와 전압 스트레스를 인가하여 시험 밸브의 정상 동작 유무를 확인한다.

#### 2.4 회로 설계

HVDC 시스템의 용량에 따라 시험 전류와 전압의 크기도 달라지는데 합성시험회로는 이러한 점을 고려하여 시험 전류와 시험 전압의 크기를 조절 할 수 있는 능력 이 요구된다. 합성시험회로의 전류원과 전압원 회로의 요구 사항은 다음과 같다.

- 시험 전류의 상승 시간 (to ~ t1) 제어

- 시험 전류의 플랫탑 (*ip*) 크기 제어

- 시험 전류의 하강 시간(t2~t5) 제어

- 시험 밸브에 인가되는 순방향 전압 및 역방향 전압의 크기와 시간 제어

전류원 회로에서 설계해야 하는 파라미터는 L이며 L은 실제 HVDC 시스템의 중복각을 모의할 수 있도록 결정한다. 전류원 회로의 입력 전압의 크기는 매우 낮기때문에 반도체 소자의 온 전압강하를 고려한 Mode-I에서의 ir는 식 (3)을 이용하여 나타낼 수 있다. 식 (3)에서  $V_{SI}$ ,  $V_{Ta}$ ,  $V_{Tr}$ ,  $V_{SZ}$ 는 각 첨자에 해당하는 반도체 소자의 순방향 전압강하를 의미한다.

$$i_{T} = \frac{V_{dc} - (V_{S1} + V_{Ta} + V_{T_{T}} + V_{S2})}{L} \times t \tag{3}$$

이와 함께 전류의 하강 시간도 제어할 수 있어야 한다. ir가 하강하는 구간을 나타내는 Mode-III에서 ir는 식 (4)로 나타낼 수 있다.

$$i_T = i_{T(t_2)} - \frac{\left( V_{dc} + V_{S1} + V_{Ta} + V_{T_T} + V_{S2} \right)}{L} \times (t - t_2) \tag{4} \label{eq:4}$$

식 (3)과 식 (4)에서 알 수 있듯이 Mode-III에서는 Mode-I 구간과는 다르게 전력 반도체 소자의 순방향 전 압강하가  $V_{dc}$  전압과 더해져 L에 인가되기 때문에  $i\tau$ 는 빠르게 감소한다. 이러한 문제점은 전압원 회로의 공진 전류 주입 타이밍을 이용하여 중복각에 해당하는 시간으로 제어 가능하기 때문에 L의 설계는  $i\tau$ 가 상승하는 Mode-I 구간을 기준으로 설계한다. 식 (3)에서 알 수 있듯이 전류의 크기와 상승시간을 제어하는데 사용 가능한 변수는 L과  $V_{dc}$ 이며, 제안하는 전류원 회로에서  $V_{dc}$ 의 크기는 Mode-IV에서 역전압을 인가하는데 사용되므로 먼저  $V_{dc}$ 의 최소값을 결정 한 후 식 (5)를 이용하여 L의 크기를 설계한다.

$$L = \frac{V_{dc} - (V_{S1} + V_{Ta} + V_{T_T} + V_{S2})}{i_T} \times t_c \tag{5}$$

여기서, tc는 Mode-I 이 유지되는 시간을 의미하며 실제 시스템에서의 중복각에 해당한다.

## 3. 시뮬레이션 결과 분석

#### 3.1 시뮬레이션 파라미터

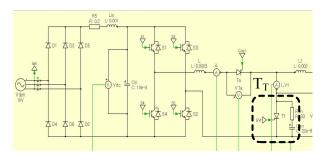

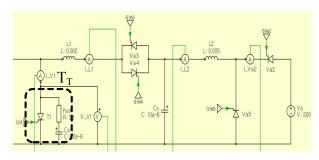

제안하는 방식의 전류원 회로를 검증하기 위한 시뮬레이션을 수행하였다. 그림 6에 Plecs 시뮬레이션 회로도를 나타내었다. 그림 6-(a)는 전류원 회로도이며 그림 6-(b)는 전압원 회로도이다. 이와 함께 시뮬레이션에 사

(a) High-current low-voltage source

(b) High-voltage low-current source

Fig. 6. Simulation circuit using plecs.

TABLE I SYSTEM PARAMETERS

| Parameter         |                     | Value    |

|-------------------|---------------------|----------|

| Current<br>Source | $V_{dc}$            | 20 [V]   |

|                   | $L_{in}$            | 1 [mH]   |

|                   | $C_{in}$            | 10 [mF]  |

|                   | L                   | 300 [uH] |

| Voltage<br>Source | $V_S$               | 200 [V]  |

|                   | $L_{I}$             | 2 [mH]   |

|                   | $L_2$               | 5 [mH]   |

|                   | $C_S$               | 10 [uF]  |

| Test<br>waveforms | i <sub>T,</sub> max | 30 [A]   |

|                   | $V_{T_T}$ , max     | 200 [V]  |

용한 파라미터를 표 1에 나타내었으며 실험실 레벨에서 검증을 위하여 설계된 파라미터이다. 전류원 회로의 입력 전압  $V_{de}$ 는 슬라이닥스와 3상 다이오드 정류기를 이용하여 생성하였다.

## 3.2 시뮬레이션 결과 파형

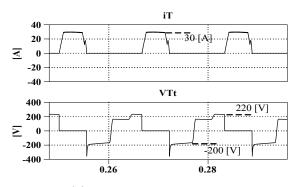

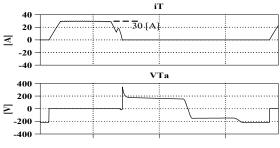

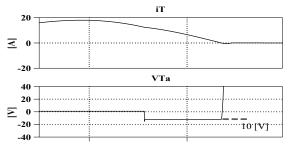

그림 7에 제안하는 전류원 회로를 이용한 사이리스터 밸브의 합성시험 파형을 나타내었다. 그림 7-(a)에 시험 밸브에 인가되는 시험 전류와 시험 전압 파형을 나타내었다. 시험 밸브에 인가되는 전압은 순방향인 경우 220

(a) Test waveforms of  $i_{T}$  and  $V_{T_{T}}$

(b) Waveforms of  $i_T$  and  $V_{Ta}$

(c) Time scale zoomed waveforms of  $i_T$  and  $V_{Ta}$  Fig. 7. Simulation waveforms of  $i_T$ ,  $V_{Ta}$  and  $V_{Tx}$

[V], 역방향인 경우 200 [V] 이며 시험 밸브에 흐르는 전류의 최대치  $i_p$ 는 30 [A]인 것을 확인할 수 있다. 그림 7-(b)에 시험 전류 파형과 보조 사이리스터 밸브에 인가되는 전압파형을 나타내었으며 그림 7-(c)에 전류원 회로의 동작이 완료되는 순간을 확대한 파형을 함께 나타내었다. 보조 밸브의 턴-오프 시  $V_{dc}$ 와 동일한 크기의역전압이 인가되는 것을 확인 할 수 있다.

# 4. 실험 결과

STC 의 다양한 기능을 나타내는 실험결과는 [4]에 상세히 나타나 있으므로 여기서는 전류원 부분만 집중해서 실험결과를 제시하고자 한다. 그림 8은 시뮬레이션과동일한 파라미터로 제작된 합성시험회로의 축소 모형이다. S1, S2, S3, 및 S4는 하나의 모듈에 두개의 IGBT가들어있는 Fairchild 사의 FM2G100US60 소자를 사용하였으며  $T_a$ 와  $T_T$ 는 SEMIKRON 사의 SKKT 57/16을 사용하였다. 합성시험회로의 제어는 Texas Instruments 사

Fig. 8. Experimental set-up for proposed high-current source of synthetic test circuit.

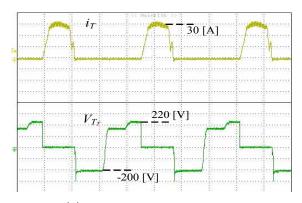

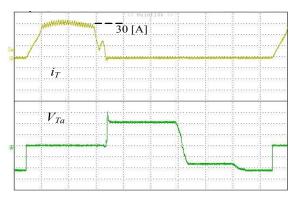

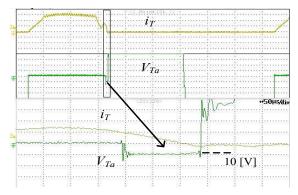

(a) Test waveforms of  $i_{T}$  and  $V_{T_{T}}$

(b) Waveforms of  $i_T$  and  $V_{Ta}$

(c) Time scale zoomed waveforms of  $i_T$  and  $V_{Ta}$  Fig. 9. Experimental waveforms of  $i_T$ ,  $V_{Ta}$ , and  $V_{T_T}$

의 TMS320F28335를 사용하였다. 보조 밸브와 시험 밸 브는 한 개의 SCR 사이리스터 소자를 사용하였다.

그림 9에 시험 전류와 시험 전압 파형을 나타내었다. 그림 9-(a)의 시간축 스케일은  $5 \left[ \text{ms/DIV} \right]$ 이며 그림 9-(b)와 9-(c)의 시간축 스케일은  $2 \left[ \text{ms} \right]$ , 시험 파형의 주기는 약  $17 \left[ \text{ms} \right]$ 이며 시험 전류  $i\tau$ 의 최대값  $i_p$ 는 약  $30 \left[ \text{A} \right]$ , 시험 전압  $V_{T_r}$ 는 순방향인 경우  $220 \left[ \text{V} \right]$ , 역방향인 경우  $200 \left[ \text{V} \right]$ 가 인가됨을 알 수 있는데 이는 시뮬레이션 결과와 유사하다는 것을 알 수 있다.

## 5. 결 론

본 논문에서는 전류형 HVDC의 사이리스터 밸브 시험을 위한 개선된 전류원회로를 제안하였다. 제안한 방식의 전류원 회로부는 기존 방식에 비해 보조 밸브의턴-오프를 위한 회로가 간단하여 부품의 갯수가 줄어들고 아울러 제어도 간단해진다는 장점이 있다. 기존 방식에서는 보조 밸브의턴-오프를 위하여 별도의 전원을 사용하였으나 제안한 회로에서는 대전류-저전압 전원부의 직류 입력전압을 활용함으로써 시스템 구성을 간단히할 수 있었다. 200 [V], 30 [A] 급의 축소 모형에 대한합성시험회로의 시뮬레이션과 실험을 통하여 제안한 방식의 전류원 회로가 타당함을 입증하였다. 제안하는 합성시험회로의 전류원 회로는 전류형 HVDC의 사이리스터 밸브 시험 장치의 성능과 신뢰도를 향상시키고 시스템 구성비용을 절감하는데 큰 기여를 할 것으로 기대된다.

이 논문은 부경대학교 자율창의학술연구비(2014년)에 의하여 연구되었음.

#### References

- [1] B. L. Sheng, E. Jansson, A. Blomberg, H. O. Bjarme, and D. Windmar, "A new synthetic test circuit for the operational tests of HVDC thyristor modules," *Applied Power Electronics Conference and Exposition(APEC)*, Vol. 2, pp. 1242–1246, Sep. 2001.

- [2] T. Bauer, H. P. Lips, G. Thiele, T. Tylutki, and M. Uder, "Operational tests on HVDC thyristor modules in a synthetic test circuit for the sylmar east restoration project," *IEEE Transactioins on Power Delivery*, Vol. 12, No. 3, pp. 1151–1158, Jul. 1997.

- [3] M. L. Woodhouse and T. Simanwe, "A new facility for testing HVDC and SVC thyristor valves," B4-309, CIGRE 2006.

- [4] E. C. Nho, B. M. Han, Y. H. Chung, S. T. Baek, and J. H. Jung, "Synthetic test circuit for thyristor valve in HVDC converter with new high-current source," *IEEE*

- Transactions on Power Electronics, Vol. 29, No. 7, pp. 3290–3296, Jul. 2014.

- [5] J. H. Jung, B. J. Goo, H. J. Jeo, E. C. Nho, B. M. Han, Y. H. Chung, and S. T. Baek, "A synthetic test circuit for HVDC thyristor valve test with simplified turn-off circuit of auxiliary thyristor," *Transactions of the Korean Institute of Power Electronics*, Vol. 19, No. 5, pp. 475–480, Oct. 2014.

# 정재헌(鄭在憲)

1981년 10월 19일생. 2007년 부경대 공대 전기제어공학부 졸업. 2009년 부경대 대학 원 전기공학과 졸업(석사). 2009년~현재 동 대학원 박사과정.

## 조한제(趙韓濟)

1980년 11월 19일생. 2007년 동의대 공대 전기공학과 졸업. 2008년~2011년 (주)효성 근무. 2011년~현재 LS산전 근무. 2013년~ 현재 부경대 대학원 전기공학과 석사과정.

# 구법진(具法陳)

1988년 7월 11일생. 2013년 부경대 공대 전 기공학과 졸업. 2015년 부경대 대학원 전기 공학과 졸업(석사). 2015년~현재 LS산전 근 무.

#### 노의철(魯義哲)

1960년 8월 2일생. 1984년 서울대 공대 전기공학과 졸업. 1986년 KAIST 전기 및 전자공학과 졸업(석사). 1991년 동 대학원 전기 및 전자공학과 졸업(공박). 1997년~1998년 미국 Univ. of Wisconsin-Madison 방문교수.

2005년~2006년 미국 University of California-Irvine 방문교수. 1995년~현재 부경대 전기공학과 교수. 당 학회 부회장.

## 정용호(鄭容昊)

1960년 5월 29일생. 1983년 한양대 공대 전 자공학과 졸업. 1985년 KAIST 전기 및 전 자공학과 졸업(석사). 1990년 동 대학원전기 및 전자공학과 졸업(공박). 1994년 ~ 1995년 미국 Wisconsin-Madison대 방문연구

원. 1985년~현재 LS산전 연구위원.

#### 백승택(白承澤)

1971년 11월 24일생. 1997년 명지대 공대 전기공학과 졸업. 1999년 동 대학원 전기공 학과 졸업(석사). 2004년 동 대학원 전기공 학과 졸업(공박). 2006년~2010년 ㈜효성 중 공연구소 연구원. 2010년~현재 LS산전 수

석연구원.