## 고해상도 디스플레이를 위한 고속 구동 Data Driver IC 설계 기술

김종석. 최병덕(한양대학교 전자컴퓨터통신공학과)

### 1. 서 론

소비자들에게 향상된 화질 및 몰입감을 제공하기 위 해 디스플레이의 성능은 계속해서 향상되고 있다. 최근 들어, 디스플레이의 가로 해상도(resolution)가 4K 급 인 UHD 디스플레이가 TV 시장을 주도하고 있으며, 머 지않은 미래에는 8K 급의 quad UHD 디스플레이가 시장을 이끌 것으로 예상된다. 또한 모션 블러(motion blur) 없는 고화질 구현을 위해 디스플레이의 프레임 주파수는 기존 60Hz에서 240Hz까지 증가하고 있다. 이러한 고해상도, 고화질 디스플레이를 구현하기 위해 서는 다양한 기술적인 문제를 극복하여야 하는데, 가장 대표적인 문제는 해상도 및 프레임 주파수 증가에 따른 구동 시간 부족 문제이다. 디스플레이 픽셀에 정확한 data 전압을 인가하기 위해서는 충분한 충전시간이 요 구되지만, 식 (1)에 나타나듯이 해상도 및 프레임 주파 수의 증가는 row-line 시간을 감소시킨다.(TROW는 row-line 시간, N<sub>ROW</sub>는 row-line의 개수, 그리고 f<sub>FR</sub> 은 프레임 주파수를 나타낸다.)

$$T_{ROW} = \frac{1}{N_{ROW} \cdot f_{ER}} \tag{1}$$

따라서, 급격하게 줄어든 row-line 시간에 대응하기 위해, 고속 구동이 가능한 저전력, 고속 data driver IC 설계 기술이 절실히 요구되고 있다. 본고에서는 이와 같은 고속 data driver IC 구현을 위한 핵심 기술인 저전력, 고속 buffer amplifier 설계 기술에 대해 기술하고자 한다.

## 2. 본 론

## 2.1. Data driver IC의 구조 및 buffer amplifier의 역할

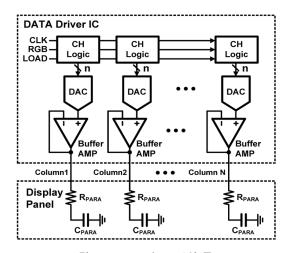

[그림 1]에 display data driver의 block diagram 을 나타냈다. Data driver는 직렬로 입력되는 digital

그림 1. Data Driver IC의 구조

display data(RGB)를 각 채널별로 병렬적으로 배열하는 channel logic, digital data를 analog 전압으로 변환하는 digital-to-analog converter(DAC), 큰 부하(RPARA, CPARA)를 갖는 column line에 DAC 전압을 빠르게 충, 방전하기 위한 buffer amplifier로 구성되어 있다.

구동 속도의 관점에서, channel logic의 동작 속도는 큰 문제가 되지 않는 반면, DAC와 amplifier의 동작속도는 data driver의 구동속도를 결정한다고 말할수 있다. 본고에서는, 고속 data driver IC를 구현하기위해, 고속 buffer amplifier 설계 기술을 중점적으로살펴본다.

### 2.2. Traditional buffer amplifier의 특징 및 한계

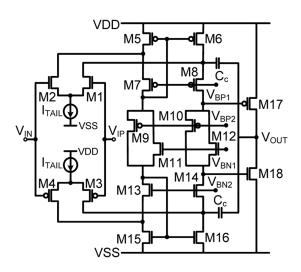

Data driver 용 buffer amplifier는 출력전압의 오차를 줄이기 위해 높은 전압이득을 가져야 하고, DAC 전압을 정확하게 전달하기 위해 넓은 범위의 입출력 전압범위를 가져야 한다. 또한 우수한 화질을 보장할 수있는 N-dot inversion 구현을 위해 push-pull 동작이가능해야 한다. 이러한 조건을 만족하기 위해 [그림 2]의 amplifier [1]가 data driver IC에 널리 사용되고있다.

Buffer amplifier의 구동속도를 증가시키려면 buffer

그림 2. Rail-to-rail folded cascade class-AB amplifier (traditional buffer amplifier) [1]

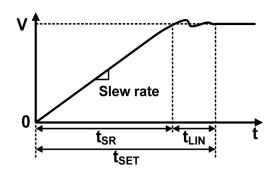

그림 3. Buffer amplifier의 정착시간(settling time)

amplifier의 정착시간(settling time)을 줄여야 한다. [그림 3]과 같이, amplifier의 정착시간(tser)은 슬루잉 시간(slewing time, tsr)과 선형정착시간(linear-settling time, tlin)으로 나뉠 수 있다. 그림에서와 같이, 일정한 기울기(슬루율, slew rate)를 가지며 출력전압이 증가하는 슬루잉 시간은 전체 정착시간의 큰 부분을 차지한다. 따라서 amplifier의 의 정착시간을 줄이기 위해서, 다시말해 amplifier의 구동속도를 높이기 위해서, 높은 슬루율을 갖는 amplifier의 설계가 필수적으로 요구된다.

그러나, 앞서 소개한 [그림 2]의 traditional buffer amplifier는 슬루율을 향상시키는데 상당한 제약이 따른다. 식 (2)는 traditional buffer amplifier의 슬루율을 나타낸 식이다.

$$SR = I_{TAII}/C_C \tag{2}$$

식에서 확인할 수 있듯이, 슬루율을 증가시키려면 주파수 보상 캐패시터(compensation capacitor, Cc)의크기를 줄이거나 amplifier의 입력단의 tail current (ITAIL)를 증가시켜야 한다. 그러나, 보상 캐패시터를 감소시킬 경우, amplifier의 위상여유(phase margin)가감소하여 주파수 특성이 나빠지며, 이로 인해 시스템이불안정해진다. 다른 방법으로, ITAIL을 증가시킬 경우, data driver에 사용되는 수 천 개의 buffer amplifier의 소비전력이 함께 증가하므로 디스플레이 시스템의소비전력이 크게 늘어난다는 단점이 있다. 따라서, amplifier의 동작속도와 소비전력은 tradeoff 관계라고할 수 있으며, 이는 고속 data driver IC 구현에 걸림돌로 작용하고 있다.

## 2.3. Dynamic biasing circuit을 이용한 slew-rate enhanced(SRE) amplifier I

앞서 설명한 traditional buffer amplifier의 제한된 슬루율 문제를 해결하기 위해, 소비전력이 작으면서도 높 은 슬루율을 구현할 수 있는 slew-rate enhanced(SRE) amplifier에 대한 연구가 이루어지고 있다.

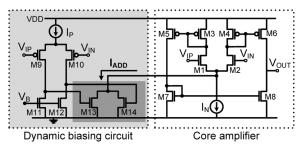

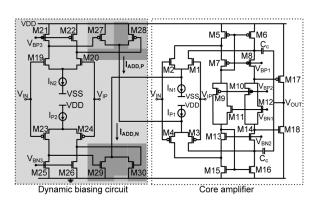

[그림 4]는 적은 소비전력으로도 높은 슬루율을 달성하기 위해 dynamic biasing circuit을 사용한 SRE amplifier(이하 SRE amplifier I으로 명명)이다 [2]. 그림의 dynamic biasing circuit은 입력 및 출력 전압이같은 정상상태(steady state)에서는 turn-off 되어서 최소한의 전류만 사용한다. 그러나 입력전압이 크게 바뀌는 슬루잉 상황이 되면, 추가적인 전류(I<sub>ADD</sub>)를 발생시키므로 core amplifier의 슬루율을 크게 증가시킬 수있다.

자세한 동작은 다음과 같다. Dynamic biasing circuit의 M13, M14 트랜지스터 게이트 전압은 정상상태에서 낮은 전압을 갖도록 설계되므로, 정상상태에서는 M13과 M14가 꺼져있다. 따라서 M13 및 M14에 흐르는 전류는 없으므로 dynamic biasing circuit에 사용되는 전류는 무시할 수 있을 만큼 작다. 반면, amplifier의 positive 입력전압( $V_P$ )이 크게 증가하는 슬루잉 조건이 될 경우, M9가 꺼져서 모든  $I_P$  전류가 M10으로 흐른다. 이로 인해 M14의 게이트 전압이 증가하여 M14가 켜지고, 반대로 M13의 게이트 전압은 감소하여 꺼진 상태를 유지한다. M14가 켜지면  $I_{ADD}$ 가 발생하여 core amplifier의 입력단에 추가 전류를 발생시키고, 이를 통해서 core amplifier의 슬루율을 크게 증가시킬 수 있다. 슬루잉 시간이 끝나고  $V_P$  전압이  $V_{OUT}$  전압과 같아지면 amplifier는 정상상태로 되돌아

그림 4. Slew-rate enhanced(SRE) amplifier I [2]

간다. 정상상태에서 M14는 꺼져서 IADD는 0이 되고, 전력소비를 최소화 할 수 있다. 위의 동작을 통해 SRE amplifier I은 적은 소비전력으로도 큰 슬루율을 가질수 있다.

이러한 장점에도 불구하고, SRE amplifier I은 몇 가지 단점으로 인해 display driver IC에 적용되기 어렵다. 첫째, core amplifier의 전압이득이 상대적으로 낮아서, 이득오차(gain error)가 크다. 둘째, core AMP가 NMOS input stage 만으로 구성되어 있으므로 DAC에서 발생하는 전압을 정확하게 디스플레이 픽셀에 전달하기 어렵다. 위의 단점들은 회로의 구조적인 문제이므로, amplifier의 구조개선을 통해 문제 해결이 가능하다.

## 2.4. Dynamic biasing circuit을 이용한 SRE amplifier II

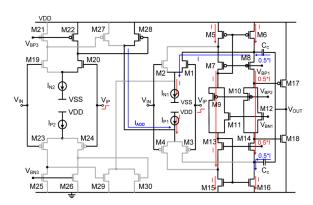

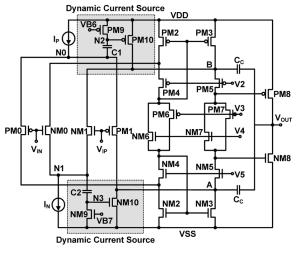

SRE amplifier I의 문제를 해결하기 위해, [그림 5]의 SRE amplifier(이하 SRE amplifier II라 명명)가 제안되었다[3]. SRE amplifier II는 data driver IC에 널리사용되고 있는 [그림 2]의 traditional buffer amplifier를 core amplifier로 사용하여 높은 전압이득, 넓은 입출력 전압범위를 가질 수 있으므로, SRE amplifier I의단점을 해결할 수 있다. 또한 [그림 4]의 dynamic biasing circuit을 사용함으로써 적은 소비전력으로도 높은 슬루율을 달성할 수 있다.

SRE amplifier II는 구조의 개선을 통해 SRE amplifier I의 단점들을 개선했으나, 슬루율 증가 범위가 작다는 한계점을 지니고 있다. [그림 6]은 입력전압  $(V_P)$ 이 높은 전압영역에서 변하는 high-to-high

그림 5. Slew-rate enhanced(SRE) amplifier II [3]

그림 6. SRE amplifier II의 high-to-high transition 동작

transition시 SRE amplifier II의 동작을 나타낸 그림이다. VIP 전압이 높기 때문에, core amplifier의 PMOS 입력단인 M3과 M4가 꺼지고, dynamic biasing circuit의 PMOS 입력단인 M23과 M24 또한 꺼진다. 이로 인해 M29 및 M30도 꺼져서 전류를 발생시키지 않는다. 반면 dynamic biasing circuit의 NMOS 입력단인 M20은 켜져서 IN2가 모두 M20으로 흐르고, 이를통해 M28이 켜져서 IADD를 발생시킨다. 그러나 그림에서와 같이 M3, M4가 꺼져있으므로, IADD가 core amplifier에 흐를 수 없고, 슬루율 향상에 기여할 수 없다. 따라서, SRE amplifier II는 입력전압이 높은 경우, dynamic biasing circuit을 사용하더라도 슬루율 증가효과를 기대하기 어렵다.

# 2.5. Dynamic biasing circuit을 이용한 SRE amplifier III

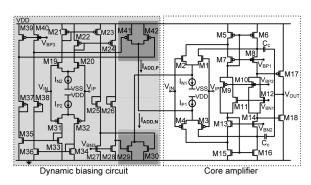

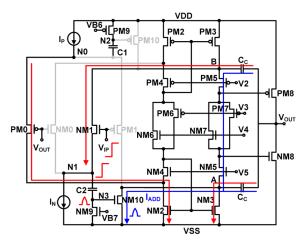

앞서 설명했듯이 SRE amplifier II의 제한된 슬루율증가 범위 현상은, 높은 전압영역에서 발생한 추가 전류가 core amplifier의 PMOS 입력단으로, 낮은 전압영역에서 발생한 추가 전류가 core amplifier의 NMOS 입력단으로 흐르기 때문에 발생한 구조적인 문제이다. 이러한 구조적 문제를 해결하기 위해 [그림 7]의 SRE amplifier(이하 SRE amplifier III)가 제안되었다[4].

[그림 8]은 SRE amplifier III의 high-to-high transition 상황을 나타낸 그림이다. 그림에서와 같이 높은 입력 전압으로 인해 core amplifier 및 dynamic biasing circuit의 PMOS 입력단 M3, M4, M31, M32가 꺼진다. 반면 dynamic biasing circuits의

그림 7. Slew-rate enhanced(SRE) amplifier III [4]

그림 8. SRE amplifier III의 high-to-high transition 동작

NMOS 입력단인 M20은 켜지므로 모든  $I_{N2}$  전류가 M20으로 흐르고, 이를 통해 M29가 켜져서  $I_{ADD}$  전류를 발생시킨다. 발생된  $I_{ADD}$ 는 amplifier core의 NMOS 입력단인 M1으로 흐르기 때문에 슬루율 향상에 기여한다. 따라서, 위의 동작을 통해 SRE amplifier III는 SRE amplifier II와는 다르게, high-to-high transition 상황에서도 높은 슬루율을 가질 수 있다는 것을 알 수 있다.

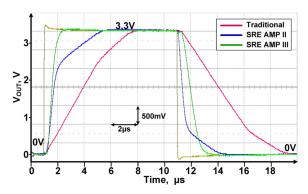

그림 9. Traditional amplifier 및 SRE amplifier II, III의 측 정파형

앞서 소개한 traditional amplifier 및 SRE amplifier II, III 세 종류의 amplifier의 속도를 비교하기 위해 [그림 이에 각 amplifier의 출력전압 측정파형을 나타냈다. 그림에서와 같이 traditional amplifier는 가장 느린 settling time을 갖는다. SRE amplifier II는 일부 영역에서는 슬루율이 증가하지만 low-to-high transition시 높은 전압 범위(high-to-low transition시 낮은 전압범위)에서 슬루율 증가 효과가 없다. 이에 반해, SRE amplifier III는 전 영역에서 높은 슬루율을 가지므로 가장 빠른 속도를 나타낸다. 따라서, 고속 구동을 위한 data driver IC에 SRE amplifier III가 적합할 것으로 예상된다.

## 2.6. Dynamic current source를 이용한 SRE amplifier IV

앞서 살펴본 SRE amplifier I, II, III는 작은 소비전력으로도 높은 슬루율을 달성할 수 있으나, dynamic biasing circuit의 동작을 위해 추가적인 전류가 필요하다. 추가된 전류는 그 크기가 작지만, 구조적으로 amplifier의 전력소모가 증가할 수밖에 없다.

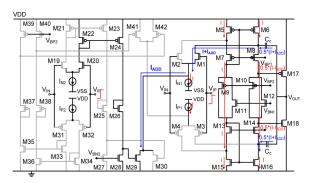

위의 한계점을 개선하기 위해, 추가적인 전력소모가 전혀 없는 dynamic current source를 이용한 SRE amplifier(이하 SRE amplifier IV)가 제안되었다[5]. SRE amplifier IV의 구조는 [그림 10]에 나타냈다. 앞서 소개한 [그림 2]의 traditional amplifier가 core

그림 10. Slew-rate enhanced(SRE) amplifier IV [5]

amplifier로 사용되었으며, 두 개의 트랜지스터와 한 개의 캐패시터로 구성된 dynamic current source가 core amplifier의 NMOS, PMOS 입력단에 추가되었다.

SRE amplifier IV의 동작은 다음과 같다. NM9는 VB7에 의해 항상 켜져 있으므로, 정상상태에서 N3 전 압은 0V이다. 이에 NM10은 꺼지므로 발생되는 전류가 없다. NM9가 항상 켜져 있지만 NM9의 drain은 C2에 연결되어 있으므로 전류를 발생시키지 않고, 따라서 추가된 dynamic current source에 전력소모가 전혀 없다. [그림 11]과 같이  $V_P$ 전압이 증가할 경우, NM1의 source 전압인 N1 전압이 함께 증가한다. N1 전압이 증가하면 C2의 coupling 현상에 의해 N3 역시 증가하고, 이로 인해 NM10이 켜져서 전류  $I_{ADD}$ 를 발생시킨다.  $I_{ADD}$ 는 core amplifier에 추가되어서 슬루율을 크게 향상시킬 수 있다.

그림 11. SRE amplifier IV의 low-to-high transition 동작

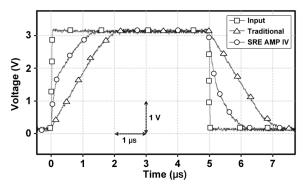

그림 12. Traditional amplifier 및 SRE amplifier IV의 측정 파형

[그림 12]에 traditional amplifier와 SRE amplifier IV의 측정파형을 나타냈다. 그림에서와 같이, SRE amplifier IV의 슬루율이 traditional amplifier에 비해 크게 증가하여 더 빠른 정착시간을 갖는다. 정상상태에서의 SRE amplifier IV의 전력소비는 traditional amplifier와 정확하게 같으므로, SRE amplifier IV는 저소비전력, 고속 구동용 data driver IC에 적합할 것으로 예상된다.

### 3. 결 론

본고에서는 해상도가 높고 프레임 주파수가 높은 고화질 디스플레이 구현 시 발생하는 구동회로 속도 문제에 대해 살펴보았고, 고속 data driver IC용 buffer amplifier 설계 기술에 대하여 살펴보았다. 특히 소비전력을 최소화하면서 높은 슬루율을 확보하기 위한 기존의 SRE amplifier I, II, III, IV의 구조 및 동작을 소개했다. 본고에서는 슬루율을 중심으로 고속 구동 data driver 설계 기술을 살펴보았으나, 이와 더불어 선형정착시간의 단축을 위한 설계 기술도 향후 연구가 절실히요구되며, 이때도 소비전력의 증가를 최소화하여야 한다는 점이 매우 중요하다.

### 참고문헌

[1] R. Hogervorst and J. Huijsing, *Design of low-voltage, low-power operational amplifier cells*, (1996).

- [2] R. Klinke, B. J. Hosticka, and H. J. Pfleiderer, *IEEE J. of Solid-State Circuits* **24**, 744 (1989).

- [3] J. Choi, K. Min, and C. Yoo, *SID Symp. Digest of Tech. Papers* **38**, 1647, (2007).

- [4] J. S. Kim, J. Y. Lee, and B. D. Choi, *Electronics Letters* **48**, 924, (2012).

- [5] H.-W. Kim and B.-D. Choi, *Proc. IMID 2002* 220, (2012).

### 저 자 약 력

#### 김 종 석

- 2010년: 한양대학교 전자통신컴퓨터공학부 공학사

- 2012년: 한양대학교

전자컴퓨터통신공학과 공학석사

- 2012년~현재: 한양대학교 전자컴퓨터통신공학과 박사과정

- 관심분야 Driving methods and circuits for flat panel displays, Power management IC design, Analog circuit design

#### 최 병 덕

- 1994년: 한양대학교 전자공학과 공학사

- 1996년: 한양대학교 전자공학과 공학석사

- 2002년: 한양대학교 전자공학과 공학박사

- 2001년~2005년: LG전자 System IC R&D Center, 선임연구원

- 2005년~현재: 한양대학교 전자컴퓨터통신공학과 교수

- 관심분야: Driving methods and circuits for flat panel displays, Hardware

implementation for cryptographic devices, Low-power circuit and analog circuit design, Power IC design