IEIE Transactions on Smart Processing and Computing

# A Multi-bit VCO-based Linear Quantizer with Frequencyto-current Feedback using a Switched-capacitor Structure

## Sangyong Park, Hyuk Ryu, Eun-Taek Sung, and Donghyun Baek

School of Electrical Engineering, Chung-Ang University / Seoul, Republic of Korea

\* Corresponding Author: Donghyun Baek

Received May 28, 2015; Accepted June 10, 2015; Published June 30, 2015

\* Short Paper

**Abstract:** In this letter, we present a new linearization method for a voltage controlled oscillator (VCO)-based quantizer in an analog-to-digital converter (ADC). The nonlinearity of the VCO generates unwanted harmonic spurs and reduces the signal-to-noise and distortion ratio (SNDR) of the VCO-based quantizer. This letter suggests a frequency-to-current feedback method to effectively suppress harmonic distortion. The proposed method decreases the harmonic spurs by more than 53 dB. And a VCO-based quantizer employing the proposed linearization method achieves a high SNDR of 74.1 dB.

Keywords: VCO, Quantizer, Low harmonic distortion, Frequency-to-current feedback

# 1. Introduction

Recently, there are difficulties in voltage-domain circuit design with decreases in supply voltage with complementary metal-oxide semiconductor (CMOS) technology scaling down. But time resolution has improved to under tens of picoseconds in the 90nm CMOS process because the effect of the parasitic component is decreased [1]. Therefore, design of time-based circuits (for example, the frequency-to-digital converter (FDC) or the time-to-digital converter (TDC) using a sub-micron CMOS process, is of great interest.

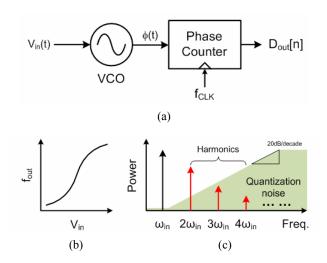

The VCO-based quantizer is usually composed of a VCO and a phase counter, as shown in Fig. 1(a). A VCO generates the phase proportionally by input voltage. The output frequency is quantized by counting edges using a phase counter, such as a FDC. The quantization noise of the previous sample affects that of the current sample, because the VCO generates continuous phase output. So, a VCO-based quantizer can achieve inherent first-order quantization noise shaping [2].

The main design difficulty of a VCO-based quantizer is attributed to the nonlinearity of the VCO gain, as depicted in Fig. 1(b), which generates harmonic spurs as illustrated in Fig. 1(c), and consequently, reduces the SNDR and effective number of bits (ENOB) of a quantizer. Several techniques have been proposed to compensate for this nonlinearity. Kim et al. [2] used a digital reverse-mapping

circuit of the nonlinear VCO gain using an external FPGA at the end of the quantizer. Hamilton et al. [3] and Yoon et al. [4] employed two identical VCO-based quantizers to remove odd harmonic spurs. However, even harmonics still remain. Iwata et al. [5] and Straayer and Perrott [6] employed analog feedback using a digital-to-analog converter (DAC), which needs many complex analog components.

In this paper, we present a simple and effective linearization technique for reducing harmonic distortion of a VCO-based quantizer using frequency-to-current feedback, which can be easily integrated in a small chip area and can suppress all the harmonic spurs.

# 2. Linearized Multi-bit VCO-based Quantizer Design

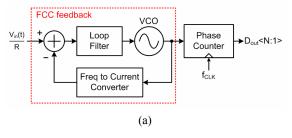

Fig. 2(a) shows a block diagram of the proposed VCO-based quantizer. The frequency-to-current feedback structure for improving the linearity of the VCO is applied. First of all, the phase counter changes the VCO output phase to a digital code at every clock edge. At the same time, the output frequency of the VCO is sampled and is converted to current in the frequency-to-current (FC) converter. The converted current is compared with input current  $V_{in}/R$ . The error current is integrated into the loop

Fig. 1. A conventional VCO-based quantizer (a) Block diagram, (b) Nonlinear VCO gain, (c) Output spectrum.

Fig. 2. The proposed VCO-based quantizer (a) Block diagram, (b) Detailed circuit.

filter. And finally, output voltage of the loop filter controls the VCO.

The detailed circuit is shown in Fig. 2(b). The VCO makes 31 phases in the proposed structure. The phase counter consists of the 31 arrays, and each one is composed of two D flip-flops and a subtractor as the XOR gate. Counting the VCO edge's previous and current clock makes the thermometer 31-bit output data from the difference of the previous and current counting data [2, 6]. Consequently, we achieve the binary five-bit output value from the thermometer 31-bit data using the thermo-tobinary decoder. The switched capacitor circuit, which is driven by one of the 31-phase VCO outputs through the non-overlapping phase generator (NOPG), is employed for frequency-to-current conversion. The switched capacitor acts as a resistor, inversely proportional to the clock frequency, with a value of  $1/(C_1 f_{vco})$ . The net current through the integrating capacitor  $C_2$  should be zero in the

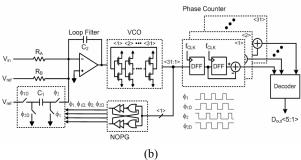

Fig. 3. The nonlinear model of the proposed VCO-based quantizer.

steady state with the FC converter current and the reference current  $V_{ref}/R_B$ . Assuming the operation amplifier is ideal, the node equation can be obtained by applying Kirchhoff's current law with the input current [7].

$$\frac{v_{in} - V_{\text{int}}}{R_A} + \frac{V_{ref} - V_{\text{int}}}{R_B} = f_{vco} \cdot C_1 \left( V_{ref} - V_{\text{int}} \right) \tag{1}$$

The reference voltage  $V_{ref}$  is usually set to  $V_{DD}$ . And if all the circuits are realized differentially,  $V_{int}$  can be set to zero. Then, rearranging the above equation, the VCO output frequency becomes

$$f_{vco} = \frac{1}{R_B C_1} + \frac{v_{in}}{V_{REF}} \frac{1}{R_A C_1} = f_c + \Delta f \cdot v_{in}$$

(2)

where  $f_c$  is the center frequency, and  $\Delta f$  is the tunable frequency range. The center frequency and the tunable range can be adjusted independently by  $R_A$ ,  $R_B$ , and  $C_1$ .

### 3. Nonlinearity Reduction

The relationship between the frequency and the control voltage of a VCO can be simplified in the phase domain, as shown in Fig. 3. The nonlinear relation between the frequency of the VCO and the control voltage can be expressed as:

$$f_{vco} = K_{vco} \cdot v_c + a_2 \cdot v_c^2 + \dots = K_{vco} \cdot v_c + f_{vl}$$

(3)

The first term  $(K_{vco} \cdot v_c)$  represents the linear part; the second and third terms  $(f_{nl})$  designate the nonlinear parts. The nonlinear part generates the harmonic spurs in the output. In the proposed architecture, these harmonic spurs originating from the VCO nonlinearity can be considerably reduced through negative feedback, and the amount of reduction can be estimated by the transfer function between  $\varphi_{vco}$  and  $\varphi_{nl}$ :

$$\left| \frac{\phi_{vco}}{\phi_{nl}} \right| = 20 \cdot \log \left( \frac{f_{f,harm}}{\sqrt{f_{f,harm}^2 + \left(V_{ref} \cdot C_2 \cdot K_{vco}/C_1\right)^2}} \right) \tag{4}$$

where  $f_{f,harm}$  is the harmonic frequency of the input signal,  $f_{vco} = d \varphi_{vco}/dt$ , and  $f_n = d \varphi_n/dt$ . Since the transfer charac-

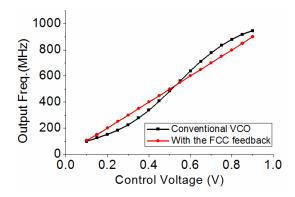

Fig. 4. Simulated output frequencies of the conventional VCO and the one with the FCC feedback vs. control voltage.

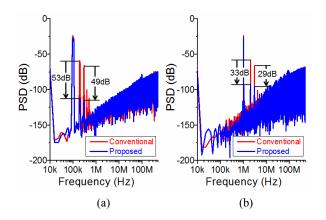

Fig. 5. Simulation result of the proposed VCO-based quantizer using Verilog-A (a)  $f_{\rm in}$  = 100 kHz, (b)  $f_{\rm in}$  = 1 MHz.

teristic is expressed as a high-pass filter, the lower is the applied input frequency of the quantizer, and the higher harmonic reduction is achieved.

#### 4. Simulation Results

The proposed VCO-based quantizer is simulated using Verilog-A, where  $V_{ref}=1$  V,  $f_{clk}=1$  GHz,  $R_A=R_B=20$  k $\Omega$ ,  $C_I=100$  fF, and  $C_2=500$  fF. A center frequency of  $f_c$  is determined by  $1/R_B \cdot C_I=500$  MHz with Eq. (2). A 31-phase ring-type VCO is used with a control voltage range of 0.1-0.9 V. Fig. 4 shows the simulated nonlinear VCO gain with a tuning range of 0.1-0.9 GHz and also the linearized VCO gain after the FCC feedback is applied. The frequency of the linearized VCO is measured at the output of the VCO in front of the phase count. A significant linearity improvement is achieved without changing the original gain.

The output spectrums of the proposed quantizer and conventional quantizer are shown in Fig. 5; 20 dB noise slopes are attributed to the first-order noise shaping characteristics of the phase counter using D flip-flops. As expected, high second and third harmonic spurs appear in the conventional VCO-based quantizer, as shown in Fig. 1(a). However, the harmonic spurs dwindle substantially

Table 1. Summary of the recently reported VCO-based quantizers.

| Name                            | Configuration          | f <sub>clk</sub><br>(MHz) | BW<br>(MHz) | SNR (dB) | SNDR (dB) |

|---------------------------------|------------------------|---------------------------|-------------|----------|-----------|

| Kim et al. [2]                  | Digital<br>Compensator | 500                       | 1           | 68.4     | 62        |

| Yoon et al. [4]                 | Harmonic Cancellation  | 100                       | 5           | 58.2     | 56.5      |

| Straayer,<br>and Perrott<br>[6] | DAC Feedback           | 950                       | 10          | 86       | 72        |

| This Work                       | FCC Feedback           | 1000                      | 5           | 76.52    | 74.1      |

with the proposed FCC feedback applied. Second harmonic spurs decrease by about 53 dB and 33 dB, or more, with input frequencies of 100 kHz and 1 MHz, respectively, and third harmonic spurs suppress roughly more than 49 dB and 29 dB in both frequencies, respectively. The amount of the harmonic reduction is well matched with the expected value from Eq. (4).

Table 1 presents the comparisons of the recently reported VCO-based quantizers. The proposed quantizer shows comparable or superior performance due to the novel switched capacitor linearization technique, despite the simple linearization scheme.

#### 5. Conclusion

A new linearization method for a VCO-based quantizer with low harmonic distortion is proposed. The nonlinearity of the VCO is effectively suppressed with a frequency-to-current feedback (FCC) configuration. Both even and odd harmonic spurs are simultaneously reduced in the proposed VCO-based quantizer. Second harmonic spurs decrease approximately 53 dB and 33 dB more with input frequencies of 100 kHz and 1 MHz, respectively, and third harmonic spurs decrease about 49 dB and 29 dB more in both frequencies. The proposed VCO-based quantizer achieves a high SNDR of 74.1 dB.

### **Acknowledgement**

This research was partly supported by the Industrial Core Technology Development Program (No.10049138) funded by the Ministry of Trade, Industry & Energy and by the Basic Science Research Program through the National Research Foundation of Korea (NRF) funded by the Ministry of Education (No.2013R1A1A2060885).

#### References

[1] Minjae Lee and Asad A. Abidi, "A 9b, 1.25 ps resolution coarse-fine time-to-digital converter in 90 nm CMOS that amplifies a time residue", IEEE J. Solid-State Circuits, vol. 43, no. 4, pp. 769-777, Apr. 2008. Article (CrossRefLink)

- [2] J. Kim, T. Jang, T. Yoon, and S. Cho, "Analysis and design of voltage-controlled oscillator based analogto-digital converter," IEEE Circuits and Syst. I. Regular Papers, vol. 57, no. 1, pp. 18-30, 2010. <u>Article (CrossRefLink)</u>

- [3] J. Hamilton, S. Yan, and T.R. Viswanathan, "A discrete-time input Δ∑ quantizer Architecture using a dual-VCO-based integrator," IEEE Trans. Circuits and Syst. II. Express Briefs, vol. 57, no. 11, pp. 848-852, 2010. Article (CrossRefLink)

- [4] Y. G. Yoon, M. C. Cho, and S. Cho, "A linearization technique for voltage controlled oscillator-based quantizer," in Proc. International SoC Design Conference (ISOCC), 2009, pp. 317-320. <a href="https://example.com/article/Article/CrossRefLink"><u>Article (CrossRefLink)</u></a>

- [5] A. Iwata, N. Sakimura, M. Nagata, and T. Morie, "The architecture of delta sigma analog-to-digital converters using a voltage-controlled oscillator as a multibit quantizer," IEEE Trans. Circuits and Syst. II, Analog and Digital Signal Processing, vol. 46, no.7, pp. 941-945, 1999. <u>Article (CrossRefLink)</u>

- [6] M. Z. Straayer, and M. H. Perrott, "A 12-Bit, 10-MHz bandwidth, continuous-time delta-sigma quantizer with a 5-bit, 950-MS/s VCO-based quantizer," IEEE J. Solid-State Circuits, vol. 43, no. 4, pp. 805-814, 2008. Article (CrossRefLink)

- [7] N. Sasidhar, R. Inti, and P. Hanumolu, "Low-noise self-referenced CMOS oscillator," Electronics letters, vol. 45, no. 18, pp. 920-9212, 2009. <u>Article</u> (CrossRefLink)