# 技術論文

J. of The Korean Society for Aeronautical and Space Sciences 43(7), 641-647(2015)

DOI:http://dx.doi.org/10.5139/JKSAS.2015.43.7.641 ISSN 1225-1348(print), 2287-6871(online)

# 디지털 위성통신중계기시스템에 적합한 다중채널 신호처리 알고리즘 분석

이정섭\*, 홍근표, 진병일

# A Study of multi-channel signal processing algorithm suitable for Digital-transponder

Jung-sub Lee\*, Keun-pyo Hong and Byoung-il Jin Samsung Thales

# **ABSTRACT**

In this paper, Analyzed the multi-channel signal processing algorithms for digital-transponder. To analyze suitable multi-channel signal processing algorithms, compare algorithms about four criteria. Four criteria are as follows, perfect reconstruction, interference rejection, resource usage and power consumption. Analysis for each algorithm in accordance with these four criteria, then propose the multi-channel signal processing algorithms for digital satellite communication system.

# 초 록

본 논문에서 디지털 위성통신중계기시스템에 적합한 다중채널 신호처리 알고리즘을 분석하였다. 위성통신중계기에 적합한 다중채널 신호처리 알고리즘을 찾는데 있어 본 논문에서는 완전복원 성능, 간섭제거시 성능, 알고리즘 별 리소스 사용량 그리고 전력소모예상량 비교 수행하였다. 이 네가지 분석기준에 따른 각 알고리즘별로 분석하여 디지털 위성통신중계기시스템에 적합한 다중채널 신호처리 알고리즘을 선정하고 제안한다.

Key Words: multi-channel signal processing(다중채널 신호처리), Polyphase filterbank (다상필터뱅크), Weighted overlap add(가중오버랩애드), Per Channel(개별 채널처리), Digital-transponder(디지털통신중계기)

## I. 서 론

위성통신기술은 한정된 주파수 자원으로 더 많은 고객에게 양질의 서비스를 제공하기 위하여 많은 기술발전이 이루어지고 있다. 위성시스템은 지형에 영향을 받지 않는 광역성이라는 장점을 가지고 있어 다양한 분야에서 다양한 목적으로

사용 중에 있다. 그 동안에는 우주환경에서 사용 가능한 고성능 집적회로의 부재로 인하여 지상에 서 수신한 신호를 주파수 변환 및 증폭하여 송신 하는 아날로그중계기(Transponder)의 개발이 대 부분이었으나, 최근 우주환경에서 사용가능한 집 적회로가 다양해짐에 따라서 디지털중계기 (Digital Transponder)의 개발이 미국, 영국, 프랑

Accepted: June 30, 2015

† Received : April 21, 2015 Revised : June 23, 2015

<sup>\*</sup> Corresponding author, E-mail: js08.lee@samsung.com

스 등 위성통신시스템을 선도하는 국가에서 개발 및 운용되고 있다. 디지털중계기의 여러 가지 형태 중 본 논문에서는 OBS(On-board Switching) 형태의 수동형 디지털중계기(Digital Transponder)에 적합한 다중채널 신호처리 알고리즘 분석에 대해 연구하였다. 수동형 디지털중계기의 장점은 채널 내의 많은 다중채널 신호들을 개별로 이득조정, 대역간 스위칭 및 간섭신호제거가 가능하기 때문에 한정된 주파수 자원의 효율을 극대화하여 사용할 수 있다는 점이다[1].

다중채널 신호처리 알고리즘은 일반적으로 개별 채널처리(Per channel), 다상필터뱅크(Polyphase filterbank), 가중 오버랩 애드(Weighted overlap add) 등이 많이 사용되어지고 있다. 본 논문에서는 상기 언급된 세 가지 다중채널 신호처리 알고리즘 중 디지털 위성통신중계기 시스템에 적합한 알고리즘을 선택할 수 있도록 분석하였다.

분석하는 기준은 알고리즘의 성능, 간섭신호원 제거 성능, 리소스량 및 전력소모량으로 선정하 였다. 이처럼 분석기준을 선정한 이유는 다음과 같다. 디지털중계기를 통과한 후의 신호의 열화 된 정도를 비교하여 알고리즘의 성능을 확인하고 블록처리방식 알고리즘인 다상필터뱅크 및 가중 오버랩 애드의 완전복원능력을 확인을 위해서다. 그리고 위성통신중계기시스템 특성상 어디서든 재머를 이용한 위성중계기 무력화가 가능하기 때 문에 원하지 않는 간섭신호원 제거성능을 비교하 였다. 또한 위성장비 특성상 수리가 불가능하기 때문에 장비의 신뢰도 또한 매우 중요하여 신뢰 도에 영향을 미치는 알고리즘의 리소스량과 전력 소모량을 비교하였다[2]. 이와 같이 네가지의 분 석기준을 가지고 디지털 위성통신중계기 시스템 에 적합한 알고리즘을 선정하고 제안한다.

# Ⅱ. 본 론

# 2.1 설계요구사항

알고리즘 분석시 기준이 되는 설계 요구사항 은 Table 1과 같이 정의한다.

Table 1. Design specifications

| Channel Bandwidth     | 50MHz                        |

|-----------------------|------------------------------|

| Number of Sub-channel | 25EA                         |

| Minimum resolution    | < 0.5MHz                     |

| Sub-channel Bandwidth | 0.5MHz, 1MHz,<br>2MHz, 4MHz, |

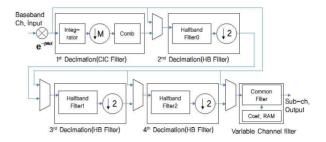

Fig. 1. Channelization block diagram of Per Channel

#### 2.2 알고리즘 구조

#### 2.2.1 개별채널처리(Per Channel) 알고리즘

단일 채널 방식을 동시에 병렬로 구성한 방식으로 전통적인 방법으로 많이 사용되는 알고리즘이다. 일반적으로 유연성이 높으나, 부채널 수에비례하여 연산량이 증가하므로 다수의 채널을 갖는 시스템을 구현할 때는 큰 연산 복잡도를 갖는다. 입력된 광대역신호를 CIC(Cascaded integrator comb filter)필터와 Halfband필터를 다단으로 이용하여 데시메이션을 수행한 뒤 가변채널필터를이용하여 부채널로 분해한 후, Halfband필터와 CIC필터를 다단으로 이용하여 인터폴레이션을수행한 뒤 모든 부채널을 합하여 광대역신호로 재합성한다[3].

본 논문에서 적용한 개별채널처리 알고리즘 구조는 Fig. 1과 같다.

채널화(Channelization)는 원하는 부채널에 대하여 통과대역 신호에 대해 기저대역으로의 주파수 변환을 수행하고, 다단의 데시메이션 구성으로 데시메이션을 수행, 마지막단의 가변계수필터를 통해 부채널 신호에 대한 필터링이 수행된다. 첫단의 데시메이터는 CIC 데시메이션 필터로 구성되어 정수배의 가변률이 가능하고, 2,3,4단은 Halfband필터 기반으로 2/4/8의 가변률을 지원한다.

Fig. 2. De-channelization block diagram of Per channel

역채널화(De-channelization)는 각 부채널에 대하여 4단의 인터폴레이션과 한 번의 주파수변환이 수행된다. 부채널별 다단의 인터폴레이션 구성으로 수행하며 주파수 변환부는 부채널별 기저대역 신호에 대하여 채널 기저대역 신호로 주파수 변환을 수행한다. 1,2,3단은 Halfband 필터 기반으로 2/4/8의 가변율을 지원하며 넷째단은 CIC 인터폴레이션 필터로 구성되어 정수배의 가변율을 가능하게 한다.

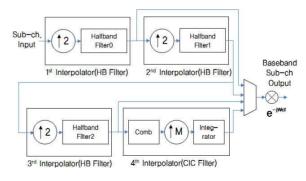

# 2.2.2 다상필터뱅크(Polyphase Filterbank) 알고리즘

블록처리방식인 다상필터뱅크방식은 입력된 광대역신호를 Time-domain 채널화, 다상필터와 DFT(FFT)를 이용하여 최소주파수분해능을 갖는 M개의 단위채널로 동시에 분리한 후, IDFT (IFFT), 다상필터, Time-domain 채널화를 이용하여 광대역신호로 재합성한다. 블록처리방식이여서 채널수에 관계없이 동일한 연산 복잡도를 갖기 때문에 채널 수가 많을 때 효과적이다[4].

블록처리방식이기 때문에 다중채널 신호처리 알고리즘으로 사용하기 위해서는 임의의 대역폭 을 갖는 부채널도 N개의 단위채널을 합성하여 손상없이 복원할 수 있는 완전복원이 가능하여야 한다. 다상필터의 필터계수는 완전복원필터로부 터 추출하여 사용한다. 대표적인 완전 복원 필터 로는 Raised cosine 필터가 있다.

본 논문에서 적용한 다상필터뱅크 알고리즘 구조는 Fig. 3과 같다.

입력된 채널신호에 대하여 1024개로 채널화를 수행 후, 각 부채널마다 다상채널화 필터를 거친후, FFT를 수행한다. FFT는 Pipeline방식으로 구성하여 출력은 각 채널출력을 시분할하여 출력하는 채널화기의 역할을 병행한다. 이렇게 채널화된신호들을 IFFT와 1024개의 다상필터를 사용하여채널화의 역순으로 수행한 후 1024개로 역채널화를 수행하면 역채널화가 완료된다. 이 때 다상필터뱅크는 8192tap의 Raised cosine 필터계수를 적용하였고, 각 다상필터는 8tap으로 구성하였다.

Fig. 3. Block diagram of polyphase filterbank

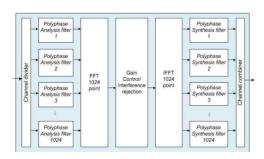

Fig. 4. Block diagram of weighted overlap add

# 2.2.3 가중 오버랩 애드(Weighted overlap add) 알고리즘

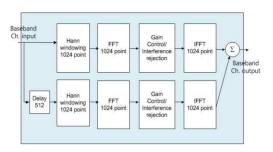

블록처리방식인 가중 오버랩 애드 방식은 입력된 광대역신호를 Window와 DFT(FFT)를 이용하여 최소주파수분해능을 갖는 M개의 단위채널로 동시에 분리한 후, IDFT(IFFT), Window를이용하여 광대역신호로 재합성한다. 블록처리방식이여서 채널수에 관계없이 동일한 연산 복잡도를 갖기 때문에 채널 수가 많을 때 효과적이다. 다상필터뱅크와 마찬가지로 블록처리방식이기 때문에 완전복원이 가능한 Window를 사용하여야 완전복원이 가능하다. 완전복원이 가능하도록 Window의 계수는 Hann Window (Raised-cosine window)를 사용한다. 본 논문에서 적용한 가중 오버랩 애드 알고리즘 구조는 Fig. 4와 같다[5].

# 2.3 알고리즘 시뮬레이션 및 분석

#### 2.3.1 알고리즘 성능 및 완전복원능력

알고리즘 성능을 분석시 Table 2와 같은 기준으로 시뮬레이션을 수행하였으며, EVM(Error Vector Magnitude)를 이용하여 성능을 확인하였다.

Table 3의 결과와 같이 모든 알고리즘에서 다중채널 신호처리 알고리즘 입력대비 출력의 EVM이 1%이내의 우수한 성능을 보였으며 다상 필터뱅크가 다소 우수한 성능을 보였다.

개별채널(Per channel)에서 부채널의 대역폭이 증가함에 따라 성능이 열화되는 이유는 대역폭이

Table 2. Simulation conditions

| Modulation        | QPSK(uncoded)               |

|-------------------|-----------------------------|

| Channel Bandwidth | 50MHz                       |

| Subch Bandwidth   | 0.5MHz, 1MHz,<br>2MHz, 4MHz |

| Subch guardband   | 20% of Bandwidth            |

| Roll-off factor   | 0.25                        |

| Interference      | SIR= -10dB, Single-tone     |

Table 3. Perfect reconstruction result (EVM)

| Algorithm               | Sub    | ch Band | dwidth [N | lHz]   |

|-------------------------|--------|---------|-----------|--------|

| Algoritiin              | 0.5MHz | 1MHz    | 2MHz      | 4MHz   |

| Per channel             | 0.420% | 0.501%  | 0.909%    | 1.159% |

| Polyphase<br>filterbank | 0.252% | 0.262%  | 0.294%    | 0.286% |

| Weighted overlap add    | 0.346% | 0.344%  | 0.344%    | 0.341% |

증가함에 따라 CIC 필터의 특성으로 인하여 통과대역내 감쇄현상이 발생하기 때문이다. 시뮬레이션 시에는 CIC 보상필터는 적용하지 않았고, 만약 적용한다면 대역폭이 증가함에 따라 성능이열화되는 현상은 최소화 할 수 있다.

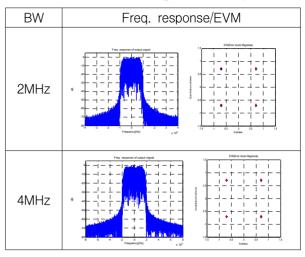

# 2.3.1.1 개별채널처리(Per Channel) 알고리즘 성능

Table 4. EVM of Per channel

| BW   | Freq. response/EVM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2MHz | Tax   square of stand ages                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 4MHz | Page   September of September |

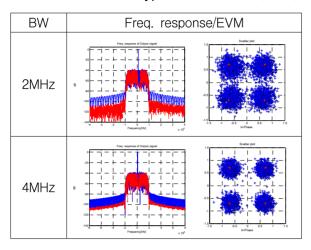

# 2.3.1.2 다상필터뱅크(Polyphase Filterbank) 알고리즘 성능

Table 5. EVM of Polyphase filterbank

| BW   | Freq. response/EVM                                                   |

|------|----------------------------------------------------------------------|

| 2MHz | Freq. supress of Oxford Appel  1.5  1.5  1.5  1.5  1.5  1.5  1.5  1. |

| 4MHz | From response of Shader signal    1                                  |

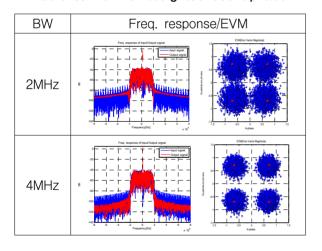

# 2.3.1.3 가중오버랩애드(Weighted overlap add) 알고리즘 성능

Table 6. EVM of Weighted overlap add

#### 2.3.2 간섭신호 제거 후 성능

간섭신호 제거는 FFT(Fast Fourier Transform) 후 FFT Bin의 널링(Nulling)을 통하여 제거하는 방법을 적용하였다. FFT 블록이 포함되는 알고리 즘에서는 매우 낮은 복잡도로 구현이 가능하다 [6].

Table 2와 같이 SIR(Signal to Interference Ratio)= -10dB의 톤형태의 간섭신호 조건에서 시뮬레이션을 수행하였으며, 간섭이 인가된 신호를 수신하여 간섭을 제거한 후의 데이터 EVM을 관찰하였다.

시뮬레이션 결과는 Table 7에서와 같이 다상 필터뱅크가 비교적 우수한 성능을 보였으며, 대 역폭이 클수록 대역폭 대비 널링되는 비율이 줄 어들어 EVM 성능이 좋아짐을 확인하였다.

# 2.3.2.1 개별채널처리(Per Channel) 알고리즘 간섭제거 성능

개별채널처리(Per channel) 알고리즘은 널링방

Table 7. Interference rejection result

|                         | Sub    | ch Band | dwidth [N | 1Hz]   |

|-------------------------|--------|---------|-----------|--------|

| Algorithm               | 0.5MHz |         | 2MHz      | 4MHz   |

| Per channel             | -      | -       | -         | -      |

| Polyphase<br>filterbank | 56.50% | 48.91%  | 33.95%    | 23.54% |

| Weighted overlap add    | 75.62% | 57.43%  | 37.59%    | 25.58% |

법으로 채널 내 인가된 간섭제거가 불가하여 별 도구현이 필요하다.

# 2.3.2.2 다상필터뱅크(Polyphase Filterbank) 알고리즘 간섭제거 성능

Table 8. EVM of Polyphase filterbank (EVM)

# 2.3.2.3 가중오버랩매드(Weighted overlap add) 알고리즘 간섭제거 성능

Table 9. EVM of Weighted overlap add

#### 2.4 리소스량

알고리즘의 리소스량은 ISE Design Suite 프로 그램을 이용하여 Xilinx社에서 최근에 내놓은 우 주급 FPGA(Field Program -mable Gate Array) 인 Virtex5-FX130소자를 이용하여 25개 부채널기 준으로 비교하였다[7]. (단, Per Channel은 Virtex5-FX130 1개 소자에 25개 부채널이 구현이 안되어 5개 부채널 기준으로 하였음)

각 알고리즘을 Virtex5-FX130의 FPGA에 구현 시 소요되는 리소스를 비교해보니 다상필터뱅크 의 리소스 사용량이 Register, LUT(Look Up

| Device Utilizatio         | n Summa | ry        |             |

|---------------------------|---------|-----------|-------------|

| Slice Logic Utilization   | Used    | Available | Utilization |

| Number of Slice Registers | 63,804  | 81,920    | 77%         |

| Number of Slice LUTs      | 56,278  | 81,920    | 68%         |

| Number of bonded          | 85      | 840       | 10%         |

| Total Memory used (KB)    | 1,350   | 10,728    | 12%         |

| Number of BUFG/BUFGCTRLs  | 9       | 32        | 28%         |

| Number of DCM_ADVs        | 1       | 12        | 8%          |

| Number of DSP48Es         | 140     | 320       | 43%         |

Fig. 5. Per Channel resource(5EA Sub-ch)

| Device Utilization        | on Summan | У         |             |

|---------------------------|-----------|-----------|-------------|

| Slice Logic Utilization   | Used      | Available | Utilization |

| Number of Slice Registers | 16,948    | 81,920    | 20%         |

| Number of Slice LUTs      | 15,219    | 81,920    | 18%         |

| Number of bonded          | 60        | 840       | 7%          |

| Total Memory used (KB)    | 1,620     | 10,728    | 15%         |

| Number of BUFG/BUFGCTRLs  | 3         | 32        | 9%          |

| Number of DCM_ADVs        | 1         | 12        | 8%          |

| Number of DSP48Es         | 118       | 320       | 36%         |

Fig. 6. Polyphase filterbank resource

| Device Utiliza            | ation Summa | ıry       |             |

|---------------------------|-------------|-----------|-------------|

| Slice Logic Utilization   | Used        | Available | Utilization |

| Number of Slice Registers | 26,228      | 81,920    | 32%         |

| Number of Slice LUTs      | 21,323      | 81,920    | 26%         |

| Number of bonded          | 60          | 840       | 7%          |

| Total Memory used (KB)    | 648         | 10,728    | 6%          |

| Number of BUFG/BUFGCTRLs  | 4           | 32        | 12%         |

| Number of DCM_ADVs        | 1           | 12        | 8%          |

| Number of DSP48Es         | 112         | 320       | 35%         |

Fig. 7. Weighted overlap Add resource

Table 10. Resource summary

| Algorithm   | Register | LUT    | DSP   |

|-------------|----------|--------|-------|

| Per Channel | 63,804   | 56,278 | 140   |

| (5 Sub-ch)  | (77%)    | (68%)  | (43%) |

| Polyphase   | 16,948   | 15,219 | 118   |

| filterbank  | (20%)    | (15%)  | (36%) |

| Weighted    | 26,228   | 21,323 | 112   |

| overlap Add | (32%)    | (26%)  | (35%) |

Table)는 가장 적게 사용되었고 가중오버랩은 DSP의 사용량이 가장 적었다.

개별채널처리방식은 FPGA 1개에 25개 부채널 이 구현되지 않아 5개 부채널 기준으로 구현하여리소스 사용량을 확인하였으며 타 알고리즘 대비 많은 리소스를 사용함을 보였다.

#### 2.5 소모전력

XPA(Xilinx Power Analyzer) 프로그램을 이용

| Name .              | Value            | Used        | Total Avrailable | Utilization (%) |

|---------------------|------------------|-------------|------------------|-----------------|

| District            | 1,20951 (W)      | 19<br>44074 | -                | 1-              |

| Logic               | 0.14755 (W)      | 44074       | 81920            | 53.8            |

| Signals             | 0.19770 (W)      | 10576       |                  | -               |

| 10 (                | 0.16007 (W)      | 70          | 942              | 7.4             |

| BRAMI               | 0.22140 (W)      | 36          | 298              | (0.0            |

| DON                 | 0.10760 (W)      | l.co.       | 12               | 8.3             |

| DSP1                | 0.06801 (W)      | 140         | 320              | 431             |

| Total Quescent Powe | 2.26209 (W)      |             |                  |                 |

| Total Dynamic Power | 2.04641 (W)      |             |                  |                 |

| Total Power         | 4.30850 (W)      |             |                  |                 |

| unction Temp        | 58.6 (degrees C) |             |                  |                 |

Fig. 8. Per Channel, Power consumption (5EA Subch)

| Name                | Value            | Used  | Total Available | Utilization (%) |

|---------------------|------------------|-------|-----------------|-----------------|

| Docks               | 0.95041 (W)      | 2     | F               | H               |

| Logic               | 0.04426 (W)      | 12733 | 81920           | 15.5            |

| Signals             | 0.13094 (W)      | 29099 |                 | -               |

| Ot .                | 3.16007 (W)      | 45    | 942             | 4.8             |

| RAM:                | 0.29854 (W)      | 46    | 298             | 0.0             |

| DOM:                |                  | 1     | 12              | 8.3             |

| DSPs                | 0.06615 (W)      | 118   | 320             | 36.9            |

| Total Quescent Powe | 2.16272 (W)      |       | -               |                 |

| Total Dynamic Power | 1.30763 (W)      |       |                 |                 |

| Total Form          | 3.47035 (W)      |       |                 |                 |

| Junction Temp       | 52.1 (degrees C) |       |                 |                 |

Fig. 9. Polyphase filterbank, Power consumption

| Name                | Value            | Used  | Total Available | Utilization (%) |

|---------------------|------------------|-------|-----------------|-----------------|

| Dooks               | 0.58310 (W)      | 2     | -               | 1-              |

| ogc                 | 0.05598 (W)      | 13897 | 81920           | 17.0            |

| Signals             | 0.10412.EV3      | 36514 | -               | 460             |

| D1                  | 0.16007 (W)      | 45    | 942             | 4.8             |

| BRAMI               | 0 12207 (W)      | 13    | 290             | 6.4             |

| DCMI                | 0.10760 (W)      | t     | 320             | 83              |

| DSP1                | 0.04314 (W)      | 112   | 320             | 25.0            |

| Total Quescent Pove | 2.44260 (W)      |       |                 | _               |

| Total Dynamic Power | 1.12474 (W)      |       |                 |                 |

| Total Power         | 3.56734 (W)      |       |                 |                 |

| Junction Temp       | 57.5 (degrees C) |       |                 |                 |

Fig. 10. Weighted overlap and Add, Power consumption

Table 11. Power consumption summary

| Algorithm                 | Power consumption | Junction<br>temperature |

|---------------------------|-------------------|-------------------------|

| Per Channel<br>(5 Sub-ch) | 4.30W             | 58.6℃                   |

| Polyphase<br>filterbank   | 3.47W             | 52.1℃                   |

| Weighted overlap Add      | 3.56W             | 57.5℃                   |

하여 FPGA의 전력소모 및 접합온도를 비교하였다. (단, 개별채널처리(Per Channel)는 Virtex5-FX130 1개 소자에 구현이 안되어 5개 부채널 기준으로 하였고, 상온는 25도임)

각 알고리즘별 XPA를 이용하여 FPGA의 예상 전력소모를 비교해본 결과 다상필터뱅크의 전력 소모량이 가장 적었으며 예측한 접합온도도 가장 낮음을 확인하였다.

## Ⅲ. 결 론

차세대 위성통신중계기는 한정된 주파수 자원의 활용을 극대화 하는 OBS형태의 수동형 디지털중계기(Digital Transponder)가 위성시스템 선도 국가에서 개발 및 운용되고 있다. 이와 같은 OBS 기능을 탑재한 통신위성을 개발시 다중채널신호처리 알고리즘을 선정이 매우 중요하다.

본 논문에서 디지털중계기에 적용할 다중채널 신호처리 알고리즘의 적합성을 분석해 보았다. 알고리즘 분석에 있어 중요하다고 판단되는 성 능, 간섭신호 제거후 성능, FPGA 리소스량 그리 고 예상전력소모량을 분석해본 결과 다상필터뱅 크와 가중오버랩애드가 개별채널처리에 비교하여 월등한 성능을 나타 냈으며, 다상필터뱅크가 가 중오버랩애드보다 DSP 리소스 사용량을 제외한 대부분의 지표에서 다소 우수한 성능을 보였다.

본 논문의 결과로 OBS 형태의 수동형 디지털 중계기에 적합한 다중채널 신호처리 알고리즘은 다상필터뱅크(Polyphase filterbank)로 분석되었다.

#### Reference

- 1) D. I. Lee, K. K. Kim, K. H. Lee "Digital Communication Satellite Transponder Technology", KICS Vol.26, No.6, 2009. pp.37~44.

- 2) J. H. Park, H. S. Kim, H. S. Ko, B. C. Jin and H. K. Seo "Experimental Verification of Heat Sink for FPGA Thermal Control", *KSAS Journal* Vol.42, No.9, 2014, pp789~794.

- 3) K. H. Lee "Efficient architectures of channelizer/dechannelizer for SDR systems," Yonsei university. 2005.

- 4) R. E. Crochiere and L. R. Rabiner, *Multirate Digital Signal Processing, Prentice-Hall,* 1983.

- 5) J. H. Yoo, H. S. Kim, K. H. Lee, J. S. Lee and J. H. Chung "Time domain multiple-channel signal processing method for converting the variable frequency band," *KICS* Vol.35, No.1, Jan. 2010.

- 6) W. W. Jones, and K. R. Jones, "Narrow

band interference suppression using filter-bank analysis/synthesis techniques," IEEE MILCOM '92 Conference, Vol. 3, Oct. 1992, pp.898-902.

7) Xilinx, Radiation-Hardened Space-Grade Virtex-5QV Family Overview(2012), Retrieved Jan.17, 2013, from http://www.xilinx.com