# GaN HEMT Die를 이용한 S-대역 내부 정합형 고효율 고출력 증폭기

# S-Band Internally-Matched High Efficiency and High Power Amplifier Using GaN HEMT Die

김상훈·최진주·최길웅\*·김형주\*

Sang-Hoon Kim · Jin-Joo Choi · Gil-Wong Choi\* · Hyoung-Joo Kim\*

요 약

본 논문은 GaN(Gallium Nitride) HEMT(High Electron Mobility Transistor) die를 이용하여 S-대역 내부 정합형 전력 증폭기 설계, 제작 그리고 실험 결과에 대해 기술하였다. S-대역 내부 정합형 전력 증폭기를 설계하기 위하여 고유전율을 가지는 기판과 알루미나 기판을 이용하여 입/출력단 정합 회로를 설계 및 제작하였다. 측정 결과로는 펄스 모드로 동작시켰을 때 3 GHz에서 55.4 dBm의 출력 전력, 78 % 드레인 효율 그리고 11 dB의 전력 이득을 얻었다.

#### **Abstract**

This paper presents the design, fabrication and measurement results of a S-band internally-matched power amplifier using Gallium Nitride High Electron Mobility Transistor(GaN HEMT) die. In order to fabricate the S-band internally-matched power amplifier, a high dielectric substrate and alumina were used for input/output matching circuits. The measured output power is 55.4 dBm, the drain efficiency is 78 % and the power gain is 11 dB under pulse operation at the frequency of 3 GHz.

Key words: S-Band, GaN HEMT Die, Internally-Matched, Power Amplifier

# T. 서 론

S-대역 고출력 전력 증폭기는 다양한 무선 통신 시스템에 사용되어지고 있다. 최근 반도체 소자의 기술 발전으로 레이더 송신기의 전력 증폭기가 반도체 소자를 이용한 반도체 전력 증폭기(Solid-State Power Amplifier: SSPA)로 교체가 되고 있다. 이러한 반도체 전력 증폭기는 신뢰성, 크기의 소형화 및 저전압 동작 등과 같은 장점

이 있다<sup>[1]</sup>. 이러한 장점들로 인하여 SSPA를 이용한 레이더가 개발이 되어 현장에 배치되어 사용되고 있다. 특히고출력 특성에 적합한 GaN HEMT bare chip을 이용하여 고출력 반도체 전력 증폭기가 활발하게 연구되고 있다<sup>[2]~[8]</sup>

본 논문에서는 S-대역 고효율 고출력 반도체 전력 증폭기를 고유전율 기판 및 알루미나 기판을 이용하여 입/출력단 내부 정합 회로를 설계하였고, 실험 결과를 얻은

<sup>「</sup>이 연구는 2014학년도 광운대학교 교내 연구비의 지원으로 연구되었음.」

광운대학교 전파공학과(Department of Wireless Communications Engineering, Kwangwoon University)

<sup>\*</sup>삼성탈레스(Samsung Thales)

<sup>·</sup> Manuscript received April 9, 2015; Revised June 8, 2015; Accepted June 9, 2015. (ID No. 20150409-026)

<sup>·</sup> Corresponding Author: Jin-Joo Choi (e-mail: jinchoi@kw.ac.kr)

것에 대해 기술하였다.

### Ⅱ. 설계 및 제작

S-대역 내부 정합형 전력 증폭기 설계를 위하여 Cree사 120 W급 CGH60120D GaN HEMT die를 선정하였다. 그림 1은 본 논문에 사용되어진 GaN HEMT die의 사진을 나타 낸다.

표 1은 Cree사 CGH60120D의 특성을 나타낸다. DC에 서부터 6 GHz까지 사용이 가능하며, 드레인 전압이 28 V일 때 4 GHz의 주파수에서 120 W의 포화 출력 전력, 13 dB의 소신호 이득과 65 %의 드레인 효율을 낼 수 있다고 데이터 시트상에 명시되어 있다.

설계는 Agilent사 Advanced Design System(ADS)을 사용하여 진행하였다. 우선, 소자의 바이어스 조건과 설계 주파수 대역에서 입/출력단 최적의 임피던스를 찾기 위해Cree 사에서 제공해준 비선형 모델과 ADS 시뮬레이션 코드를 이용하여 소스/로드-풀 시뮬레이션을 수행하였다. 300 W이상의 전력을 얻기 위해 CGH60120D 소자를 병렬적으로 연결하였고, Cree사에서 제공해준 비선형 모델의 유효한 드레인 전압 범위 28 V에서 48 V내에서 시뮬레이션을

그림 1. Cree사 GaN HEMT die CGH60120D 형상

Fig. 1. GaN HEMT die Cree's CGH60120D.

표 1. CGH60120D 소자의 제원 Table 1. Specification of CGH60120D.

| 성능 변수     | 잢                       |

|-----------|-------------------------|

| 사용 가능 주파수 | DC-6 GHz                |

| 포화 출력 전력  | 120 W @ 4 GHz           |

| 소신호 이득    | 13 dB @ 4 GHz           |

| 드레인 효율    | 65 % @ P <sub>sat</sub> |

| 드레인 전압    | 28 V                    |

| 크기        | 5.26×0.92×0.10 mm       |

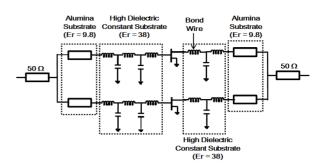

그림 2. 내부 정합 회로 구성도

Fig. 2. Schematic of internally matched circuit.

진행하여 최적의 입/출력 임피던스를 추출하였다. 시뮬레이션에서 얻은 입/출력 임피던스 결과는 2.9 GHz에서 드레인 전압 42 V, 바이어스 전류가 500 mA일 때의 최적의 소스 임피던스는 0.52+j0.09  $\Omega$ 이고, 로드 임피던스는 1.65+j1.15  $\Omega$ 이다. 단일 소자를 이용하여 ADS 소스/로드풀 시뮬레이션에서 얻은 결과를 바탕으로 2개의 소자를 병렬적으로 배치하여 그림 2와 같은 구성도를 가지는 내부 정합형 전력 증폭기를 설계하였다.

GaN HEMT Die를 이용하여 정합 회로 설계를 하기 위 한 방법에는 소자로부터 직접 본딩 와이어를 연결하는 방법, Shunt-C를 사용하는 방법과 Shunt-L을 이용하여 정 합 회로를 설계하는 방법이 있다<sup>14]</sup>. GaN HEMT Die에서 바로 알루미나 기판을 이용한 정합 회로에 연결을 했을 경우에는 조립이 간단하고 소형화 시킬 수 있는 장점이 있는 반면에 대역폭 확보가 힘들다는 단점이 있다. 그리 고 Shunt-L을 이용하는 방법은 본딩 와이어를 소자로부터 정합 회로 기판에 연결하고, 또 다른 본딩 와이어는 소자 로부터 DC block 커패시터로 연결하는 방법이다. 이 방법 은 실험 시 튜닝(tuning)의 여지가 가장 높은 반면에, 실제 로 구현하기기 힘들다는 단점이 있다. 그리하여 본 논문 에서는 구현의 용이성 및 대역폭의 확보를 위해 Shunt-C 를 이용한 정합 회로를 구현하였다. 그림 2에서 확인할 수 있듯이, 내부 정합형 전력 증폭기는 크게 3단으로 나 눌 수 있다. 첫 번째 단은 Shunt-C 구현함에 있어 사이즈 측면에서의 단점을 극복하기 위해 고유전율 기판( $\varepsilon_r$ =38) 을 이용하여 설계한 부분과, 본딩 와이어의 높이와 길이 를 조절을 통한 인덕턴스 성분으로 정합 회로를 설계한

부분이다. 두 번째 단은 알루미나 기판을 이용하여 이중 패드를 갖는 구조로 정합 회로를 설계하였다. 여기서 이중 패드 구조는 소자에서 발생되는 전류 분포를 균등하게 가져가기 위하여 패드를 이중으로 나눠서 설계를 진행한 부분이다. 그리고 마지막으로 세 번째 단은 전력 증폭기 구동을 위한 50 Ohm 바이어스 회로 부분이다. 본 논문에 사용된 금 와이어의 직경은 2 mils이고, 고유전율 기판( $\varepsilon$ ,=38) 회로는 미국 Applied Thin-film Products(ATP) 사에서 제작하였으며, 병렬 구조로 되어있는 입/출력단정합 회로의 분배 및 결합 구조는 알루미나 기판( $\varepsilon$ ,=9.8)

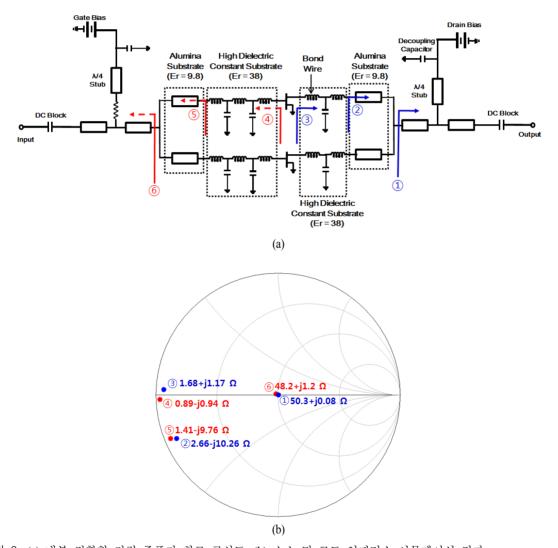

을 이용하여 설계 및 제작하였다. 그림 3(a)는 설계된 내부 정합형 전력 증폭기 회로 구성도를 나타내고, 그림 3(b)는 ADS를 이용하여 그림 3(a)에서 표시한 각 단에서의 바라보는 소스 및 로드 임피던스의 위치를 보여준다. 설계 결과, 2.9 GHz에서의 소스 임피던스는 0.89 — j0.94 요이고, 로드 임피던스는 1.68+j1.17 요이다. 앞에서 언급하였듯이, ADS 소스/로드- 풀 코드를 통해 얻어낸 소스 및로드 임피던스와 완벽하게 일치하지는 않지만, 소스/로드-풀 시뮬레이션 코드에서 얻은 임피던스 점을 기반으로하여 최적의 결과를 얻기 위하여 시뮬레이션에서 얻은

그림 3. (a) 내부 정합형 전력 증폭기 회로 구성도, (b) 소스 및 로드 임피던스 시뮬레이션 결과

Fig. 3. (a) Circuit of the internally matched power amplifier, (b) The simulation results of source & load impedance.

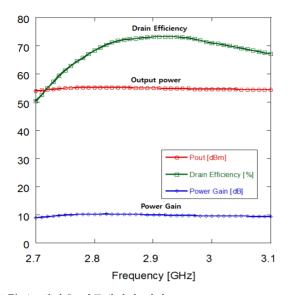

그림 4. 대신호 시뮬레이션 결과(ADS) Fig. 4. The simulation results of the large signal(ADS).

임피던스 지점 근방에서 최적의 임피던스를 가지는 입출력 정합 회로를 설계하였다. 설계되어진 입출력 정합 회로를 바탕으로 ADS 시뮬레이션 코드를 통해 대신호 시뮬레이션을 진행하였다. 그 결과, 그림 4와 같이 2.7 GHz에서 3.1 GHz 주파수 대역 내에서 최대 55.22 dBm 출력전력, 10.2 dB 전력 이득 및 73 %의 드레인 효율을 얻을수 있었다.

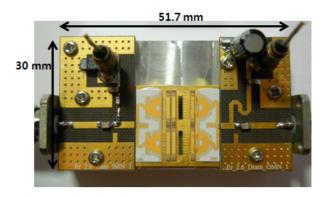

그림 5는 실제 제작된 전력 증폭기이다. 제작된 입/출력단 정합 회로 기판은 서로 다른 3가지 기판으로 나눠서 제작이 되었다. 내부 정합 회로는 유전율이 38인 고유전율 기판과 유전율이 9.8인 알루미나 기판을 사용하여 제작하였고, 기판 두께는 10 mils이다. 그리고 라인 폭과 길이를 변화시킬 수 있는 튜닝 패드를 설계하여 제작하였다. 마지막으로 50음 바이어스 회로는 유전율이 2.6인 TACONIC사 TLX-7 기판을 이용하여 설계 및 제작을 하였다. 전력 증폭기에 사용된 캐리어는 GaN bare die에서 발생하는 열을 효과적으로 배출하기 위해 15:85 % 비율로 합금된 CuW 로 제작되었으며, 표면 처리는 GaN bare die의 유테틱 본딩을 위해 소프트 금도금 처리를 하였다. 그리고 GaN bare die는 90:10 % 비율로 합금된 AuSn을 이용하여 제작된 캐리어에 유테틱 본딩 작업을 통해 조립하였고, GaN bare chip과 입출력단 정합 회로와의 연결을 위

그림 5. 제작된 내부 정합형 전력 증폭기 사진 Fig. 5. The photograph of the fabricated internally man

Fig. 5. The photograph of the fabricated internally matched power amplifier.

해 2 mils의 직경을 가지는 금 와이어를 이용하여 와이어 본딩 작업을 하였다. 그림 1에서 보듯이, 게이트단과 드 레인단에 각각 8개의 패드가 있고, 각 패드에 1개씩 와이 어 본딩을 하여 총 8개를 연결하였다.

## Ⅲ. 측정 결과

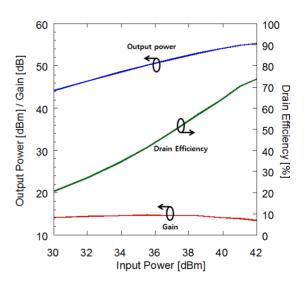

그림 6은 제작된 내부 정합형 전력 증폭기의 입력 전력에 따른 출력 전력, 전력 이득 및 드레인 효율 측정 결과

그림 6. 입력 전력에 따른 S-대역 내부 정항협 전력 증폭 기 측정 결과

Fig. 6. Measured results of S-band internally matched power amplifier as a function of input power.

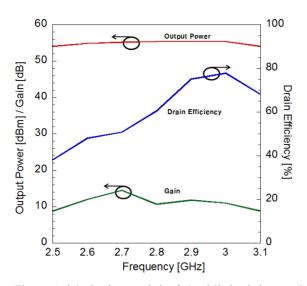

그림 7. 주파수에 따른 S-대역 내부 정합형 전력 증폭기 측정 결과

Fig. 7. Measured results of S-band internally matched power amplifier as a function of frequency.

표 2. S-대역 내부 정합형 GaN 전력 증폭기 성능 비교 Table 2. Performance comparison of S-band internally matched GaN power amplifier.

| 주파수       | 최대 출력  | 효율   | 이득   | 드레인 전압 | 참고문헌     |

|-----------|--------|------|------|--------|----------|

| [GHz]     | 전력 [W] | [%]  | [dB] | [V]    | 召上世인     |

| 2.11~2.17 | 250    | 70   | 13   | 50     | [2]      |

| 2.14~2.5  | 290    | 58.9 | 12   | 48     | [3]      |

| 2.7~3.1   | 249    | 61   | 11.9 | 28     | [4], [6] |

| 2.9~3.5   | 446    | 55.5 | 12   | 65     | [5]      |

| 3.1~3.5   | 250    | 60   | 12.1 | 28     | [4], [7] |

| 3.3~3.6   | 550    | 66   | 12.5 | 55     | [8]      |

| 2.5~3.1   | 346    | 78   | 11   | 42     | 본 논문     |

를 보여준다. 실험 조건은 42 V의 드레인 전압과 -3.35 V의 게이트 전압을 갖는 Class AB 바이어스 조건에서 전력 증폭기를 구동시켰고, 입/출력단은 50 Ohm으로 정합되어진 바이어스 회로를 포함하였다. 전력 증폭기 측정에 사용한 입력 신호는 Agilent사 81110A를 사용하여 펄스폭  $10~\mu s$ , 듀티 사이클 1~% 펄스 조건에서 측정하였다. 그림 6에서 확인할 수 있듯이, 주파수 2.9 GHz에서 55.4 dBm의 출력전력, 75~%의 드레인 효율 및 11.8 dB의 전력 이득을

얻었다. 제작된 전력 증폭기의 주파수 응답 특성은 그림 7에 나타내었다. 2.5 GHz에서 3.1 GHz의 대역에서 54 dBm 이상의 출력 전력, 9 dB 이상의 전력 이득과 최대 78 %의 드레인 효율을 얻었다.

S-대역 내부 정합형 전력 증폭기 특성을 본 논문과 비교를 위해 표 2에 나타내었다. 표 2에 나타난 결과는 펄스측정 결과이며, 표 2에서 명시된 주파수 대역 내에서 최대 출력 출력이 나오는 주파수 지점에서 최대 효율 특성을 나타내는 결과를 보여주고 있는데, 참고문헌 [8]에서만 3.55 GHz에서 521 W의 출력 전력을 낼 때 최대 효율72.4%의 드레인 효율을 나타낸다고 명시되어 있다. 본논문은 비교 대상들에 비해 최대 효율 특성이 우수하다.

### Ⅳ. 결 론

본 연구에서는 GaN bare die를 이용하여 S-대역 내부 정합형 전력 증폭기를 설계 및 제작하였다. 전력 증폭기측정은 펄스 모드로 측정을 하였다. 측정 결과로는 3 GHz에서 55.4 dBm의 출력 전력, 78 % 드레인 효율 및 11 dB전력 이득을 얻었다. 본 논문의 결과는 효율 측면에서 S-대역 내부 정합형 GaN 전력 증폭기 타 제품보다 우수한특성을 보인다. 향후 본 논문에서 설계 및 제작된 연구를기반으로 패키지화시키는 연구를 지속적으로 이루어져야 할 것으로 여겨진다.

#### References

- [1] Aethercomm, "Gallium Nitride(GaN) microwave transistor technology for radar applications", *Microwave Journal*, vol. 51, no. 1, p. 106, Jan. 2008.

- [2] Isao Takenka, Kazunori Asano, Shinnosuke Takahashi, Yasuhiro Murase, Yuji Ando, Hidemasa Takahashi, and Chiaki Sasaoka, "High-efficiency and high power microwave amplifier using GaN-on-Si FET with improves high temperature operation characteristics", *IEEE Trans. Microw. Theory Tech.*, vol. 62, no. 3, pp. 502-512, Mar. 2014.

- [3] K. Krishnamurthy, M. J. Poulton, J. Martin, R. Vetury, J. D. Brown, and J. B. Shealy, "A 250 W S-band GaN

- HEMT amplifier", Compound Semiconductor Integrated Circuit Symposium, pp. 1-4, Oct. 2007.

- [4] Simon M. Wood, Ulf Andre, Bradley J. Millon, and Jim Milligan, "Hybrid and monolithic GaN power transistors for high power S-band radar applications", *Microwave Integrated Circuits Conference(EuMIC)*, pp. 421-424, Oct. 2012.

- [5] K. Krishnamurthy, J. Martin, B. Landberg, R. Vetury, and M. J. Poulton, "Wideband 400 W pulsed power amplifiers", *Microwave Symposium Digest*, 2008 IEEE MTT-S International, pp. 303-306, Jun. 2008.

- [6] CGH31240F, "240 W, 2,700~3,100 MHz, 50-ohm input/ output matched, GaN HEMT for S-band radar systems", *Cree*, Available http://cree.com

- [7] CGH35240F, "240 W, 3,100~3,500 MHz, 50-ohm input/output matched, GaN HEMT for S-band radar systems", *Cree*, Available http://cree.com

- [8] Y. -F. Wu, S. M. Wood, R. P. Smith, S. Sheppard, S. T. Allen, P. Parikh, and J. Milligan, "An interanlly-matched GaN HEMT amplifier with 550-watt peak power at 3.5 GHz", *Electron Devices Meeting*, 2006. IEDM, pp. 1-3, Dec. 2006.

#### 김 상 훈

2009년 2월: 광운대학교 전파공학과 (공학 사)

2009년 9월~현재: 광운대학교 전파공학 과 석박사통합과정

[주 관심분야] RF 회로 설계, 고출력 증폭 기, TRM 등

# 최 길 웅

2002년 2월: 광운대학교 전자공학부 (공학 사)

2006년 2월: 광운대학교 전파공학과 (공학 석사)

2011년 2월: 광운대학교 전파공학과 (공학 박사)

2011년 3월~현재: 삼성탈레스 ISR · PGM

연구소 위성·전자전체계그룹 전문연구원 [주 관심분야] RF 회로 설계, 능동 위상 배열 시스템 등

#### 최 진 주

1983년 8월: 서울대학교 물리교육학과 (이 학사)

1985년 8월: 미국 Georgia State University 물리학과 (이학석사)

1991년 8월: 미국 University of Michigan 핵공학과 (공학박사)

1991년 5월~1997년 8월: 미국 해군연구

소(NRL) 연구원

1997년 9월~현재: 광운대학교 전자융합공학과 교수 [주 관심분야] RF 회로 설계, 고출력 증폭기, Vacuum Tube Amplifier 등

#### 김 형 주

전체계그룹 수석연구원

1989년 2월: 광운대학교 전자통신공학과 (공학사)

1992년 2월: 성균관대학교 전자공학과 (공 학석사)

1989년 3월~1998년 2월: 삼성전자 연구 원

■ 1998년 3월~2006년 2월: Radionix 이사

2006년 3월~2008년 12월: M&M Lynx 수석연구원 2009년 1월~현재: 삼성탈레스 ISR·PGM 연구소 위성·전자

[주 관심분야] 안테나, RF 시스템, 레이더 시스템 등