# 테라헤르츠 이미징을 위한 Si 기반의 헤테로다인 수신기

유 대 근 이 재 성

고려대학교

# Ⅰ. 개 요

최근 테라헤르츠(terahertz)의 다양한 응용에 대한 관심이증가하고 있다. 테라헤르츠의 정의는 아직까지 명확하게 정해지지 않았지만, 대략 300 GHz에서 3 THz 사이의 주파수밴드를 테라헤르츠라고 정의하는 경우가 많다. 테라헤르츠는 다양한 응용에 사용될 수 있지만, 그중에서도 이미징에 대한 연구가 많이 진행되고 있다. 이미징 수신기의 해상도는주파수에 의해 결정되고, sensitivity는 잡음 수준에 의해 결정이 된다. 이에 테라헤르츠 이미징 수신기의 경우, 정해진 주파수에서 잡음 수준을 감소시킴으로써 이미지의 품질을 향상시킬 수 있다.

고전적으로 이미징 수신기의 잡음를 줄이는 방법은 극저 온에서 이미징 수신기를 동작시키는 것이다<sup>[1]</sup>. 그러나 이 경우, 냉각 장치가 필요하게 되어 작고 저렴한 이미징 수신기에는 적용되기가 어렵다. 다른 방법으로는 이미징 시스템 앞단에 LNA(Low Noise Amplifier)를 적용하여 잡음 수준을 감소시키는 방법이다<sup>[2]</sup>. 하지만 현재의 전자 소자의 기술로는 테라헤르츠 영역에서 동작하는 LNA를 만들기가 어렵기 때문에 테라헤르츠 이미징 수신기에 적용하기에는 한계가 있다<sup>[3],[4]</sup>

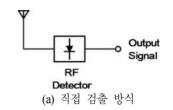

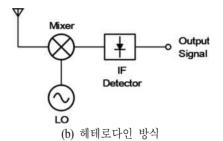

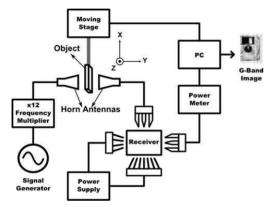

이미징 수신기에 헤테로다인 방식 적용하는 것은 잡음 수준을 줄일 수 있는 또 다른 방법으로 고려될 수 있다. 일반적으로 헤테로다인에 사용되는 혼합기(mixer)의 잡음 수준은 직접 검출기의 노이즈 레벨보다 더 낮은 것으로 알려져 있다<sup>[5]</sup>. 또한 혼합기의 경우, 하모닉 신호들을 이용하여 LNA가 동작하는 주파수보다 더 높은 주파수에서 동작시킬 수 있다. 혼합기에서 출력되는 IF 신호의 경우 저주파이므로 쉽게 증폭할수 있으므로 IF 신호 검출기의 잡음 수준의 영향을 쉽게 제거할 수 있다. [그림 1]은 이전에 많이 사용되던 직접 검출기를 이용한 이미징 수신기와 헤테로다인 방식을 사용한 이미

[그림 1] 이미징 수신기 블록 다이어그램

징 수신기의 블록 다이어그램이다. 직접 검출 방식은 안테나를 통해 입력되는 RF 신호를 바로 DC 신호로 변환하는 방식이다. 반면에, 헤테로다인 방식은 안테나를 통해 입력되는 RF 신호를 혼합기를 이용하여 IF 신호로 바꾼 후, IF 증폭기를 이용・증폭하여 IF 검출기를 이용하여 DC 신호를 변환하는 방식이다.

# II. 직접 검출 방식과 헤테로다인 방식의 이미징 시스템의 성능 비교

직접 검출 방식과 헤테로다인 방식의 이미징 검출기는 잡음 수준을 서로 다른 방식으로 표현한다. 직접 검출 방식은 잡음 수준을 NEP(Noise Equivalent Power)로 표현하고, 헤테로다인 방식은 잡음 수준을 NF(Noise Figure)로 표현한다. 따라서 두 가지 잡음 파라미터를 하나로 변환하여 두 가지 방식의 성능을 비교해야 한다. 두 가지 파라미터는 식 (1)로 상호 변환이 가능하다.

$$F = 1 + \frac{NEP}{kT\sqrt{B}} \tag{1}$$

여기서 k는 볼츠만 상수, T는 온도, B는 대역폭, F는 noise factor로서  $NF = 10 \log F \log F \log F$ 다.

100 GHz 이상에서 동작하는 직접 검출기의 경우, 약 10~100 pW/Hz<sup>1/2</sup>의 NEP를 가진다. 여기서 대역폭을 5 GHz로 가정하면 직접 검출기의 NF는 45.3~55.3 dB로 변환될 수 있다. 100 GHz 이상에서 동작하는 혼합기의 경우, 직접 검출기의 NF보다 훨씬 낮은 값을 가지고 있음을 알 수 있다<sup>[5]</sup>. 하지만 테라헤르츠 대역에서 동작하는 혼합기의 경우, conversion loss를 가지고 있으므로 IF 검출기의 잡음의 영향이 커질 수 있다. 이러한 관계는 아래의 Friis 공식으로 계산할 수 있다.

$$F_{total} = F_{mixer} + L_{mixer} (F_{IF\_amp} - 1) + \frac{L_{mixer} (F_{dectector} - 1)}{G_{IF\_amp}}$$

(2)

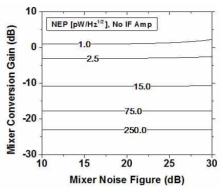

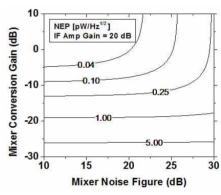

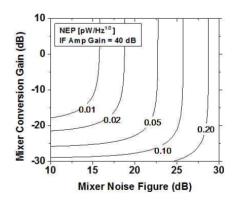

여기서  $F_{total}$ ,  $F_{mixer}$ ,  $F_{IF\ amp}$ ,  $F_{detector}$ 는 각각 전체 이미징 시 스템, 혼합기, IF 증폭기, IF 검출기의 noise factor를 나타낸 다.  $L_{mixer}$ 는 혼합기의 conversion loss를 나타내고,  $G_{IF\ amp}$ 는 IF 증폭기의 이득을 나타낸다. 여기에서 믹서의 성능인  $L_{mixer}$ ,  $F_{mixer}$  및 IF 증폭기의 이득인  $G_{IF\ amp}$ 의 세 개의 파라미터에 따른 헤테로다인 방식의 이미징 수신기의 성능 변화를 보기 위하여 [그림 2]와 같이 G<sub>IF amp</sub>가 0 dB, 20 dB, 40 dB일 때의 계산된 NEP의 contour plot을 혼합기의 CG(Conversion Gain) 과 NF에 따라서 그려보았다. 이때 IF 증폭기의 NF는 5 dB, IF 검출기의 NEP는 5 pW/Hz<sup>1/2</sup>의 일반적인 값으로 가정하였 다. 혼합기의 CG가 커질수록, 그리고 NF가 작아질수록 헤테 로다인 방식의 이미징 수신기의 성능이 좋아짐을 알 수 있 다. 또한 혼합기의 성능이 일정할 경우, IF 증폭기의 이득이 커질수록 NEP 값이 작아짐을 알 수 있다. 여기서 계산된 헤 테로다인 방식의 이미징 수신기의 NEP는 직접 검출 방식의 이미징 시스템의 NEP 값인 1~100 pW/Hz<sup>1/2</sup>보다 훨씬 낮은 값을 가지고 있음을 알 수 있다. 이에 본 연구진에서는 헤테 로다인 방식의 테라헤르츠 이미징 수신기에 대한 연구를 수 행한 바 있으며, 이에 일부 내용을 지면을 통해 소개하고자 하다.

(a) IF 증폭기가 없을 경우

(b) IF 증폭기 이득 = 20 dB일 경우

(c) IF 증폭기 이득 = 40 dB일 경우

[그림 2] 헤테로다인 방식의 이미징 시스템의 NEP contour plot

# Ⅲ. CMOS에 기반한 헤테로다인 이미징 시스템

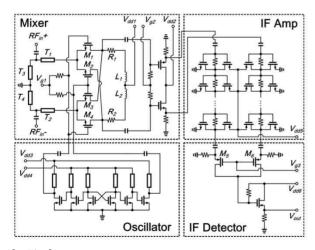

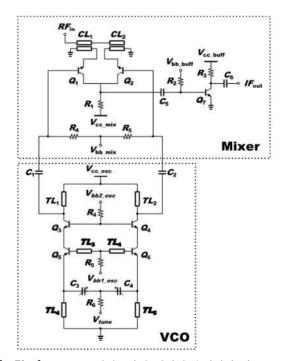

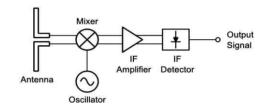

본 절에서는 CMOS를 이용하여 제작된 125 GHz와 290 GHz에서 동작하는 헤테로다인 이미징 시스템을 기술한다

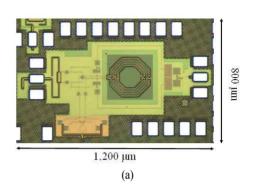

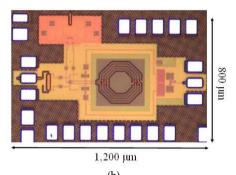

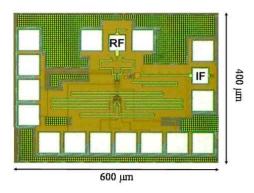

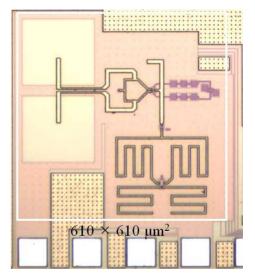

[6][7]. 두 가지 이미징 시스템은 삼성 65-nm CMOS 공정을 이 용하여 제작되었다. 삼성 65-nm CMOS 공정의 fyfmax는 소자 모델에 기반, 200/250 GHz 정도의 값을 보인다. [그림 3]은 125 GHz와 290 GHz의 헤테로다인 이미징 시스템의 회로도 를 나타낸다. 두 가지 회로 모두 혼합기와 발진기를 제외하 고는 같은 IF 증폭기와 IF 검출기 회로로 구현되었다. 125 GHz 이미징 수신기의 경우, fundamental mode에서 동작하는 혼합기를 사용하고, 발진기의 주파수도 125 GHz에서 발진 하도록 설계되었다. 하지만 290 GHz의 이미징 수신기의 경 우, 동작 주파수가 공정의  $f_{max}$ 인 250 GHz 넘게 되므로,  $3^{rd}$ subharmonic 혼합기를 사용하였고, 그에 알맞게 발진기도 100 GHz에서 동작하도록 제작하였다. 125 GHz 헤테로다인 이미징 수신기는 720 kV/W의 최대 반응도(responsivity)와 0.9 pW/Hz<sup>1/2</sup>의 최소 NEP가 측정되었다. 290 GHz 헤테로다인 이 미징 수신기의 경우에는 20 kV/W의 최대 반응도와 29 pW/ Hz<sup>1/2</sup>의 최소 NEP가 측정되었다. [그림 4]는 125 GHz와 290 GHz 헤테로다인 이미징 수신기의 칩 사진이다.

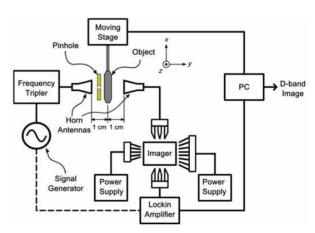

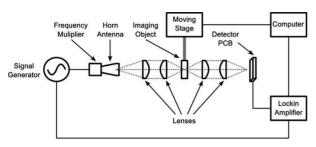

두 종류의 헤테로다인 이미징 수신기에 기반한 이미지가 [그림 5]의 transmission mode 이미징 셋업을 통하여 획득되었다. 테라헤르츠 신호는 주파수 체배기를 통하여 혼 안테나를 통하여 방사되고, 이미징 대상 물체를 투과하게 하였다. 제작된 칩은 온-웨이퍼 프로빙되어 혼 안테나를 통하여 물체를 투과한 테라헤르츠 신호를 받아들이도록 구성되었다.

[그림 3] 125 GHz와 290 GHz 헤테로다인 이미징 수신기의 회 로도

물체는 moving stage를 이용하여 x-, z- 방향으로 움직이도록 구성되었다. 이미징 수신기의 신호는 lockin amplifier를 이용하여 획득되었고, 컴퓨터에 의해 제어되는 moving stage의 위치 및 lockin amplifier의 출력 신호를 이용하여 이미지를 생

[그림 4] 125 GHz와 290 GHz 헤테로다인 이미징 수신기의 칩 사진

[그림 5] 125 GHz와 290 GHz 헤테로다인 수신기의 이미징 획 득을 위한 측정 셋업

성하였다. 이 셋업은 별도의 광학 렌즈가 없이 두 혼 안테나 사이의 거리를 2 cm가 되도록 가깝게 유지하여 이미지를 측 정하였다. 또한 near field 이미징을 테스트하기 위하여 핀홀 (pinhole)을 이용한 실험도 같이 수행하였다.

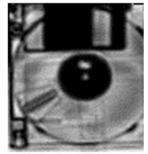

[그림 6]은 125 GHz, 290 GHz에서 각각 획득한 플로피 디 스크의 이미지이다. 플라스틱 재질을 투과하는 테라헤르츠 파의 특성에 의해 플로피 디스크의 내부 구조가 보임을 알 수 있다. 290 GHz에서 획득한 이미지가 125 GHz에서 획득한 이미지 대비 해상도가 우월하며, 또한 같은 주파수에서라도 핀홀을 이용하여 near field 이미징을 수행한 경우 해상력이 더 개선됨을 알 수 있다.

### Ⅳ. SiGe HBT에 기반한 헤테로다인 이미징 수신기

본 절에서는 SiGe HBT 공정을 이용하여 제작된 200 GHz 와 300 GHz의 헤테로다인 이미징 수신기를 소개한다. 200 GHz 헤테로다인 이미징 수신기는  $f_T/f_{max}$ 가 90/130 GHz인

(a) 125 GHz 이미지 w/o 핀홀 (b) 125 GHz 이미지 w/ 핀홀

(c) 290 GHz 이미지 w/o 핀홀

[그림 6] 125 GHz와 290 GHz 헤테로다인 이미징 수신기에서 생성된 이미지

TowerJazz 0.18-μm 공정을 이용하여 설계되었다<sup>[8]</sup>. [그림 7] 은 200 GHz 헤테로다인 이미징 수신기의 회로도를 나타낸 다. 회로가  $f_{max}$  이상에서 동작하므로 혼합기는  $3^{rd}$  subharmonic 혼합기를 사용하였고, VCO의 중심 주파수가 67 GHz 근방이 되도록 설계하였다. 혼합기는 square-law의 원리로 동작하고, 혼합기에서 출력된 IF 신호는 CE(Common Emitter) 증폭기를 통해서 증폭된 후 출력된다. [그림 8]은 200 GHz 헤테로다인 이미징 수신기의 칩 사진이다. VCO는 65.5~67.5 GHz로 2 GHz의 tuning range를 가진 것으로 측정되었고, 최대 CG은 195 GHz에서 −12.5 dB를 가지고 있는 것으로 측정되었다.

[그림 9]는 200 GHz 헤테로다인 이미징 수신기의 측정 셋 업을 나타낸다. CMOS 125 GHz/290 GHz 헤테로다인 이미 징 수신기 측정 셋업과 유사하나 IF 검출기가 집적되지 않아, IF 신호를 측정하기 위해 lockin amplifier 대신 파워 미터가 사용되었다. [그림 10]은 획득한 이미지를 보여주고 있다. 플 로피 디스크의 이미지가 성공적으로 획득되었으나, 공정의 한 계로 인하여 잡음의 영향이 상당히 있음을 알 수 있다.

300 GHz 헤테로다인 이미징 수신기는 IHP SiGe HBT 공 정을 사용하여 제작되었다. IHP SiGe HBT 공정은 소자의

[그림 7] 200 GHz 헤테로다인 이미징 수신기의 회로도

[그림 8] 200 GHz 헤테로다인 이미징 수신기의 칩 사진

[그림 9] 200 GHz 헤테로다인 수신기의 이미징 획득을 위한 측정 셋업

frlfmax가 400/500 GHz 정도의 값을 보인다<sup>19</sup>. [그림 11]은 300 GHz 이미징 수신기의 블록 다이어그램이다. 이 수신기는 온-칩 안테나가 포함되어 있으며, 방사 효율의 향상을 위해 패키징 단계에서 실리콘 렌즈와 결합되어 사용된다. 또한 혼합기를 subharmonic mode가 아닌 fundamental mode로 동작시켜 수신기의 반응도를 높이도록 하였다.

[그림 12]는 제작한 300 GHz 헤테로다인 이미징 수신기의 칩 사진이다. 측정된 최대 반응도 300 GHz에서 322 kV/W이고, 최소 NEP는 3.9 pW/Hz<sup>1/2</sup>이다. 제작된 수신기는 온-칩 안테나가 있으므로 [그림 13]과 같은 광학 측정 셋업을 구축하여 이미지를 획득하였다. 이전 측정 셋업과 동일하나, 렌즈를이용하여 혼 안테나, 이미징 대상 물체, 수신기에 테라헤르츠 빔을 포커싱하여 이미지를 획득하였다. [그림 14]는 300 GHz 헤테로다인 이미징 수신기에서 생성한 이미지이다. 플

로피 디스크의 내부가 보이는 이미지가 성공적으로 획득되었으며, 해상도 및 잡음 성능도 상대적으로 뛰어난 것을 알수 있다.

[그림 10] 200 GHz 헤테로다인 이미징 수신기에서 획득한 이미지

[그림 11] 300 GHz 헤테로다인 이미징 수신기의 블록 다이어 그램

[그림 12] 300 GHz 헤테로다인 이미징 수신기의 칩 사진

[그림 13] 300 GHz 헤테로다인 수신기의 이미징 획득을 위한 측정 셋업

[그림 14] 300 GHz 헤테로다인 이미징 수신기에서 획득한 이미지

### V. 결 론

이상으로 본 연구진에 의해 수행 중인 실리콘 기반 트랜지스터 기술 기반 테라헤르츠대역 헤테로다인 이미징 수신기제작 및 측정에 대한 연구를 소개하였다. 분석 및 측정을 통하여 헤테로다인 이미징 수신단이 직접 검출 이미징 수신단에 비해 향상된 잡음 특성을 보이고 있음을 실험적으로 보일수 있었다. 이러한 헤테로다인 기법은 소자 특성의 한계로 증폭기 설계가 어려운 테라헤르츠 대역에서의 수신단 잡음 수준을 낮추는 효율적인 좋은 방법이 될 것으로 기대된다.

# 참 고 문 헌

[1] F. Sizov, A. Rogalski, "THz detectors", Prog. Quantum Elec-

- tron., 34(5), pp. 278-347, Sep. 2010.

- [2] Q. J. Gu, Z. Xu, A. Tang and M.-C. F. Chang, "A D-band passive imager in 65 nm CMOS", *IEEE Microw. Wirel. Com*pon. Lett., 22(5), pp. 263-265, May 2012.

- [3] O. Momeni, "A 260 GHz amplifier with 9.2 dB gain and -3.9 dBm saturated power in 65nm CMOS", in 2013 Solid-State Circuits Conference Digest of Technical Papers (ISSCC), pp. 140-141, 2013.

- [4] K. Schmalz, J. Borngraber, Y. Mao, H. Rucker and R. Weber, "A 245 GHz LNA in SiGe technology", *IEEE Microw. Wirel. Compon. Lett.*, 22(10), pp. 533-535, Oct. 2012.

- [5] E. Ojefors, B. Heinemann and U. R. Pfeiffer, "Subharmonic 220- and 320-GHz SiGe HBT receiver front-ends", *IEEE Trans. Microw. Theory Tech.*, 60(5), pp. 1397-1404, May 2012.

- [6] D. Yoon, K. Song, J. Kim and J.-S. Rieh, "Si-based Sub-THz heterodyne imaging circuits", in 2014 Asian-Pacific Microw. Conf. (APMC), pp. 1136 - 1138, 2014.

- [7] D. Yoon, N. Kim, K. Song, J. Kim, S. J. Oh and J.-S. Rieh, "D-band heterodyne integrated imager in a 65-nm CMOS technology", *IEEE Microw. Wirel. Compon. Lett.*, 25(3), pp. 196-198, Mar. 2015.

- [8] D. Yoon, J.-S. Rieh, "A 200 GHz heterodyne image receiver with an integrated VCO in a SiGe BiCMOS technology", *IEEE Microw. Wirel. Compon. Lett.*, 24(8), pp. 557- 559, Aug. 2014.

- [9] B. Heinemann, R. Barth, D. Bolze, J. Drews et al., "SiGe HBT technology with f<sub>T</sub>/f<sub>max</sub> of 300 GHz/500 GHz and 2.0 ps CML gate delay", in 2010 Electron Devices Meeting (IEDM), pp. 30.5.1-30.5.4, 2010.

■ 필자소개 =윤 대 근

자 및 회로

2006년 8월: 고려대학교 전기전자전파공학부 (공학사)

2015년 2월: 고려대학교 전자전기공학과 (공학 박사)

2015년 3월~현재: 고려대학교 BK21플러스사업 단 연구교수

[주 관심분야] 밀리미터파 소자 및 회로, THz 소

이 재 성

1991년 2월: 서울대학교 전자공학과 (공학사) 1995년 2월: 서울대학교 전자공학과 (공학석사) 1999년 11월: Univ. of Michigan EECS (공학박 사)

1999년~2004년: IBM Semiconductor R&D Center

2004년~현재: 고려대학교 전기전자전파공학부 교

수

[주 관심분야] 밀리미터파 소자 및 회로, THz 소자 및 회로