http://dx.doi.org/10.6113/TKPE.2015.20.2.167

# ZVS 위상천이 풀브릿지 컨버터의 디지털 샘플링 기법에 따른 소신호 모델 분석

김정우<sup>1</sup>, 조영훈<sup>†</sup>, 최규하<sup>1</sup>

An Analysis of ZVS Phase-Shift Full-Bridge Converter's Small Signal Model according to Digital Sampling Method

Jeong-Woo Kim<sup>1</sup>, Younghoon Cho<sup>†</sup>, and Gyu-Ha Choe<sup>1</sup>

#### **Abstract**

This study describes how digital time delay deteriorates control performance in zero voltage switching (ZVS) phase-shifted full bridge (PSFB) converter. The small-signal model of the ZVS PSFB converter is derived from the buck-converter small-signal model. Digital time delay effects have been considered according to the digital sampling methods. The analysis verifies that digital time delays reduce the stability margin of the converter, and the double sampling technique exhibits better performance than the single sampling technique. Both simulation and experimental results based on 250 W ZVS PSFB confirm the validity of the analyses performed in the study.

**Key words:** ZVS(Zero Voltage Switching), DPWM(Digital Pulse-Width Modulator), ZVS PSFB(Zero Voltage Switching Phase-Shift Full Bridge)

#### 1. 서 론

디지털 제어기는 아날로그 제어기와 달리 비선형 영역의 쉬운 접근, 복잡한 제어기 및 시퀀스의 용이한 구현, 그리고 하드웨어의 수정없이 제어기법의 전환이 가능하다는 장점 때문에 산업 전반에 결쳐 그 사용도가증가되고 있는 추세이다<sup>[1]-[3]</sup>. 그러나 이러한 디지털 제어기의 수요와 보급이 늘어남에 따라 디지털 제어기의 문제점 또한 대두되고 있는데, 그 중 하나가 디지털 제어기의 시지연 효과이다. 이러한 시지연은 연산과정, 정보를 검출하는 과정, 그리고 정보를 갱신하는 과정에서 발생하는데, 정보를 검출하고 갱신하는 방법에 따라 크게 단일 샘플링, 이중 샘플링 및 다중 샘플링으로 나뉠수 있으며 각각의 경우에 발생되는 지연시간이 다르다 [4]-[7]. 이와 같은 시지연은 디지털 제어기를 포함한 전체

제어 시스템의 위상 여유 및 제어 대역폭의 감소를 초 래하여 제어성능저하를 가져오게 된다<sup>[8]</sup>.

한편 영전압 스위칭 위상천이 풀브릿지(Zero voltage switching phase-shift full bridge : ZVS PSFB) 컨버터 는 위상 변조와 회로의 기생성분을 이용하여 쉽게 소프 트스위칭을 얻을 수 있으며 높은 효율을 갖기 때문에 산업용, 가전용, 그리고 자동차용 전력변환시스템에 매 우 활발히 적용되고 있다<sup>[9]</sup>. 이러한 ZVS PSFB 컨버터 는 제어 구조가 간단하여 주로 아날로그 제어기를 이용 하여 개발이 되어 왔으나, 최근에는 신뢰성 있는 제어 시퀀스의 구현, 그리고 다양한 운전 조건에서의 제어 성 능 확보를 위하여 디지털 제어기를 적용하는 연구가 많 이 진행되고 있는 추세이다[10]. 그러나 기존의 논문들은 대부분 디지털 제어기를 ZVS PSFB 컨버터에 단순 적 용하는데에 중점을 두어 왔으며, 디지털 제어기의 적용 으로 인하여 어느 정도의 위상지연 및 크기 감소 효과 와 어느 정도의 제어 성능 저하가 나타나는지에 대해서 는 연구가 거의 진행되지 않고 있는 실정이다.

본 논문에서는 이러한 ZVS PSFB 컨버터에 디지털 제어기를 적용할 경우 발생되는 변조기의 위상 지연 및 제어대역폭 저하 효과를 디지털 제어기의 샘플링 기법에 따라 분석하고자 한다. 이를 위하여 ZVS PSFB 컨버

Paper number: TKPE-2015-20-2-9

<sup>+</sup> Print ISSN: 1229-2214 Online ISSN: 2288-6281 + Corresponding author: yhcho98@konkuk.ac.kr, Dept. of

Electrical Eng., Konkuk University

Tel: +82-2-450-4109 Fax: +82-2-447-9186

<sup>&</sup>lt;sup>1</sup> Dept. of Electrical Eng., Konkuk University Manuscript received Oct. 8, 2014; accepted Feb. 11, 2015 — 본 논문은 2014년 전력전자학술대회 외부장학금 수혜논문임

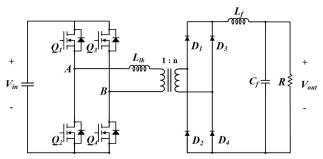

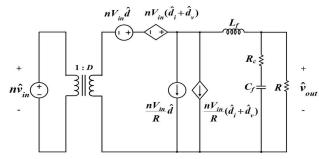

Fig. 1. The ZVS PSFB converter.

터의 제어신호와 출력 전압 및 전류 관계의 소신호 모델링, 그리고 디지털 펄스폭 변조기(Digital pulse-width modulator : DPWM)의 소신호 모델링을 수행하고, 시뮬레이션과 실험을 통하여 유도한 모델의 정확도를 검증하다.

#### 2. ZVS PSFB 컨버터의 소신호 모델링

그림 1은 본 논문에서 다루는 ZVS PSFB 컨버터의 회로구조를 보여주고 있다. 그림에 나타난 것처럼 ZVS PSFB 컨버터는 풀브릿지 회로, 고주파 변압기, 다이오 드 정류기, 그리고 LC필터로 구성되어 있다. 여기서 다이오드 정류기는 반파 정류기, 배압 정류기등 다양한 회로로 구성이 가능하나 본 논문에서는 전파 정류기를 이용한다. 그림 1에서 2차측의 회로 도통 구조는 벅컨버터와 유사하다. 한편 식 (1)은 ZVS PSFB 컨버터의 전압전달비로 출력전압  $v_{out}$ 은 변압기 권선비 n, 변압기 2차측 전압 듀티 사이클  $D_{eff}$ , 입력전압  $v_{in}$ 의 곱과 같음을 나타내는데 이 또한 권선비를 제외하고는 벅컨버터와 동일함을 알 수 있다.

$$v_{out} = nD_{eff}v_{in} \tag{1}$$

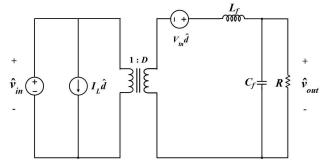

## 2.1 벅컨버터의 소신호 모델링

벅컨버터의 입력전압, 입력전류, 듀티 사이클을  $v_{in}(t)$ ,  $i_{in}(t)$ , D라 하고, 출력전압, 인덕터 전류를  $v_o(t)$ ,  $i_L(t)$ 이라 할 때 벅컨버터의 소신호 분석을 통해식 (2)와 식 (3)을 구할 수 있다. 또한 식 (2)와 식 (3)에 근거하여 그림 2와 같이 벅컨버터의 소신호 등가회로를 나타낼 수 있다.

$$\hat{i}_{r}(t) = \hat{Di}_{r}(t) + \hat{I}_{r}\hat{d}(t) \tag{2}$$

$$\widehat{v_o}(t) = \widehat{Dv_{in}}(t) + V_{in}\widehat{d}(t) \tag{3}$$

그림 2의 벅컨버터 소신호 등가회로에 변압기와 제어 입력인 위상천이로 발생하는 변압기 2차측 유효 듀티 사이클  $D_{eff}$ 에 영향을 끼치는 요소들을 추가하면 ZVS PSFB 컨버터의 소신호 모델링을 구할 수 있다.

Fig. 2. The small signal equivalent circuit of buck-converter.

#### 2.2 ZVS PSFB 컨버터의 소신호 모델링

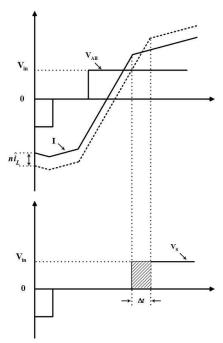

ZVS PSFB 컨버터의 듀티 사이클은 제어입력인 위상천이에 의한 변압기 1차측 듀티 사이클 외에도 필터 인덕터 전류의 변동  $\hat{i_L}$ , 입력 전압의 변동  $\hat{v_{in}}$ 에 의해 영향을 받는다. 그림 3은 필터 인덕터 전류의 변화에 의한듀티 사이클의 변화를 나타낸다. 그림 3에서 1차측 전류가 실선과 같이 흐르고 있을 때 필터 인덕터 전류가  $\hat{i_L}$ 만큼 증가하면 1차측 전류는  $m\hat{i_L}$ 의 크기만큼 증가하면서 점선과 같이 흐르게 된다. 1차측 전류의 증가는 2차측 전압의 상승시간을 지연시켜 2차측 전압의 듀티 사이클을 감소시킨다. 이때  $\hat{i_L}$ 에 의해 발생하는 시지연  $\Delta t$ 와 감소한 듀티 사이클  $\hat{d_i}$ 는 다음과 같이 구할 수 있다.

$$\Delta t = 2n\hat{i}_L \frac{L_{lk}}{V_{in}} \tag{4}$$

$$\hat{d}_i = -\frac{\Delta t}{(T_s/2)} = -\frac{4nL_{lk}f_s}{V_{in}}\hat{i}_L \tag{5}$$

$$\hat{d}_i = -\frac{R_d}{V} \hat{i}_L \tag{6}$$

식 (6)에서  $R_d = 4n^2 L_{ll} f_s$ 는 소신호 변동에 의한 임피던스로 시스템에 추가적인 제동을 가하는 역할을 한다.

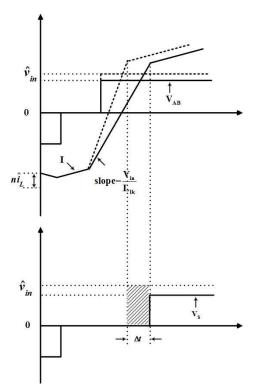

$\hat{i_L}$  외에 듀티 사이클에 영향을 끼치는 요소에는 입력 전압의 변동  $\hat{v_{in}}$ 이 있다. 그림 4와 같이 정상상태 동작에서 입력전압이  $\hat{v_{in}}$ 의 크기만큼 커질 때 실선과 같이 흐르던 1차측 전류의 기울기는 점선처럼 증가한다. 1차측 전류 기울기의 증가는 2차측 전압의 상승시간을 앞당기며 2차측 전압의 듀티 사이클 증가시킨다. 이때  $\hat{v_{in}}$ 에 의해 앞당겨진 시간  $\Delta t$ 와 증가한 듀티 사이클  $\hat{d_v}$ 는 다음과 같이 구할 수 있다.

$$\Delta t = n(2I_L - \frac{V_{out}}{L}D'\frac{T_s}{2})(\frac{L_{lk}}{V_{in}} - \frac{L_{lk}}{V_{in} + \widehat{v_{in}}})$$

(7)

$$\Delta t = n(2I_L - \frac{V_{out}}{L}D^{'}\frac{T_s}{2}) - \frac{L_{lk}}{V_{in}(V_{in} + \widehat{V_{in}})}\widehat{v_{in}}$$

(8)

Fig. 3. Duty cycle modulation due to the change of filter inductor current.

식 (7)과 식 (8)에서  $D^{'}=(1-D)$ 이고, 소신호  $\widehat{v_{in}}$ 은  $V_{in}$ 보다 매우 작으므로 무시하면 식 (8)은 식 (9)와 같이 나타낼 수 있다.

$$\Delta t = n \left( 2I_L - \frac{V_{out}}{L} D' \frac{T_s}{2} \right) \frac{L_{lk}}{V_{in}^2} \widehat{v_{in}}$$

(9)

컨버터의 1차측 순환 전류에 의한 도통 손실을 줄이기 위해  $D^{'}$ 를 최소화할 필요가 있으며 이로 인해 식 (9)에서  $D^{'}$ 를 무시하면 식 (9)는 다음과 같이 나타낼 수 있다.

$$\hat{d_v} = \frac{4nL_{lk}f_sI_L}{V_{in}^2}\hat{v_{in}}$$

(10)

$$\hat{d_v} = \frac{R_d I_L}{V_c^2} \hat{v_{in}} \tag{11}$$

변압기 1차측 듀티 사이클의 변동을  $\hat{d}$ 라 하면 변압기 2차측 유효 듀티 사이클의 변동  $\hat{d_{eff}}$ 는  $\hat{i_L}$ ,  $\hat{v_{in}}$ 에 의한 듀티 사이클의 변동을  $\hat{d_i}$ ,  $\hat{d_v}$ 와 함께 식 (12)와 같이 나타낼 수 있다.

$$\widehat{d_{eff}} = \widehat{d} + \widehat{d}_i + \widehat{d}_v \tag{12}$$

그림 2의 벅컨버터 소신호 모델에서 제어입력  $\hat{d}$ 를 식 (12)의 유효 듀티 사이클로 바꾸고 변압기 권선비 n을 추가하면 그림 5의 ZVS PSFB 컨버터의 소신호 모델을 구할 수 있다.

Fig. 4. Duty cycle modulation due to the change of input voltage.

Fig. 5. The ESR added small signal equivalent circuit of ZVS PSFB converter.

#### 2.3 제어입력에 따른 출력 전압, 전류

듀티 사이클에 영향을 주는 두 요소  $\hat{d}_i$ ,  $\hat{d}_v$ 에 의한  $R_d$ 와 필터 커패시터의 ESR을 고려하면 ZVS PSFB 소신호 등가회로는 그림 5와 같이 나타낼 수 있다<sup>[13]</sup>.

그림 5에서 제어입력인 유효 듀티 사이클에 따른 필터 인덕터 전류의 변동을  $G_{id}(s)$ 라 하고 라플라스 영역에서 나타내면 식 (13)과 같다.

$$G_{id}(s) = \frac{I_L}{D_{eff}} = n V_{in} k_{id} \frac{1 + \frac{s}{\omega_{esr}}}{\frac{s^2}{\omega_o^2} + \frac{s}{Q\omega_o} + 1}$$

(13)

식 (13)에서  $k_{id}$ ,  $\omega_{esr}$ ,  $\omega_{o}$ , Q는 각각 식 (14), 식 (15), 식(16), 식 (17)이다.

$$U(s) \xrightarrow{T_s} U(s)^* \xrightarrow{G_{pwm}(s)} D_{eff} \xrightarrow{Q_{out}} G(s)$$

Fig. 6. Block diagram of ZVS PSFB converter.

$$k_{id} = \frac{1}{(R_d + R)} \tag{14}$$

$$\omega_{esr} = \frac{1}{(R_c + R)C} \tag{15}$$

$$\omega_o = \sqrt{\frac{R_d + R}{(R_c + R)LC}} \tag{16}$$

$$Q = \frac{1}{\omega_o} \frac{R + R_d}{L + C(R_d R_c + R_d R + R_c R)}$$

(17)

그림 5에서 제어입력인 유효 듀티 사이클에 따른 출력 전압 변동을  $G_{vd}(s)$ 라 하고 라플라스 영역에서 나타내면 식 (18)과 같다.

$$G_{vd}(s) = \frac{V_{out}}{D_{eff}} = n V_{in} k_{vd} \frac{1 + \frac{s}{\omega'_{esr}}}{\frac{s^2}{\omega'_o^2} + \frac{s}{Q'\omega'_o} + 1}$$

(18)

식 (18)에서  $k_{vd}$ ,  $\omega'_{esr}$ ,  $\omega'_{o}$ , Q'는 각각 식 (19), 식 (20), 식 (21), 식 (22)이다.

$$k_{vd} = \frac{R}{(R + R_d)} \tag{19}$$

$$\omega'_{esr} = \frac{1}{R_c C} \tag{20}$$

$$\omega'_{o} = \sqrt{\frac{R + R_{d}}{(R + R_{c})LC}} \tag{21}$$

$$Q' = \frac{1}{\omega'_{o}} \frac{R + R_{d}}{L + C(R_{d}R_{c} + R_{d}R + R_{c}R)}$$

(22)

# 3. 샘플링기법

디지털 제어기에서는 그림 6과 같이  $G_{pwm}(s)$ 에 의해 전체 시스템의 위상여유와 제어 대역폭의 감소를 야기하는 시지연이 발생하고, 이러한 시지연은 샘플링 기법에 따라 달라진다<sup>[12]</sup>. 이번 장에서는 싱글 샘플링과 더블 샘플링 기법에 의해 생긴 시지연이 앞서 구한 ZVS PSFB 컨버터의 전달함수에 어떻게 영향을 끼치는지 알아본다.

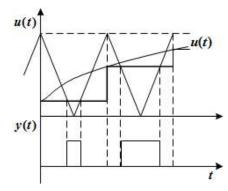

#### 3.1 싱글 샘플링 기법

싱글 샘플링 기법에서는 샘플링 주파수와 스위칭 주 파수가 같으며 캐리어 신호 한 주기에 한 번 기준신호 가 갱신된다. 본 논문에서는 그림 7과 같이 대칭삼각파

Fig. 7. The single-update-mode triangular-carrier modulators.

Fig. 8. The double-update-mode triangular-carrier modulators.

를 캐리어 신호로 사용하고 기준 신호 u(t)를 대칭 삼각파의 최대값일 때 갱신한다. 이때 라플라스 영역에서 싱글 샘플링 기법의 PWM 입출력 전달함수  $G_{single}(s)$ 는 식 (23)과 같이 나타낼 수 있다 $^{[12]}$ .

$$G_{single}(s) = \frac{Y(s)}{U(s)} = \frac{1}{2} \left(e^{-s\frac{(1-D)T_s}{2}} + e^{-s\frac{(1+D)T_s}{2}}\right)$$

(23)

또한 식 (23)은  $s=j\omega$ 라는 관계식을 이용하여 식 (24) 와 같이 크기와 위상으로 나타낼 수 있다 $^{[12]}$ .

$$G_{single}(j\omega) = \cos(\frac{wDT_s}{2}) \angle (-\frac{\omega T_s}{2})$$

(24)

식 (24)를 통해 싱글 샘플링 기법이 ZVS PSFB 컨버터의 전달함수 크기와 위상에 어떤 영향을 끼치는지 알수 있다. 전달함수의 크기는 듀티 사이클 D와  $\omega$ 의 주파수에 영향을 받고 위상은 샘플링 주기의 반만큼 지연된다. 따라서 기준 신호 u(t)를 샘플링하는 과정과 PWM과정에서  $\frac{3}{2}T_s$ 만큼의 시지연이 발생한다.

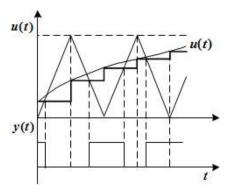

#### 3.2 더블 샘플링 기법

더블 샘플링 기법에서는 샘플링 주파수가 스위칭 주파수의 2배이며 그림 8과 같이 기준 신호 u(t)를 대칭삼각파의 한 주기 동안 두 번 갱신한다. 이때 라플라스

| CONVENTER        |         |  |

|------------------|---------|--|

| Parameter        | Value   |  |

| $ m V_{in}$      | 100 [V] |  |

| $ m V_{out}$     | 37 [V]  |  |

| P <sub>out</sub> | 250 [W] |  |

| f.               | 20[kHz] |  |

$C_{mos}$

$L_{lk}$

TABLE I SIMULATION PARAMETER OF ZVS PSFB CONVERTER

영역에서 더블 샘플링 기법의 PWM 입출력 전달함수  $G_{double}(s)$ 는 식 (25)와 같이 나타낼 수 있으며  $s=j\omega$ 의 관계식을 이용하여 식 (26)과 같이 나타낼 수 있다 $^{[12]}$ .

$$G_{double}(s) = \frac{Y(s)}{U(s)} = \frac{1}{2} \left( e^{-s(1-D)T_{s}'} + e^{-sDT_{s}'} \right)$$

(25)

80[pF] 15[uH]

$$G_{double}(j\omega) = \cos(\omega(D - \frac{1}{2})T_{s}^{'}) \angle \left(-\frac{\omega T_{s}^{'}}{2}\right)$$

(26)

식 (26)을 통해 더블 샘플링 기법이 ZVS PSFB 컨버터의 전달함수의 크기와 위상에 미치는 영향을 알 수있다. 전달함수의 크기는 싱글 샘플링의 경우와 마찬가지로 듀티 사이클 D와  $\omega$ 의 주파수에 영향을 받고 위상은 샘플링 주기의 반만큼 지연된다. 싱글 샘플링의 샘플링 주기는 더블 샘플링의 샘플링 주기의 2배인  $T_s=2T_s^{'}$ 이므로 더블 샘플링의 경우 기준 신호 u(t)를 샘플링하는 과정과 PWM 과정에서  $\frac{3}{4}T_s$ 만큼의 시지연이 발생한다.

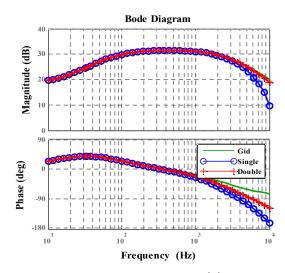

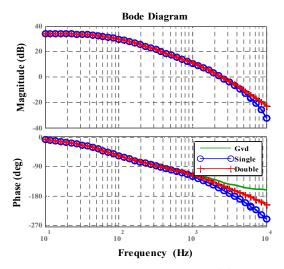

## 4. 시뮬레이션

시뮬레이션을 통해 싱글 샘플링 기법과 더블 샘플링 기법이 시스템 전달함수에 끼치는 영향을 살펴보았다. 표 1은 시뮬레이션에 사용된 변수들이며, 그림 9는 스위칭 주파수  $f_s$ 가  $20[kHz]일 때 주파수 영역에서 샘플링기법에 따른 <math>G_{id}(s)$ 의 크기와 위상의 변화를 보여준다. 나이퀴스트 주파수 이전에서  $G_{id}(s)$ 의 크기는 샘플링기법에 따라 큰 차이가 없으나  $G_{id}(s)$ 의 위상은 샘플링기법에 따라 달라짐을 보인다.

표 2는 그림 9에서 주파수가 2[kHz]일 때 샘플링 기법에 따른  $G_{id}(s)$ 의 위상을 비교한 것으로 더블 샘플링에서는 싱글 샘플링의 경우 보다 16.8[%] 개선된다.

그림 10은 스위칭 주파수  $f_s$ 가 20[kHz]일 때 샘플링기법에 따른  $G_{vd}(s)$ 의 이득과 위상의 변화를 나타낸다.

Fig. 9. The frequency response of  $G_{id}(s)$  according to sampling method.

TABLE II  $\mbox{PHASE OF} \ G_{id}(s) \ \mbox{ACCORDING TO SAMPLING } \\ \mbox{METHOD}$

| Sampling Method | Phase  |

|-----------------|--------|

| Analog          | -35°   |

| Single Sampling | -52.9° |

| Double Sampling | -44°   |

Fig. 10. The frequency response of  $G_{vd}(s)$  according to sampling method.

표 3은 그림 10에서 주파수가 2[kHz]일 때 샘플링 기법에 따른  $G_{vd}(s)$ 의 위상을 비교한 것으로 더블 샘플링에서는 싱글 샘플링의 경우 보다 위상이 6.08[%] 개선된다.

TABLE III  $\begin{tabular}{ll} PHASE OF $G_{\!v\!d}(s)$ ACCORDING TO SAMPLING \\ METHOD \end{tabular}$

| Sampling Method | Phase |

|-----------------|-------|

| Analog          | -130° |

| Single Sampling | -148° |

| Double Sampling | -139° |

Fig. 11. Hardware of ZVS PSFB converter.

Fig. 12. Input and output of ZVS PSFB converter.

# 5. 실 험

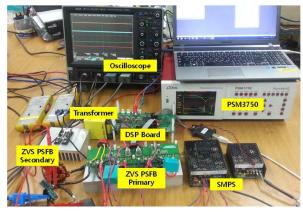

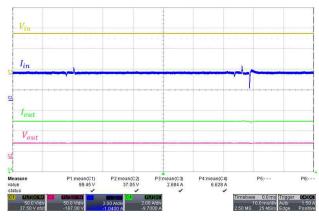

디지털 제어기의 위상지연 효과를 확인하기 위하여 그림 11과 같이 250[W]급의 ZVS PSFB 컨버터를 이용하여 실험을 수행하였다. 표 4는 실험에 사용된 조건을 보여주고 있다. 샘플링 기법에 따른  $G_{vd}(s)$ 의 크기와 위상을 분석하기 위하여 PSM3750을 사용하여 섭동 신호의 발생 및 측정을 수행하였다. PSM3750의 주파수 스윕(frequency sweep) 신호는 DSP보드의 ADC(analog-to-digital converter)로 입력되어 출력 듀티 지령에 반영된다. 그림 12는 시간 도메인상에서 ZVS PSFB 컨버터의 입출력 전압과 전류를 보여주고 있다.

TABLE IV

EXPERIMENT PARAMETER OF ZVS PSFB

CONVERTER SYSTEM

| Parameter                                | Value     |

|------------------------------------------|-----------|

| Input voltage, $V_{in}$                  | 100 [V]   |

| Output voltage, $V_{out}$                | 37 [V]    |

| Transformer turns ratio, n               | 0.52      |

| Transformer leakage inductance, $L_{lk}$ | 11.7 [uH] |

| Switching frequency, $f_s$               | 20 [kHz]  |

| Output filter inductor, L                | 80 [uH]   |

| Output filter capacitor, C               | 2000 [uF] |

| Load resistor, R                         | 5 [Ω]     |

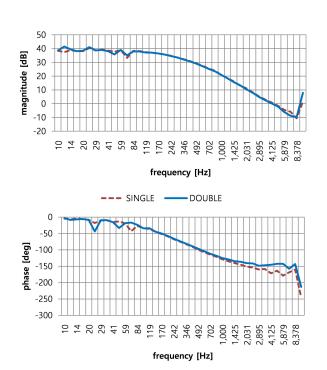

Fig. 13. Control-to-output voltage transfer functions of ZVS PSFB converter.

DOUBLE

--- SINGLE -

그림 13은 싱글 샘플링과 더블 샘플링을 수행할 경우입력 듀티 지령 대비 출력 전압의 변동폭을 PSM3750을 이용하여 주파수별로 측정한 결과이다. 그림에서 싱글샘플링은 점선으로, 더블 샘플링은 실선으로 표시되어있다. 그림 13에서 수십Hz 근방의 저주파 대역에서는싱글 샘플링을 한 경우와 더블 샘플링을 한 경우의 크기와 위상에 큰 차이가 없으나,스위칭 주파수  $f_s$ 의 10%인 2kHz 이상에서는싱글 샘플링의 경우 크기와 위상 감소가 확연히 나타남을 알 수 있다.특히 위상 정보의 경우 싱글 샘플링은 약 3kHz 대역에서  $-160^\circ$ 를 통

과하는데 더블 샘플링은 약 7kHz 대역에서 그 위상각을 교차한다. 이는 싱글 샘플링의 경우 더블 샘플링에 비하여 더 낮은 주파수에서 개루프 제어시스템이 불안정 영역으로 들어감을 의미한다. 만약 제어 대역폭을 2kHz로 선정한다면, 더블 샘플링의 위상여유가 싱글 샘플링에 비해 7.01[%] 더 큰 것을 확인할 수 있다. 한편, 그림 13의 실험결과는 그림 10의 시뮬레이션 결과 2[kHz]에서 더블 샘플링의 경우 싱글 샘플링 보다 전달함수의 위상이 6.08[%] 개선된 것과 0.98[%] 차이가 있는데, 그이유는 실험에서는 디지털 제어기에 내장되어 있는 ADC로 인한 위상 지연 효과가 추가되었기 때문이다.

또한, 싱글 샘플링과 더블샘플링 모두 -180° 이상에서는 응답 크기 상승(magnitude boost)이 나타나는데,이는 DPWM의 특성이 ZOH(zero order hold)와 비슷하여 나타나는 현상이다.

## 6. 결 론

본 논문에서는 ZVS PSFB 컨버터에 디지털 제어기를 적용했을 때 발생하는 위상지연 효과가 샘플링 기법에 따라 어떻게 변하는지를 연구하였다. 이를 위하여 ZVS PSFB 컨버터의 소신호 모델을 수행하였고, DPWM이 적용될 경우 샘플링 기법에 따른 모듈레이터의 주파수 응답특성을 분석하였다. 분석한 내용의 검증을 위하여 250W급 ZVS PSFB 컨버터를 대상으로 시뮬레이션과 실험을 실시하였고 그로부터 더블 샘플링을 수행하는 경우 위상지연과 제어대역폭 저하 효과가 개선됨을 확인하였다.

## References

- [1] Y. Y. Tzou, S. Y Hwang, H. J. Wu, and I. K. Wang, "Design and inpementation of and interactive digital controller development system," *Industrial Electronics Society, IECON'89., 15th Annual Conference of IEEE*, Vol. 4, pp. 792–798, 1989.

- [2] B. J. Patella, A. Prodic, A. Zirger, and D. Maksimovic, "High-frequency digital PWM controller IC for DC/DC converters," *IEEE Trans. Power Electron.*, Vol. 18, No. 1, pp. 438-446, Jan. 2003.

- [3] A. Prodic and D. Maksimovic, "Digital PWM controller and current estimator for a low-power switching converter," in *Proc. IEEE COMPEL Conf.*, pp. 123–128, 2000.

- [4] A. Syed, E. Ahmed, D. Maksimovic, and E. Alarcon, "Digital pulse width modulator architectures," 2004 Power Electronics Specialists Conference (PESC), pp. 4689 - 4695, 20–25 Jun. 2004.

- [5] L. Corradini and P. Mattavelli, "Analysis of multiple sampling technique for digitally controlled dc-dc converters," in Proc. IEEE 37th Annu. PESC, Jeju, Korea, pp. 1 - 6, 18-22 Jun. 2006.

- [6] E. Tedeschi, P. Mattavelli, D. Trevisan, and L. Corradini, "Repetitive ripple estimation in multi-sampling digitally controlled dc-dc converters," 32nd Annual Conference of the IEEE Industriel Electronics Society, IECON'06, Nov. 7-10, 2006.

- [7] L. Corradini, E. Tedeschi, and P. Mattavelli, "Advantages of the symmetric-on time modulator in multiple-sampled digitally controlled DC-DC converters," 2007 Power Electronics Specialists Conference (PESC), pp. 1974–1980, 17–21 Jun. 2007.

- [8] L. Corradin, P. Mattavelli, E. Tedeschi, and D. Trevisan, "High-bandwidth multisampled digitally controlled DC-DC converters using ripple compensation," *IEEE Transactions on Industrial Electronics*, Vol. 55, No. 4, pp. 1501–1508, Apr. 2008.

- [9] J. A. Sabate, V. Vlatkovic, R. B. Ridley, F. Lee, and B. H. Cho, "Design considerations for high-voltage, high-power full-bridge zero-voltage-switched PWM converter," *Applied Power Electronics Conference and Exposition*, pp. 275–284, 1990.

- [10] G. B. Koo, G. W. Moon, and M. J. Youn, "New zero-voltage-switching phase-shift full-bridge converter with low conduction losses," *IEEE Transaction on Industrial Electronics*, Vol. 52, pp. 228-235, Feb. 2005.

- [11] V. Vlatkovic, J. A. Sabate, R. B. Ridley, F. C. Lee, and B. H. Cho, "Small-signal analysis of the phase-shifted PWM converter," *IEEE Transaction on Power Electronics*, Vol. 7, No. 1, pp. 128–130, Jan. 1992.

- [12] D. M. Van de Sype, K. De Gusseme, A. P. Van den Bossche, and J. A. Melkebeek, "Small-signal laplace-domain analysis of uniformly-sampled pulse-width modulator," in *Proc. IEEE 35th Annu. PESC*, Vol. 6, pp. 4292 - 4298, Jun. 20-25, 2004.

- [13] J. G. Lim and S. K. Chung, "Digital control of phase-shifted full-bridge PWM converter," *Journal of Power Electronics*, Vol. 8, pp. 201 - 209, Jul. 2008.

# 김정우(金正雨)

1989년 6월 23일생. 2014년 건국대 전기공학과 졸업. 2014년~현재 동 대학원 전기공학과 석사과정.

## 조영훈(曺永勳)

1980년 2월 4일생. 2002년 건국대 전기공학 과 졸업. 2004년 서울대 전기공학과 졸업(석 사). 2012년 버지니아공대 졸업(공박). 2004 년~2009년 현대모비스 기술연구소 주임연 구원. 2012년~2013년 에너트로닉스 책임연

구원. 2013년~현재 건국대 전기공학과 조교수.

# 최규하(崔圭夏)

1955년 7월 24일생. 1978년 서울대 공대 전기공학과 졸업. 1980년 동 대학원 전기공학과 졸업(석사). 1983년 동 대학원 전기공학과 졸업(공박). 1987년~1988년 미국 오레곤주립대 전기공학과 Post-Doc. 1998년~1999

년 버지니아주립대 교환방문교수. 1996년~현재 건국대 산업기술연구원 에너지전자연구센터 소장. 현재 건국대 전기공학과 교수. 2007년~2008년 당 학회 회장 역임.