# 고출력 LED 조명 개발 및 기술개발동향

# I. 서 론

최초의 가시광선 LED(발광 다이오드)가 1962년 개발된 이래 1960년대 적색 LED, 1970~1980년대를 거치면서 녹색 LED가 개발되었고, 1995년 일본의 니치아 청색 LED가 개발되면서 이제 명실상부한 총천연색(full color)의 구현이 가능하게 되었다, 2000년대에 들어서면서 생활 전반에 사용되기 시작하여 휴대폰의 액정 표지 소자, 옥외용대형 디스플레이 전광판, 교통 신호등, 자동차 부품, TV를 중심으로 한가전제품 등 모든 분야에서 다양한 용도로 사용되고 있다. [1-2] LED는반도체 고체 조명으로 환경 친화적이고, 기존의 일반 조명 기구에 비하여에너지 절약 효과가 우수하고, 장시간 사용이 가능한 반영구적인 긴

수명 등의 장점으로 인하 여 국가적 관심 산업이 되어 정부에서도 국가적 정책 방향을 설정하고 지원하고 있다. <sup>[3]</sup> 이에 기반 하여 국내에서도 출력과 효

감성 조명이란 LED의 여러 파장을 이용하여 감성을 조절하는 조명이다. 현재 인간과 동물의 감성을 조절하는데 많은 연구가 이루어지고 있다.

율을 향상하고 궁극적으로 일반 조명을 비롯하여 감성 조명 등 다양한 용도로 활용하기 위해 연구개발이 활발히 진행되고 있다. [4-6]

사파이어 기판을 사용하는 질화물 반도체는 청색, 녹색 발광 LED로 써 청색 LED와 녹색발광 형광체를 함께 사용하면 백색 LED가 되어 조명용으로 사용할 수 있다. 하지만 고휘도를 위해서 필요한 높은 전류를 주입하는 경우 p-형 GaN의 도핑농도가 낮아 저항이 높고 더욱 사파이어 기판의 낮은 열전달로 인해 높은 전류에 의해 구동 시 LED 접합의 온도가 올라가 수 W의 고휘도 LED 제작에 걸림돌이 되고 있다. 사파이어 기판에 에피성장 LED 구조의 시료를 열전달이 좋은 Cu 또는 Si

권성훈 (주)대화 기업부설연구소

**38**\_The Magazine of the IEIE

기판에 접합시킨 후 사파이어 기판에서 에피층을 향하여 강한 레이저를 쪼여주면 GaN 에피층이 분해되어 사파이어 기판을 에피층으로 부터 분리할 수 있어 Cu 또는 Si 기판에 LED 소자가 있는 수직형 LED를 제작할 수 있다. 이렇게 제작된 LED소자는 열전달의 문제를 해결할 수 있어 고휘도 LED 제작이 좀 더 용이하다.

LED 소자 제작 기술의 단계는 통상적으로 에피, 칩, 패키지, 모듈 및 시스템 기술로 분류할 수 있는데, 본 기고에서는 LED 기술의 중심이라고 할 수 있는 기판을 포함한 에피(Epi), 고휘도, 고출력 칩(chip) 제조 기술과 고출력에 사용되는 패키지 기술에 대하여 살펴본다.

기판에서는 상용화되어 사용되는 사파이어나 SiC 기판을 중심으로 설명하고 이외에 연구가 진행 중인 GaN 기판 등을 간단히 소개하고자 한다. 특히 사파이어 기판에 대하여 현재 광 추출 성능을 증진하기 위한 PSS(patterned sapphire substrate) 기술과 에피 성장에 관련된 MOCVD(metal organic chemical vapor deposition)기술, 칩의 구조와 최대 광추출 능력을 향상하기 위해 사용되는 기술에 대하여 알아본다.

고출력 LED 패키지 기술은 플라스틱 패키징, 웨이퍼 레벨 패키징(Wafer Level Packaging, WLP), 세라믹 적층 패키징, Multi-chip 패키징, 금속 패키징(Metal Packaging), COB (Chip on Board)에 대하여 알아본다.

# Ⅱ. LED 제조 공정기술

#### 1. 공정 개요

LED 제조기술의 단계는 통상적으로 기판 단결정 제조 공정, 에피웨이퍼 제조공정, 칩제조공정, 패키지 공정 및 모듈 및 시스템 기술로 분류할 수 있으며 일련의 과정은 그림 1과 같다. 본 논고에서는 LED 기술의 핵심인 기판을 포함한 에피, 칩, 패키지의 중요한 기술 이슈에 대하여 알아본다.

## 2. 기판 제조

반도체 공정에 의하여 기판(wafer) 위에 반도체가 성장 되는데, 이 기판의 구조가 성장 가능한 반도체의 종류 및

| 1 | Substrate       |      |

|---|-----------------|------|

| 2 | Epi Growth      |      |

| 3 | Chip Process    | 1 mm |

| 4 | PKG             |      |

| 5 | LED Module/응용제품 |      |

〈그림 1〉 LED 응용제품 제조 5 Steps

구조를 결정한다. 따라서 기판은 반도체의 성장을 결정하는 기반이 되며, 따라서 격자 상수 등 성장하고자 하는 반도체의 성질에 적합한 구조를 가진 것을 선택한다. 일반적으로 알려진 실리콘 반도체 성장을 위해서는 실리콘 기판이 사용되지만 화합물 반도체인 LED 성장을 위해서는 다른 종류의 기판들이 사용된다.<sup>[7]</sup>

일반적으로 상용화된 LED 기판은 GaAs, InP, GaN, 사파이어(Al<sub>2</sub>O<sub>3</sub>)나 SiC 기판이며 LED 칩은 이들 기판 위에서 에피 성장하여 제작이 되나, 광효율 향상 및 고출력에 따른 특성 확보를 위해 새로운 기판을 사용하여 이들기판 위에서 에피 성장하는 방법이 연구 개발 중이다. 이러한 새로운 기판은 사파이어 및 SiC 기판에서 LED를 성장하는 현존하는 주요 선진업체인 니치아, 크리, 도요타고세이 등의 핵심 특허를 피할 수 있는 해결책이 될 수 있어 국내에서도 연구를 활발히 진행 중이다.

단결정을 성장하는 방법으로는 일반적으로 쵸크랄스키법(CZ, Czochralski method, 결정인상법)과 브리지만 방법(VB, Bridgman method)이 널리 쓰이고 있다. 이외에 플로팅존법(FZ, Floating zone method), 액체캡슐법(LE, Liquid encapsulated method), EFG법(Edgedefined film—fed growth method)등이 있다. 여러 가지 방법이 있지만 현재 양산에 사용되는 기판 제조방법은 GaAs와 GaN 기준으로 볼 때 CZ 방법이 널리 쓰이고 있다. CZ 방법은 Seed가 되는 작은 실리콘 단결정을 원료물질이 녹아 있는 Bath에서 천천히 회전을 하며 단결정을 생성시키는 방법이다. 최근의 결정성장은 CZ과

39 전자공학회지 2015, 1 \_ **39**

LEC 방법을 혼합하여 양산에 적용하고 있다. 사파이어는 InGaN/GaN LED의 기판으로 사용되는데 결정성장법은 수직-수평 온도구배법, 열교환법(HEM), CZ, EFG법, 베르누이법이 사용되고 있다.

수직-수평 온도구배법은 (VGF, vertical gradient freezing)은 전위밀도가 가장 낮은 고품질의 단결정을 성장시킬 수 있는 방법이다. 단결정의 크기의 제한이 없고, 형상의 제약 또한 없다.

열교환법(HEM, heat exchanger method)은 로의 내부구조에 따라 자연스럽게 형성되는 상하방향의 온도구배에 의해 단결정을 성장시키는 방법으로 장점은 대형 사파이어 제조가 가능하고 사파이어 품질이 우수한 것이다. 반면 단점으로는 길이와 직경의 비가 제한되며, 성장속도가 느리다는 점이다.

EFG법(Edge-defined flim-fed growth)은 도가니 내에서 용해된 모세관현상에 의해 좁은 틈 사이로 빨려 올라와 Seed와 접촉하면서 끌어올려져 단결정을 성장시키는 방법으로 다양한 형상이 가능하고 생산성이 높은 장점이 있다. 반면 품질이 다소 떨어지는 경향이 있으며 표면결합으로 인해 회수율이 떨어지고 두께의 제한이 따르는 단점이 존재한다.

베르누이법(Verneuil method)은 재료분말을 수소와 산소의 혼합가스 불꽃을 통과하면서 녹인 후 Seed 결정 위에 부착시켜 단결정을 성장시키는 방법으로 현재까지 사용되는 방법 중에 가장 쉬운 방법이며 생산성이 높은 장점이 있다. 하지만 내부결합과 크기의 제약(30 mm 이 하)이 따르며 원형의 잉곳(ingot)만 생산이 가능한 단점 이 있다.

〈표 1〉 각 기판별 물성 비교

|                                   | 격자         | 열팽창 | 특성        |          |    |      |          |  |

|-----------------------------------|------------|-----|-----------|----------|----|------|----------|--|

| 기판                                | 부정합        | 계수차 | 전기<br>전도성 | 열<br>전도성 | 가격 | 크기   | 습식<br>식각 |  |

| 사파이어                              | -16        | -34 | X         | X        | 0  | 2~4" | X        |  |

| SiC                               | 3.5        | 25  | 0         | 양호       | Δ  | 3"   | 0        |  |

| Si                                | -16.9      | 54  | 0         | 양호       | 0  | 12"  | 0        |  |

| GaN                               | _          | -   | 0         | 양호       | X  | 2"   | X        |  |

| ZnO                               | 2          | 48  | 0         | Δ        | Δ  | 1"   | 0        |  |

| β -Ga <sub>2</sub> O <sub>3</sub> | Monoclinic |     | 0         | _        | _  | 0.5" | Δ        |  |

위에 기술한 단결정 성장방법에 의한 기판들의 LED 제조 시 미치는 영향들과 특성들에 대하여 좀 더 살펴보기로 한다. GaAs 기반 LED와 달리 질화물계 LED에서 문제가 되는 것은 적절한 기판의 부재이다. 현재 질화물계 LED용으로 가장 많이 쓰는 것은 사파이어와 SiC 기판인데 이들은 에피층과의 격자부정합(lattice mismatch)과열팽창계수 차이로 인하여 생성되는 여러 가지 결합의 극복이 가장 큰 기술과제로 대두되고 연구되어지고 있다. 〈표 1〉에 각 기판별 물성 비교가 나타나 있다.

#### 가. 사파이어 기판

사파이어는 〈표 1〉에서 보는 바와 같이 격자 부정합이 크고 전기 부도체이며 열전도율이 낮고 다이싱(dicing) 비용이 높으나. GaN와 마찬가지로 육방정 구조를 가지 며 (0001)면의 결정학적 구조가 서로 유사하다. 사파이 어는 융점이 2050℃ 정도로 매우 높아 GaN과 같이 고온 증착해야 하는 박막의 기판으로 적합하고, 산이나 알칼리 에 쉽게 부식되지 않으므로 각종 습식 식각(wet etching) 에도 잘 견디며 가격이 상대적으로 저렴한 장점을 가지 고 있다. 하지만 GaN과 격자 부정합이 매우 크기 때문에 사파이어를 기판으로 하여 GaN 박막을 성장하면 계면에 서 격자 불일치로 발생하는 변위(dislocation)가 GaN 박 막 내부로 전파되어 LED 제조 시 소자 특성을 저하시키 는 결정적인 결함으로 작용한다. 지금은 LED의 효율이 상대적으로 높지 않아 사파이어 기판을 사용할 수 있지만 향후 고출력, 고효율의 LED를 제조할 때 열 방출 문제를 해결해야하는 큰 기술적 과제를 앉고 있다.

#### 나. SiC 기판

《표 1》에서 보는 바와 같이 SiC는 GaN과 격자부정합도 비교적 적고 열 특성이 우수해 GaN 박막을 성장하는 기판으로도 사용되고 있다. 하지만 SiC 기판은 사파이어기판 대비 10배 정도의 고가이고, 근자외선 영역인 411 nm 근처에서 광손실이 존재하며 기판의 굴절률이 낮아광추출 효율이 낮다. 또한 SiC는 간접 천이형 반도체로전자와 정공이 결합할 때 다량의 열을 발생하여 LED 제조에는 부적합하다고 알려져 있으나, 단결정 제조 기술이

GaN 및 ZnO등 다른 기판에 비해 워낙 앞서 있기 때문에 SiC를 기반으로 하는 LED 기술도 계속 연구될 전망이다.

#### 다. GaN 기판

사파이어 기판이나 SiC 기판은 〈표 1〉에 정리된 것처럼 청색 계열의 LED 반도체 재료인 GaN 화합물 반도체와 격자 상수의 차이가 상당히 크다. 이러한 GaN 화합물 반도체와 사파이어나 SiC 기판과의 격자 상수 차이로 인한 결함을 해결하기 위해 같은 종류인 GaN 화합물로 제작된 기판이 GaN 기판이다. GaN 기판은 동일한 종류의 재료를 사용하기 때문에 격자 불일치 문제를 해결할 수있어 저결함 특성을 지닌 고품질 에피 성장이 가능하나, 그 가격이 매우 고가로 실제의 양산까지는 많은 시간이 필요하다. 실제 이렇게 격자 상수가 일치하는 GaN 기판을 이용하여 2007년 마쓰시타는 당시 최고 수준인 청색

LED 개발을 발표한 바 있다. 비극성 GaN 기판은 위에서 언급한 격자 상수의 일치라는 큰 장점에도 불구하고 아직 자체적인 몇 가지의 문제점을 가지고 있다. 그 중 하나가 비극성 GaN 기판의 수급 문제인데, 통상적으로 m-GaN 기판은 (100)

LiAlO<sub>2</sub>(Lithium Aluminate) 상에서 성장된다. 그런데 이종 기판인 LiAlO<sub>2</sub> 가 고가이고, 비극성 GaN 기판 자체가 매우 비싸지면서도 실제 크기는 양산하기에는 너무 작다. 최대 ~5×10mm² 크기로 현재 실험실에서 연구의 수준이며, 아직 상용화에는 문제가 있다. 이러한 고가의 문제를 해결하기 위해 기존의 사파이어 기판을 사용한 LED 공정과 유사하게 진행할 수 있는 r-plane 사파이어를 이용한 a-plane GaN 기판이 연구 개발 중이다. 하지만 이러한 방법은 r-plane 사파이어를 이용하기 때문에 결정학적 차이에 기인한 a-plane GaN의 성장의 문제점이 여전히 존재한다. 즉 Ga과 N-face의 성장 속도의 차이에 의한 V-pit 형성으로 비극성 a-plane GaN의 표면 facet이 형성되고, 비등방성 격자(lattice: ~16% [1-100]& ~1% [0001]) 및 열적 부정합(thermal: ~25% [1-100] & ~0.1% [0001])에 의한 비극성 aplane의 결

정에 결함이 발생한다.

## 라. 무분극 기판

통상적으로 에피 성장에 사용되는 것은 c-plane 사파이어 기판인데, 이 기판에서는 자발적인 압전 (piezoelectric) 및 분극(polarization) 현상이 야기되며, 에너지 밴드를 휘게 만들고 양자 우물(quantum well)에서 전하의 분포를 분리시킨다. 이런 bending 현상은 양자 우물에서 전하의 분포가 분리되면서 발광의 적색 편이 현상이 나타나고 전자(electron)와 정공(hole)의 재결합효율이 낮아져 발광 효율이 낮아지고 높은 문턱 전류가 필요하게 된다. 이런 문제점은 사파이어 기판의 결정 방향을 고려한 무분극(non polar) 기판의 도입으로 해결의실마리를 찾아가고 있다. 무분극 기판에서 성장된 LED는 극성의 소멸로 양자 효율이 증가하고 ~7×10<sup>18</sup>/cm³ 정

도의 고농도 p-GaN 도핑이 가능하게 한다. p-GaN 도핑은 까다로운 LED 기술 부분이다. 자외선 LED는 AlInGaN p-형 도핑이 매우 어려워 파장이 짧아질수록 효율이 떨어지나, 무분극 기판에 의해 p-형 도핑이 용이해져 효율이 증가할 수 있

다. 또한 무분극 기판에 의한 LED는 편광범을 방출하여 LCD BLU에서 유효 범이 40~70% 정도 증가하고 출력에 따른 파장 변화가 없으며, 두꺼운 양자 우물이 가능해고출력 LED의 droop 현상 문제 해결에 도움이 된다. 반면 무분극 기판을 사용한 에피 성장은 매우 어려운 3차원표면에피 성장기술이어서 거울 같은 평탄한 표면을 제어하기가 매우 어렵고, stacking fault가 생성되고 변위가다량 발생하며 양호한 광학적 특성의 확보가 어렵다.

#### 마. ZnO 기판

〈표 1〉에서 볼 수 있듯이 ZnO 기판은 GaN와 격자 상수가 비슷하고, 결정 구조가 GaN 결정과 같은 우르자이트 구조(wurtzite structure)로 불리는 육각 기둥 모양의 결정 구조를 가지기 있고 전기 전도성이 좋아서, 일본 업계를 중심으로 연구 개발 중이다. 시판되고 있는 청

41 전자공학회지 2015, 1 **41**

광 추출 효율은 LED 칩으로부터

입력된 파워로 부터 광을 끌어내는 효율 이다. 광 추출의 중요성은

LED의 열효율 개선에도 매우 중요한

무제로 대두 되고 있다.

색 LED는 사파이어 기판 위에 성장시키는 GaN의 성장 면은 c-plane이라는 극성면을 이용한다. 즉 c-plane의 법선 방향(c축 방향)을 성장 축으로 하고 있다. 극성면을 이용하면 InN의 격자 상수가 GaN의 격자 상수보다 크 기 때문에 압전 효과가 생기고. 발광 시에 압전 효과에 의 해서 활성층에 주입한 전자와 정공이 공간적으로 멀어져, 재결합하는 확률이 줄어들기 때문에 발광 효율이 저하된 다. c-plane이라고 하는 극성면의 법선 방향의 면에 해 당하는 m-plane이나 a-plane 같은 무극성 면을 이용 하면 활성층에 생기는 압전 효과의 영향을 약하게 할 수 있다. ZnO 기판을 이용한 InGaN계 LED 소자는 청색만 이 아니고. 녹색이나 적색. 적외선이라고 하는 장파장용 LED 제조도 가능하다. 그 방법은 ZnO의 무극성 면을 이 용함으로써 압전 효과를 억제하거나 저온 성장 등에 의해 서 장파장을 만들기 위해 늘어난 인듐(Indium)양에 의한 상 분리 반응을 저온 성장으로 억제하는 것이다. 그러나 ZnO 기판을 이용함으로써 결정 결함이 적은 고품질인 무 극성 GaN 결정을 성장할 수 있지만 아직은 상용화하여 LED 소자의 생산까지는 도달하지 못했다. 그 걸림돌은 일반적인 제작 기법을 이용하여 1000℃에 도달하는 고온 하에서 GaN 결정을 성장시키면 ZnO와 GaN의 반응이 이루어져 화합물이 되어 높은 품질의 결정을 만드는 것이 매우 어렵기 때문이다.

#### 바, 실리콘 기판

실리콘 반도체의 잘 확립된 공정과 대면적화된 기판 등의 장점을 살리기 위해 실리콘 기판 위에서 GaN 질화물반도체 에피 성장을 하는 기술이 연구되고 있으나 아직상용화 되지는 못하고 있다. 〈표 1〉에서 볼 수 있듯이 격자 상수의 차이가 크고, 실리콘 기판 위에 GaN 반도체를 성장시킬 경우 2차원 성장 모드 보다는 3차원 성장 모드가 우선하여 평탄한 표면을 갖는 에피 성장이 어려운 본질적인 문제점이 있다. 버퍼충 등의 반도체 적충을 교대로 반복하여 두텁게 성장하면 평탄한 표면은 얻을 수 있으나 일정 두께 이상에서 과도한 Al 조성에 의한 스트레인 때문에 표면에 결함이 발생한다. 이러한 문제점을 해결하기 위해 성장 조건이나 구조 자체를 변경하기도 하

〈표 2〉 다양한 에피성장법의 특징 및 제한사항

| 성장방법  | 특징                   | 제한사항                          |  |  |

|-------|----------------------|-------------------------------|--|--|

| LPE   | 기판위에 과포화용액에<br>의한 성장 | - 제한된 기판크기<br>- 얇은 층의 성장제어    |  |  |

| VPE   | 이송재로 메탈할라이드<br>사용    | - AI 없는 화합물만 성장<br>- 두꺼운층만 성장 |  |  |

| MBE   | 초진공 상태 증착            | - 고 증기압을 갖는 재료의 성장            |  |  |

| MOCVD | 소스로 유기화합물 사용         | - 독성가스 사용(예, AsH3)            |  |  |

〈표 3〉 다양한 에피성장법의 장단점

| 성장방법  | 장점                               | 단점                            |  |  |

|-------|----------------------------------|-------------------------------|--|--|

| LPE   | - 고품질 재료 성장<br>- 정확한 합금조성, 저가격   | - 제한된 기판크기<br>- 얇은 층의 성장 곤란   |  |  |

| VPE   | - 고품질 재료 성장                      | - AI 없는 화합물만 성장<br>- 두꺼운층만 성장 |  |  |

| MBE   | - 고품질 재료 성장<br>- 원자적으로 급격한 계면 가능 | - 주의를 요하는 고가<br>성장기술          |  |  |

| MOCVD | - 비평형상태의 시스템으로 성장                | 00/12                         |  |  |

고, 버퍼층에 새로운 물질을 사용하는 성장 기술 등이 계속 연구되고 있다.

#### 3. 에피웨이퍼(Epi-wafer) 제조

에피택시(Epitaxy, Epitaxial growth)는 기초 소재인 단결정 기판위에 단결정 박막(Epilayer, Epitaxial layer) 을 성장하는 과정이다. 에피택시는 동종에피성장(Homo epitaxcy) 및 이종에피성장(Hetero epitaxcy)으로 분류 된다. 에피성장은 성장표면에서의 원자적, 분자적인 메커 니즘에 의해 일어난다. 표면으로 재료가 이송되고, 표면 에서 흡착(adsorption) 및 탈착(desorption)이 일어나고 표면확산(Surface diffusion)에 의해 원자 또는 분자들의 핵형성(necleation)에 의해 에피층이 성장된다.

화합물반도체의 주된 에피성장법은 Hydride 기상성장법(HVPE), 분자선 결정성장법(MBE), 유기금속기상성장법(MOCVD)등으로 분류된다. 각 성장법에 대한 특징과제한사항, 장단점이 〈표 2〉와 〈표 3〉에 정리되었다.

## 가. 다양한 에피 성장법

(1) MOCVD(Metal Organic Chemical Vapor Deposition)법

기본적으로 CVD 방법에 근거한 에피성장법이고. 단

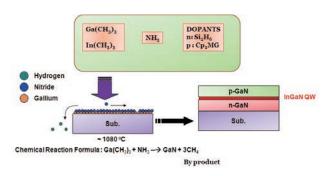

〈그림 2〉 MOCVD (Metal Organic Chemical Vapor Deposition) 방법에 의한 GaN 박막성장

지 Source로 유기금속을 쓰는 점이 다르다. MOCVD는 빠른 성장속도, 균일한 도핑, 재현성을 가져 양질의에피성장 방법이며에피성장 장치 중 가장 널리 사용되고 있다. 높은 생산성과 고진공이 필요 없어 경제적인 이점 및 높은 시스템 up—time을 갖는다. 또한 동일 시스템으로 여러 다른 물질을 성장할 수 있어 높은 유연성을 가지며 급격한 계면의 성장이 가능하여 이종접합구조 (heterostructure)의 성장에 적합하다. 예로 다층양자우물구조(Multiple Quantum Well, MQW)의 성장을 들을수 있다. 〈그림 2〉에 MOCVD 방법에 의한 개략적인 화학적 반응 현상이 도시되어 있다.

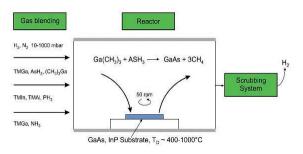

위에 도시한 GaN의 성장순서를 바탕으로 일반적인 MOCVD 공정순서를 설명해보면 다음과 같고. 시스템전체적인 흐름도가 〈그림 3〉에 나타나 있다.

- ① 유기금속(Ga(CH<sub>3</sub>)H<sub>3</sub>, In(CH<sub>3</sub>)H<sub>3</sub>) 및 수소화물 (NH<sub>3</sub>) 반응기(reactor) 안으로 주입

- ② 소스가 반응기 내에서 혼합되며 증착 영역으로 이동

- ③ 고온 증착 영역은 소스의 분해 및 기상반응이 일어 나고, 필름 전구체(precursor)가 형성

〈그림 3〉 MOCVD 시스템 구성도

- ④ 필름 전구체는 성장표면으로 이동

- ⑤ 필름 전구체가 성장표면위에 흡착

- ⑥ 필름 전구체는 성장지점으로 확산

- ⑦ 그 표면에서 박막원자는 표면반응을 통하여 성장 중 인 박막과 혼합된다.

- ⑧ 표면반응의 부산물(by−product, 3CH4)은 표면 밖 으로 탈착되다.

- ⑨ 부산물은 반응영역으로부터 멀리 떨어진 반응기 출 구쪽(Scrubbing system)으로 이동

#### (2) MBE(Molecular Beam Epitaxy)

고 진공에서 단 원소(예: Ga. In. As)를 가열하여 나오 는 분자살(molecular beam)을 기판 위에 증착하여 성장 시키는 방법이다. 일정 온도로 가열된 기판 표면에 증착 된 분자들이 열에너지에 의해 격자점 위치로 이동하여 결 정구조를 형성하게 된다. MBE에서는 분자살의 평균자유 행로(mean free path)가 길어 곧바로 기면 표면까지 도 달할 수 있어 비평형상태에서 성장되므로 기판과 에피층 사이의 물리적 성질(격자상수, 물질구조)이 다른 경우에 도 성장이 가능하다. MBE법은 유기금속가스 및 수소화 가스를 기판에 분사시켜 기판 임계면상에서 화학반응을 일으켜 생성된 화합물을 확산에 의해 기판 위에 성장시키 는 방법이다. 초고진공(10-11 torr 이하) 장치 내에서 원 료 물질을 증발시켜 기판에 증착시키는 물리적 증착기술, 즉 PVD 기술의 하나이다. MOCVD 공정은 성장물질의 이송체인 유기금속 화합물 및 수소화 화합물을 기판 표면 에서 열분해 해야하므로 기판온도가 높아야 되고 임계면 에서 열분해 되어 생성된 성장물질(예: GaAs)이 열평형 상태에서 확산 과정을 통해 기판표면에 성장된다. 그러 나 MBE는 상대적으로 낮은 온도에서 결정성장이 가능하 고 급준한 계면을 형성할 수 있어 매우 얇은 박막층 성장 에 유리하다. MO 소스를 사용하는 MOMBE법도 있는데 MOCVD와 같이 성장원소의 공급원으로 유기금속화합물 또는 수소화합물을 사용하나 고진공에서 미리 열분해하 여 원소들을 분자상태로 쏘아주므로 원리적으로는 MBE 에 가깝다.

43 전자공학회지 2015, 1 **43**

## (3) LPE(Liquid Phase Epitaxy)

Ga, In등의 녹는점이 낮은 금속을 사용하여 화합물반 도체의 얇은 층을 성장시키는 방법으로 발광다이오드. 레 이저다이오드 등의 제조에 사용된다. 이 기법에서는 먼 저 금속용액에 화합물반도체를 녹여서 포화시킨 후. 온 도를 낮투어 과포화의 용질을 기판면 위에 부착시켜 단결 정층을 성장한다. 기판면 위에 종류가 다른 여러 가지 반 도체 결정층을 성장시키는 경우에는 용액이 각각 들어 있 는 용기를 차례로 이동시켜 기판에 접촉시키게 되어 있는 그래파이트제의 슬라이드식 보드가 사용된다. 성장은 성 장하고자하는 반도체의 융점 바로 아래 온도에서 일어난 다. 기판위의 에피층 성장은 거의 평형상태에서 진행되며 천천히 균일하게 진행된다. 평형상태는 온도와 용매 내에

용해된 반도체의 농도에 크게 의존 한다. 액상으로부터의 층의 성장은 용매의 강제적 냉각에 의해서 제어 된다. Ga, In, Sn, Bi 등의 낮은 용 용점 금속을 용매로 하고, 이 단원 자에 석출물질(GaAs, InP)을 녹이 고, 온도차를 준 용매의 고온 측에

원료결정을 놓고 저온 측에 기판 결정을 놓아서 용해도가 높은 측에서 낮은 측으로 결정재료의 확산을 일으켜 원료 결정에서 기판 위로 박막성장이 가능하게 한다. 성장속도 는 기판과 용질간의 온도차에 의해 결정된다.

LPE 방법에 의한 화합물은 3원소(ternery)의 성장과 GaAs 기판의 4원소(quarternery) 3-5족 화합물이다. 주로 GaAs. GaP 생산에 사용된다.

#### (4) HVPE(Hydride Vapor Phase Epitaxy)

VPE는 결정재료가 포함된 반응가스를 기판위로 흘리 면서 열에 의한 분해와 반응을 통해 기판위에 결정을 성 장시키는 것으로서 반응가스의 원료형태에 따라 수소화 물 VPE(hydride VPE, HVPE), 할로겐화물 VPE(halide VPE). 유기금속 VPE(metal organic VPE, MOVPE)등 으로 분류된다. GaAs 성장에는 Ga/AsCl3,GaP의 경우 Ga/PCl3 계가 사용된다. 이 방법은 각 원소의 유량과 분 압의 제어가 어렵지만 비교적 재현성이 좋은 성장층을 얻 을 수 있기 때문에 GaAsP 결정 성장에 주로 사용된다. 최근에는 GaN계 LED의 동종에피를 위해 사용될 수 있 는 두꺼운 GaN의 성장에도 사용된다.

#### (5) ALE(Atomic Layer Epitaxy)

단 원자층 제어 결정 성장에 쓰이는 방법으로 1 원자층 의 결정성장이 진행되면 결정성장이 정지하는, '성장의 자기 정지 기구'를 수반하고 있는 것이 최대의 특징이며, 막 후의 제어성. 성장막의 기판상에서의 균일성이 지극히 우수한 것이 특징이다. 주로 2-6족 화합물반도체의 초 격자(superlattice) 제작에 이용 된다. 막 형성에 필요한 원소를 한번에 한 가지씩 증발시켜 ZnS 박막을 형성하 는 원자층 적층 성장(atomic layer epitaxy, ALE) 기술

> 은 1974년에 핀란드 특허가, 1977 년에 미국 특허가 등록되었지만 그 당시에는 큰 관심을 끌지 못하였다. 아마도 기존의 박막 형성 방법과 너 무 다르고 응용 분야가 특수하게 보 였기 때문이었을 것이다. 그러나 이

EL은 전계발광으로 소자에 전기장을 특히 저온에서 그 특성을 잘 나타내고 있고. PL과 더불어 전기와 광의 특성을 기술을 사용하여 핀란드의 Lohja

사가 ZnS:Mn을 사용하여 미국과 일본의 경쟁사 제품보 다 훨씬 뛰어난 대면적의 EL 표시 소자를 1980년대 초 에 내놓았고 이것이 1982년에 Society of Information Display 학회가 수여하는 기술상을 받은 이후 ALE 기술 은 고품질의 박막을 형성하는 방법으로 주목을 받기 시작 했습니다. 적층 성장이 아닌 경우도 포함하기 위해 더 일 반적으로 이 기술을 ALE가 아니라 원자층 증착(atomic layer deposition) 즉. ALD 기술이 라고 부르게 되었다. 본 기술은 실리콘 공정에서도 유용한 증착방법으로 활용 할 범위가 아주 넓다.

#### 나. MOCVD 장치를 이용한 에피성장기술의 주요 관점

## (1) p-GaN 성장 기술

LED의 에피에서 p-GaN의 성장 기술은 현재에도 여 전히 주요한 이슈 중의 하나이다. 일반적으로 n-GaN 층 이나 p-GaN 층 같은 클래딩(clading)층의 제작 시 Si와 Mg가 도핑 물질로 사용되는데. p-GaN 제작 시 도핑 물

44 **44** \_ The Magazine of the IEIE

가하면 빛을 발하는 현상이다.

잘 나타내고 있다.

질로 사용된 Mg 원자가 Ga 자리에 완전히 치환되지 않고 질소 원료로 주입되는  $NH_3$ 가 열분해된 수소와 결합하여 Mg-H 복합체를 GaN 층 내에 형성하여 106 ohm 정도로 높은 저항값의 절연 특성을 가진다. 이러한 이유로 p-GaN 제작은 많은 시간과 연구를 거쳐 1986년에 이르러서야 Mg-doped GaN 단결정층을 LEEBI 방식에 의해표면을 열처리하여 처음 성공하였다. 이 후 1992년에 이르러 성장된 Mg-doped GaN 단결정층을  $400^{\circ}$ C 이상에서 고온 열처리하여 캐리어 농도  $5 \times 10^{17}$ /cm³ 및 이동도  $10 \text{ cm}^2$ /V-sec 정도의 유용한 p-GaN을 제작하였다.

실제 Mg-doped p-GaN 층의 Mg 농도가 10<sup>19</sup> ~ 10<sup>21</sup>/cm<sup>3</sup> 정도인데 반해 열공정 후의 캐리어 농도가 ~5 × 10<sup>17</sup>/cm<sup>3</sup> 정도로. Si-doped n-GaN 층의 캐리어 농 도  $\sim 10^{19} / \text{cm}^3$  정도에 비하여 낮은 편이다. 이 때문에 저 항성 전극(ohmic contact) 형성 공정 중에서 전류의 원 활한 공급이 어려우며, 과도한 Mg 원자 또는 Mg-H 복 합체에 의하여 Mg-doped p-GaN 층의 발열을 야기하 고, 또 실제 LED에서 발광되어 방출되는 빛을 포획하 여 발광 효율을 저하시킨다. 일반적으로 LED의 열 발생 은 주로 저항 성분이 높은 p-GaN 층과 결정성이 나쁜 AlInGaN 다중양자 우물 구조에 의한 것이다. 그래서 이 러한 p-GaN 층의 불충분한 활성화로 인하여 투명 전극 같은 전기적 전도층의 도움이 필요하다. 한편, 다중 양자 우물 구조 표면에 다량의 V-pit 같은 결정 결함이 존재 하고 그 위에 p-GaN 층을 형성할 경우 피트가 p-GaN 층으로 전파되고, 피트 자체가 결정 결함의 통로가 되 어 Mg 원자가 내부 확산을 통해 발광층으로 주입되어 발 광 효율의 저하를 초래하며, 동작 시 과대한 누설 전류로 LED 자체가 파괴되기도 한다. 따라서 결정 결함을 줄여 표면 평탄도를 향상시키고 p-GaN 층의 캐리어 농도 ~5 × 10<sup>17</sup>/cm<sup>3</sup> 정도를 n-GaN 층의 캐리어 농도 ~10<sup>19</sup>/ cm<sup>3</sup> 정도로 향상시키는 획기적인 원천기술 개발이 절대 적으로 필요하다.

## (2) 저온 완충층 성장 기술

저온 완충충(buffer layer)은 사파이어 및 SiC 기판과 의 격자 상수(lattice constant) 및 열팽창 계수(thermal

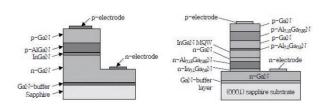

(그림 4) InGaN LED 소자구조(좌: SQW, 우: MQWs, 자료: 니찌아)

expansion coefficient)의 불일치에 의해서 발생하는 결정 결함(crystal defect)을 최소화하여 양질의 결정성을 갖는 GaN 질화물 반도체 에피 웨이퍼를 얻기 위해서 필요하다. 1992년 니치아사의 나카무라 등이 저온의 GaN 완충층을 적용하여 양질의 단결정 GaN 질화물 반도체를 성장시키는데 성공하였다. 관련된 단일양자우물(SQW)과 다중양자우물(MQWs)구조 소자의 에피 구조가 〈그림 4〉에 도식 되었다.

#### (3) AlInGaN계 활성층 성장 기술

휘도 및 신뢰성 향상을 위한 LED의 기술 혁신 중 하나 는 발광층의 내부 양자 효율을 향상시키는 것인데, 1995 년 상용화 초기에는 InGaN/GaN 또는InGaN/InGaN 형 태의 단일양자우물 구조를 적용하였다. 1999년 이후 활 성층 구조가 AlInGaN계 다중 양자 우물 구조로 변경되 었고, 2000년 이후 고휘도 제품이 요구되면서 발광층 자 체의 내부 양자 효율 향상을 기본으로 하여 n/p-AlGaN/ GaN 초격자 클래드층(superlattice clad layer)이 적용 되어 비약적인 발전을 하였다. 이렇게 발광층의 내부 양 자 효율을 향상시키기 위해서는 발광층 자체의 고품위 성 장 기술을 개발해야 하며. 그러하지 못할 경우 성장 초기 에 발생한 피트 같은 결정 결함은 성장 후 표면까지 전파 된다. 또 n/p-이종 접합 LED 구조는 압전효과가 발생 하여 발광 효율을 좌우하므로 이를 억제하는 성장 기술 이 필요한데, 발광층 자체가 스트레인(strain)을 발생시 키므로 외부에서 이러한 스트레인을 최소화하는 구조 개 발이 진행 중이다. 한편, 자외선 LED의 경우 사용되는 AlGaN/GaN계 활성층은 큰 격자 부정합으로 인한 응력 때문에 활성층 내부에 강한 전기장이 발생하여 전자-정 공 캐리어의 파동 함수가 분리되어 발광 효율이 저하되 는 문제가 발생한다. 이러한 내부 전기장은 활성층에 사

45 전자공학회지 2015, 1 \_ **45**

용되는 Al 조성 및 다중 양자 우물 구조 개수를 제한하여 발광 출력을 저하시킨다. 이러한 문제점을 극복하기 위한 4 성분계 AlInGaN 박막을 활성층에 사용하는 연구가 진행 중인데, 4 성분계 자료는 격자 상수와 에너지 밴드갭의 크기를 독립적으로 변화시킬 수 있기 때문에 이종 구조 형성 시 원하는 발광 파장을 격자 정합으로 유지하면서 조절할 수 있다는 장점이 있다. 또한 InGaN 박막에서의 In 상분리(phaseseparation)에 의한 캐리어 국지효과를 AlInGaN 박막에서도 얻을 수 있어 하부 질화물층의 높은 변위밀도(dislocation density)에도 불구하고 AlInGaN 박막에서의 발광 효율 증대효과를 기대할 수 있다

#### (4) 기타

변위는 결정의 성장 과정에서 나타나는 결정 결함인데 LED의 경우 통상적으로 변위 밀도는  $10^8 \sim 10^{10}/\mathrm{cm}^2$  정도이다. 변위 밀도는 발광 효율에도 커다란 영향을 미치는데, 발광 효율의 향상을 위하여 변위 밀도를  $1 \times 10^7/\mathrm{cm}^2$  정도 이하가 가능한 에피 성장 기술이 요구된다.

LED의 기본 광원인 적색, 녹색, 청색의 광원 중에서 청색과 적색을 발광하는 비교적 고효율의 LED는 존재 하나 발광 파장 대역이 550 nm 근처에서 발광하는 고효 율 녹색 LED가 아직 존재하지 않는다. 적색을 발광하는 AlGaInP 소재 LED는 650 nm 근처에서 최고의 효율을 나타내나 파장이 짧아지면서 효율이 급락하고, 청색을 발 광하는 InGaN 소재 LED는 380 nm 근처에서 최고의 효 율을 나타내나 파장이 길어지면서 효율이 떨어진다. 두 색상의 중간 지점인 550 nm 근처 녹색 영역에서 외부 양 자 효율이 10% 이하로, 현재로써는 고효율로 발광하는 녹색 LED는 개발되지 못하고 있다. InGaN의 경우, 높은 In 조성을 갖는 활성층을 성장하기 어려우며, c-plane 사파이어 기판을 사용함에 따른 내부 전계로 인하여 발 광 효율이 저하되는 단점이 있다. 하지만 고출력/고효율 을 갖는 green LED는 대형 디스플레이, LED TV, RGB 백색 조명, 감성 조명 등을 구현할 수 있는 필수적인 핵심 광원이므로, 고출력/고효율 green LED의 연구개발이 시 급하다.

정전기 방전(ESD)은 전위가 다른 두 물체 간에 정전기에 의한 유한한 양의 전하가 급속하게 이동하는 방전 현상으로, 외부 정전기에 의해 LED 내부 결함을 통하여 자체의 파괴를 초래한다. 일반적으로 이러한 파괴를 방지하기 위해 모바일 제품은 제너다이오드 등을 실장하여 정전기 방전을 회피하나 제품의 다양화 등에 일정한 한계가 있다. 기술적으로 보면 니치아, 크리, 도요타고세이 등의해외 선진업체 LED 제품의 내정 전압은 2 kV 이상이나대만이나 국내 제품은 아직 이에 미치지 못하고 있다. 이러한 정전기에 의한 파괴를 방지하기 위해서는 고품위 성장 기술과 최적의 LED 설계기술 확립이 필요하다.

## Ⅲ. 칩 제조

칩은 LED 개별 소자를 말하는 것으로, 칩 제작은 에 피 웨이퍼에 전극을 형성하고 절단하는 등의 공정을 통 하여 발광할 수 있는 최소의 단위 칩으로 만드는 단계이 다. 통상적으로 윗면인 p-형 반도체에 (+) 전극이 형성 되고, 절연체 기판 위에 전극이 형성될 수 없어 건식 식 각(drying etching) 방식으로 위에서 n-형 반도체 일부 분까지 식각하여 전극을 형성하는데. 이러한 방식은 보통 수평 전류가 흘러 전류 밀집 효과로 발광 효율이 저하된 다. 칩 구조의 예시가 그림 10에 도시되어 있다. 고출력 LED의 필요성에 따라 대면적 칩이 제작되고 있으나 발열 이나 광효율 및 생산 저하의 문제가 아직 존재한다. 니치 아는 작은 면적 칩을 적용하여 100 lm/W LED를 2007 년부터 양산하기 시작하였고. 루미레즈는 대면적 칩을 적 용하여 115 lm/W LED 개발을 2007년 발표하기도 했 다. 칩의 구조는 발광 효율을 극대화하는 방향으로 발전 해 왔다. 고출력 수직 칩의 제조와 관련된 공정기술에 대 하여 알아본다.

#### 1. 칩 구조 변경에 의한 고출력 LED 제조

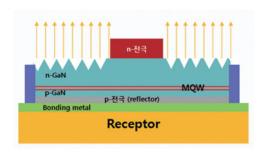

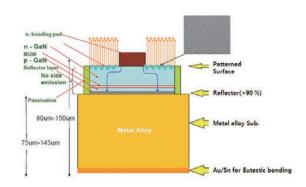

수직형(thin GaN) LED도 일반형 LED와 같은 발광의 기본 구조에서 식각에 의해 적충된 일부분을 제거하지 않 은 원래의 형태를 유지한다. 통상적으로 적충된 윗부분 의 클래딩층에 bonding/reflector와 receptor 기판을 차

〈그림 5〉 일반적인 수직 칩 구조도

례로 부착한 후, 전극을 형성하고 반대편의 기판을 분리한다. 분리된 기판의 클래딩층에 전극을 형성하면 수직형 LED의 기본 구조가 완성된다. 수직형 LED의 활성층에서 발광된 빛은 아래 면의 반사판에서 수직으로 반사되어 윗부분으로 방출되며, 방열 특성과 고출력 특성이 우수하다. 이렇게 칩의 형태는 변화하여 표준적인 형태로부터기판을 제거한 thin GaN 형태의 수직형에 이르기까지 발달하여 발광 효율이 3배 정도 증가하였다. 〈그림 5〉에 수직형 칩 구조도가 도시되어있다.

## 2, 표면 가공기술에 의한 광추출 증진

실제 LED 칩으로부터 발광할 때, LED 반도체 소재와 공기의 굴절률 차이로 인하여 활성층 내부에서 발광된 빛 이 일정 각도 이상이 되면 공기와의 경계면에서 내부로 전반사되어 외부로 발광이 되지 않는다. 광추출(optical extraction) 기술은 이러한 내부로의 반사를 막아 외부로 탈출하게 하여 방출되는 빛의 양을 향상시키기 위한 기술 이다.[8] 활성층에서 발광하는 빛이 공기와 반도체의 굴 절률 상관 차이에 의하여 표면에서 탈출한다. 광추출 효 율 면에서 보면 개략적으로 표면으로 방출되는 양이 약 8%. 기판에서의 손실이 약 20%. 칩 내부에서 가이드 되 는 양이 약 72% 정도로 추정된다. 따라서 사파이어 기판 을 제거하거나 LED 칩의 표면을 가공하여 빛을 탈출시키 면 많은 부분이 개선될 수가 있다. 광추출 효율을 향상시 키기 위해 다양한 기술들이 연구 개발 중인데, 최근에는 전도성 투명 전극이 사용되기도 한다. 이러한 전도성 투 명 전극은 가시광의 투과율이 매우 높기 때문에 전극 자 체에 의한 광손실이 거의 없고 굴절률이 GaN계 결정의 굴절률과 몰드 재료인 수지의 굴절률과의 중간 정도이기

〈그림 6〉 PSS 표면가공 모습

때문에 추출 효율을 대폭 향상시킬 수 있다. 다음은 다양 한 광추출 효율 향상 기술들에 대하여 알아본다.

#### 가. PSS 표면 가공 기술

PSS 표면 가공 기술은 사파이어 기판 표면에 일정한 형태의 형상과 깊이로 패터닝을 식각하여 사파이어 기 판 쪽으로 진행하는 빛을 굴절률 차이에 의해 외부로 방 출하는 방법이다. 요철을 형성한 사파이어 기판(PSS) 위 에 질화갈류을 성장시키면 활성층에서 발생한 빛이 요철 이 형성된 기판과 질화갈륨의 계면에서 난반사를 일으키 게 된다. 이를 이용하면 LED 내부에서 빛의 경로를 변 화시킬 수 있고 결과적으로 탈출확률이 증가하여 광 추 출효율을 개선시킬 수 있다. 이후 플립칩 LED에서도 사 파이어 표면에 포토 리소그래피(photo-lithography)를 이용한 요철 형성과 건식식각 기술을 이용해 광추출 효 율의 향상이 보고되었다. 최근에는 e-beam 리소그래 피(e-beam lithography). 레이저 홀로그램 리소그래 피(hologram lithography), 나노임프린트 리소그래피 (nano-imprinted lithography) 등의 나노사이즈의 마 스크형성 기술과 식각 기술의 발전으로 보다 정교하게 요 철을 형성하여 높은 광 추출효과를 얻고 있음이 보고되고 있다 [9-10]

PSS의 표면 가공의 모습이 〈그림 6〉에 나타나 있다.

#### 나. Top(n or p)-GaN Roughness 성장 기술

Top-GaN Roughness 성장 기술은 LED Top-GaN 표면 쪽에서 반사되어 내부로 재반사 되는 광 손실을 제 거하여 외부로 빛을 방출시키는 기술이다. 대만은 PSS 기술 대신에 Top-GaN 반도체 표면에 일정한 형상 및 깊이로 거칠기를 변화시키는 효율 향상 기술을 개발하였다. 대면적/고출력, 청색/녹색 및 power LED 제품에 적용되고 있는 성장 기술이나. PSS 기술보다 5 ~ 10 % 정도 효

47 전자공학회지 2015, 1 **47**

〈그림 7〉 Metal Alloy 기판을 사용한 수직 칩 Top(n-GaN) Pattern 구조

율은 낮다. 〈그림 7〉에 Metal base 수직 칩 구조에서의 적용 모습을 보여 주고 있다. 니치아나 도요타고세이 같 은 선진업체들이 적용하고 있다.

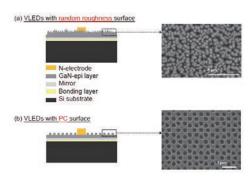

#### 다. PBC 기술

PBC 기술은 p-GaN 표면에 photonic band gap이 있는 photonic crystal에 의해 광추출 효율 증가시키는 기술이다. 이 방법은 p-GaN 전극 접촉 부분으로 방출되는 파장을 고려한 이론적 설계를 바탕으로 나노 형상의 주기적 패턴을 E-beam 노광과 ICP/RIE 식각 공정에 의하여형성한다. 최대 광추출은 패턴 깊이와 크기에 의해 결정되지만 전기적 특성까지 개선되는 것은 아니며, p-GaN층의 낮은 전기 전도도에 의해 광추출 효율 면에서는 일정 두께 이상을 요구하지만 동작 전압 등과 같은 전기적특성을 고려한 최적의 설계 조건이 필요하다. 청색

LED 소자의 경우 광추출 효율을 최대 30% 이상 증가 시킬 수 있지만 현재 상용화가 이루어지지 않고 있으며, 향후 고휘도/고출력 LED 성능 향상을 위해기술 개발이

〈그림 8〉 수직형 LED에서 PC 구조도와 패턴 사진

필요하다. 〈그림 8〉에 PC LED 구조와 패턴이 도식되어 있다.

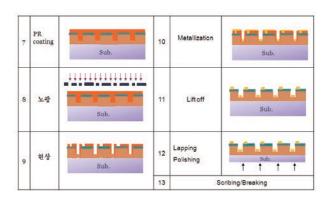

## 라. 칩 제조 공정

칩 제조 공정은 에피성장을 마친 wafer를 LED로 기능을 발휘할 수 있도록 칩 단위로 만드는 공정이다. 공정은 크게 전극 절연층 형성과정과 전극형성, 기판 래핑 (Lapping)과 Polishing, Sawing 공정으로 구분된다. 절연막 형성 공정과정이 ⟨그림 9⟩에 나타나 있다. 여기서 절연막의 역할은 n극과 p극의 분리를 위한 메사(mesa) 에칭 동안의 마스크로 사용된다. 에칭이 완료되면 습식 방식으로 절연막을 완전히 제거하고, RTA(rapid thermal annealing) 장비로 급속 열처리하여 격자손상을 보상한다.

전국 형성은 실리콘 공정에서와는 달리 LED 공정에서는 리프트 오프(lift off)공정으로 메탈전국을 형성한다. 〈그림 10〉에 공정 순서도가 도시되어있다. 먼저 일반적인 포토공정을 통해 원하는 패턴을 형성하고 Evaporation 방법에 의해 메탈을 증착한다. 증착 후 PR을 제거하면 PR 위에 금속은 사라진다. 메탈을 RTP 장비로 합금화하여 보호막을 입히면 금속배선을 형성하는 공정은 완료된다. 본 공정흐름은 실리콘 공정과 비교할 때 절연막, 에칭 공정이 하나 줄이는 효과적 메탈 형성 방법이다. 이를 lift off 공정이라 칭한다. 이 후 기판 래핑과 폴리싱 공정과 쇼잉(sawing) 공정을 통해 최종 개별 칩을 얻는다.

쇼잉에 경우 레이저를 사용하는 이유는 LED 칩이 매우 작기 때문에 쇼잉에 의한 칩 소모를 줄이기 위해 사용한

| 1 | 전극<br>절연막<br>중착 | LED Layer Sub.                             | 4 | Oxide<br>etching<br>(RIE) | LED 子丞<br>Sub. |

|---|-----------------|--------------------------------------------|---|---------------------------|----------------|

| 2 | 노광              | Mask + + + + + + + + + + + + + + + + + + + | 5 | GeN<br>etching<br>(ICP)   | LED子丞<br>Sub.  |

| 3 | 현상              | LED Layer Sub.                             | 6 | 절연막<br>제거후 RTA            | Sub.           |

〈그림 9〉 전극형성에서 절연막 형성과정 단계

〈그림 10〉 메탈 전극 및 칩 분리 공정

다. Test 역시 도중에 시험할 수 있는 단계가 없이 최종 공정이 완료 후에 시행한다 물론 이 시험을 통해서 칩의 파장별, 성능별 구분을 하게 된다.

# Ⅳ. 고출력 LED 패키지

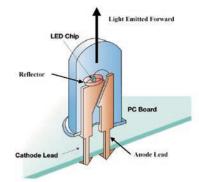

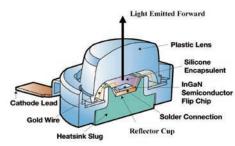

## 1. 플라스틱 패키징

기존의 LED 패키징은 주로 플라스틱 몸체를 가지 는 패키징이며, 기존의 정보표시 소자들은 리드프레임 (leadframe)에 에폭시 수지로 몰딩하는 램프형의 패키징 이 주로 사용되어 왔음. 이 경우 열방출은 전기적인 연결 을 수행하는 리드프레임을 통해서만 가능하므로 열방출 효과가 미흡하여 열저항이 매우 높게 되어 고출력 LED 용으로는 이러한 패키징은 적합하지 않다. 현재 대부분의 고출력 LED 패키징은 표면 실장형으로서 플라스틱 몸체 에 열전도도가 우수한 구리나 알루미늄 등의 금속 히트싱 크(Heat Sink)를 칩 하단 위치에 채용한 형태가 주류를 이루고 있다. 플라스틱 패키징은 패키징 몸체가 열전달이 어려운 플라스틱으로 이루어져 주로 리드프레임 만으로 열방출을 함 따라서 기존의 램프형 패키징의 열저항은 300℃/W 이하. 리드선의 개수가 4개이고 램프형 패키징 에 비해 굵은 Flux형 LED 패키징의 경우도 약 150 ℃/W 부근의 열저항을 가지고 있음. 그러나 LED 칩 하단에 금 속 히트싱크를 채용한 고출력 패키징의 경우 10℃/W 이 하로서 방열 성능이 매우 우수하다. 〈그림 11〉에 일반 램 프형 LED 패키징과 고출력용 LED 패키징 구조도가 도 시되어있다

(a) 일반 램프형 LED 패키징

(b) 고출력 LED 패키징

〈그림 11〉 일반 램프형 LED 패키징과 고출력용 LED 패키징 (출처:www.lumileds.com)

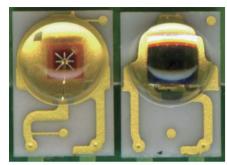

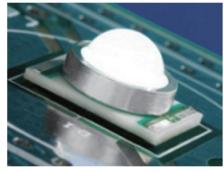

#### 2. 웨이퍼레벨 패키징(Wafer Level Packaging, WLP)

WLP는 웨이퍼 상태 및 반도체 FAB 공정에서 패키징 제조가 이루어지는 형태를 의미하며, 매우 사이즈가 작 고 다른 반도체 소자와도 집적화가 가능하다는 장점을 가 지고 있다. 실리콘 기반의 WLP는 실리콘 기판을 MEMS 공정으로 가공하여 패키지로 사용하며, 단결정 실리콘 기 판의 우수한 열방출 효과와 함께 소형 및 다중배열 형태 의 구조가 가능한 장점이 있다. 그러나 단결정 기판을 사 용하므로 습식 에칭 방법으로 식각하여 리플렉터를 제작 할 때 리플렉터의 각도를 마음대로 변경할 수 없는 단점 이 있다. 이에 비해 세라믹 기판을 기반으로 한 WLP는 박막 또는 후막으로 기판 표면에 패턴을 형성하고, 기판 표면을 식각하는 대신 평면상에 LED 칩을 실장하고 렌즈 를 성형하여 부착하는 형태로 대량 생산과 저가격화에 유 리한 방식으로 주목을 받고 있다. 〈그림 12〉에 실리콘 기 반의 LED 웨이퍼레벨 패키징(WLP) 제품을 도시하였다. 〈그림 13〉에는 세라믹 기반의 LED 웨이퍼레벨 패키징 (WLP) 제품이 도시되어 있다.

49 전자공학회지 2015. 1 \_ 49

XIOB (LG Innotek)

〈그림 12〉 실리콘 기반의 LED 웨이퍼레벨 패키징(WLP)

(a) Luxeon Rebel(Lumileds)

(b) XLamp(Cree)

〈그림 13〉 세라믹 기반의 LED 웨이퍼레벨 패키징(WLP)

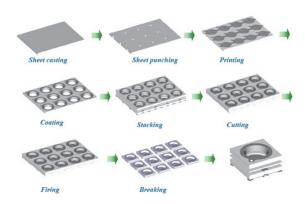

#### 3. 세라믹 적층 패키징

세라믹 적충 패키징은 패키지 몸체가 세라믹으로 이루어져 있는 것으로 기존 플라스틱 몸체에 비해 방열 성능이 우수하며, LED 칩과 유사한 열팽창 계수를 가지고 있어, LED 패키징 제조 중 또는 사용 중의 지속적인 온도변화에도 불구하고 장기적인 신뢰성이 우수하며 부피가작아 소형화가 가능하고 복잡한 배선 형성이 가능하다는 장점을 가지고 있다. 세라믹 패키징은 무기물 소재로서자외선에도 매우 안정하므로 자외선에 취약한 플라스틱패키징 대신 UV LED 응용에도 적용이 가능하고, 세라믹패키징의 열방출 효과를 더 높이기 위해 플라스틱패키징과 같은 방법으로 칩 하단부에 방열용 비아홀(thermal via)을 형성하거나 금속 물질(heat slug)을 부착하는 경

〈그림 14〉 세라믹 적층 LED 패키징 제조 공정도 (출처: Ceratech)

우도 증가하고 있다.

적층 세라믹 패키징은 적층 및 후막 제조공정을 이용하여 LED 패키지의 몸체와 리드선을 제조한 것으로 기존에 사용되던 통신용 세라믹 인덕터나 콘덴서, 필터 등과 제조공정이 매우 유사하며 1,000℃ 이하에서 소결이가능한 LTCC(Low Temperature Co-fired Ceramics)소재와 고온 소결이 필요한 알루미나( $Al_2O_3$ )와 같은 HTCC(High Temperature Co-fired Ceramics)소재로나눌 수 있다.  $\langle$ 그림 14〉에 세라믹 적층 LED 패키징 제조 공정의 흐름도가 도시되어 있다.

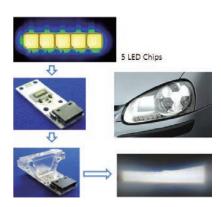

#### 4. Multi-chip 패키징

최근 단위 패키징 내에 여러 개의 칩을 실장하여 고출력을 내는 조명으로 사용하려는 시도가 많아지고 있다. 따라서, 한 개의 패키지 내에 여러 개의 칩을 내장하기 위해 Substrate type의 LED 패키징의 개념을 확장한 형태의 패키징이 개발되고 있다. 향후 조명 출력이 계속적

〈그림 15〉 Multi-chip 패키징을 이용한 자동차 전조등 (출처: Osram)

50 \_ The Magazine of the IEIE 50

으로 향상되면서 그 수요는 더욱 늘어날 가능성이 큰 것 으로 전망된다. 대표적인 패키징이 자동차용 헤드라이트 용으로 개발되고 있는 Osram의 Ostar인데 이 패키징은 AIN 기판상에 금속 패턴을 형성하고 5개의 LED 칩을 부 착한 것이다. 〈그림 15〉에 Multi-chip 패키징을 이용한 자동차 전조등의 모습이 도시되어있다.

# 5. 금속 패키징(Metal Packaging)

금속 패키징은 패키지의 몸체를 열전도도가 낮은 플라 스틱을 사용하는 대신 열전도도가 높은 구리나 알루미늄

과 같은 금속을 사용하여 패키지의 방열특성을 극대화한 패키징이다(< 그림 16〉참조). 금속 몸체의 가공 은 기계 가공으로 제조하기 어려우 므로 금속분말 사출성형법을 많이 이용하고 있다. 이 방법은 금속 분말 을 유기 바인더와 혼합하고 사출성

형법으로 성형한 뒤 바인더를 제거하고 소결하는 공정을 거쳐 제조하는 방법을 사용한다. 단순한 사출성형만으로 는 매끄러운 외관이 나오지 않아 2차 가공으로 외관의 치 수 등을 다시 조절하여야 하는 경우가 발생하기도 한다.

#### 6. COB(Chip on Board)

LED 모듈에서의 열방출은 소재 자체의 열전도도에도 영향을 받지만 소재와 소재간의 계면에서의 접촉저항에 의해서도 큰 영향을 받게 된다. 따라서 LED 모듈을 구성 하는 여러 요소 중에서 일부 제거하거나 두 가지 구성요 소를 일체형으로 만들어 열저항을 저감하는 기술에 대한 연구개발이 진행되고 있다. 이중에서 패키지와 PCB 기 판을 일체화한 것이 COB이며, 이는 칩을 패키지 내부에

〈그림 16〉 고출력 LED용 금속 패키징 (출처: Intops)

〈그림 17〉 열저항 감소를 위한 COB 기술로 제작된 60W High power LED

실장하고 밀봉하여 제조하는 대신에 PCB 기판 위에 직 접 칩을 실장하고 그 위에 렌즈를 성형하는 방식을 사용

> 한다. 이러한 패키징은 칩에서 발 생한 열이 유출되는 경로를 줄임으 로써 전체적인 방열효과를 증대시 키는 데 유리한 장점이 있으며 패 키징 자체의 높이가 줄어들게 된 다. 〈그림 17〉에 열저항 감소를 위 한 COB 기술로 제작된 60W High

power LED를 도시하였다.

## Ⅴ. 맺음말

열 저항은 LED 소자를 제작 시 열의

위해서는 열의 근원이 무엇인지 잘

파악해야한다.

근원이 되는 저항 성분이다. 하나의 양질의 LED를 제작하기

> 고출력 LED 소자 제작 부분에서 기판과, 에피성장, 칩 제작, 패키지에 관한 4 가지 부분에 대하여 중요 사항에 관하여 요약 정리해 보았다. 실리콘 공정도 마찬가지이 지만 아무리 훌륭한 개념과 설계가 있더라도 이를 실현해 주는 공정기술이 뒷받침 되지 않으면 상품 또는 제품으로 현실화 할 수 없다. 결국 LED는 기존의 실리콘 장비들을 효율적으로 이용하면서 더욱 더 큰 사이즈 웨이퍼 생산기 술 확보, 광추출 효과 향상에 의한 열 방출문제 및 휘도문 제 해결 등이 시급하다.

#### 참고문헌

- [1] "Light Emitting Diodes (LEDs) for Generating Illumination," OIDA Technology Road Map Update 2002, 2002.

- [2] Manning Fan et al., "Color Filter-less Technology of LED Back Light for LCD-TV,"Proc. SPIE, Vol.6841, 2007, pp.68410G1-68410G6.

51 전자공학회지 2015. 1 \_ 51

- [3] 장선호, 권영희, "LED 산업동향 및 정책추진 방향," IT SoC Magazine, Vol.31, 2009, pp.9-14.

- [4] 손원국, "조명용 LED 시장의 개발 현황 및 사업화 동향," 전자부품, Vol.259, 2009, pp.20-26.

- [5] 산업교육연구소, LED 부품소재 기술 · 시장 편람, 2008.

- [6] 백종협, 황남, 송상빈, 조용익, 유영문, "LED의 기초와 응용," 광학과 기술, Vol.11, 2007, pp.21-38.

- [7] 이영국, "LED 기판 재료의 연구 개발 동향," 전자부품, Vol.259, 2009, pp.52-57.

- [8] V. Coffey, "Microlens Array Improve the Extraction Efficiency of Nitride LEDs," Laser Focus World, Vol.44, 2008, pp.29-30.

- [9] S. J. Chang et al., Appl. Phys. Lett. 91, 013504 (2007).

- [10] D. S. Wuu et al., IEEE Photon. Technol. Lett. 17, 288 (2005).

권성훈

- 2000년 2월 서울시립대학교 전자전기공학 학사

- 2002년 2월 서울시립대학교 전자전기컴퓨터공학 석사

- 2012년 8월 서울시립대학교 전자전기컴퓨터공학 박사

- 2002년 3월~2006년 11월 팬택앤큐리텔 중앙연구소 전임연구원

- 2007년 11월~2009년 4월 FIH KOREA (FOXCONN) 서울연구소 책임연구원

- 2009년 4월~2011년 6월 (주)멜파스 / Cypress semiconductor 책임연구원 /부장

- 2013년 3월~현재 (주) 한국플렉스 / (주)대화 기업부설연구소 연구소장

〈관심분야〉 반도체공정, 태양전지 반사방지막, 박막증착, NCS 교육과정

**52** The Magazine of the IEIE