Journal of the Korea Institute of Information and Communication Engineering

한국정보통신학회논문지(J. Korea Inst. Inf. Commun. Eng.) Vol. 19, No. 2: 401~406 Feb. 2015

### 채널길이에 대한 비대칭 이중게이트 MOSFET의 문턱전압이하 스윙 분석

정학기\*

## Analysis of Subthreshold Swing for Channel Length of Asymmetric Double Gate MOSFET

#### Hakkee Jung\*

Department of Electronic Engineering, Kunsan National University, Gunsan 573-701, Korea

#### 요 약

본 논문에서는 비대칭 이중게이트(double gate; DG) MOSFET의 채널길이에 대한 문턱전압이하 스윙의 변화에 대하여 분석하였다. 문턱전압이하 스윙은 트랜지스터의 디지털특성을 결정하는 중요한 요소로서 채널길이가 감소하면 특성이 저하되는 문제가 나타나고 있다. 이러한 문제를 해결하기 위하여 개발된 DGMOSFET의 문턱전압이하 스윙의 채널길이에 대한 변화를 채널두께, 산화막두께, 상하단 게이트 전압 및 도핑농도 등에 따라 조사하고자 한다. 특히 하단 게이트 구조를 상단과 달리 제작할 수 있는 비대칭 DGMOSFET에 대하여 문턱전압이하 스윙을 분석함으로써 하단 게이트 전압 및 하단 산화막 두께 등에 대하여 자세히 관찰하였다. 문턱전압이하 스윙의 해석학적 모델을 구하기 위하여 포아송방정식에서 해석학적 전위분포모델을 유도하였으며 도핑분포함수는 가우스분포함수를 사용하였다. 결과적으로 문턱전압이하 스윙은 상하단 게이트 전압 및 채널도핑농도 그리고 채널의 크기에 매우 민감하게 변화하고 있다는 것을 알 수 있었다.

#### **ABSTRACT**

The change of subthreshold swing for channel length of asymmetric double gate(DG) MOSFET has been analyzed. The subthreshold swing is the important factor to determine digital chracteristics of transistor and is degraded with reduction of channel. The subthreshold swing for channel length of the DGMOSFET developed to solve this problem is investigated for channel thickness, oxide thickness, top and bottom gate voltage and doping concentration. Especially the subthreshold swing for asymmetric DGMOSFET to be able to be fabricated with different top and bottom gate structure is investigated in detail for bottom gate voltage and bottom oxide thickness. To obtain the analytical subthreshold swing, the analytical potential distribution is derived from Possion's equation, and Gaussian distribution function is used as doping profile. As a result, subthreshold swing is sensitively changed according to top and bottom gate voltage, channel doping concentration and channel dimension.

키워드 : 비대칭 이중게이트, 문턱전압이하 스윙, 포아송방정식, 채널길이

Key word: asymmetric double gate, threshold voltage, Poisson equation, channel length

접수일자: 2014. 11. 07 심사완료일자: 2014. 11. 13 게재확정일자: 2014. 11. 28

\* Corresponding Author Hakkee Jung(E-mail:hkjung@kunsan.ac.kr, Tel:+82-63-469-4684) Department of Electronic Engineering, Kunsan National University, Gunsan 573-701, Korea

Open Access http://dx.doi.org/10.6109/jkiice.2015.19.2.401

print ISSN: 2234-4772 online ISSN: 2288-4165

©This is an Open Access article distributed under the terms of the Creative Commons Attribution Non-Commercial License(http://creativecommons.org/li-censes/by-nc/3.0/) which permits unrestricted non-commercial use, distribution, and reproduction in any medium, provided the original work is properly cited. Copyright © The Korea Institute of Information and Communication Engineering.

#### Ⅰ. 서 론

집적회로에서 사용하고 있는 반도체소자의 개발은 궁극적으로 초소형화가 최종 목표이다. 반도체소자가 소형화되면 될수록 소비전력의 감소 및 고주파영역에 서의 동작 등이 가능하므로 세계적인 유명 반도체업체 들은 반도체소자의 소형화에 막대한 연구비를 투자하 고 있다. 뿐만 아니라 반도체소자의 소형화는 결과적으 로 집적회로의 소형화를 유도하여 생산성향상 및 가격 경쟁력 제고로 이어질 수 있다. 우리나라 역시 명실 공 히 반도체메모리분야에서 세계적인 중심에 서 있으며 스마트폰 및 테블릿 PC 등 모바일 장치의 확산에 따라 모바일 마이크로프로세서 등 경쟁력 있는 상품의 개발 에 주력하고 있다. 반도체소자 중에서도 가장 중요한 트랜지스터의 크기감소는 메모리용량이 기가바이트에 서 테라바이트로 기하급수적으로 증가하면서 필연적인 사항이 되었다. 전술한 바와 같이 트랜지스터의 크기감 소는 트랜지스터의 성능을 향상시키면서 생산성을 증 대시킨다는 장점이 있지만 단채널효과의 증가라는 단 점도 도출되고 있다[1]. 기존의 CMOSFET는 단일 게이 트 소자로서 10 나노이하 단위로 게이트길이를 제작하 는데 한계를 갖고 있다. 10 나노이하로 게이트를 제작 하였을 때 스켈링 이론에 의하여 게이트 산화막 두께가 너무 작아져 게이트단자로 기생전류가 흐를 수 있으며 채널의 도핑농도 증가에 의한 유효이동도의 감소 등 트 랜지스터 동작에 심각한 영향을 미치고 있다. 특히 문 턱전압이하 스윙특성 저하, 문턱전압의 이동, 드레인유 도 장벽감소 현상 등 단채널효과가 크게 나타남으로써 CMOSFET를 나노소자로 사용하기 어려운 상황이다.

이러한 문제점을 해결하기 위하여 연구/개발되고 있는 트랜지스터가 다중게이트 MOSFET(Multi Gate MOSFET; Mug FET) 소자이다[2,3]. 채널주변에 게이트단자를 2개 이상 제작하여 궁극적으로 단채널이지만게이트단자에 의한 전류제어 능력을 향상시키며 채널도핑을 낮게 하여 채널에서의 불순물산란 현상을 감소시켜 이동도를 증가시킬 수 있다. MugFET 중에 가장활발히 연구되고 있는 소자는 FinFET와 이중게이트 (double gate;DG) MOSFET이다[4,5].

기존의 CMOSFET는 20nm이하에서 심각한 단채널 효과 때문에 더 이상 소자를 미세화하는데 어려움을 겪 고 있다. 그러나 최근 생산성향상 및 소자성능향상 그 리고 가격경쟁력 향상 등을 이유로 소자의 미세화는 필 연적인 요소가 되었다. 이러한 상황에 가장 부합된 소 자로서 개발되고 있는 것이 DGMOSFET 소자이다. 그 동안 연구되고 있는 대칭적 구조의 DGMOSFET 해석 은 상하단 게이트의 구조를 반드시 동일하게 제작하였 을 경우만 가능하였다. 이에 본 연구에서는 대칭적 구 조가 아닌 비대칭적 구조를 가진 DGMOSFET에서도 사용가능한 문턱전압이하 전류전송모델을 제시하고자 한다. 이를 위하여 Ding 등의 모델[6]을 기반으로 해석 학적 전위모델을 제시할 것이며 문턱전압이하 스윙 모 델을 해석학적으로 제시하고자 한다. 제시한 문턱전압 이하 스윙 모델을 이용하여 하단게이트 전압, 채널길이, 채널두께, 상하단 산화막 두께 등에 따른 문턱전압이하 스윙의 변화를 고찰할 것이다.

### Ⅱ. 비대칭 DGMOSFET의 전위분포 및 문턱전 압이하 스윙 모델

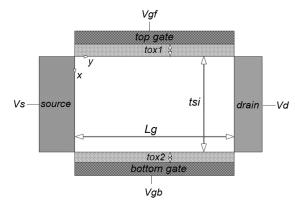

그림 1. 비대칭 이중게이트 MOSFET의 개략도

Fig. 1 Schematic sectional diagram of asymmetric double gate MOSFET

그림 1은 비대칭 DGMOSFET의 개략도이다. DG MOSFET는 주로 3단자(3T) 소자로 사용하기 위하여 대칭적 구조를 갖는다. 즉 상하단의 게이트에 동일한 전압을 인가할 수 있도록 상호 연결시켜 사용하고 있다. 그러나 상단과 하단 게이트의 역할을 구분함으로써 전류제어 능력을 향상시키고자하는 노력을 하고 있다. 이에 부응하기 위하여 개발된 소자가 그림 1과 같은 비대칭 DGMOSFET이다. 비대칭 DGMOSFET는 상단과 하

단 게이트 단자에 전압을 각각 별도로 인가할 수 있고 상단과 하단의 게이트 산화막을 다르게 제작할 수 있 는 4단자(4T) 소자이다.

Ding 등[6]은 비대칭 DGMOSFET의 표면전위 및 문 턱전압이하 스윙특성을 해석하기 위하여 포아송방정식 을 풀어 해석학적 전위분포를 구하였다. 그러나 그들은 채널도핑농도를 일정하게 유지하면서 식 (1)의 포아송 방정식을 이용한 해석학적 전위분포를 구하였으나 본 연구에서는 채널도핑 시 주로 사용하는 이온주입법에 서 발생하는 식 (2)와 같은 가우스분포함수를 도핑분포 함수로 사용하여 전위분포를 구하였다[7].

$$\frac{\partial^2 \phi}{\partial x^2} + \frac{\partial^2 \phi}{\partial y^2} = \frac{q n(x)}{\epsilon_S} \tag{1}$$

$$n(x) = N_p \exp \left(-\frac{(x - R_p)^2}{2\sigma_p^2}\right) \tag{2}$$

여기서  $\epsilon_{si}$ 는 실리콘의 유전율이며 n(x)는 채널 내도핑분포함수이다. 이때 다음 조건과 같은 경계조건을 이용한다.

$$\begin{split} \phi(x,y=0) &= V_s \\ \phi(x,y=L_g) &= V_s + V_d \\ \phi(x=0,y) &= V_{gf} + \frac{\epsilon_S}{C_{ox1}} \frac{\partial \phi}{\partial x} |_{x=0} \\ \phi(x=t_S,y) &= V_{gb} - \frac{\epsilon_S}{C_{ox2}} \frac{\partial \phi}{\partial x} |_{x=t_S} \end{split} \tag{3}$$

여기서  $V_s$ 는 기준전압인 소스 전압,  $V_d$ 는 드레인 전압,  $V_{gf}$ 는 평탄전압을 고려한 상단 게이트 전압,  $V_{gh}$ 는 평탄전압을 고려한 하단게이트 전압, 그리고  $C_{ox1}$ 과  $C_{ox2}$ 는 각각 상단과 하단 게이트 산화막의 커패시턴스 값이다. 경계조건의 처음 두 개의 식을 이용하여 식 (1)을 풀면 다음과 같은 급수형태의 전위분포를 구할 수 있다[6].

$$\phi(x,y) = V_s + \frac{V_d}{L_g} y + \sum_{n=1}^{\infty} A_n(x) \sin \frac{n\pi y}{L_g}$$

(4)

$$\begin{split} A_{n}(x) &= C_{n}e^{k_{n}x} + D_{n}e^{-k_{n}x} + B_{1}erf\left(\tau + b_{1}/2\right) \\ &+ B_{2}erf\left(\tau + b_{2}/2\right) + A \end{split} \tag{5}$$

이며 여기서 n은 정수,  $k_n=n\pi/L_g$ 이며  $V_s$ 는 소스 전압,  $V_d$ 는 드레인 전압,  $A_n(x)$ 에 나타나는 상수는 참고문헌[8]에 표기하였다.

이때 상단 게이트 전압  $V_{gf}$ 에 대한 문턱전압이하 스윙은 식(4)를 이용하면 다음과 같이 표현할 수 있다. 즉,

$$S = \frac{\partial V_{gf}}{\partial (\log_{10} I_d)} = 2.3 V_t \left[ \frac{\partial \phi(x,y)}{\partial V_{gf}} \right]^{-1}$$

$$= 2.3 V_t \left[ \sum_{n=1}^{\infty} \frac{2}{n\pi} (1 - (-1)^n) \left( \frac{a_4 e^{k_n x} - a_3 e^{-k_n x}}{a_1 a_4 - a_2 a_3} \right) \right]^{-1}$$

$$\bullet \sin \frac{n\pi y}{L_g}$$

(6)

이다. 여기서 계수는

$$\begin{split} &a_{1} = 1 - k_{n}\epsilon_{S}/C_{ox1} \\ &a_{2} = 1 + k_{n}\epsilon_{S}/C_{ox1} \\ &a_{3} = e^{k_{n}t_{S}} + \epsilon_{S}k_{n}e^{k_{n}t_{S}}/C_{ox2} \\ &a_{4} = e^{-k_{n}t_{S}} - \epsilon_{S}k_{n}e^{-k_{n}t_{S}}/C_{ox2} \end{split}$$

이다.

문턱전압이하 스윙을 구하기 위하여 식 (6)의 y에 상 단게이트의 표면전위 중 최소값을 갖는  $y_{\min}$  값을 구하여 대입하며 x는 다음과 같은 식에서 전도중심  $x_{eff}$  값을 대입하여 문턱전압이하 스윙값을 구한다.

$$x_{eff} = \int_{0}^{t_{si}} x e^{q\phi(x, y_{\min})/kT} dx / \int_{0}^{t_{si}} e^{q\phi(x, y_{\min})/kT} dx$$

(7)

여기서 k는 볼쯔만상수이며 T는 절대온도이다.

식 (4)의 전위분포는 채널길이, 채널두께, 하단게이 트 전압 그리고 도핑농도 등에 따라 변화하므로 이를 이용하여 유도되고 있는 식(6)의 문턱전압이하 스윙값역시 이 들값에 따라 변화한다는 것을 알 수 있다. 그러므로 본 연구에서는 비대칭 이중게이트 MOSFET의 채널길이에 대한 문턱전압이하 스윙 값의 변화를 채널두께, 하단게이트 전압 그리고 산화막 두께 및 도핑농도등을 파라미터로 하여 분석하고자 한다.

# Ⅲ. 비대칭 DGMOSFET의 문턱전압이하 스윙 결과 분석

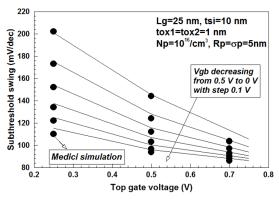

그림 2. 상단게이트 전압에 대한 문턱전압이하 스윙 값의 변화 Fig. 2 The change of subthreshold swing for top gate voltage

식(6)의 문턱전압이하 스윙에 대한 타당성을 증명하기 위하여 2차원 수치해석학적 시뮬레이션인 Medici 시뮬레이션의 결과[6]와 비교한 그래프를 그림 2에 도시하였다. 결과적으로 2차원 시뮬레이션값과 잘 일치하는 것을 알 수 있으므로 식(6)은 타당하다고 사료된다. 그림 2에서 알 수 있듯이 상단게이트 전압이 증가할수록 문턱전압이하 스윙은 감소하며 하단게이트 전압이 감소할수록 문턱전압이하 스윙은 감소한다. 비대칭 DGMOSFET는 하단게이트 전압을 별도로 인가할 수 있으므로 가능하면 하단게이트 전압은 작게 인가하고 상단게이트 전압은 크게 인가하여야 문턱전압이하 스윙을 감소시킬수 있다.

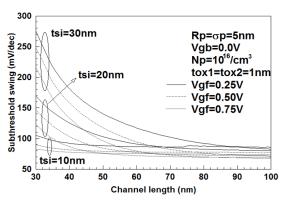

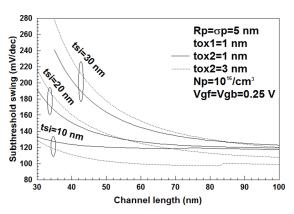

상단 게이트 전압 및 채널두께 변화에 대한 문턱전압이하 스윙의 변화를 채널길이에 대하여 관찰한 결과를 그림 3에 도시하였다. 그림 2에서 관찰한 바와 같이 상단 게이트 전압이 증가할수록 채널두께에 관계없이 문턱전압이하 스윙은 감소하는 것을 알 수 있다. 그러나채널길이가 증가하면 상단 게이트 전압의 변화에 대한문턱전압이하 스윙의 변화는 매우 감소하게 된다는 것을 그림 3에서 알 수 있다.

채널길이가 감소하면 단채널효과에 의하여 문턱전 압이하 스윙이 증가하는 문제점이 나타나며 채널두께 가 증가할수록 문턱전압이하 스윙특성이 크게 저하되 는 것을 관찰할 수 있다.

**그림 3.** 상단 게이트 전압과 채널두께를 파라미터로 계산한 채 널길이에 대한 문턱전압이하 스윙 값의 변화

Fig. 3 The change of subthreshold swing for channel length with parameters of top gate voltage and channel thickness

채널두께가 증가하면 문턱전압이하 스윙이 크게 증가하는 단채널효과가 발생하며 채널두께가 작아지면 채널두께에 대한 채널길이가 상대적으로 길어져 단채 널효과가 감소하는 효과가 나타나고 있다. 특히 채널길이가 작아지면 상단 게이트 전압이 변화하여도 문턱전압이하 스윙이 크게 변화하지 않는다는 것을 알 수 있다. 하단 게이트 전압 및 채널두께 변화에 대한 문턱전압이하 스윙의 변화를 채널길이에 대하여 계산한 결과를 그림 4에 도시하였다.

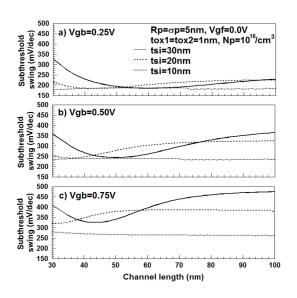

하단 게이트 전압이 증가하면 문턱전압이하 스윙이 증가하며 특히, 채널두께가 30 nm의 경우 채널길이가 50 nm 이상에서 문턱전압이하 스윙이 증가하는 경향을 보이고 있다. 채널두께가 감소하면 이와 같은 경향은 감소하나 하단 게이트 전압이 0 V 일 때 보다 문턱전압이하 스윙이 증가한다. 채널두께가 감소하면 채널길이에 따라 문턱전압이하 스윙이 거의 변화가 없다는 것을 그림 4에서 관찰할 수 있다.

전술한 바와 같이 비대칭 DGMOSFET는 상단과 하단의게이트 산화막 두께를 달리 제작할 수 있다. 하단게이트 산화막 두께가 변화할 때, 문턱전압이하 스윙의변화를 그림 5에 채널두께를 파라미터로 도시하였다.채널두께에 대한 변화는 그림3과 동일하지만 하단 산화막 두께에 대한 문턱전압이하 스윙의 변화는 채널두께에 따라달리 나타나는 것을 관찰할 수 있다. 즉, 채널두께가 30 nm일 때는 하단 산화막 두께가 클 때 문턱전압이하 스윙이 증가하나 채널두께가 20 nm일 때는 하단

산화막 두께가 클 때 채널길이가 약 55 nm 이하에서는 문턱전압이하 스윙이 증가하나 채널길이가 증가하면 감소하는 경향을 나타낸다.

**그림 4.** 하단 게이트 전압과 채널두께를 파라미터로 계산한 채 널길이에 대한 문턱전압이하 스윙 값의 변화

Fig. 4 The change of subthreshold swing for channel length with parameters of bottom gate voltage and channel thickness

또한 채널두께가 10 nm 이하로 감소하면 채널길이가 30 nm이상에서 하단 산화막 두께가 커질수록 문턱 전압이하 스윙은 감소하는 경향을 보이는 것을 알 수 있다. 이와 같이 채널길이와 채널두께의 비에 따라 하 단 산화막 두께가 문턱전압이하 스윙에 미치는 영향이 변화한다는 것을 관찰할 수 있었다.

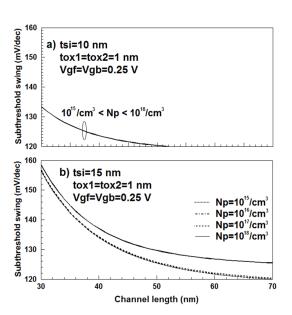

채널 도핑농도 및 채널두께에 대한 문턱전압이하 스 왕의 변화를 그림 6에 도시하였다. DGMOSFET는 채널의 실제 크기가 매우 작아 도핑농도가 적을 경우 실제불순물의 양은 극히 작아지게 된다. 그림 6a)에서 알 수 있듯이 채널두께가 10 nm로 작을 경우, 도핑농도에 따른 실제불순물의 양에 큰 차이가 없으므로 채널길이에 대한 문턱전압이하 스윙이 도핑농도에 따라 거의 동일하게 유지되고 있다. 그러나 채널두께가 15 nm로 증가하면 실제불순물의 양이 도핑농도에 따라 변화를 보이면서 고도핑에서 문턱전압이하 스윙이 증가하는 현상을 그림 6b)에서 관찰할 수 있다.

**그림 5.** 하단 산화막 두께와 채널두께를 파라미터로 계산한 채 널길이에 대한 문턱전압이하 스윙 값의 변화

Fig. 5 The change of subthreshold swing for channel length with parameters of bottom oxide thickness and channel thickness

**그림 6.** 채널도핑농도와 채널두께를 파라미터로 계산한 채널길 이에 대한 문턱전압이하 스윙 값의 변화  ${\bf a})~t_{si}=10\,nm$ 일 경우 b)  $t_{si}=15\,nm$ 일 경우

**Fig. 6** The change of subthreshold swing for channel length with parameters of doping concentration and channel thickness a)  $t_{si}=10\,nm$  and b)  $t_{si}=15\,nm$

그러나 저농도 도핑의 경우, 채널두께의 변화와 관계 없이 일정한 문턱전압이하 스윙을 나타내고 있다는 것 을 알 수 있다.

#### Ⅳ. 결 론

본 연구에서는 비대칭 DGMOSFET의 채널길이에 대한 문턱전압이하 스윙의 변화에 대하여 분석하였다. 비대칭 DGMOSFET는 하단 게이트 구조를 상단과 달 리 제작할 수 있는 특징이 있으므로 문턱전압이하 스윙 을 조절할 수 있는 요소가 증가하게 된다. 그러므로 비 대칭 DGMOSFET의 채널길이에 대한 문턱전압이하 스윙의 변화를 채널두께, 하단 산화막 두께, 상하단 게 이트 전압 및 도핑농도 등에 따라 조사하였다. 채널두 께가 증가에 따라 문턱전압이하 스윙이 크게 증가하는 단채널 효과가 발생하며 채널두께가 작아지면 채널두 께에 대한 채널길이가 상대적으로 길어져 단채널효과 가 감소하는 효과가 나타나고 있었다. 특히 채널길이가 작아지면 상단 게이트 전압이 변화하여도 문턱전압이 하 스윙이 크게 변화하지 않았다. 하단게이트 전압에 따른 문턱전압이하 스윙의 변화는 채널두께 및 채널길 이에 따라 비례 및 반비례의 관계를 보이나 채널두께가 감소하면 문턱전압이하 스윙의 변화가 일정하게 나타 나고 있었다.

하단 산화막 두께에 대한 변화 역시 채널두께에 따라 하단 산화막 두께가 미치는 영향이 변화하였으며 저도핑의 경우 도핑농도에 따라 문턱전압이하 스윙은 거의 일정하였으나 채널크기가 증가하면 문턱전압이하스윙에 변화가 생기고 있었다. 이와 같은 결과는 향후비대칭 DGMOSFET의 설계에 활용될 수 있으리라 사료된다.

#### **REFERENCES**

- [1] S. Dimitrijev, *Principles of Semiconductor Devices*, Oxford University Press, NewYork, 2012.

- [2] J.P.Duarte, S.J.Choi, D.I.Moon and Y.K.Choi, "A nonpiecewise model for long-channel junctionless cylindrical nanowire FETs," *IEEE Electron Device Letters*, vol.33, no.2, pp.155-157, 2012.

- [3] R.Vaddi, S.Dasgupta and R.P.Agarwal, "Analytical modeling of subthreshold current and subthreshold swing of an underlap DGMOSFET with tied independent gate and symmetric asymmetric options," *Microelectronics J.*, vol.42, no.5, pp.798-807, 2011.

- [4] N.Seoane, G.Indalecio, E.Comesane, M.Aldegunde, A.J.Garcia-Loureiro and K.Kalna, "Random Dopant, Line-Edge Roughness and Gate Workfunction Variability in a Nano InGaAs FinFETs," *IEEE Trans. on Electron Devices*, vol. 61, no.2, pp.466-472, 2006.

- [5] J.B.Roldan, B.Gonzalez, B.Iniguez, A.M.Roldan, A.Lazaro and A.Cerdeira, "In-depth analysis and modelling of self-heating effects in nanometric DGMOSFETs," *Solid-state electronics*, vol.79, no.1, pp.179-184, 2013.

- [6] Z.Ding, G.Hu, J.Gu, R.Liu, L.Wang and T.Tang, "An analytical model for channel potential and subthreshold swing of the symmetric and asymmetric double-gate MOSFETs," *Microelectronics J.*, vol.42, pp.515-519, 2011.

- [7] P.K.Tiwari, S.Kumar, S.Mittal, V.Srivastava and U.Pandey, "A 2D Analytical Model of the Channel Potential and Threshold Voltage of Double-Gate(DG) MOSFETs With Vertical Gaussian Doping Profile," *IMPACT-2009*, pp.52-55, 2009.

- [8] Hakkee Jung, :Analysis for Potential Distribution of Asymmetric Double Gate MOSFET Using Series Function, *J. of KIICE*, vol.17, no.11, pp.2621-2626, 2013.

정학기(Hak Kee Jung)

1983,3 아주대학교 전자공학과 B.S. 1985,3 연세대학교 전자공학과M.S. 1990,8 연세대학교전자공학과 Ph.D 1995,8 일본 오사카대학 교환교수 2005,8 호주 그리피스대학 교환교수 1990,3-현재 군산대학교 전자공학과 교수 2014 1-현재 학구정부통시한히 회장

※관심분야: 반도체소자 시뮬레이션, 몬테칼로 시뮬레이션, 회로 및 시스템 해석 등