**JPE 15-1-16**

http://dx.doi.org/10.6113/JPE.2015.15.1.160 ISSN(Print): 1598-2092 / ISSN(Online): 2093-4718

# Optimum Design of Integer and Fractional-Order PID Controllers for Boost Converter Using SPEA Look-up Tables

Ahmadreza Amirahmadi<sup>†</sup>, Mohammadreza Rafiei<sup>\*</sup>, Kambiz Tehrani<sup>\*\*</sup>, Giovanni Griva<sup>\*</sup>, and Issa Batarseh<sup>\*\*\*</sup>

†\*\*\*\*Department of Electrical Engineering and Computer Science, University of Central Florida, Florida, U.S.A

\*Politechnico Di Torino, Turin, Italy

\*\*University of Nancy (INPL), Nancy, France

#### **Abstract**

This paper presents a method of designing optimal integer- and fractional-order proportional-integral-derivative (FOPID) controllers for a boost converter to gain a set of favorable characteristics at various operating points. A Pareto-based multi-objective optimization approach called strength Pareto evolutionary algorithm (SPEA) is used to obtain fast and low overshoot start-up and dynamic responses and switching stability. The optimization approach generates a set of optimal gains called Pareto set, which corresponds to a Pareto front. The Pareto front is a set of optimal results for objective functions. These results provide designers with a trade-off look-up table, in which they can easily choose any of the optimal gains based on design requirements. The SPEA also overcomes the difficulties of tuning the FOPID controller, which is an extension to the classic integer-order PID controllers and potentially promises better results. The proposed optimized FOPID controller provides an excellent start-up response and the desired dynamic response. This paper presents a detailed comparison of the optimum integer- and the fractional-order PID controllers. Extensive simulation and experimental results prove the superiority of the proposed design methodology to achieve a wide set of desired technical goals.

Key words: Boost converter, Chaos, FOPID controller, Multi-objective optimization, PID controller

#### I. Introduction

Control of DC–DC converters has been of particular interest in the last two decades [1]-[4]. From the control point of view, nearly all the power conversion systems are regarded as a tracking problem because the output quantity should follow the reference command with a fast transient behavior and a low steady-state error. Most of these systems are inherently time varying, uncertain [5], [6], have a non-minimum phase, and are non-linear with some possible complex behavior like chaos [7], [8]. The most popular

method for modeling DC-DC converters is state space averaging. State space averaging provides an approximate linear time-invariant (LTI) model [2], [9], [10]. This model does not adequately predict a large signal behavior of the converters. Accordingly, limited linear control approaches are designed based on the non-linear model of the converter. These approaches cannot normally guarantee an optimized large signal behavior, including the start-up regime. Even advanced linear control approaches, such as  $H^{\infty}$  [11]-[13],  $\mu$ [14]-[17], and Hammerstein model-based control [3], [18] cannot guarantee a fast and low overshoot response in the start-up period [1]. One solution is using non-linear and intelligent controllers, such fuzzy as Implementing these controllers is harder than implementing linear controllers, especially in the digital domain [19]-[24].

Other linear solutions, such as the linear quadratic regulator [25], linear quadratic Gaussian [26], [27], and quantitative feedback theory [28], which are designed based

Manuscript received Apr. 14, 2014; accepted Aug. 7, 2014 Recommended for publication by Associate Editor Se-Kyo Chung.

<sup>&</sup>lt;sup>†</sup>Corresponding Author: amirahmadi@knights.ucf.edu

Tel: +1-402-823-2000, University of Central Florida

<sup>\*</sup>Politechnico Di Torino, Italy

<sup>\*\*\*</sup>University of Nancy (INPL), Nancy, France

<sup>\*\*\*</sup>Dept. of Electrical Engineering and Computer Science, University of Central Florida, U.S.A

on the linearized model of the converter, are not appropriate choices for large signal conditions. However, these solutions overcome the model uncertainties of the converters [5], [6]. Another design difficulty based on the LTI model is that the calculated LTI model depends on the operating point of the converter. Any change in the reference command, load parameters, or input DC voltage may alter the operating condition of the system. Consequently, this change alters some parameters of the corresponding LTI model [29].

The closed loop DC-DC power converter may exhibit complex and chaotic behavior in some cases [30]-[35]. This chaotic behavior is undesirable because it may result in low-quality output signal and undesirable acoustic noise [36]. Such a complex behavior and the existence of various major sources of uncertainty make the controller design task difficult. The results from Ref. [1] indicate that a linear controller may not be useful in overcoming switching instability.

Linear controllers are prevalently used in industrial applications because implementing them is straightforward. Attempts to improve the quality and robustness of the PID controllers have been continuously conducted [37]. Using fractional-order controllers with non-integer derivation and integration parts is one method of improving the traditional PID controllers. However, the difficulties of designing fractional-order PID (FOPID) compared with traditional PID controllers are relatively higher because FOPID controllers include derivative and integrated orders as design parameters [38]. Using the FOPID controller may provide better robustness for a linear system if the dynamic characteristics are basically the same using either integer-order PID controller or FOPID controller [39]. The conventional FOPID controller tuning methods are regularly based on estimating the order of fractional calculus using experience first, and then tuning other parameters according to the tuning methods of the integer-order controllers. The designed controller acquires better results than integer-order controllers. However, the efficiency is still relatively low. Furthermore, these tuning methods may fail to achieve the global optimal solution [40].

An evolutionary approach such as the genetic algorithm with a proper objective function is a good approach in designing an integer or fractional-order PID controller for a non-linear and complex system. However, selecting an appropriate objective function is critical. Traditionally used objective functions, such as integral of the squared error and integral of time multiplied by absolute error, may not lead to a favorable response because they do not represent the output desired characteristics (e.g., overshoot and settling time) in an explicit manner. Therefore, several modifications in the objective function through trial and error may be required.

First, this paper aims to design a simple PID controller to gain an optimized transient, steady-state response, and switching stability for various operating points using the SPEA multi-objective optimization approach [41]. This approach is based on the Pareto optimality concept used in game theory literature. Settling time, overshoot, dynamic response, robustness, and switching stability are employed as objective functions. The gains of the PID controller (i.e.,  $K_p$ ,  $K_i$ , and  $K_d$ ) and the maximum and the minimum of the modulator harder are the design variables. Second, this paper implements the SPEA to design the FOPID controller. The FOPID controller design is considered a real parameter optimization problem in a five-dimensional hyperspace. This paper concludes with a comparison of the results of the optimized integer and the FOPID controller.

#### II. MULTI-OBJECTIVE OPTIMIZATION

A general multi-objective problem is represented as follows:

Min/Max

$$y = f(x) = (f_1(x), f_2(x), ... f_k(x))$$

(1)

Subject to  $x = (x_1, x_2, .... x_n)eX$  &  $y = (y_1, y_2, ... y_k)eY$  where x, X, y, and Y are the decision vector, parameter space, objective vector, and objective space, respectively.

Evolutionary algorithms (EAs) are often well suited for optimization problems that involve several, often conflicting

optimization problems that involve several, often conflicting objectives. The EAs are divided into three major categories [41].

The first category is based on plain aggregating approaches, which combine the desired goals of the optimization problem, construct a scalar function, and use a common scalar optimization approach to solve the problem. The major problem of these methodologies is the unavailability of any straightforward methods for combining the objectives or goals of the problem. However, its advantage is its simplicity and its ability to produce a single solution.

The second category is the population-based non-Pareto approaches, where the search is guided in several directions at the same time by changing the selection criterion during the reproduction phase. The fraction of the mating pool in this type is selected according to one of the objectives or multiple linear combinations of the objectives in parallel. Some advanced approaches in this category are as follows:

- Hajela's and Lin's genetic algorithm [42]

- Vector-evaluated genetic algorithm [43]

The last category is the Pareto-based approaches, which use the Pareto dominance to determine the reproduction probability of each individual.

According to the definition of the Pareto dominance, vector  $\mathbf{a}$  in the search space dominates vector  $\mathbf{b}$  if

$$\forall_{i} \in \{1, 2, \dots, k\}: f_{i}(a) \ge f_{i}(b)$$

$$\exists_{i} \in \{1, 2, \dots, k\}: f_{i}(a) > f_{i}(b)$$

(2)

**b** is called dominated if at least one vector dominates **b** and called non-dominated, otherwise. Each non-dominated

solution is regarded optimal in the sense of Pareto or called Pareto optimal. One is obviously the best in terms of one of the objectives between any pairs of points on a Pareto set. The set of all non-dominated solutions is called the Pareto optimal set. The set of the corresponding values of the objective functions is called the Pareto optimal front (POF) or simply, the Pareto front. Some advanced Pareto-based evolutionary methods are as follows:

- niched Pareto genetic algorithm [44]

- non-dominated sorting genetic algorithm [45]

- SPEA [41]

The SPEA integrates established techniques used in the existing Pareto-based EAs in a single unique algorithm. Its convergence to the Pareto optimal front and preserving the population diversity are its advantages over other EAs [41].

#### A SPEA

A flowchart of the approach including the following major steps is presented in Fig. 1 [41]:

#### SPEA:

- generating an initial population P and creating the empty external non-dominated set P';

- 2. pasting non-dominated members of P into P';

- 3. removing all solutions within P', which are covered by any other members of P';

- pruning P' by clustering if the number of externally stored non-dominated solutions exceeds a given maximum N';

- 5. calculating the fitness of all individuals in P and P';

- using binary tournament selection with replacement and selecting individuals from P and P' until the mating pool is filled;

- 7. applying crossover and mutation operators;

- 8. stopping if the maximum number of generations is reached, and repeating step 2, otherwise.

Fitness assignment is performed using the two following steps:

strength  $0 \le \text{Si} < 1$ , which is equal to the following value, is considered for every individual (i) of P':

$$S_i = \frac{n}{N+1} \tag{3}$$

where N is the size of P, and n is the number of individuals in P dominated by individual (i) of P'. The fitness of (i) is equal to  $S_i$ .

- Fitness (*f<sub>j</sub>*) is equal to the following value for every individual (*j*) of P:

$$f_j = 1 + \sum_{i,i \ge j} S_i$$

where  $f_j \in [1, N)$  (4)

Small fitness values correspond to high reproduction probabilities. Hence, 1 is added to sum up the strengths of P' individuals that dominate j. The members of P' have better fitness than the members of P.

Fig. 1. Optimization flowchart of the strength Pareto.

The major point of clustering is that the point with a minimal average distance to all other points in a cluster is considered the representative for that cluster [41].

#### III. FRACTIONAL SYSTEMS

#### A. Fractional Calculus

Fractional-order systems are characterized by the fractional-order differential equations. Fractional calculus considers any real number for derivatives and integrals. The FOPID controller is the expansion of the conventional integer-order PID controller based on fractional calculus.

Fractional calculus is a branch of mathematics that deals with real number powers of differential or integral operators. The following definition, which was proposed by Riemann and Liouville, is the most common among all the different definitions [46]:

$$_{c}D_{x}^{-n}f(x) = \int_{c}^{x} \frac{(x-t)^{n-1}}{(n-1)!}f(t)dt, \quad n \in \Re$$

(5)

The general definition of D is presented by Eq. (6) as follows:

$${}_{c}D_{x}^{\nu}f(x) = \begin{cases} \int_{c}^{x} \frac{(x-t)^{-\nu-1}}{\Gamma(-\nu)} f(t)dt, & \text{if } \nu < 0\\ f(x) & \text{if } \nu = 0\\ D^{n}[{}_{c}D_{x}^{\nu-n}f(x)] & \text{if } \nu > 0 \end{cases}$$

$$n = \min\{K \in \Re, K > v\}$$

where  $\Gamma(\cdot)$  is the well-known Euler's gamma function.

# B. Approximation of the Fractional-Order Derivative and Integral

The functions used in this section provide an integer-order frequency-domain approximation of transfer functions that involve the fractional powers of s.

The following equation is obtained for the frequency-domain transfer function C(s) given by Eq. (7) as follows:

$$C(s) = Ks^{\nu} \qquad \qquad \nu \in \Re \tag{7}$$

Crone is a well-known continuous approximation approach. Crone is a French acronym that means "robust fractional-order control." This approximation implements a recursive distribution of *N* zeros and N poles, which leads to a transfer function as Eq. (8):

$$C(s) = K' \prod_{n=1}^{N} \frac{1 + \frac{s}{\omega_{zn}}}{1 + \frac{s}{\omega_{pn}}}$$

(8)

where K' is an adjusted gain so that both Eqs. (7) and (8) have a unit gain at 1 rad/s. Zeros and poles have to be over a frequency domain  $[w_i; w_h]$  with a valid approximation. These zeros and poles are given for a positive v by Eqs. (9)–(11) as follows:

$$\omega_{z1} = \omega_l \sqrt{\eta} \tag{9}$$

$$\omega_{pn} = \omega_{z,n-1}\alpha \qquad n = 1...N \tag{10}$$

$$\omega_{zn} = \omega_{p,n-1} \eta \qquad n = 2...N \tag{11}$$

where  $\alpha$  and  $\eta$  are calculated according to Eqs. (12) and (13).

$$\alpha = \left(\frac{\omega_h}{\omega_l}\right)^{\frac{v}{N}} \tag{12}$$

$$\eta = \left(\frac{\omega_h}{\omega_l}\right)^{\frac{1-\nu}{N}} \tag{13}$$

The roles of zeros and poles are swapped for negative  $\nu$  values. The number of poles and zeros is initially selected. The desired performance of this approximation depends on the order N. A simple approximation is provided with a lower-order N, which causes ripples in both gain and phase characteristics. The approximation is not satisfactory when  $|\nu| > 1$ . The fractional-order  $\nu$  is usually separated as Eq. (14). Moreover, only the first term  $s^{\nu}$  needs to be approximated.

$$s^{\nu} = s^{\beta} s^{n}, \quad \nu = n + \beta, \quad n \in \Re, \quad \beta \in [0,1]$$

(14)

## C. Fractional PID Controller

Researchers found that controllers, which use fractional-order derivatives and integrals, achieve better performance and robustness than conventional integer-order

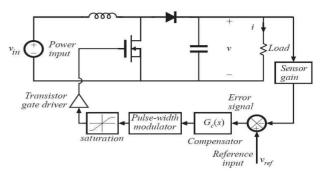

Fig. 2. Boost converter.

TABLE I

CIRCUIT PARAMETERS OF THE BOOST CONVERTER

| Parameter        | Value                  |  |  |  |

|------------------|------------------------|--|--|--|

| Capacitor        | 1056 μF                |  |  |  |

| Inductor         | 250 μΗ                 |  |  |  |

| Load             | 25 Ω                   |  |  |  |

| ESR of capacitor | $30~\mathrm{m}~\Omega$ |  |  |  |

| ESR of inductor  | $10~\text{m}~\Omega$   |  |  |  |

controllers [47]. The FOPID controller is more flexible and provides an opportunity for a better adjustment of the dynamical characteristics of the control system.

The FOPID controller, which is proposed by Podlubny in 1999, is the expansion of the conventional PID controller based on fractional calculus [48],[49].

The general form of the FOPID controller is  $PI^{\alpha}D^{\beta}$ . Its general transfer function is given by Eq. (15) as follows:

$$G_c(s) = K_p + K_i S^{-\alpha} + K_d S^{\beta}$$

(15)

Aside from selecting  $K_p$ ,  $K_i$ , and  $K_d$ , this controller needs to select  $\alpha$  and  $\beta$ , which are not necessarily integer numbers [50], [51].

## IV. PID CONTROLLER FOR BOOST CONVERTER

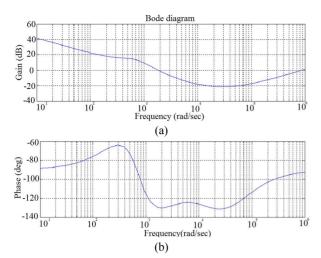

The studied DC–DC converter (Fig. 2) is a boost converter with a switching frequency equal to 15 kHz that converts a 5 V input supply to a 12 V output. Table I presents the prototype circuit parameters. The parameters are similar to those used in Ref. [24] for easy comparison of results. The standard state-space averaging technique is usually used to obtain the output-to-control small-signal transfer function. However, the controller design based on this mathematical model cannot provide the best performance because of a significant model error. Ref. [24] proposed a transfer function for the studied boost converter based on the measured experimental frequency response. This transfer function [Eq. (16)] is referred to in this part because it is more accurate than the theoretical one. The frequency response of the transfer function is presented in Fig. 3(a).

$$\frac{\hat{v}_o(s)}{\hat{d}(s)} = \frac{-5.6956 \times 10^{-3} S^2 - 2.5589 \times 10^2 s + 4.9831 \times 10^6}{s^2 + 8.2525 \times 10^2 s + 5.4241 \times 10^5}$$

(16)

Fig. 3. Frequency response of the boost converter: (a) open and (b) closed loops [24].

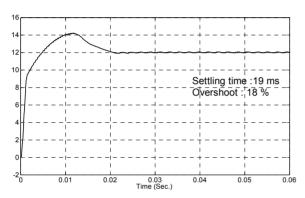

Fig. 4. Start-up response of the boost converter with the PID controller proposed in Ref. [24].

The PID controller designed based on the measured small-signal model in Eq. (16) is presented in Eq. (17) as follows:

$$G_C(s) = 0.567 + \frac{134.13}{s} + 1.98 \times 10^{-4} s$$

(17)

The Bode plot of the PID-compensated boost converter is illustrated in Fig. 3(b). The gain crossover frequency of the PID-compensated system is approximately 290 Hz, while the phase margin is 50°. The start-up response obtained using this PID controller is presented in Fig. 4. The settling time is 0.019 s, while the overshoot is 18%. Neither of the two values is satisfactory.

# V. PID CONTROLLER OPTIMIZATION

The flowchart in Fig. 1 is used to optimize the PID controller. Table 2 presents the optimization parameters. The program is conducted using m-file in MATLAB. The objective functions are calculated in SIMULINK using the details of the system. Consequently, this method reduces the approximation error in the mathematical model. The parameters are sent to the SIMULINK environment so each

TABLE II

SPECIFICATIONS OF THE EVOLUTIONARY ALGORITHMS

| Parameter                  | SPEA                                            |  |  |

|----------------------------|-------------------------------------------------|--|--|

| Iteration                  | 25                                              |  |  |

| Population size            | 30                                              |  |  |

| Chromosome coding          | Real-code                                       |  |  |

| External non-dominated set | 30                                              |  |  |

| size                       | B 1 1 .1                                        |  |  |

| Selection                  | Roulette wheel                                  |  |  |

| Recombination              | Single-point crossover, with probability of 0.7 |  |  |

| Mutation                   | Discrete, with probability of 1/variables       |  |  |

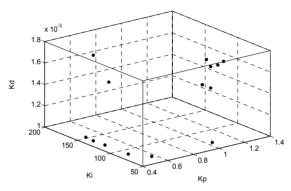

Fig. 5. Pareto set (i.e., PID coefficients).

member of each generation obtains the objective functions. The values of the objective functions are returned to the program after the simulation running time is finished.

The SPEA algorithm runs until the stop condition is satisfied. The members of  $P^\prime$  in the last iteration are the optimized parameters.

#### A. Large-Signal Response Optimization

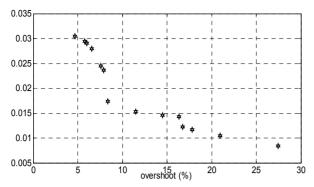

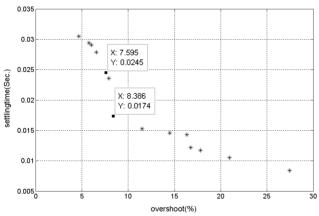

The program used to optimize the large-signal response (i.e., start-up response) with the PID gains (i.e.,  $K_p$ ,  $K_i$ , and  $K_d$ ) as design variables generates a set of optimal gains called the Pareto set (Fig. 5 and Table III). The Pareto set corresponds to a set of optimal results for the objective functions called the Pareto front (Fig. 6).

The cost functions for this optimization are as follows:

$$F_1 = \text{Overshoot} = \frac{y_{m \ ax-} y_d}{y_d} 100\%$$

$F_2$  = Settling time =  $m \dot{n} \{t: e(t) < 1.5\%\}$

where y is the output voltage, and e is the tracking error in percent. The desired output is 12 V.

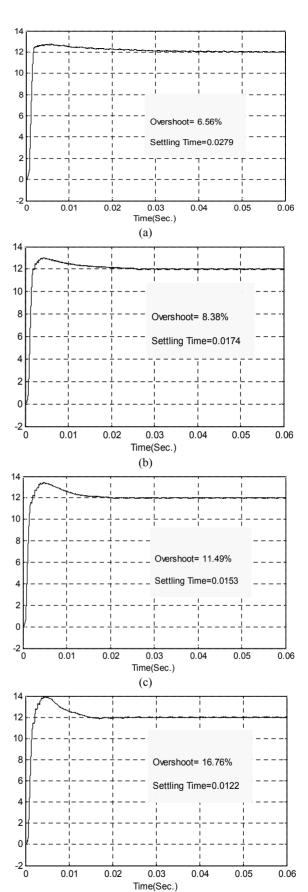

A designer can easily select any of the results based on their features and his/her own engineering view. Some results are given in Fig. 7. Some have low overshoot but high settling time, whereas others have low settling time but high overshoot. The fastest among these optimal responses provides an 8.4 ms settling time and causes a high overshoot

Fig. 6. Pareto front.

TABLE III

PARETO SET (I.E., PID CONTROLLER COEFFICIENTS) AND PARETO FRONT (I.E., SETTLING TIME AND OVERSHOOT)

| Point | $\mathbf{K}_{\mathrm{p}}$ | K <sub>i</sub> | $\mathbf{K}_{d}$ | Setting<br>time<br>(Sec.) | Overshoot<br>(Percent) |

|-------|---------------------------|----------------|------------------|---------------------------|------------------------|

| 1     | 0.9743                    | 64.9645        | 0.0018           | 0.0294                    | 5.7608                 |

| 2     | 1.0953                    | 71.2187        | 0.0017           | 0.0291                    | 6.0208                 |

| 3     | 0.4717                    | 139.6785       | 0.0018           | 0.0143                    | 16.34                  |

| 4     | 0.4786                    | 117.5642       | 0.0016           | 0.0146                    | 14.495                 |

| 5     | 1.0388                    | 71.2187        | 0.0017           | 0.0279                    | 6.5633                 |

| 6     | 0.4812                    | 153.1965       | 0.001            | 0.0105                    | 20.96                  |

| 7     | 1.0388                    | 84.0616        | 0.0015           | 0.0236                    | 7.9158                 |

| 8     | 1.0388                    | 71.2187        | 0.0015           | 0.0245                    | 7.595                  |

| 9     | 0.4812                    | 87.9465        | 0.001            | 0.0153                    | 11.4933                |

| 10    | 0.4717                    | 139.6785       | 0.001            | 0.0117                    | 17.805                 |

| 11    | 1.0374                    | 68.1873        | 0.001            | 0.0084                    | 27.4358                |

| 12    | 1.0388                    | 50.9062        | 0.0018           | 0.0305                    | 4.6625                 |

| 13    | 0.5686                    | 69.3299        | 0.001            | 0.0174                    | 8.3858                 |

| 14    | 0.4786                    | 123.4201       | 0.001            | 0.0122                    | 16.7625                |

of 27.4%. However, these values are all optimum in the sense of the Pareto optimality criterion.

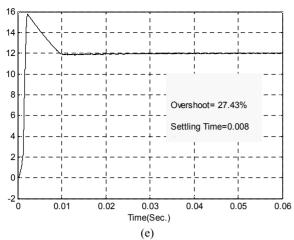

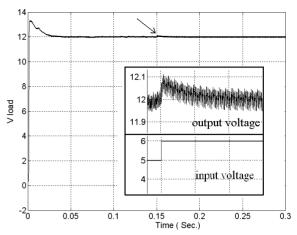

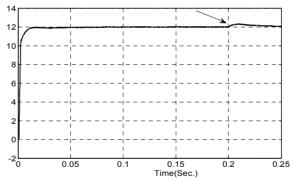

Aside from the large-signal behavior, small-signal response is also important. Hence, the dynamic behavior of the output voltage to the step change of the input supply for one of these optimal PID gains is evaluated. The satisfactory dynamic response is depicted in Fig. 8. Taking the dynamic response characteristics as additional objective function(s) is also possible. Accordingly, both large- and small-signal responses are optimized at the same time using a simple PID controller. This optimization is discussed in the next section.

Some interesting information, which helps in creating an efficient design, is obtained from the Pareto front. Accordingly, a jump on the Pareto front is important. For example, that the two points cause a nearly identical overshoot (around 8%) is determined by comparing the two points marked in the Pareto front (Fig. 9). However, the lower point provides nearly a 50% faster settling time. Hence, from the practical point of view, the lower point provides better results if the overshoot is acceptable.

(d)

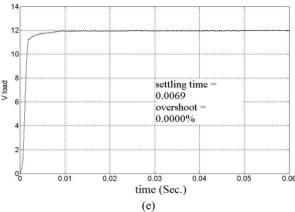

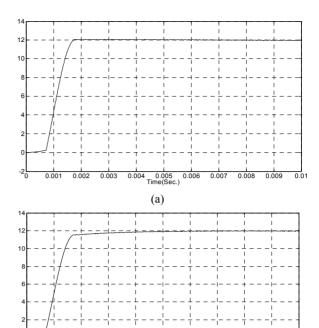

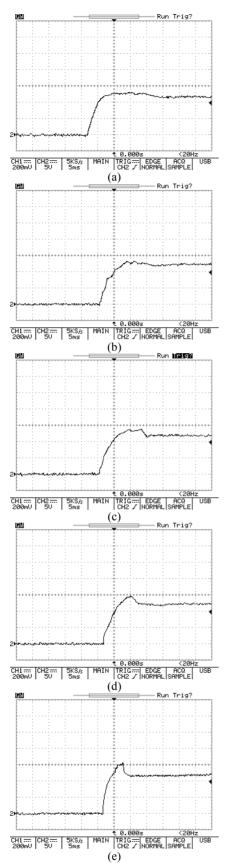

Fig. 7. Some start-up responses selected from the Pareto front (Table 3): (a), (b), (c), (d), and (e) correspond to points 5, 13, 9, 14, and 11, respectively.

Fig. 8. Small-signal behavior of the converter with the Pareto-based PID controller when a change occurs in the 5 V to 6 V input voltage (i.e., the PID gains are based on point 13 in Table III).

Fig. 9. Comparison of two different points of the Pareto front.

## B. Large and Dynamic Response Optimization

Dynamic response and large signal are important for some applications. The dynamic response is added as an additional objective function to the previous optimization process. In addition to the large signal, the small-signal response of the

Fig. 10. One of the dynamic response optimization results in addition to the large-signal optimization selected according to the design requirements (point 8 in Table IV).

Fig. 11. Pareto front.

converter to a 20% increase in the input voltage at 0.15 s is defined as an optimization objective. The Pareto set and the Pareto front obtained from the optimization are presented in Table IV. The cost functions in this part are as follows:

$$F_1$$

: Overshoot =  $\frac{y_{m \ ax-y_d}}{y_d} 100\%$

F<sub>2</sub>: Settling time =  $m \dot{n} \{t: e(t) < 1.5\%\}$

F<sub>3</sub>: Dynamic overshoot =

$$\frac{y_{m \text{ ax(after } t=0.15)}-y_d}{y_d}$$

100%

One set of the PID coefficients suggested by Table 4 is selected according to the required features of the converter output response. The PID coefficient is  $K_p = 0.6509$ ,  $K_i = 75.1074$ , and  $K_d = 0.0021$  if the start-up overshoot, settling time, and dynamic overshoot must be below 15%, 0.03 s, 1.5%, respectively. This response is depicted in Fig. 10.

# C. Large-signal Response Optimization with More Variables

The dynamic response is not considered an optimization objective in this program. However, these results also obtain satisfactory dynamic responses. The output voltage has a

TABLE IV

PARETO SET (I.E., PID COEFFICIENTS) AND PARETO FRONT

(I.E., SETTLING TIME, OVERSHOOT, AND DYNAMIC RESPONSE)

| Point | $K_{P}$ | K <sub>I</sub> | K <sub>D</sub> | Overshoot<br>(Percent) | Setting time<br>(Sec.) | Dynamic Overshoot<br>(Percent) |

|-------|---------|----------------|----------------|------------------------|------------------------|--------------------------------|

| 1     | 1.1395  | 56.6066        | 0.0048         | 6.0458                 | 0.0375                 | 2.5300                         |

| 2     | 0.9489  | 126.1336       | 0.0033         | 9.8292                 | 0.0239                 | 2.1967                         |

| 3     | 0.7388  | 143.3492       | 0.0026         | 14.3117                | 0.0168                 | 2.2483                         |

| 4     | 0.9256  | 107.6074       | 0.0021         | 30.8883                | 0.0157                 | 0.8550                         |

| 5     | 0.9489  | 143.3492       | 0.0026         | 22.3808                | 0.0164                 | 1.8292                         |

| 6     | 0.9256  | 107.6077       | 0.0041         | 8.3525                 | 0.0286                 | 3.1175                         |

| 7     | 1.1395  | 56.6066        | 0.0026         | 26.7425                | 0.0196                 | 1.8050                         |

| 8     | 0.6509  | 75.1074        | 0.0021         | 10.9208                | 0.0226                 | 1.0808                         |

| 9     | 0.9256  | 97.5122        | 0.0026         | 18.4042                | 0.0192                 | 1.9500                         |

| 10    | 1.1395  | 143.3495       | 0.0026         | 30.7592                | 0.0154                 | 1.7667                         |

| 11    | 0.6509  | 158.6336       | 0.0046         | 137292                 | 0.0386                 | 0.3817                         |

| 12    | 0.9489  | 75.0995        | 0.0021         | 30.8883                | 0.0164                 | 0.8008                         |

| 13    | 0.9653  | 126.1336       | 0.0033         | 9.7792                 | 0.0239                 | 2.3400                         |

| 14    | 1.1395  | 56.6066        | 0.0044         | 5.9058                 | 0.0374                 | 2.9375                         |

| 15    | 0.9653  | 75.1074        | 0.0023         | 26.8317                | 0.0207                 | 1.1683                         |

$TABLE\ V$  Pareto Set (i.e., PID Coefficients and Max and Min of the Hard Limiter) and Pareto Front (i.e., Settling Time and Overshoot)

| Point | K <sub>P</sub> | K <sub>I</sub> | K <sub>D</sub> | Min    | Max    | Overshoot<br>(Percent) | Setting time<br>(Sec.) |

|-------|----------------|----------------|----------------|--------|--------|------------------------|------------------------|

| 1     | 1.4365         | 68.9257        | 0.0010         | 0.0117 | 0.6685 | 1.3200                 | 0.0017                 |

| 2     | 1.4681         | 32.7811        | 0.0036         | 0.1327 | 0.6892 | 0.4058                 | 0.0018                 |

| 3     | 1.5161         | 51.6227        | 0.0047         | 0.1340 | 0.7276 | 0.3075                 | 0.0025                 |

| 4     | 1.5817         | 51.6227        | 0.0053         | 0.1340 | 0.6989 | 0.1675                 | 0.0058                 |

| 5     | 1.4192         | 51.6227        | 0.0047         | 0.1340 | 0.6727 | 0.0000                 | 0.0069                 |

TABLE VI

PARETO SET (I.E., PID COEFFICIENTS AND MAX AND MIN OF THE HARD LIMITER) AND

PARETO FRONT (I.E., SETTLING TIME, OVERSHOOT, AND SWITCHING STABILITY)

| Point | K <sub>P</sub> | K <sub>I</sub> | K <sub>D</sub> | Min    | Max    | Overshoot<br>(Percent) | Setting time (Sec.) | Jp2 e5 |

|-------|----------------|----------------|----------------|--------|--------|------------------------|---------------------|--------|

| 1     | 0.4000         | 50.9884        | 0.0032         | 0.0471 | 0.6093 | 0.5683                 | 0.0207              | 0.0000 |

| 2     | 1.0120         | 51.1002        | 0.0041         | 0.0425 | 0.6093 | 0.2733                 | 0.0264              | 0.0002 |

| 3     | 0.4576         | 75.1674        | 0.0032         | 0.0425 | 0.6093 | 1.4646                 | 0.0154              | 0.0004 |

| 4     | 0.4168         | 46.2172        | 0.0047         | 0.1748 | 0.6093 | 1.3550                 | 0.0064              | 0.0005 |

| 5     | 1.0534         | 75.0531        | 0.0032         | 0.0471 | 0.6093 | 0.8933                 | 0.0136              | 0.0025 |

| 6     | 0.6496         | 56.5743        | 0.0039         | 0.0425 | 0.6093 | 0.2983                 | 0.0220              | 0.0078 |

| 7     | 1.6480         | 84.6851        | 0.0025         | 0.0228 | 0.0228 | 0.7166                 | 0.0092              | 0.4391 |

| 8     | 1.0116         | 43.1117        | 0.0041         | 0.1591 | 0.1591 | 1.4591                 | 0.0040              | 0.9911 |

| 9     | 1.1076         | 60.1767        | 0.0024         | 0.1231 | 0.1231 | 1.4583                 | 0.0018              | 1.0569 |

| 10    | 1.1347         | 67.2025        | 0.0015         | 0.0463 | 0.0463 | 0.8875                 | 0.0079              | 1.1385 |

| 11    | 1.1346         | 41.4555        | 0.0032         | 0.1214 | 0.1214 | 0.6925                 | 0.0033              | 1.2439 |

| 12    | 1.6778         | 67.2918        | 0.0043         | 0.1216 | 0.1216 | 1.5750                 | 0.0017              | 1.4098 |

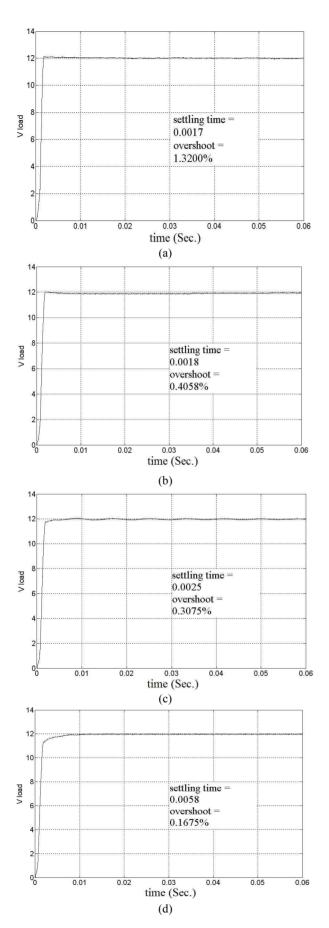

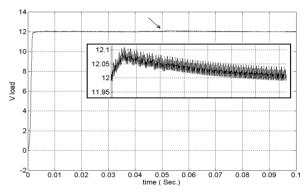

Fig. 12. Responses of the Pareto front with the max and min hard limiter and the PID controller coefficients as optimization variables.

Fig. 13. Small-signal behavior of the converter with the Pareto-based PID controller (max and min of the hard limiter optimization in addition to PID coefficients) when a step change from 5 V to 6 V occurs in the input voltage at 0.05 s.

negligible overshoot when a 20% step increase in the input voltage occurs at 0.05 s (Fig. 13).

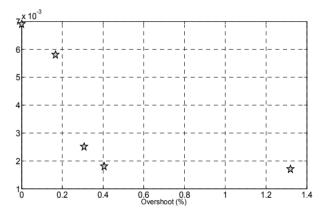

The max and min bounds of the hard limiter used to limit the duty cycle are added to the optimization variables, whereas the cost functions remain the same to improve the large-signal response. Table V and Fig. 11 present the Pareto set and the Pareto front for this optimization program. The start-up response of these results is given in Fig. 12 to illustrate the significant improvement achieved using this optimization. All the points on the POF in Fig. 11 dominate the points on the POF in Fig. 6.

#### D. Switching Stability and Large-Signal Optimization

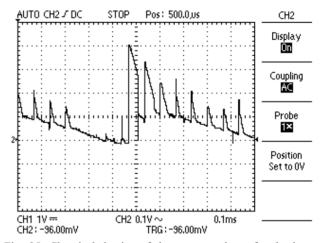

The frequency of the output voltage ripples is less than the pulse-width modulation (PWM) generator signal (Fig. 14). The frequency can even be non-periodic. This phenomenon is called chaos.

This problem is solved by considering the switching stability as an optimization objective in addition to the settling time and overshoot of the large-signal response. The sum of the errors between every two successive points of error signal sampled synchronized with the PWM clock at a

Fig. 14. Chaotic behavior in the steady-state response of the waveform depicted in Fig. 10. (a) Chaos behavior. (b) Phase plot.

steady state must tend to zero to improve the chaotic behavior.

The cost functions are as follows:

F<sub>1</sub>: Overshoot =

$$\frac{y_m \ ax - y_d}{y_d} 100\%$$

F<sub>2</sub>: Settling time =  $m \dot{n} \{t: e(t) < 1.5\%\}$

$$F_3$$

:  $J_{p2} = \sum_{i=3000}^{4000} |e_i - e_{i-1}|) \times 100,000$

where  $e_i$  is the error signal at the *i*th switching instance.

Table VI presents the Pareto set and the Pareto front obtained from this optimization.

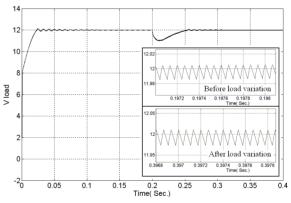

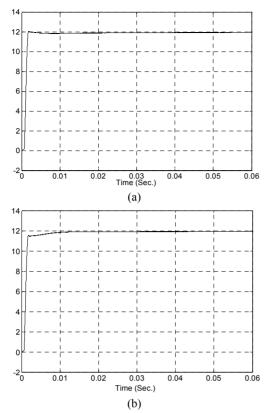

Chaos has completely been removed for the first point in Table VI ( $J_{\rm p2}$  = 0.0000). This response is illustrated in Fig. 15. The dynamic response of this point is satisfactory while a load change of 100% is applied to the system (Fig. 16). Moreover, the system keeps switching stability after the dynamic response.

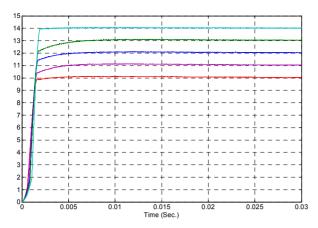

# E. Start-up Optimization for Various Operating Points

Both poles and the right-half-plane zero of the boost converter depend on the steady-state duty cycle. Therefore, the Bode plots for various operating points exhibit a significant variation. A classical PID controller designed based on the frequency response may not respond well to the significant changes in the operating point [24].

The optimization in the previous parts was performed for the nominal operating point. The optimization was conducted for several system operating points to make the system robust for different voltage references. The design variables, PID

Fig. 15. Chaos rejection for the (a) large-signal response and the first point of Table 6, (b) phase plot.

Fig. 16. Chaotic behavior before and after the 100% load increase (at 0.2 s) for the first point in Table VI.

parameters, and objective functions are considered to have the worst start-up response overshoot and settling time. The reference voltage is equal to 10, 11, 12, 13, and 14 V. Table VII presents the results of this optimization. The minimum of the hard limiter is set to zero, while the maximum is set proportional to the reference voltage to obtain these results (i.e., maximum of hard limiter = 0.058 \* reference voltage). The ratio is estimated using the results in Table V.

Point one of the Pareto front is presented in Fig. 17. This point provides a fast start-up response for a wide range of

Fig. 17. Optimized start-up response for five different references (point 1 in Table VII).

TABLE VII

PARETO SET (I.E., PID COEFFICIENTS) AND PARETO FRONT (I.E.,

WORST SETTLING TIME AND OVERSHOOT FOR VARIOUS

OPERATING POINTS)

| Point | K <sub>p</sub> | K <sub>i</sub> | $\mathbf{K}_{\mathbf{d}}$ | Setting<br>time<br>(Sec.) | Overshoot<br>(Percent) |

|-------|----------------|----------------|---------------------------|---------------------------|------------------------|

| 1     | 1.7            | 93.7726        | 0.0016                    | 0.0048                    | 1.3                    |

| 2     | 1.959          | 96.4222        | 0.0023                    | 0.0075                    | 0.82                   |

| 3     | 1.959          | 96.4222        | 0.0024                    | 0.0088                    | 0.78                   |

| 4     | 1.959          | 96.4222        | 0.003                     | 0.0125                    | 0.73                   |

| 5     | 1.5638         | 79.0163        | 0.0028                    | 0.0145                    | 0.69                   |

| 6     | 1.9816         | 94.8275        | 0.0035                    | 0.0147                    | 0.46                   |

references with nearly no overshoot. A high robustness is achieved using the SPEA algorithm. Similarly, the effect of other disturbance sources in the load and input voltage is considered.

#### VI. OPTIMIZATION OF FRACTIONAL ORDER PID CONTROLLER

## A. Design Parameter and Objective Functions

Five parameters should be designed for the FOPID controller according to the control objectives. The initial members of the first population are represented by 5-dimension vectors. These initial values are randomly generated in the defined range.

The optimization stop criterion is based on the maximum number of generations to be produced. Accordingly, 100 generations are used in this paper.

The Crone approximation with an order of 5 and a frequency range equal to [0.01; 1000000] rad/s for FOPID controller is used.

#### B. Optimization of Start-Up Response

This optimization uses the FOPID coefficients as the design variables. The objective functions are as follows:

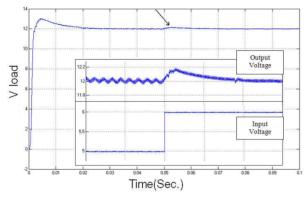

(b) Fig. 18. Start-up response for results of the Pareto front in Table 8: points (a) 1 and (b) 2.

$F_1$ : Overshoot = Max y

$F_2$ : Settling time = Min t, where error < 1.5%

error

$$=\frac{12-y_d}{12}100\%$$

where *y* is the DC output voltage of the boost converter. Table 8 shows the results of the SPEA program.

The results (Table VIII) show that the fractionality of the derivation and integration parts of the optimum results is very low but has a significant effect. The start-up responses for these results are presented in Fig. 18. These simulation results verify the effectiveness of the tuning strategy proposed in this part.

The Pareto optimization is a useful tool for preference evaluation and parameter selection in the design of power converters. From an engineering perspective, the goal of the optimization is finding the optimal solution, gaining insight on the system properties being designed, and visualizing the trade-off between them.

#### C. Optimization of Start-Up and Dynamic Responses

Aside from the characteristics of the start-up response, the dynamic response is also considered an objective function in this section. The dynamic response is defined as follows:

$F_3$ : Dynamic overshoot = Max y after t = 0.2 s. where the input voltage has a step change from 5 V to 6 V at 0.2 s. Table IX presents the results of this optimization.

The fractionality of the results in Table IX is notably higher than that in Table 8. The designer can design the FOPID controller according to point 5 in Table IX if he/she

TABLE VIII

PARETO SET AND PARETO FRONT FOR THE FOPID CONTROLLER AND OPTIMIZATION

OF THE START-UP RESPONSE OVERSHOOT AND SETTLING TIME

| Point | K <sub>P</sub> | K <sub>I</sub> | K <sub>D</sub> | α      | β       | Overshoot<br>(Percent) | Setting time<br>(Sec.) |

|-------|----------------|----------------|----------------|--------|---------|------------------------|------------------------|

| 1     | 1.5885         | 40.8865        | 0.0015         | 0.9048 | 0.99999 | 0.535                  | 0.0017                 |

| 2     | 1.4244         | 40.8731        | 0.0015         | 0.9048 | 0.99999 | 0.0000                 | 0.0035                 |

TABLE IX

PARETO SET AND PARETO FRONT FOR FOPID CONTROLLER, OPTIMIZATION OF START-UP OVERSHOOT, SETTLING TIME, AND DYNAMIC RESPONSE

| Point | $\mathbf{K}_{\mathbf{p}}$ | K <sub>i</sub> | $K_d$  | α      | β      | Overshoot<br>(Percent) | Setting time<br>(Sec.) | Dynamic overshoot<br>(Percent) |

|-------|---------------------------|----------------|--------|--------|--------|------------------------|------------------------|--------------------------------|

| 1     | 1.4052                    | 39.3011        | 0.0050 | 0.9322 | 0.7228 | 12.6483                | 0.0529                 | 1.6458                         |

| 2     | 0.6963                    | 78.5440        | 0.0052 | 0.8502 | 0.8319 | 62.8625                | 0.0466                 | 0.9483                         |

| 3     | 1.1933                    | 62.3019        | 0.0038 | 0.9792 | 0.9118 | 0.0558                 | 0.0109                 | 2.5742                         |

| 4     | 1.6808                    | 82.0184        | 0.0049 | 0.9658 | 0.8530 | 2.2417                 | 0.0122                 | 1.7692                         |

| 5     | 0.8956                    | 40.3368        | 0.0038 | 0.8616 | 0.8007 | 78.9633                | 0.0917                 | 0.7950                         |

| 6     | 0.6607                    | 31.8860        | 0.0042 | 0.8512 | 0.7656 | 60.1817                | 0.0684                 | 1.0242                         |

| 7     | 1.4406                    | 85.0000        | 0.0033 | 0.9848 | 0.7098 | 17.7683                | 0.0209                 | 1.4842                         |

| 8     | 1.4052                    | 39.3011        | 0.0050 | 0.9322 | 0.7098 | 12.6483                | 0.0543                 | 1.6075                         |

| 9     | 0.6607                    | 31.8851        | 0.0042 | 0.8544 | 0.8545 | 41.4792                | 0.0343                 | 1.0492                         |

Table X  ${\it Pareto Set and Pareto Front for the FOPID Controller, Optimization of Start-Up Overshoot, } \\ {\it Settling Time, and Dynamic Response, Maximum Bandwidth} \textit{W}_{\it H} \mbox{ of } 40,000 \mbox{ rad/s}$

| Point | K <sub>P</sub> | K <sub>I</sub> | K <sub>D</sub> | α      | β        | Overshoot<br>(Percent) | Setting time<br>(Sec.) |

|-------|----------------|----------------|----------------|--------|----------|------------------------|------------------------|

| 1     | 0.1000         | 16.4459        | 0.0007         | 0.8938 | 0.999999 | 0.5200                 | 0.0017                 |

| 2     | 0.1000         | 16.4459        | 0.0007         | 0.9157 | 0.999999 | 0.0000                 | 0.004                  |

Fig. 19. Start-up and dynamic responses for point 5 in Table 9. Dynamic response is for a step change in the input voltage from 5 V to 6 V at t = 0.2 s: (a) start-up and (b) dynamic responses.

Fig. 20. Start-up and dynamic responses for point 3 in Table IX. Dynamic response is for a step change in the input voltage from 5 V to 6 V at t = 0.2 s.

selects the dynamic response as his/her first priority. This response is presented in Fig. 19. Point 3 in Table IX can be chosen if the start-up response has a higher priority considering a compromise between the start-up and the dynamic responses as the objective functions. This response is illustrated in Fig. 20.

The bandwidth of the FOPID controller is changed in this part. This change in the bandwidth ensures that the controller works within a large bandwidth. The other parameters (i.e.,  $K_p$ ,  $K_i$ ,  $K_d$ ,  $\alpha$ , and  $\beta$ ) need to be optimized again when the

Fig. 21. Start-up response of the results in Table 10: points (a) 1 and (b) 2.

Fig. 22. Comparison of the Pareto fronts for the integer-order PID and FOPID controllers (optimization of the start-up response overshoot and settling time).

bandwidth is changed. Furthermore, a new optimization is conducted for the [0.01; 40,000] rad/s bandwidth. Table 10 shows the optimization results for a bandwidth within [0.01; 40,000] rad/s. The start-up response of these results is presented in Fig. 21.

# VII. COMPARISON OF INTEGER-ORDER PID AND FOPID CONTROLLERS

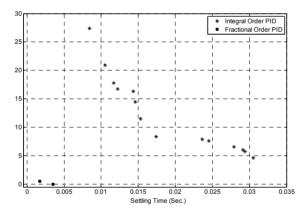

This section presents a comparison of the results of multi-objective optimization for the FOPID and integer-order PID controllers.

#### A. Comparison of Pareto front for Start-Up Response

The Pareto front of the start-up response overshoot and the settling time optimization for the integer-order PID and FOPID controllers is presented in Fig. 22.

The FOPID controller provides a much better start-up response (Fig. 22).

# B. Comparison of the Pareto Front for Dynamic and Start-Up Responses

A comparison of Tables IV and IX clearly indicates that the FOPID controller provides much better results when both the start-up and the dynamic responses are objective functions with the start-up response as the first priority.

#### VIII. EXPERIMENTAL VERIFICATION

The proposed PID and FOPID controller coefficients are validated on a boost converter prototype. The passive components and the other converter parameters are similar to those mentioned in Section IV. The discrete control scheme is implemented on a F2812 DSP for the integer-order PID controller and a dSPACE 1104 for the FOPID controller.

## A. Large-Signal Response

The experimental results of the start-up response for some points in Table III are illustrated in Fig. 23. Accordingly, the experimental results are quite close to the corresponding simulation results. The overshoot clearly increases from 7.5% to 30% when the settling time is reduced from 25 ms to 8 ms. One objective function becomes more desirable than the others by scrolling on the Pareto front. All these results are considered optimum, and any other PID coefficients cannot be found on the same conditions, which results in a faster settling time and a lower overshoot than the others.

# B. Large-Signal Response with More Optimization Variables

The simulation results of the optimization of start-up response overshoot and settling time, with the PID coefficients and max-min of hard limiter as design variables, have very close overshoots to each other. Given that the difference between them is not significant, for only one point of Table V, the start-up response is shown in Fig. 24. A numerical comparison of the experimental and simulation results of start-up response is presented in Table XI.

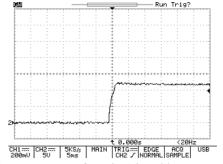

#### B. Chaos Rejection

The experimental results for the chaotic behavior of the boost converter are presented in Figs. 25 and 26. The chaotic behavior of the boost converter for point 12 in Table VI is illustrated in Fig. 25. The same behavior obtained based on point 1 in Table VI shows 100% chaos rejection (Fig. 26). The chaotic behavior is completely removed if other objective functions are not as important as the switching stability.

Fig. 23. Start-up response for some points selected from Pareto front (Table III): (a), (b), (c), (d), (e) correspond to points 5, 13, 9, 14, 11 respectively.

Fig. 24. Start-up response for point 3 in Table V.

Fig. 25. Chaotic behavior of the output voltage for the boost converter (point 12 in Table VI).

Fig. 26. Rejection of the chaotic behavior for the boost converter (point 1 in Table VI).

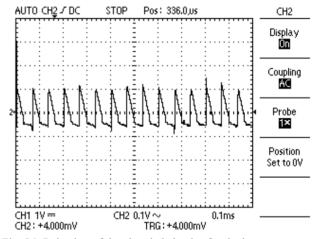

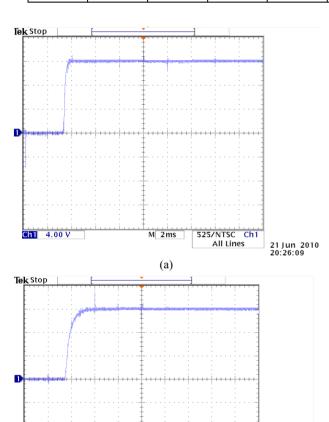

## D. Large-Signal Response with FOPID Controller

The order of the Crone approximation is 5 for the experimental implementation of the FOPID controller. Furthermore, the bandwidth with a valid approximation is [0.01; 40,000] rad/s. Table 12 shows the experimental results, while Fig. 27 presents the start-up waveforms. A comparison of Tables 10 and 12 shows that the experimental results effectively confirm the theoretical results.

$\label{thm:comparison} TABLE\ XI$  Comparison of the Experimental and the Simulation Results

|       |       | Simulatio         | n results     | Experimental results |               |  |

|-------|-------|-------------------|---------------|----------------------|---------------|--|

| Table | Point | Settling time (s) | Overshoot (%) | Settling time (s)    | Overshoot (%) |  |

| 3     | 5     | 0.0279            | 6.5633        | 0.0252               | 7.5           |  |

| 3     | 13    | 0.0174            | 8.3858        | 0.0165               | 9.1           |  |

| 3     | 9     | 0.0153            | 11.4933       | 0.0152               | 11.7          |  |

| 3     | 14    | 0.0122            | 16.7625       | 0.0120               | 18.3          |  |

| 3     | 11    | 0.0084            | 27.4358       | 0.0076               | 29.1          |  |

| 5     | 3     | 0.0025            | 0.3075        | 0.0021               | 0.8           |  |

TABLE XII

EXPERIMENTAL RESULTS FOR THE FOPID CONTROLLER

| Point | K <sub>P</sub> | K <sub>I</sub> | K <sub>D</sub> | α      | β        | Overshoot (Percent) | Setting time (Sec.) |

|-------|----------------|----------------|----------------|--------|----------|---------------------|---------------------|

| 1     | 0.1000         | 16.4459        | 0.0007         | 0.8938 | 0.999999 | 0.5200              | 0.002               |

| 2     | 0.1000         | 16.4459        | 0.0007         | 0.9157 | 0.999999 | 0.0000              | 0.004               |

(b) Fig. 27. Start-up response for the results of Table X: points (a) 1 and (b) 2.

525/NTSC Ch

All Lines

4.00 V

#### IX. CONCLUSION

This study simultaneously optimizes some important features of the boost converter. These features include the

large-signal response overshoot and settling time, dynamic response, and switching stability. The SPEA is used to improve these features. A designer can easily choose any of the results based on their features and his/her own engineering view with the help of the Pareto sets and fronts obtained in this paper. SPEA multi-objective optimization is employed to overcome the difficulties of designing the FOPID controller in the second part of the paper. The optimized FOPID controller exhibits a good dynamic response and an excellent start-up response. The extensive simulation results verify that the tuning of the PID and FOPID controllers with the use of the SPEA multi-objective approach is highly effective, rejects chaotic behavior, and provides robustness against change in the operating point. Moreover, the experimental results validate the theoretical results that were presented and discussed

#### REFERENCES

- [1] S. M. R. Rafiei, R. Ghazi, R. Asgharian, M. Barakati, and H. A. Toliyat, "Robust control of DC-DC PWM converters: A comparison of H\_inf, Miu, and fuzzy logic based approaches," in *Proc. the IEEE 2003 Control Applications Conference*, pp. 603-608, 2003.

- [2] R. W. Erickson and D. Maksimovic, Fundamentals of Power Electronics, 2nd ed., Kluwer Academic Publisher, 2000.

- [3] F. Alonge, F. D'Ippolito, T. Cangemi, "Identification and robust control of DC/DC converter Hammerstein model," *IEEE Trans. Power Electron.*, Vol. 23, No. 6, pp. 2990-3003, Nov. 2008.

- [4] A. G. Beccuti, G. Papafotiou, and M. Morari, "Optimal control of the DC-DC converter," in *Proc. the IEEE* Conference on Decision and Control, pp. 4457-4462, 2005

- [5] J. Leyva-Ramos and A. Morales-Saldaa "Uncertainty models for switch-mode DC-DC converters," *IEEE Trans. Circuits Syst. I, Fundam. Theory Appl.*, Vol. 47, No. 2, pp. 200-203, Feb. 2000.

- [6] G. Garcera, A. Abellan, and E. Figueres, "Sensitivity study of the control loops of DC-DC converters by means of robust parametric control theory," *IEEE Trans. Ind. Electron.*, Vol.49, No. 3, pp. 581-586, Jun. 2002.

- [7] J. H. B. Dean and D. C. Hamill, "Instability, subharmonics, and chaos in power electronic systems," *IEEE Trans. Power Electron.*, Vol. 5, No. 3, pp. 581-586, Jul. 1990.

- [8] D. C. Hamill, J. H. B. Dean, and D. J. Jefferies, "Modeling of chaotic DC-DC converters by iterated non-linear mappings," *IEEE Trans. Power Electron.*, Vol. 7, No. 1, pp. 21-36, Jan. 1992.

- [9] R. D. Middlebrook and S. Cuk, "A general unified approach to modeling switching converter power stages," *Int. J. Electron.*, Vol. 42, No. 6, pp. 521-550, Jun. 1977.

- [10] F. J. Perez-Pinal, C. Nunez, and R. Alvarez, "Direct voltage control for boost converter," 1<sup>st</sup> International Conference on Electrical and Electronics Engineering, pp. 579-583, 2004.

- [11] E. Vidal-Idiarte, L. Martinez-Salamero, H.Valderrama-Blavi, F. Guinjoan, and J. Maixe, , "Analysis and design of H<sup>∞</sup> control of non-minimum phase-switching converters," *IEEE Trans. Circuits Syst. I, Fundam. Theory Appl.*, Vol. 50, No. 10, pp. 1316-1323, Oct. 2003.

- [12] R. Naim, G. Weiss, and S. Ben-Yaakov, "H<sup>∞</sup> control applied to boost power converters" *IEEE Trans. Power Electron.*, Vol. 12, No. 4, pp. 677-683, Jul. 1997.

- [13] R. Naim, G. Weiss, and S. Ben-Yaakov, "H<sup>®</sup> control of boost converters: Comparison to voltage mode, feedforword and current mode controls," in *Proc. IEEE PESC Tage Mode*, Vol. 2, pp. 1327–1332, 1995.

- [14] G. C. Loannidis and S. N. Manias, "H<sup>∞</sup> loop-shaping control schemes for buck converter and their evaluation using μ-analysis," *IEE Proc-Electr. Power Appl.*, Vol. 146, No. 2, pp. 237-246, Mar. 1999.

- 146, No. 2, pp. 237-246, Mar. 1999.

[15] S. Buso, "Design of a robust voltage controller for a buck-boost converter using μ-Synthesis," IEEE Trans. Contr. Syst. Technol., Vol. 7, No. 2, pp. 222-229, Mar. 1999.

- [16] G. F. Wallis and R. Tymerski, "Generalized approach for  $\mu$  synthesis of robust switching regulators," IEEE Trans. Aerosp. Electron. Syst., Vol. 36, No. 2, pp. 422-431, Apr. 2000

- [17] J. Bu, M. Sznaier, Z.-Q. Wang, and I. Batarseh, "Robust controller design for a parallel resonant converter using μ-sysnthesis," *IEEE Trans. Power Electron.*, Vol. 12, No. 5, pp. 837-853, Sep. 1997.

- [18] F. Alonge, F. D'Ippolito, and T. Cangemi, "Hammerstein model-based robust control of DC/DC converters," in *Proc. IEEE PEDS2007 Conf.*, pp. 754-762, 2007.

- [19] T. Gupta, R. R. Boudreaux, R. M. Nelms, and Y. Hung, "Implementation of a fuzzy controller for DC-DC converters using an 8-b micro controller," *IEEE Trans. Ind. Electron.*, Vol. 44, No. 5, pp. 661-669, Oct. 1997.

- [20] V. S. C. Ravirij and P. C. Sen, "Comparative study of proportional-integral, sliding mode, and fuzzy logic controllers for power converters," *IEEE Trans. Ind. Appl.*, Vol. 33, No. 2, pp 518-524, Apr. 1997.

- [21] E. Vidal, L. Martinez-Salamero, F. Guinjoan, J. Calvente, and Gomariz, "Sliding and fuzzy control of a boost converter using an 8-bit microcontroller," *IEE Proc.-Electr. Power Appl.*, Vol. 151, No. 1, pp. 5-11, Jan, 2004.

- [22] A. Balestrino, A. Landi, and L. Sani, "CUK converter global control via fuzzy logic and scaling factors," *IEEE Trans. Ind. Appl.*, Vol. 38, No. 2, pp. 406-413, Apr. 2002.

- [23] S. K. Mazumder, A. H. Nayfeh, and D. Borojevic, "Robust control of parallel DC-DC buck converters by combining integral-variable-structure and multiple-sliding-surface control schemes," *IEEE Trans. Power Electron.*, Vol. 17, No. 3, pp. 428-437, May 2002.

- [24] L. Guo, J. Y. Hung, and R. M. Nelms, "Evaluation of DSP-based PID and fuzzy controllers for DC-DC

- converters" *IEEE Trans. Ind. Electron.*, Vol. 56, No. 16, pp. 2237-2249, Jun. 2009

- [25] F. H. F. Leung, P. K. S. Tam, and C. K. Li, "The control of switching dc-dc converters – A general LQR problem," *IEEE Trans. Ind. Electron.* Vol. 38, No. 1, pp. 65-71, Feb. 1991.

- [26] F. H. F. Leung, P. K. S. Tam, and C. K. Li, "An improved LQR-based controller for switching DC-DC converters," *IEEE Trans. Ind. Electron.*, Vol. 40, No. 5, pp. 521-528, Oct. 1993.

- [27] D. Czarkowski, L. R. Pujara, and M. K. Kazimicrczuk, "Robust stability of state-feedback control of PWM DC-DC push-pull converter," *IEEE Trans. Ind. Electron.*, Vol. 42, No. 1, pp. 108-111, Feb. 1995.

- [28] Y.-H. Chang and L.-W. Chen, "QFT-based robust controller design of series resonant DC/DC converters," *IEEE International Electric Machines and Drives Conference*, pp.18-21, 1997.

- [29] A. Davoudi, J. Jatskevich, and T. D. Rybel, "Numerical state-space average-value modeling of PWM Dc-DC converters operating in DCM and CCM," *IEEE Trans. Power Electron.*, Vol. 21, No. 4, pp.1003-1012, Jul. 2006

[30] J. H. B. Deane, "Chaos in a current-mode controlled boost

- [30] J. H. B. Deane, "Chaos in a current-mode controlled boost DC-DC converter," *IEEE Trans. Circuits Syst. I, Fundam. Theory Appl.*, Vol. 39. No. 8, pp. 680-683, Aug. 1992.

- [31] S. Banerjee, "Nonlinear modelling and bifurcation in boost converter," *IEEE Trans. Power Electron.*, Vol. 13, No. 2, pp. 253-260, Mar. 1998.

- [32] J. L. R. Marrero, J. M. Font, and G. C. Verghese, "Analysis of the chaotic regime for DC-DC converters under current-mode control," *Power Electronics Specialists Conference*, PESC, pp. 1477-1483, 1996.

- [33] M. B. Shadmand, M. Mosa, R. S. Balog, and H. A. Rub, "An improved MPPT technique of high gain DC-DC converter by model predictive control for photovoltaic applications," *IEEE Applied Power Electronics Conference & Exposition (APEC)*, pp. 2993-2999, 2014.

- [34] R. Ahmadi, D. Paschedag, and M. Ferdowsi "Closed-loop input and output impedances of DC-DC switching converters operating in voltage and current mode control," *IECON 2010-36th Annual Conference on IEEE Industrial Electronics Society*, pp. 2311-2316, 2100.

- [35] N. Zhu, W. L. Wu, and J. A. Shao. "Chaos control strategy for the current-mode boost converter with small parameter perturbation," *Journal of Circuits and Systems*, Vol. 9, pp. 79-83, Feb. 2004.

- [36] A. N. Natsheh, N. B. Janson, and J. G. Kettleborough "Control of chaos in a DC-DC boost converter," *IEEE International Symposium on Industrial Electronics*, pp. 317-322, 2008.

- [37] D. Maiti, A. Acharya M. Chakraborty, A. Konar, and R. Janarthanan, "Tuning PID and fractional PID controllers using the integral time absolute error criterion," 4th International Conference on Information and Automation for Sustainability, pp. 457-462, 2008.

- [38] B. Jayakrishna and V. Agarwal "FPGA implementation of QFT based controller for a buck type DC-DC power converter and comparison with fractional and integral order PID controllers," *COMPEL*, pp. 1-6, 2008.

- [39] Y. Luo and J. Li, "The controlling parameters tuning and its application of fractional order PID bacterial foraging-based oriented by particle swarm optimization," *IEEE International Conference on Intelligent Computing and Intelligent Systems*, pp. 4-7, 2009.

- [40] D. Valsrio, J. S. da Costa, "Tuning of fractional PID controllers with Ziegler-Nichols-type rules," Signal Processing, Vol. 86, No. 10, pp. 2771-2784, Oct. 2006.

- [41] E. Zitzler and L. Thiele, "Multi-objective evolutionary algorithms A comparative case study and the strength pareto approach," *IEEE Trans. Evol. Comput.*, Vol. 3, No. 4, pp. 257-271, Nov. 1999.

- [42] P. Hajela and C. Y. Lin, "Genetic search strategies in multicriterion optimal design," *Structural Optimization*, Vol. 4, No. 2, pp. 99-107, Jun. 1992.

- [43] M. P. Fourman, "Compaction of symbolic layout using genetic algorithms," in *Proc. Int. Conf. Genetic Algorithms and Their Applications*, 1985.

- [44] J. Horn, N. Nafpliotis, and D. E. Goldberg, "A niched pareto genetic algorithm for multiobjective optimization," in *Proc. 1st IEEE Conf. Evolutionary Computation, IEEE* World Congr. Computational Computation, Vol. 1, pp. 82-87, 1994.

- [45] N. Srinivas and K. Deb, "Multiobjective optimization using nondominated sorting in genetic algorithms," *IEEE Trans. Evol. Comput.*, Vol. 2, No. 3, pp. 221-248, Sep. 1994.

- [46] Y. Zhao, Y. Gao, Z. Hu, Y. Yang, J. Zhan, and Y. Zhang, "Damping inter area oscillations of power systems by a fractional order PID controller," *International Conference* on Energy and Environment Technology, pp. 103-106, 2009

- [47] J.-Y. Cao and B.-G. Cao, "Design of fractional order controller based on particle swarm optimization," *Int. J. Control, Automat., Syst.*, Vol. 4, No.6, pp. 775-781, Dec. 2006

- [48] D. Kundu, K. Suresh, S. Ghosh, and S. Das, "Designing fractional-order PID controller using a modified invasive weed optimization algorithm," World Congress on Nature and Biologically Inspired Computing, pp. 1315-1320, 2009

- [49] I. Podlubny "Fractional-order system and PI<sup>α</sup>D<sup>β</sup> controller," *IEEE Trans. Automat. Contr.*, No. 44, No. 1, pp. 208-214, Jan. 1999.

- [50] J.-Y. Cao, J. Liang, B.-G. Cao, "Optimization of fractional ordered PID controllers based on genetic algorithms," in Proc. the Fourth International Conference on Machine Learning and Cybernetics, pp. 5686-5689, 2005.

- [51] M. Cai, X. Pan, and Y. Du, "New elite multi-parent crossover evolutionary optimization algorithm of parameters tuning of fractional-order PID controller and its application," Fourth International Conference on Innovative Computing, Information and Control, pp. 64-67, 2009

Ahmadreza Amirahmadi received his B.S. and M.S. degrees in Electrical Engineering from Shahrood University of Technology, Shahrood, Iran, in 2007 and 2010, respectively. He has been a Ph.D. student at the University of Central Florida, Orlando, Florida, USA, since 2010. Since 2010, he has been a research assistant in the Florida

Power Electronics Center, University of Central Florida, where he focuses on efficiency optimization of DC/AC inverters. He has been a marketing engineering intern from June 2013 at the International Rectifier. His research interests include high-frequency DC-DC converters, soft switching control of power electronic inverters, and efficiency optimization.

Mohammadreza Rafiei was born in 1969 in Tehran, Iran. He received his B.Sc. degree with honors from the Sistan and Baluchistan University, Zahedan, Iran, in 1991. He obtained his M.Sc. and Ph.D. degrees in Electrical Engineering from the Ferdowsi University of Mashhad, Mashhad, Iran, in 1995 and 2000, respectively. He is a senior

member of the IEEE since 2004 and a member of the IEEE Control Systems, Power Electronics, and Power and Energy Societies. His fields of interest includes energy system optimization, control systems, power electronics, and power quality. He serves as a reviewer for several IEEE journals, among other publications.

Kambiz Tehrani was born in Tehran, Iran, in 1978. He received his degree in Electrical Engineering from the University of Arak, Iran, in 2003. He received his master's degree and his Ph.D. degree from the University of Nancy (INPL), Nancy, France, in 2005 and 2010, respectively. He is currently an associate professor in Power

Electronics Systems at ESIGELEC in Rouen, France. His main research interests include energy systems, current control systems, and multilevel inverters.

Giovanni Griva received his five-year degree and a Ph.D. degree in Electrical Engineering from the Politecnico di Torino, Torino, Italy in 1990 and 1994, respectively. He joined the Department of Electrical Engineering, Politecnico di Torino, as assistant professor in 1995. He has been an associate professor since 2002. His fields of interest are power

electronics conversion, integrated electronic/electromechanical design, high-performance speed servo drives, and applications of power quality issues. He has published over 100 papers in international conferences and technical journals. He was the recipient of the IEEE Industry Applications Society First Prize Paper Award in 1992. He serves as a reviewer for the IET Proceedings and IEEE Transactions on Industrial Electronics.

Issa Batarseh received his B.S. degree in Electrical and Computer Engineering and his M.S. and Ph.D. degrees in Electrical Engineering in 1983, 1985, and 1990, respectively, from the University of Illinois, Chicago. He is currently a professor of electrical engineering in the School of Electrical Engineering and Computer

Science, University of Central Florida (UCF), Orlando, FL. He became a visiting assistant professor at Purdue University, Calumet, IN from 1989 to 1990 before joining the Department of Electrical and Computer Engineering, UCF in 1991. His research interests include power electronics, developing high-frequency energy conversion systems to improve power density, efficiency, and performance, the analysis and design of high-frequency solar and wind energy conversion topologies, and power factor correction techniques. He has authored or co-authored more than 60 refereed journals and 300 conference papers in addition to securing 14 U.S. patents. He is also an author of a textbook entitled Power Electronic Circuits (New York: John Wiley, 2003). He is a registered professional engineer in the state of Florida and a fellow member of IEE. He has served as a chairman for the IEEE PESC '07 conference and was the chair of the IEEE Power Engineering Chapter and the IEEE Orlando Section.