# 이중게이트 구조의 Junctionless FET 의 성능 개선에 대한 연구

## Development of Gate Structure in Junctionless Double Gate Field Effect Transistors

조 일 환\*. 서 동 선\*\*

Il Hwan Cho\*, Dongsun Seo\*\*

#### Abstract

We propose the multiple gate structure of double gate junctionless metal oxide silicon field oxide transistor (JL MOSFET) for device optimization. Since different workfunction within multiple metal gates, electric potential nearby source and drain region is modulated in accordance with metal gate length. On current, off current and threshold voltage are influenced with gate structure and make possible to meet some device specification. Through the device simulation work, performance optimization of double gate JL MOSFETs are introduced and investigated.

#### 요 약

본 논문에서는 이중 게이트 junctionless MOSFET 의 성능 최적화를 위하여 다중 게이트 형태를 적용하여 평가 한다. 금속 게이트들 사이의 일함수가 서로 다르므로 다중 게이트 구조를 적용할 경우 금속게이트 길이에 따라 소 스와 드레인 주변의 전위를 조절할 수 있다. 동작 전류와 누설 전류 그리고 동작 전압은 게이트 구조에 의해 조절 이 가능하며 이로 인한 동작 특성 최적화가 가능하다. 본 연구에서는 반도체 소자 시뮬레이션을 통하여 junctionless MOSFET 의 최적화를 구현하고 분석하는 연구를 수행 한다

Key words: device optimization, multiple gate, junctionless field effect transistor, threshold voltage, subthreshold swing

ISSN: 1226-7244 (Print)

This work was supported by 2015 Research Fund of Myongji University

Manuscript received Nov 20, 2015; revised Dec 1. 2015; accepted Dec 3, 2015

This is an Open-Access article distributed under the terms of the Creative Commons Attribution Non-Commercial License (http://creativecommons.org/licenses/by-nc/3.0) which permits unrestricted non-commercial use, distribution, and reproduction in any medium, provided the original work is properly cited.

## 1. 서론

3차원 게이트 구조의 MOSFET 의 경우 나노 크기의 트랜지스터 개발에 있어서 가장 큰 가능 성을 갖는 구조로 개발되어 왔다[1]. 하지만 3차워 MOSFET 에서는 정밀한 도핑 농도의 분포를 만 드는 것이 해결하기 어려운 문제 중 하나이다. Junctionless (JL) MOSFET 의 경우 소스와 드

<sup>\*</sup> Dept. of Electronic Engineering, Myongji University

<sup>★ +81-31-330-6369,</sup> e-mail: sdsphoto@mju.ac.kr

<sup>※</sup> Acknowledgement

레인 그리고 채널 사이에 도핑을 사용하지 않으므로 정밀한 도핑 농도의 분포에 대한 문제가 발생하지 않는다<sup>[2]</sup>. 하지만 이와 같은 JL MOSFET의 경우에도 짧은 채널로 인한 열화 문제가 발생하게 되며, 이와 같은 문제는 일반적인 MOSFET과 마찬가지로 다중 게이트와 고유전을 유전체를 적용하는 것으로 성능을 개선하는 것이 가능하다<sup>[3]-[9]</sup>. 이전에 진행된 성능 개선 연구의 경우 단일 물질 게이트 구조로 진행되어 있으며, 이는 게이트 물질 최적화를 통한 성능 개서에 많은 제약이 있음을 의미한다<sup>[10]</sup>. 본 연구에서는 복수의 게이트 물질을 적용하여 JL MOSFET의 성능을 개선하는 방안에 대하여 소개한다.

## Ⅱ. 본론

#### 1. 시뮬레이션 소자 구조

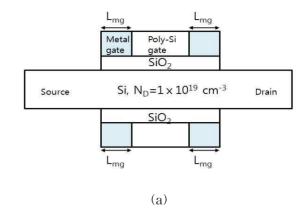

본 연구에서는 이중게이트 구조의 MOSFET 소자의 특성을 분석하기 위하여 SILVACO 의 A TLAS 시뮬레이터를 사용한다. 시뮬레이션은 2 차원 구조로 진행되며 그림 1 (a) 에 소자의 구조가 소개되어 있다. 그림 1 (a) 에서 보는 바와 같이 게이트는 기본적으로 이중 게이트 구조를 하고 있으며 세 영역으로 나뉘어 서 서로 다른 물질로 구성된다. 그림 1 (a) 에서 의 Lmg 는 금속 게이트 부분의 길이를 의미하며 nm에서 50 nm 의 값을 갖는다. 또한 금속 게이 트는 일함수 5.0 eV를 갖는 것으로 가정하였다. 폴리실리콘 게이트의 경우 도핑 농도는  $10^{20}~\mathrm{cm}^3$ (인, phosphorus ) 의 값을 가지며, L<sub>mg</sub> 에 따른 소자 특성 비교 시 전체 채널 길이는 100 nm 로 고정된다. 실리콘 채널의 폭은 10 nm. 게이트 산 화막의 두께는 3 nm 로 고정되어 있으며 도핑 농도는  $10^{19}$  cm<sup>3</sup> (인, phosphorus) 의 값을 갖는 다. 본 연구에 사용된 ATLAS 시뮬레이터에 구 현된 소자의 구조는 그림 1(b) 에 소개되어 있다.

Fig. 1. (a) Schematic structure of double gate junctionless MOSFETs with different gate materials (b) Simulation structure of suggested JL MOSFETs

그림 1. (a) 이중 게이트 구조를 갖는 JL MOSFET 에 다 중 금속 게이트 구조를 적용한 개요도 (b) 제안 된 JL MOSFET 의 시뮬레이션 구조

## 2. 결과 및 분석

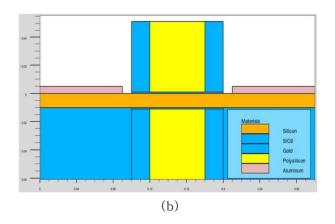

그림 2(a)에 금속 게이트 길이에 따른 JL MOSFET 의 기본적인 전압-전류 특성이 소개되어 있다.

본 연구에서 소자의 전압, 전류 특성을 구하기위하여 Lombardi mobility 모델과 Shockley Read Hall recombination 모델이 사용되었다. 드레인 전압은 1 V로 고정되어 있으며, 게이트 전압은 0 V에서 2 V 까지 변화시켜가면서 소자의전기적 특성을 측정하였다. 또한 폴리실리콘 게이트만을 사용할 경우에 채널 공핍에 의하여 소자가 꺼지지 않도록 채널 도핑과 채널 폭이 설정되어 있다. 그림 2(a)에서 전체를 폴리실리콘을 사용한 경우에 비해서 금속 게이트 비중을 증가

Fig. 2 (a) Current voltage relationship of various gate JL MOSFETs (b) Off current variation with gate configuration (c) On current variation with gate configuration

그림 2 (a) 게이트 구조에 따른 전압-전류 관계 (b) 게이 트 구조에 따른 누설 전류 특성 (c) 게이트 구조 에 따른 동작 전류 특성

시킬수록 동작 전압이 증가하고 누설 전류가 감소하는 특징을 알 수 있다. 그림 2(b) 와 (c)에 소개되어 있는 바와 같이 동작 전류와 누설 전류 모두 게이트 구조에 영향을 받는 것을 알 수 있 다. 이와 같은 특성을 분석하기 위하여 추출된

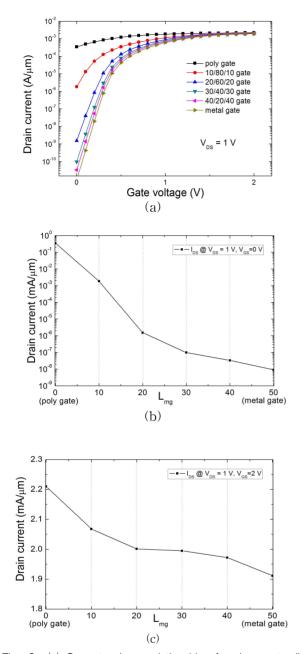

Fig. 3. Energy band diagram of multi gate JL MOSFETs with zero bias with (a) metal gate (b)  $L_{mg}$  =10 nm (c)  $L_{mg}$  =40 nm (d) poly gate

그림 3.  $0\ V\$ 전압이 인가되었을 때 게이트 구조에 따른 JL MOSFET 의 채널 영역 에너지 밴드 다이어그램 (a) metal gate (b)  $L_{mg}$  = 40 nm (c)  $L_{mg}$  = 10 nm (d) poly gate

에너지 밴드가 그림 3에 소개 되어 있다. 에너지 밴드는 전압을 인가되지 않은 상태에서, 채널 가운데 영역에서 추출하였다. 그림 3(a)에서 볼수 있는 것 같이 전체를 금속 게이트로 제작할 경우 MOSFET 에서와 유사하게 소스와 채널, 그리고 드레인과 채널 사이에 에너지 장벽이 형성됨을 알 수 있다.

그림 3에서 알 수 있는 바와 같이 금속 게이트 부분의 비율이 변할수록 실질적으로 소스와 채널 사이에 존재하는 장벽의 높이도 변함을 알 수 있 다.

이와 같은 전위 장벽의 변화로 인하여 JL MOSFET 의 동작 전압과 동작 전류 그리고 누설 전류의 특성이 변하게 되는 것이다. 특히 누설 전류의 경우 금속 게이트 부분이 증가하여 장벽이 증가하면 효율적으로 억제되는 것을 확인할수 있으며 이번 연구에 사용된 구조에서 에너지밴드에서 발생하는 장벽은 최대 0.38 eV 까지 얻을 수 있었다.

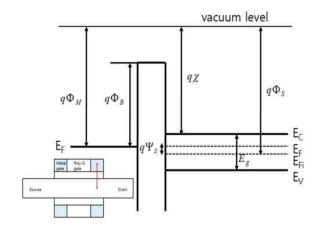

Fig. 4. Energy band diagram from metal gate to channel region with 0V gate bias. (Metal workfunction is assumed to be same with silicon workfunction)

그림 4. 0 V 전압이 인가되었을 때 금속게이트 영역에서 채널 영역까지의 에너지밴드 다이어그램 (금속의 일함수와 실리콘의 일함수가 같은 경우를 가정)

그림 3의 에너지 밴드의 경우 그림 4와 같이 채널 영역과 게이트 영역의 일함수 차이에 의하여 밴드구조가 결정된다. 그림 4는 금속 게이트 부분에서 채널 영역까지의 에너지 밴드를 나타낸 것으로,  $\Phi_{M}$  은 금속의 일함수,  $\Phi_{B}$  은 유전체의

전도대와 금속의 페르미 준위사이의 장벽,  $\Phi_s$ 은 실리콘 채널영역의 일함수,  $E_g$  은 실리콘의 에너지 밴드갭,  $\chi$ 은 실리콘의 전자친화도,  $\Psi_s$ 은 실리콘 표면 전위를 나타낸다. 게이트 물질의 일함수와 실리콘의 일함수차이에 의하여 채널 부분의에너지 밴드가 결정되므로, 금속의 종류를 변경할 경우 폴리실리콘이 사용된 부분과의 에너지밴드 차이를 변경할 수 있게 된다.

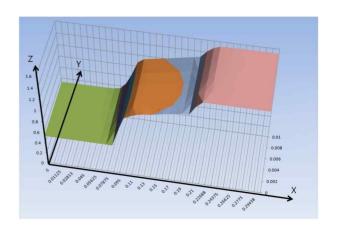

본 연구에 사용된 JL MOSFET 의 경우 기본 적으로 이중게이트 구조를 갖고 있으므로 금속 게이트의 영향에 대하여 신중하게 분석 되어야 한다. 그림 5에는 Lmg 가 10 nm 인 소자의 채널 영역에서의 전압 분포가 소개되어 있다. 게이트 전압은 2 V 드레인 전압은 1 V 가 인가 되었다. 그림에서 왼쪽이 소스 영역이며 오른쪽 영역이 드레인 영역을 나타낸다. 또한 그림에서 X 축은 채널의 길이 방향, Y 방향은 채널의 너비 방향 그리고 Z 방향은 채널의 높이 방향을 의미한다. 그림 5에서 알 수 있는 것과 같이 채널 폭이 10 nm 로 얇은 두께를 갖고 있지만 채널 내에서의 전압 분포가 일정하지 않게 분포함을 알 수 있 다. 이와 같은 전압 분포에서 채널에 흐르는 전 류 또한 일정하지 않음을 예상할 수 있다. 이것 은 금속 게이트를 이용하여 다중 게이트 구조를 적용하는 것 이외에 채널의 두께도 소자 특성의 최적화에 중요한 변수로 작용할 수 있음을 의미 하다.

Fig. 5. Potential distribution in the channel region with  $V_{\text{date}} = 2 \ V \ \text{and} \ V_{\text{drain}} = 1 \ V$

그림 5. 게이트 전압에 2 V, 드레인 전압에 1 V 가 인가 되어 있을 때, 채널 영역 내에서의 전압 분포

## Ⅲ 결론

본 연구에서는 다중 금속 게이트 구조를 이중게이트 형태의 JL MOSFET 에 적용하여 성능변화 특성을 분석하였다. 소자 시뮬레이션을 통한 연구 결과 다중 금속 게이트 구조를 이용할경우 동작 전압과 누설 전류와 같은 소자의 동작특성을 조절하는 것이 가능하다. 서로 다른 일함수를 갖는 게이트 물질을 통하여 소스와 드레인사이에 에너지 장벽을 만드는 것이 가능하며 이때 금속 게이트 부분의 길이를 조절할 경우 소자의 동작 특성을 미세하게 조절할 수 있다. 기존의 단일 물질을 사용하는 게이트의 경우 물질의특성을 변경하는 것에 상당한 제약을 받지만, 본연구에 제안된 구조를 이용할 경우 JL MOSFET의 특성을 정밀하게 제어하는 것이 가능하다.

## References

[1] T. Park, H. J. Cho, J. D. Choe, I. H. Cho, D. Park, E. Yoon and J. H. Lee, "Characteristics of body-tied triple-gate pMOSFETs," *IEEE Electron Dev. Lett.* 25, pp. 798–800, December 2011.

[2] C.-W.Lee, A. Afzalian, N. D. Akhavan, R. Yan, I. Ferain, and J. - P Colinge, "Junctionless multigate field-effect transistor," *Appl. Phys. Lett.* 94, pp. 053511-1-053511-2, February 2009.

[3] J. Rahul, S. Yadav, and V. K. Bohat, "Effects of metal gate electrode and HfO2 in junctionless vertical double gate MOSFET," *Intl. Journal of Sci. Eng. And Tech.* 3, pp. 671–674, May 2014.

[4] E. Gnani, A. Gnudi, S. Reggiani, and G. Baccarani, "Theory of the junctionless nanowire FET," *IEEE Electron Dev. Lett.* 58, pp. 2903–2910, September 2011.

[5] M. Wu, X. Jin, H. - I. Kwon, R. Chuai, X. Liu, and J. - H. Lee, "The optimal design of junctionless transistors with double-gate structure for reducing the effect of

band-to-band tunneling," *Journal of Semi. Tech.* and Sci. 13, pp. 245–251, June 2013.

[6] R. Rios, A. Cappellani, M. Armstrong, A. Budrevich, H. Gomez, R. Pai, N. Rahhal-orabi, and K. Kuhn, "Comparison of junctionless and conventional trigate transistors with Lg down to 26 nm," *IEEE Electron Dev. Lett. 32, pp. 1170–1172*, September 2011.

[7] S. - J. Choi, D. Moon, S. Kim, J. - H. Ahn, J. - S. Lee, J. - Y. Kim, and Y. - K. Choi, "Nonvolatile memory by all-around-gate junctionless transistor composed of silicon nanowire on bulk substrate," *IEEE Electron Dev. Lett.* 32, pp. 602–604, May 2011.

[8] Y. Song, C. Zhang, R. Dowdy, K. Chabak, P. K. Mohseni, W. Choi, and X. Li, "III-V junctionless gate-all-around nanowire MOSFETs for high linearity low power applications," *IEEE Electron Dev. Lett.* 35, pp. 324–326, March 2014. [9] S. Gundapaneni, S. Ganguly, and A. Kottantharayil, "Enhanced electrostatic integrity of short-channel junctionless transistor with high κ spacers," *IEEE Electron Dev. Lett.* 32, pp. 1325–1327, October 2011.

[10] M. - K. Jung, S. - H. Liu, J. - H. Ahn, K. - T. Lee, H. - S. Kang, Y. - W. Kim, and K. - P. Suh, "The influence of Cu diffusion on NMOS device characteristics," *Journal of Kor. Phy. Soc.* 40, pp. 692–696, April 2002.

## BIOGRAPHY

Il Hwan Cho (Member)

2000 : B.S. degree in Electrical Engineering, KAIST

2002: M.S. degree in Electrical Engineering, Seoul National University.

2007 : Ph.D. degree in Electrical Engineering, Seoul National University.

2012 ~ Present: Associate Professor, Dept. of Electronics, Myong Ji University

## Dongsun Seo (Life Member)

1980: B.S. degree in Electronics, Yonsei University 1985: M.S. degree in Electronics, Yonsei University

1989: Ph.D. degree in Electrical

Engineering, Univ. of New

Mexico, USA 1990 ~ Present: Professor, Dept. of Electronics,

MyongJi University