# 비정질 규소막의 공정조건이 HSG-Si 형성에 미치는 영향

정재영<sup>\*</sup> · 강성준<sup>\*\*</sup> · 정양희<sup>\*\*\*</sup>

Influence of the process conditions for the amorphous silicon on the HSG-Si formation

Jae-Young Jeong\* · Seong-Jun Kang\*\* · Yang-Hee Joung\*\*\*

요 약

본 논문은 비정질 규소막 성장의 공정 조건이 저장 전극의 표면에 HSG-Si를 형성할 때 미치는 영향을 조사하였다. 그 결과 비정질 규소막의 인 농도가 5.5±0.1E19 atoms/cm 이상이면 HSG-Si가 제대로 형성되지 않는 인 농도 의존성을 나타내었다. 또한 HSG 두께가 500Å 이상에서는 전극과 전극을 단락시키는 비트 불량을 유발하기 때문에 비정질 규소막의 인농도는 4.5E19 atoms/cm, HSG 임계 두께는 450Å이 최적 조건임을 확인하였다.

#### **ABSTRACT**

In this paper, the processing conditions of the amorphous silicon film growth were investigated the effect in forming the HSG-Si on the surface of the storage electrode. As a result, when the amorphous silicon film phosphorus concentration is greater than  $5.5 \pm 0.1E19$  atoms / cm, HSG-Si is not formed correctly and showed the concentration dependency of HSG formation. Also, the optimum condition of the phosphorus concentration for amorphous silicon and HSG thickness are 4.5E19 atoms/cm and  $450\,\text{Å}$ , respectively, because of the HSG thickness over the  $500\,\text{Å}$  create to bit failure according to a short of the electrodes and the electrode.

#### 키워드

Amorphous Silicon, Storage Electrode, Phosphorus, Concetration 비정질 규소막, 저장 전극, 인, 농도

#### 1. 서 론

반도체 집적회로의 고집적화, 초미세화와 함께 소자의 특성 향상을 위하여 새로운 공정기술의 개발의 요구되고 있다[1-2]. 특히, 고집적 메모리소자의 발전에 따라 단위 셀 면적은 축소되었고 이는 셀 커패시턴스의 감소를 초래하게 되므로 커패시턴스 확보를 위해 저장전극의 표면적 증가가 필수적이므로 이에 대한 많은 연구가 이루어져 왔다[3-5]. 최근 이와 같

은 문제점을 해결하기 위한 방법으로 커패시터 축전용량 향상을 위해 저장전극의 표면에 HSG-Si(: Hemispherical Grained Silicon)을 형성하여 셀의 면적과 높이를 증가시키지 않고 전극의 표면적을 증가시켜 DRAM 커패시터를 제작할 수 있는 HSG-Si 형성 방법과 특성에 대한 관심이 집중되고 있다[6-10]. 따라서 본 논문에서는 저장전극으로 사용되는 LPCVD를 이용한 비정질 규소막의 공정 조건이 HSG-Si 형성에 미치는 영향을 조사하였다.

- \* LG 디스플레이(pride116@naver.com)

- \*\* 전남대학교 전기및반도체공학과(ferroksj@jnu.ac.kr)

- \*\*\* 교신저자 : 전남대학교 전기및반도체공학과

- •접 수 일: 2015. 10. 01 •수정완료일: 2015. 11. 13 •게재확정일: 2015. 11. 23

- Received: Oct. 01, 2015, Revised: Nov. 13, 2015, Accepted: Nov. 23, 2015

- · Corresponding author: Yang-Hee Joung

Dept. of Electrical and Semiconductor Engineering, Chonnam National University

Email: jyanghee@jnu.ac.kr

#### II. 시료제작 및 실험방법

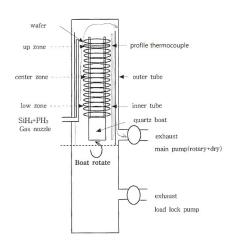

#### 2.1 저압화학기상 증착장치

비정질 규소막을 증착하기 위하여 그림 1과 같은 수직형 LPCVD를 사용하였다. 시료인 웨이퍼는 150매 까지 탑재할 수 있으며, 웨이퍼가 최상측에 놓인 것을 up zone, 가운데를 center zone, 최하측을 low zone 이라고 정의하였다.

그림 1. L/L LPCVD 장치의 개략도

Fig. 1 Schematic diagram of LPCVD system with load lock

가스 공급은 규소막을 중착시키기 위한 사일렌 (SiH4)과 캐리어를 주입하는데 사용되는 PH3 및 대기 반송을 위한 N2 등이 있으며 이들 가스는 MFC를 통하여 정밀하게 제어하여 챔버내 분사노즐을 통하여 공급하게 된다. 가스 공급의 균일성 향상을 위하여 분사노즐의 up zone과 low zone의 구경을 달리하였으며, 웨이퍼가 탑재되어 있는 석영 보트는 중착하는 동안 균일성 향상을 위하여 회전하게 되어있다.

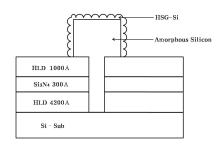

#### 2.2 시료제작

비저항이 9~12Ωcm이고 결정면이 (100)인 P형 실리콘 웨이퍼를 사용하였고, 커패시터 전극으로 사용되는 HSG-Si 시료는 그림 2와 같이 제작되었다. 실리콘웨이퍼 위에 열산화막인 HLD막을 약 4200Å 증착하고, 질화막의 전세정으로 SC1(NH4OH:H2O2:H2O

=1:2:10) 세정을 50℃에서 10분간 처리하고 자연산화막 제거를 위한 1:500=HF:H2O 세정을 한 후, 질화막을 300Å 증착하였다. 여기에 사용된 질화막은 고진공상 태에서 HSG-Si 형성시 실리콘 기판에서의 불순물과 금속 배선 및 하지층에서의 확산(out diffusion)에 의한 진공도 저하를 방지하는 차단막 역할을 하게 된다.

그림 2. HSG-Si 시료의 단면도 Fig. 2 Cross section of the HSG-Si sample

질화막 형성 후 HSG-Si 하지막인 HLD를 1000Å 증착하고 사진식각 공정과 플라즈마 RIE(Reaction Ion Etch)로 콘택 홀을 형성하였다. HSG-Si 형성을 위한 비정질 규소막 증착은 압력을 약 130~150 Pa, 온도는 520~540℃로 하고 가스의 유량은 SiH4:PH3=1000:19sccm으로 LPCVD에서 약 11,300Å 증착하였으며, 두께 측정에는 Opti-probe 사의 OP-2600을 사용하였다. HSG-Si 는 주성엔지니어링의 Eureka-2000을 사용하였으며 1×10<sup>-7</sup>Torr의 압력으로 약 770℃에서 Si2H6 10sccm을 100초간 주입하고 100초간 열처리를 통하여 형성하였다.

#### 2.3 실험방법

본 실험에서는 box형 저장전극의 유효면적 확장을 위한 HSG-Si 형성 공정에서 비정질 규소막의 증착 조건이 HSG-Si의 성장에 미치는 영향을 조사하기 위하여 11,300Å의 비정질 규소막에 인농도를 각각 8.0±0.3E19, 450±0.1E19, 3.5±0.1E19atoms/㎝로 하였으며, 증착온도는 520∼540℃로하여 장치내에서 웨이퍼가 놓이는 위치간의 농도 분포를 TRXRF(: Total Reflection X-ray Fluorescence) 모델 Rigaku-3630을이용하여 확인하였다. 또한 HSG-Si의 형성과 인농도의 상관관계를 조사하기 위하여 Nanometrics사의 Nano-8000 모델을 사용하여 HSG-Si의 두께를 측정

하여 비교하였다. 완성된 box형 캐패시터의 전기적 특성은 Keithley S-457을 이용하여 셀 커패시턴스 값 을 측정하고 이들이 인 농도 및 HSG-Si의 두께차이 에 의한 상관관계도 함께 조사하였다.

## Ⅲ. 결과 및 논의

#### 3.1 비정질 규소막의 성장

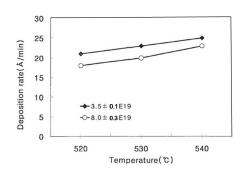

인이 주입된 비정질 규소막의 인농도와 증착 온도에 따른 성장률을 그림 3에 나타내었다.

그림 3. 인주입 비정질 규소막의 인농도와 증착온도에 따른 증착률

Fig. 3 The amorphous silicon deposition rate by the temperature and phosphorous concentration

그림에서 보는바와 같이 동일한 농도에서의 비정질 규소막의 성장 속도는 온도를 상승시키면 가스 분자의 열적 활성화 에너지가 증가하고, 확산 속도가 빨라져 성장 속도가 증가함을 알 수 있다. 또한 불순물이증가하면 실리콘과의 재결합 확률이 줄어들기 때문에성장 속도는 감소하는 것으로 해석된다.

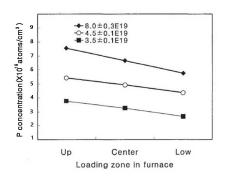

#### 3.2 비정질 규소막의 농도 분포

LPCVD에서 성장한 비정질 규소막의 장치내 zone 별 농도 차이를 그림 4에 나타내었다. 그림에서 보는 바와 같이 batch형의 확산로이기 때문에 위치간의 확산 속도 및 가스의 흐름에 따라 up zone의 농도가 높고, low zone의 농도가 낮아짐을 볼 수 있다. 8.0±0.3E19atoms/cm의 경우는 위치별 인동도 균일성이 약 17%로 좋지 않으며 아래쪽으로 갈수록 인동도가 낮게 나타나고 있다.

그림 4. LPCVD 위치별 인농도

Fig. 4 The phosphorus concentration according to the loading zone of LPCVD

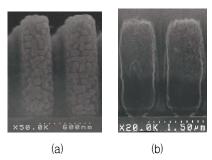

이와 같은 로내 위치간 농도 불균일성을 개선하기 위하여 인동도를 4.50±0.1E19atoms/cm, 압력을 133Pa에서 150Pa로 하였을 때 위치간 균일성이 약 12%로 향상되었으며 인농도가 3.5±0.1E19atoms/cm에서도 동일하게 유지되었다. 또한 인농도가 8.0±0.3E19atoms/cm로 하였을 경우 로의 위쪽에 위치한 웨이퍼에서 box형 저장전극의 하부에 HSG-Si형성 불량이 나타났으며 이를 그림 5에 나타내었다. 이는 low zone으로 갈수록 인농도 분포가 낮게 형성되는데 대략5.50±0.2E19atoms/cm 이상의 up zone에서 특히 인농도 분포가 높기 때문에 비정질 규소막이 재결정화 되어서 전극 표면에서의 실리콘 원자의 이동이 원활히일어나지 않아 HSG-Si의 성장에 영향을 미친 것으로해석된다.

그림 5. HSG-Si 형성 단면도 (a) 정상 (b) 비정상 Fig. 5 Cross section of HSG-Si formation (a) normal (b) abnormal

#### 3.3 HSG-Si의 형성

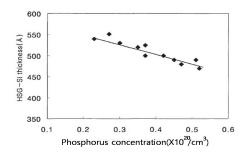

인주입 비정질 규소막의 인농도에 따른 HSG-Si 두께를 그림 6에 나타내었다. 그림에서와 같이 HSG의 두께는 인 농도에 반비례하는 강한 상관 관계를 가지는 것으로 나타났으며 이는 HSG-Si의 형성에 변수가 될 수 있는 것으로 해석되어 진다.

그림 6. 인농도에 따른 HSG-Si 두께 Fig. 6 HSG-Si thickness according to the phosphorus concentration

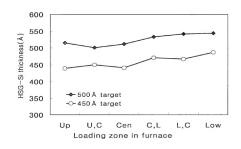

그림 7은 HSG-Si 두께를 약 500Å 및 450Å 범위에서 중착하였을 경우 확산로 위치에 따른 HSG-Si 두께를 나타낸 것으로 인농도가 낮을수록 비정질 규소 막의 표면에서 실리콘 원자의 이동에 의한 핵 형성은 촉진되고, 인 농도가 높으면 표면에서의 실리콘 원자의 이동을 방해하는 것으로 해석된다. 이는 앞의 up zone에서 높은 불순물 농도와 HSG 형성 불량과도 일치하는 결과이다. 또한 HSG-Si의 두께는 인주입 비정질 규소막을 증착하는 장치에서의 증착 위치에 따른 의존성을 보이며, low zone에 up zone에 비해서 약 20~40Å 두껍게 증착됨을 볼 수 있는데 이는 위치간의 농도 유의차에 기인된 것으로 해석할 수 있다.

그림 7. Loading zone별 HSG-Si 두께 Fig. 7 HSG-Si thickness according to the loading zone

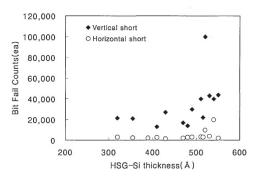

그림8은 HSG-Si의 두께에 따른 전극간의 단락 불량률을 나타내었다. 그림에서와 같이 HSG-Si 두께를 500Å 이상으로 증가시키면 실리콘의 그레인이 떨어져 전극과 전극간의 단락으로 비트 불량이 급격히 증가하여 소자의 수율에 악영향을 미치게 된다. 따라서 HSG-Si의 임계 두께는 450Å범위가 적합한 것으로 판단할 수 있다.

그림 8. HSG-Si 두께와 Bit 불량 수 Fig. 8 Bit failure counts vs. HSG-Si thickness

#### 3.4 셀 캐패시턴스의 측정

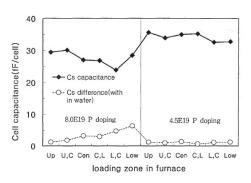

저장 전극의 인농도와 셀 커패시턴스의 관계를 그림 9에 나타내었다. .인주입 비정질 규소막 증착시 인 농도를 8.0±0.3E19atoms/cm로 적용한 시료의 경우 셀커패시턴스가 23~30fF/cell로 전반적으로 낮으면서 HSG-Si의 형성이 잘 이루어지지 않는 이상 단면이관찰되었고, 이는 장치내의 up zone의 경우에 불량이증가하는 위치 의존성을 나타내는 것과도 일치한다.

그림 9. 저장 전극의 인농도와 셀 커패시턴스 Fig. 9 Cell capacitance vs. phosphorus concentration of storage electrode

인농도를 평균 4.50±0.1E19atoms/cm로 낮게 제작한 시료의 경우에는 위치간의 인농도의 균일성이 개선되었고, 평균 셀 커패시턴스가 약 5.77fF/cell 만큼 증가되었다. 이는 농도를 낮게 제작할 경우에는 표면에서의 실리콘 이동에 의한 HSG-Si 형성이 촉진되어, 표면적의 증가에 따른 커패시턴스의 증가로 해석할 수있다. 그러나 인농도를 과도하게 낮추면 저장 전극의저항 및 과도한 HSG-Si 형성등의 문제가 발생할 수있다.

## Ⅵ. 결 론

본 논문에서는 메모리 소자의 고집적화와 미세화에 따라 단위 셀 면적의 감소에 의한 셀 커패시턴스를 보상하기 위한 방법으로 전극의 유효 면적을 크게 할수 있는 HSG-Si 형성 기술에서 인주입 비정질 규소막 증착의 공정 조건이 HGS-Si 형성에 미치는 영향을 조사하였다. 그 결과로 인주입 비정질 규소막은 증착 온도를 상승시키면 증착 속도가 증가하고 인농도를 증가시키면 증착속도는 감소함을 알았다. 또한 인농도는 실리콘 표면에서 HSG-Si 형성을 결정하는 중요한 요소이며 인농도가 높으면 HSG-Si 형성이 잘이루어지지 않아 커패시턴스가 낮게 나타났다. 더불어 HSG-Si의 두께가 500Å 이상에서는 HSG-Si의 과잉으로 전극간의 단락 불량이 발생함을 확인할 수 있었다.

#### Reference

- [1] S. Mori, E. Sakagami, Y. Kaneko, and Y. Ohshima, "Bottom-Oxide scaling for Thin Nitride/Oxide interpoly dielectric in stacked-Gate Nonvolatile Memory Cells," *IEEE Trans. on Electron Devices*, vol. 39, no. 2, 1992, pp. 283-291.

- [2] N. Matsuo, Y. Nakata, and S. Okada, "The oxide nitride oxide film deposition on the tunnel-structured polycrystalline silicon (polysilicon) electrodes for high-density dRAMs," J. Appl. Phys., vol. 70, no. 9, 1991, pp. 5085-5089.

- [3] S. Mun, S. Kang, and Y. Joung, "A study on the DC parameter matching according to the shrink of 0.13um technology," J. of the Korea Institute of Electronic Communication Sciences, vol. 9, no. 11, 2014, pp. 1227-1232.

- [4] S. Mun, S. Kang, and Y. Joung, "A study on the Hot Carrier Injection Improvement of I/O Transistor," J. of the Korea Institute of Electronic Communication Sciences, vol. 7, no. 8, 2014, pp. 847-852.

- [5] S. Mun, S. Kang, and Y. Joung, "A study on Flicker Noise Improvement by Decoupled Plasma Nitridation," J. of the Korea Institute of Electronic Communication Sciences, vol. 9, no. 7, 2014, pp. 747-752.

- [6] N. Matsuo, H. Ogawa, T. Kouzaki, and S. Okada, "Nucleation and growth mechanism of hemispherical grain polycrystalline silicon," J. of Appl. Phys. Lett., vol. 60, no. 21, 1992, pp. 2607-2609.

- [7] A. Sakai, T. Tatsumi, and K. Ishida, "Growth kinetics of Si hemispherical grains on clean amorphous Si surfaces," J. of Vacuum Science, vol. 11, no. 6, 1993, pp. 2950-2953.

- [8] H. Watanabe, T. Tatsumi, and S. Ohnishi, "Hemispherical grained Si formation on in-situ phosphorus doped amorphous-Si electrode for 256Mb DRAMs capacitor," *IEEE. Trans. Electron Devices*, vol. 42, no. 7, 1995, pp. 1247-1254.

- [9] H. Watanabe, A. Sakai, T. Tatsumi, and T. Niino, "Hemispherical grain silicon for high density DRAMs," *Solid State Technology*, vol. 35, no. 7, 1992, pp. 29-33.

- [10] H. Watanabe, T. Tatsumi, and S. Ohnishi, "A new cylindrical capacitor using hemispherical grained Si for 256Mb DRAMs," *IEEE Electron Devices meeting*, *IEDM* 92, San Francisco, USA, Dec. 1992, pp. 259-262.

## 저자 소개

# 정재영(Jae-Young Jeong)

1986년 명지대학교 전자공학과졸 업(공학사)

2002년 전남대학교 대학원 전기 및반도체공학과 졸업(공학석사)

2007년 전남대학교 전기및반도체공학과(공학박사) 현재 LG 디스플레이 부장

※ 관심분야 : 디스플레이 공정 개발

# 강성준(Seong-jun Kang)

1989년 인하대학교 응용물리학과 졸업(공학사) 1994년 인하대학교 대학원 전자 재료공학과 졸업(공학석사)

1999년 인하대학교 대학원 전자재료공학과 졸업 (공학박사)

현재 전남대학교 전기및반도체공학과 교수 ※ 관심분야 : 기능성박막, 반도체공정 및 재료

# 정양희(Yang-hee Joung)

1983년 단국대학교 응용물리학과 졸업(공학사) 1985년 인하대학교 대학원 응용 물리학과 졸업(공학석사)

1993년 인하대학교 대학원 전자재료공학과 졸업 (공학박사)

1995년 ~현재 전남대학교 전기및반도체공학과 교수 ※ 관심분야 : 반도체 공정 및 물성