논문 2015-52-12-8

# 위치 기반 시스템을 위한 CMOS IR-UWB RFIC

(A CMOS IR-UWB RFIC for Location Based Systems)

이 중 무\*. 박 명 철\*. 어 유 성\*\*

(Jung Moo Lee, Myung Chul Park, and Yun Seong Eo<sup>©</sup>)

요 약

본 논문에서는 근거리 위치 기반 시스템을 위한 3 - 5 GHz IR-UWB(impulse radio-ultra wide band) RFIC를 제안한다. 수 신기의 구조는 에너지 검출 방식으로 설계되었고, 고속 sampling을 하기 위해서 4 bit ADC 와 DLL(delay locked loop) 을 이 용하여 equivalent-time sampling 기술을 사용하도록 설계되었다. 송신기는 저전력의 디지털 UWB impulse generator 를 설계 하였다. 설계된 IR-UWB RFIC 는 CMOS 0.18 μm 공정을 이용하여 제작되었다. 측정된 수신기의 감도는 -85.7 dBm 이며, 송 신기와 수신기는 1.8 V 전원 전압에서 각각 32 mA 와 25.5 mA 의 전류를 소모한다.

#### Abstract

This paper presents a fully integrated 3 - 5 GHz IR-UWB(impulse radio ultra-wide band) RFIC for Location based system. The receiver architecture adopts the energy detection method and for high speed sampling, the equivalent time sampling technique using the integrated DLL(delay locked loop) and 4 bit ADC. The digitally synthesized UWB impulse generator with low power consumption is also designed. The designed IR-UWB RFIC is implemented on 0.18 µm CMOS technology. The receiver's sensitivity is -85.7 dBm and the current consumption of receiver and transmitter is 32 mA and 25.5 mA respectively at 1.8 V supply.

Keywords: UWB RF transceiver, Digitally synthesized impulse generator, RF notch filter, Energy detection receiver

## I. 서 론

최근 UWB(ultra-wide band) 시스템은 위치 기반

시스템과 WBAN(wireless body area network) 뿐만

\* 학생회원, \*\* 정회원, 광운대학교 전자공학과 (Department of EE, Kwangwoon University)

Received; October 6, 2015 Revised; October 21, 2015

Accepted; November 20, 2015

아니라 탐지 레이더 시스템에서 각광받는 분야로서 활 발히 연구가 이루어지고 있다<sup>[1~6]</sup>. 위치기반 시스템은 근거리 무선 통신 시스템으로 저전력화가 요구되며 소 형화 추세이다. 따라서 본 논문에서는 이러한 고속의 전송 속도가 가능하면서도 소형화 및 저전력이 가능한 UWB 수신기 및 위치기반 시스템 송수신기 회로를 설 계하였다.

위치기반 시스템 분야에서 사용할 수 있는 UWB 수 신기의 구조는 저전력, 소형화가 가능해야 하며 또한 고속통신이 가능해야 한다. 본 논문에서는 이러한 점들 을 고려하여 회로 구조가 비교적 간단하며 별도의 주파 수 합성기가 필요치 않는 비동기 방식의 수신기와 디 지털 로직을 이용한 UWB impulse generator를 적용한 송신기 구조를 사용하였다.

<sup>©</sup> Corresponding Author(E-mail: yseo71@kw.ac.kr)

<sup>※</sup> 본 연구는 미래창조과학부 및 정보통신기술연구진흥 센터의 정보통신방송 연구개발사업[14-911-01-001, 준밀리미터파 채널적응형 안테나 및 송수신기 개발] 의 지원과 한국산업기술평가관리원을 통해 산업통상 자원부의 산업기술혁신사업 (10053023, IoT향 다중대 역 RF MEMS 소자 원천기술 개발)의 지원을 받아 수행되었음.

또한 UWB 수신기의 RF Front End 부가 광대역 특성을 갖고 있기 때문에, 외부의 방해신호 또한 실제 채널에 수신되고 합성되어서 결국에 수신기의 수신감도를 낮출 수 있다. 실험적인 경험에 의하면 인접한 2.4 GHz 대역의 ISM band 와 WCDMA band 등의 상당히 큰인접 잡음으로 이해 UWB RF 수신기의 감도가 열화되거나 심지어 포화되어 동작하지 않는 경우가 발생하기 쉽다. 지금까지 이들을 제거하기 위해 RF notch filter 를 구현한 사례들이 있으나 아직까지 감도 등의정확한 데이터를 제공한 사례는 많지 않다. 그러므로본 논문에서는 2.4 GHz 이하 대역을 억제하기 위한 가변 가능한 능동 RF notch filter가 RF front end에 집적되었고, 수신 감도 또한 RF notch filter의 동작에 의해 개선되는 것을 보여 준다.

또한 디지털부와의 interface 를 용이하게 하기 위하여 4 Bit ADC(analog to digital converter)가 RFIC에 같이 집적 되었다. 위치인식을 위해 impulse 형태의 UWB 신호를 이용하여 거리 측정을 하기 위해선 고속 ADC 를 이용하여 신호의 위치를 찾아야 하는 문제가 있게 된다. 3 - 10 GHz 대역의 UWB impulse 신호의 경우 ADC 의 sampling 주파수가 최소 12 - 40 GHz 가 되어야 하는데, 이는 현실적으로 불가능하게 된다. 따라서 본 논문에서는 이러한 문제점을 해결하기 위해 일반적인 UWB 수신기 구조에 4 bit ADC 및 DLL 을 이용한 equivalent-time sampling 기법을 적용하여 송수신 거리를 측정하는 회로를 설계하였다.

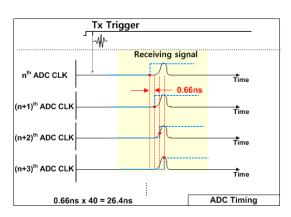

Carrier 주파수가 없이 multiplier에서 만들어진 UWB 의 envelope 신호는 증폭되고 ADC 에서 적절한속도의 clock으로 sampling 된다. 10 cm 이하의 거리해상도를 얻기 위해서 equivalent-time sampling 시간간격은 0.66 ns으로 결정된다. 사용된 sampling clock은 37.8 MHz crystal이기 때문에, 0.66 ns 의 offset 시간을 가진 40 clock이 DLL 회로로부터 제공된다. ADC의 sampling clock속도는 37.8 MHz이고 ADC회로는 4 Bit의 flash type이 적용된다. 40 clock으로부터 만들어진 26.4 ns의 시간은 공기 중에서 7.9 m의 거리와 같고,이는 디지털 영역에서 시간 간격을 반복함으로써 79 m까지 가상확장할 수 있다. 본 논문의 UWBRFIC는 0.18 μm CMOS 공정으로 제작되었다.

## Ⅱ. UWB RF 송수신기 회로 설계

#### 1. UWB 수신기

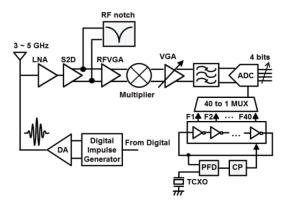

그림 1은 본 논문에서 설계한 UWB RF transceiver 의 전체적인 block diagram 을 보여준다. 수신기의 RF front end 부는 저잡음 증폭기(low noise amplifier), S2D(single to differential) 증폭기, RF notch filter, RF 가변 이득 증폭기(variable gain amplifier) 와 multiplier 로 구성되어 있고, analog 회로부는 VGA와 filter 및 ADC와 DLL로 이루어져 있다.

그림 1. 위치기반 시스템을 위한 UWB RF 송수신기의 전체적인 block diagram

Fig. 1. Overall block diagram of UWB RF transceiver for LBS.

### 가. 저잡음 증폭기 와 S2D 증폭기

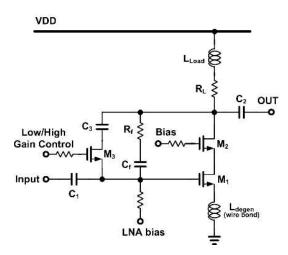

그림 2는 수신기의 첫 번째 단으로 전체 수신기의 잡음 특성을 결정짓는 광대역 특성의 single-end 저잡음 증폭기 회로를 나타내고 있다. 이 저잡음 증폭기 회로는 광대역 매칭을 위한 resistive shunt feedback 구조와 shunt inductor 를 사용하여 광대역 특성을 갖도록설계되었다. 수신기에서 single 형태의 신호는 공통잡음에 취약하므로 fully differential 형태로 설계를 해야 한다. 그러므로 첫 번째 단 저잡음 증폭기에 의해 증폭된 UWB 신호는 S2D(single to differential) 증폭기 회로에 의해서 fully differential 신호로 변환된다.

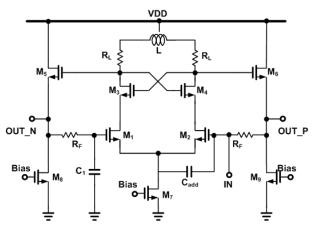

그림 3은 설계한 S2D 증폭기 회로도로서 공통 게이트(CG) 증폭기와 공통 소스(CS) 증폭기를 사용하였다. 또한 cross-coupled 구조를 사용하고 shunt inductor 를 사용하여 광대역 특성을 얻을 수 있었다. 공통 게이트 와 공통 소스 단 사이에서의 이득과 위상의 균형을 위

그림 2. 광대역 single-end 저잡음 증폭기 회로도 Fig. 2. Wideband single-end LNA Circuit.

그림 3. 광대역 S2D 증폭기 회로도

Fig. 3. Circuit schematic of the wideband S2D amplifier.

해서 부가적인 capacitor( $C_{add}$ )가 전류 소스 M7의  $C_{db}$  효과를 보상하기 위해서 공통 소스 증폭기의 NMOS에 병렬로 추가되었다<sup>[7]</sup>.

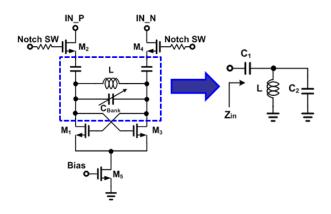

## 나. RF Notch Filter

그림 4는 RF notch filter 의 회로도를 보여준다. S2D 증폭기에 의해서 fully differential 형태로 변환된 신호로 설계하였다. RF notch filter는 가변 가능한 형태로 2.4 GHz 이하의 방해 신호를 약화시키기 위하여 S2D amplifier의 부하로 연결되어 있다. Notch filter의 차단주파수는 L 과 digitally 전환 가능한 capacitor bank로 조정 가능하다. 등가 모델로 표현되는 notch filter 의 차단주파수는 다음과 같다.

그림 4. RF notch filter 회로 Fig. 4. RF notch filter circuit.

그림 5. RF 가변 이득 증폭기 회로도

Fig. 5. Circuit schematic of the variable gain amplifier.

$$\omega_{cutoff} = \sqrt{\frac{1}{(C_1 + C_2)L}} \tag{1}$$

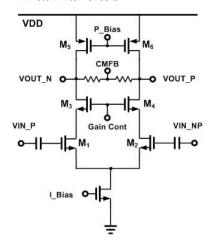

#### 다. RF 가변 이득 증폭기 및 Multiplier

IR-UWB 시스템에서 사용하는 UWB 신호의 경우수 ns 의 매우 짧은 펄스폭을 가지고 있다. 이를 정확한 시간에 복조를 하기 위해서는 주파수 합성기를 이용한 동기화가 필요하나 이는 저전력 및 소형화하기에는 부적합하다. 따라서 본 논문에서는 gilbert mixer를 self-mixing 하는 방법을 사용하는 비동기 방식을 사용하였다. 수신된 UWB 신호 자체를 self-mixing 하기 때문에 별도의 주파수 합성기가 필요치 않으며, 수신되는 신호와의 동기를 위한 회로도 필요치 않아 간단한 구조로 복조 할 수 있다. Gilbert cell mixer 의 경우 passive mixer에 비하여 높은 변환 이득을 가지고 있지만 본 논문에서처럼 self-mixing을 하는 경우에는 일반적 경

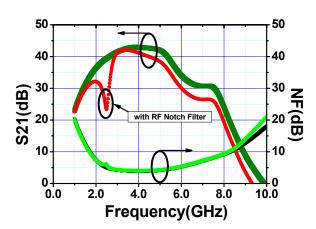

그림 6. RF notch filter 'on'/'off' 에 따른 RF front-end 이 득 및 NF simulation 결과

Fig. 6. Simulation result of gain and NF with RF notch filter 'on'/'off'.

우에 비하여 낮은 변환 이득을 갖게 된다. 따라서 RF 가변 이득 증폭기를 설계하여 충분한 이득을 가지고 증폭하여 수신단의 가변 범위를 향상 시켰다. 그림 5는 설계된 RF 가변 이득 증폭기를 보여주고 있다. 가변 이득 증폭기는 cascode 형태의 fully differential 구조로설계가 되었으며, 선형적인 이득 조절을 위해 M3와 M4의 게이트 바이어스를 조절할 수 있도록 하였다.

#### 라. RF front end simulation

그림 6은 RF front end 부의 시뮬레이션 결과를 보여준다. RF front end 부의 이득은 RF VGA와 LNA로 조정 가능하다. RF front end 부의 시뮬레이션 결과에서 볼 수 있듯이 이득과 NF는 각각 40 dB 이상과 약3.8 dB 정도로 설계 되었다. 그림 6에서 볼 수 있듯이 notch filter의 rejection은 2.4 GHz 대역에서 15 dB 이상이 되도록 설계되었다.

#### 마. Analog Baseband and ADC

RF front end 부의 마지막인 Multiplier 다음 단인 analog VGA는 UWB의 envelope 신호를 30 dB 가변적으로 증폭한다. Analog LPF(low pass filter)는 적분기형태의 종류로 대역폭은 300 MHz이다. 수신기의 마지막 단인 4 Bit ADC는 flash type 으로 sampling clock은 37.8 MHz이다. 0.66 ns의 offset-time clock을 제공하기 위해 DLL(delay locked loop) 회로를 이용하였다. Delay cell은 일반적인 VCDL(voltage controlled delay line)을 이용하여 설계되었고, DLL은 40개의 다른 clock

그림 7. Equivalent-time sampling 기법

Fig. 7. Equivalent-time sampling technique.

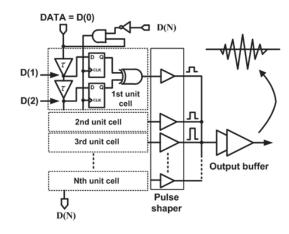

그림 8. 디지털 합성 impulse 생성기의 block diagram

Fig. 8. Block diagram of the digitally synthesized impulse generator.

들을 MUX 입력에 제공한다. 그림 7은 equivalent-time sampling 기법을 보여주는 것으로 같은 UWB 신호가 반복적으로 40번 송신되는 동안에 수신기는 0.66 ns의 offset-time clock가 순차적으로 40개의 수신된 신호를 sampling 하게 된다. 이렇게 equivalent-time sampling 동작을 하는 ADC는 사실상 1.5 GHz sampling(0.66 ns)의 동작을 얻을 수 있다.

## 2. UWB 송신기

본 논문의 송신기는 디지털 회로로 구현하여 간단한 구조와 낮은 전력을 소모하도록 설계되었다. 그림 8은 디지털 합성 impulse 송신기의 block diagram 을 보여준다. 본 논문에서 제안한 pulse 생성기는 단위 pulse generator, pulse combiner, 그리고 envelope shaper로 구성되어져 있다. 단위 pulse 생성기는 단위 시간 delay cell과 XOR 게이트 기반의 미분기로 이루어져 있다. 그

림 8에 나타나 있는 단위 시간 delay cell은 current starved type의 inverter를 사용하여 설계되었고 inverter의 전류를 조절함으로써 delay 시간을 조절할수 있다. UWB impulse 의 carrier 주파수가 1/2 τ 이기때문에 delay cell은 필수 block이다. 그리고 합성된 단위 pulse 들의 개수가 UWB pulse 의 지속 시간, 즉 대역폭을 결정한다. 가변 할 수 있는 단위 시간 delay 뿐만 아니라 합성된 pulse 들 또한 pulse 생성기 cell 을 on/off 함으로써 조절 가능하다<sup>[8]</sup>.

## Ⅲ. UWB 송수신기 측정 결과

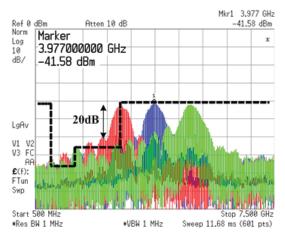

본 논문의 UWB RF 송수신기 RFIC는 0.18 µm CMOS 공정으로 제작되었고 측정하였다. 송신기의 모듈레이션을 위해 25 MHz RZ data를 이용하여 측정하였다. Carrier 주파수는 3 GHz에서 5 GHz까지 가변 할수 있다. 그림 9는 impulse 생성기의 측정 결과로 모든스펙트럼들이 요구되는 EIRP인 -41.3 dBm/MHz 를 만족한다.

수신기의 수신감도는 송신된 신호의 파워와 케이블 그리고 감쇄기의 손실을 계산하면서 케이블과 감쇄기를 이용하여 측정하였다. 집적된 RF notch filter를 이용함으로써 수신 감도는 2.4 GHz의 CW jamming 신호들과함께 있는 RF notch filter 'off' 상태에 비해서 10 dB 정도 개선되는 것을 확인 하였다. 2.4 GHz jamming 신호는 2.4 GHz 대역의 WiFi 잡음이 실제에서 가장 주

그림 9. 측정된 impulse 생성기의 스펙트럼 (3.5 GHz - 4.5 GHz)

Fig. 9. Measured spectrum of the impulse genertor. (3.5 GHz - 4.5 GHz)

요한 영향을 주기 때문에 선택되었다.

외부의 RF BPF(band pass filter) 또한 존재하고 방해신호를 제거 한다고 가정 했을 때, 방해신호의 파워는 -30 dBm 정도이다. 측정된 수신감도는 BER 10<sup>-3</sup>의 25 Mbps data rate에서 -85.7 dBm이다. 37.8 MHz의 sampling clock은 디지털부에서 제공되고 측정된 거리범위는 7.9 m에 해당하는 26.4 ns이다.

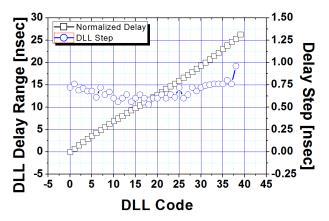

그림 10은 측정된 DLL의 특성을 나타낸 것으로 총 40개의 위상이 delay된 clock을 ADC에 제공을 해주게되며 총 26.4 ns까지의 지연이 가능하다. 그리고 이때 delay 간격은 0.66 ns로 측정되었다.

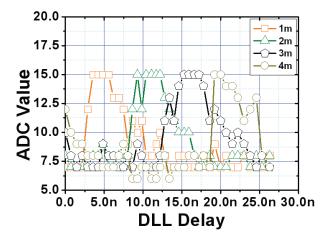

그림 11은 송신기와 수신기가 각각 1, 2, 3, 4 m 길이의 다른 RF 동축 케이블로 연결되어 있을 때 수신된 UWB envelope 신호가 ADC의 출력에서 어떻게 존재하는지 설명해준다. 케이블의 유전상수의 영향을 고려

그림 10. DLL 의 측정

Fig. 10. Measured result of DLL.

그림 11. 측정된 수신기의 ADC 출력 vs DLL 시간 delay

Fig. 11. Measured receiver ADC output vs DLL time delay.

표 1. IR-UWB 송수신기 성능 및 비교표 Table 1. Performance summary and comparison of IR-UWB transceiver.

|                          |    | [1]                 | [2]              | [3]                | This work                  |

|--------------------------|----|---------------------|------------------|--------------------|----------------------------|

| Technology               |    | BiCMOS              | CMOS             | CMOS               | CMOS                       |

|                          |    | 0.18 µm             | 0.13 µm          | 0.18 µm            | 0.18 µm                    |

| Operating                |    | $3.1 \sim 10.6$     | 4∼5 GHz          | 3∼5 GHz            | 3~5 GHz                    |

| frequency                |    | GHz                 |                  |                    |                            |

| Modulation               |    | BPSK                | DBPSK            | OOK                | OOK                        |

| Unwanted band rejection  |    | 100 Mbps            | 31 Mbps          | 1 Mbps             | 25 Mbps                    |

| Sensitivity improvement  |    | 10 dB               | N/A              | N/A                | 15 dB                      |

| Sensitivity<br>@BER 10-3 |    | -80 dBm             | -78 dBm          | -88 dBm            | -85.7 dBm                  |

| Power efficiency @1Mbps  | Tx | N/A                 | 0.7 nJ/bit       | 0.3 nJ/bit         | 20.6 pJ/bit (excluding DA) |

|                          | Rx | 53.7 nJ/bit         | 7 nJ/bit         | 4.3 nJ/bit         | 49.5 nJ/bit                |

| Chip size                |    | 2.3 mm <sup>2</sup> | $8 \text{ mm}^2$ | 12 mm <sup>2</sup> | 6.5 mm <sup>2</sup>        |

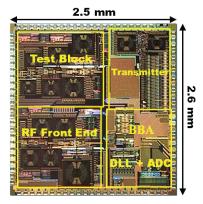

그림 12. 제작된 RFIC 칩의 사진(2.5 mm × 2.6 mm) Fig. 12. Photograph of the fabricated RFIC chip. (2.5 mm × 2.6 mm)

했을 때 전기적인 거리는 물리적인 케이블 거리에 1.5 배 정도 된다. 그러므로 20 ns 또는 4 m 케이블 길이는 실제 공기 중에서 6 m가 된다. 그리고 26 ns의 DLL delay는 실제 공기 중에서 7.9 m 정도가 된다.

표 1은 제작된 UWB RF 송수신기 RFIC 의 성능 및 비교표로 측정된 성능을 보여준다. 수신기와 송신 기의 전류 소모는 1.8 V 전원 공급에서 각각 32 mA와 25.5 mA(DA 포함해서)이다. 그림 12는 제작된 UWB RFIC의 사진을 보여준다. 칩의 크기는 2.5 mm × 2.6 mm이다.

#### Ⅳ. 결 론

본 논문에서는 위치 인식 시스템을 위한 3 - 5 GHz CMOS IR-UWB 송수신기 IC가 4 Bit ADC와 함께 구현 되었다. Equivalnet-time sampling이 DLL 회로로부터 생성된 offset-timed clock을 사용하여 이루어졌으며 0.66 ns 의 유효 해상도 또한 쉽게 얻을 수 있었다. 저전력 디지털 합성 송신기는 미국의 연방통신위원회(FCC) 규제를 준수하는 가변 가능한 UWB impulse 신호들을 제안한다. 거리는 8 m(4 - 5 m in cable)까지 측정되었으며 거리 범위는 80 m까지 확장 될 수 있다. 측정된 수신 감도는 -85.7 dBm이고, 수신기와 송신기의 전류소모는 각각 32 mA 와 25.5 mA 이다.

#### **REFERENCES**

- [1] F. Lee and A. Chandrakasan, "A BiCMOS ultra-wideband 3.1-10.6-GHzfront-end," IEEE J. Solid-State Circuits, vol. 41, no. 8, pp. 1784-1791, Aug. 2006.

- [2] D. Lachartre, B. Denis, D. Morche, L. Ouvry, M. Pezzin, B. Piaget, J.Prouvee, and P. Vincent, "A 1.1nJ/b 802.15.4a-compliant fullyintegrated UWB transceiver in 0.13μm CMOS," Proc. 56th IEEE Intern.Solid-State Circuits Conference, San Francisco, USA, 18.4, pp. 312–313a, Feb. 2009.

- [3] Y. Gao, X. Liu, Y. Zheng, S. Diao, W. Toh, Y. Wang, B. Zhao, M. Je, and C. Heng, "A low power interference robust IR-UWB transceiverSoC for WBAN applications," Proc. 8th IEEE Intern. Symp. On RadioFrequency Integration Technology, Singapore, Singapore, pp. 153-155, Nov. 2012.

- [4] A. Medi, and N. Won, "A high data-rate energy -efficient interference tolerant fully integrated CMOS frequency channelized UWB transceiver for impulse radio," IEEE J. Solid-State Circuits, vol. 43, no. 4, pp. 974-980, April 2008.

- [5] A. Vallese, A. Bevilacqua, C. Sandner, M. Tiebout, A. Gerosa, and A.Neviani, "Analysis and design of an integrated notch filter for therejection of interference in UWB systems," IEEE J. Solid-State Circuits,vol. 44, no. 2, pp. 331-343, Feb. 2009.

- [6] T. Chu, J. Roderick, S. Chang, T. Mercer, C.

- Du, H. Hashemi, "A shortrangeUWB impulse-radio CMOS sensor for human feature detection", IEEE Int. Solid-State Circuits Conf. (ISSCC) Dig. Tech. Papers, pp.294-296, Feb. 2011.

- [7] J. O. Ha, M. C. Park, S. H. Jung, Y. S. Eo, "UWB WBAN Receiver for Real Time Location System", Journal of The Institute of Electronics Engineers of Korea, Vol.50, No. 10, pp. 98–104, Oct. 2013.

- [8] Myung Chul Park, Won Il Jang, Kyoung Hak Lee, Yun Seong Eo "A Fully Integrated 0.18µm CMOS IR-UWB RF Transceiver for WBAN", IEIE summer conference, pp. 368-371, 2015.

#### - 저 자 소 개 -

이 중 무(학생회원) 2014년 2월 광운대학교 전자공학과 (공학사) 2014년 3월~현재 광운대학교 전자공학과 (석사과정)

<주관심분야: 무선 통신 및 레이다 시스템을 위한 CMOS RF/ Analog 집적회로 설계, Data Converter>

박 명 철(학생회원)

2011년 2월 광운대학교

전자공학과 (공학사)

2011년 3월 ~ 현재 광운대학교

전자공학과

(석박통합과정)

<주관심분야: 무선 통신 및 레이다 시스템을 위한 CMOS RF/ Analog 집적회로 설계>

어 윤 성(정회원)-교신저자

1993년 2월 한국과학기술원 전기 및 전자공학 (공학사)

1995년 2월 한국과학기술원 전기 및 전자공학 (공학석사)

2001년 2월 한국과학기술원 전기 및 전자공학 (공학박사)

2000년 8월~2002년 8월 LG 전자기술원 RF team 선임연구원

2002년 9월~2005월 8월 삼성종합기술원 Chip Solution Center 책임 연구원

2004년 3월~2004년 4월 그리스 Athena Semi사 파견 공동연구

2005년 9월~현재 광운대학교 전자공학과 부교수 <주관심분야: 초고주파 CMOS 송수신기 설계, 초고주파 CMOS 시스템 설계, CMOS 전력증폭 기 설계, UWB 송수신기 설계, 화합물 반도체>