# 역전류 주입방식기반의 DC차단기의 개선된 토폴로지

# An Improved Topology of DC Circuit Breaker Based on Inverse Current Injection Method

조 영 배\*·손 호 익\*·김 학 만<sup>†</sup>·곽 주 식\*\*·안 용 호\*\* (Young-Bae Cho·Ho-Ik Son·Hak-Man Kim·Joosik Kwak·Yong-Ho An)

**Abstract** - VSC-HVDC system is vulnerable to a DC fault because the fault current can be injected from AC system to DC system during the fault. Therefore, DC circuit breaker is required to isolate faults in VSC-HVDC system. The inverse current injection method of circuit breaker has been considered as DC circuit breaker. However, the topology has drawback that the breaking time is longer than hybrid circuit breaker using semiconductor devices. In order to solve this problem, this paper proposes an improved topology of circuit breaker based on inverse current injection method . In addition, the proposed topology will be compared with the existing topology. And we will verify its effects by using the simulation results.

Key Words: VSC-HVDC, Inverse Current Injection Method, Circuit Breaker, Breaking Time

### 1. 서 론

HVDC 시스템은 장거리 송전에 있어 AC 시스템에 비하여 많은 장점들을 가지고 있기 때문에 대규모 해상풍력 연계 및 수퍼그리드 구성에 많이 이용되고 있다. 특히, 전압형 HVDC 시스템은 고조파 필터의 감소, 독립적인 유·무효전력의 제어, 빠른 제어응답 등으로 인하여 그 적용성은 확대될 전망이다[1-6]. 그러나 전압형 HVDC 시스템의 경우 전력변환용 반도체소자로서 프리휠링 다이오드를 구비한 IGBT를 사용하기 때문에 DC선로사고 시 고장전류가 AC측에서 DC 측으로 전이되는 문제가 발생한다[7]. 따라서 전압형 HVDC 시스템을 이용한 전력망의 구성 시 전력 네트워크의 안정성향상을 위하여 사고보호에 대한 신뢰성을 향상시키는 것이요구된다. 그 중 가장 중요한 부분으로서 각 컨버터 스테이션마다 DC 차단기의 설치가 요구된다[8-10].

일반적으로 차단기의 경우 스위치의 개폐 시 돌입전류나 과전압 등을 억제하기 위해 전류가 zero-crossing point에서 차단을 실시한다. AC시스템의 경우 전류의 zero-crossing point가 주기적으로 발생하지만 DC시스템의 경우 전류의 zero-crossing point가 발생하지 않는다. 따라서 고장전류를 차단하기 위하여 인위적으로 DC전류의 zero-crossing point 점을 발생시키는 과정이 요구된다[11,12].

한편, 역전류 주입방식 DC차단기는 용량적인 측면이나

- \* Dept. of Electrical Engineering, Incheon National Univ., Korea

- \*\* Korea Electric Power Corporation Research Institute

- † Corresponding Author: Research Institute for Northeast Asian Super Grid, Incheon National Univ., Korea E-mail: hmkim@incheon.ac.kr

Received: July 04, 2014; Accepted: October 29, 2014

범용성을 고려하였을 때 전압형 HVDC 시스템에 적합한 차단 방식 중 하나이다[13,14]. 그러나 역전류 주입방식 DC차단기의 경우 고장전류 차단 시 차단시간이 길어진다는 단점이 있다. 이러한 차단시간은 역전류 주입방식 DC차단기를 구성하는 요소들의 파라미터 값에 따라서 달라질 수 있다. 그러나 이는 차단기 내부 구성요소들의 큰 정격을 요구하기때문에 다소 제한적이다.

따라서 본 논문에서는 기존의 역전류 주입방식 차단기 차단시간 단축 및 고장전류 감소시키기 위한 토폴로지를 제안하고자 한다. 제안하는 토폴로지는 Matlab/Simulink를 이용하여 모델링되었으며, 기존의 토폴로지에 대한 동작특성의차이를 설명한다. 또한, 모델링된 차단기를 전압형 HVDC시스템에 적용하고 DC선로 사고모의를 통하여 그 성능을 검증하고자 한다.

# 2. 역전류 주입방식 DC 차단기

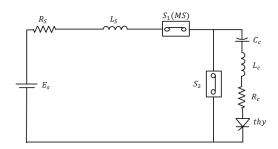

역전류 주입방식 차단기는 DC차단방식 중 하나로 차단기 내에 존재하는 커패시터와 인덕터간의 고주파 역전류를 발 생시키고, 이를 DC선로에 주입시켜 DC선로에 흐르는 전류 를 상쇄시킴으로써 DC전류의 영점을 발생시킨다. 역전류 주 입방식 차단기가 적용되는 DC회로는 그림 1과 같은 등가회 로로서 나타낼 수 있다.

그림 1에서 커패시터( $C_c$ ), 저항( $R_c$ ), 인덕터( $L_c$ )는 역전류주입에 필요한 보조회로에 직렬로 연결되며, DC선로 사고시 고장전류를 트립하기 위하여 보조회로에서 충분한 고주파 역전류를 주입할 수 있도록 미리  $C_c$ 는 충분한 전압으로충전된다. 그림 1에서  $R_s$ 와  $L_s$ 는 주 전송 회로의 시스템 및 선로의 저항과 인덕터를 의미하며,  $S_1$ 과  $S_2$ 는 차단기 내부

그림 1 역전류 주입 방식 차단기가 적용된 등가회로

including the Inverse current Fig. 1 Equivalent circuit injecting breaker

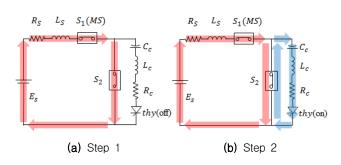

에 주 스위치, 보조 스위치를 각각 의미한다. DC선로 사고 시 역전류 주입방식 차단기의 기본적인 동작메커니즘은 각 step 별 시퀀스 제어에 따라 그림 2와 같이 구분될 수 있으 며, step 별 동작메커니즘의 상세한 설명은 다음과 같다[15].

- Step 1: DC선로 사고 발생 시 사고 지점과 DC 링크의 전위차 에 의해 DC전류는 급격하게 증가한다. 이때, 사전에 설정된 trip 전류 이상의 전류가 흐르면 trip 신호를 생 성한다.

- Step 2: 생성된 trip 신호는 사이리스터에 입력되고 사이리스터 는 turn-on되어 보조 회로에서 고주파 역전류가 주 전 송회로로 주입된다. 또한, 주입된 전류로 인하여  $S_2$ 에 흐르는 전류가 영점을 도달하게 되면  $S_2$ 는 개방된다.

- ullet Step 3: 모든 고장전류가 보조회로 측으로 흐름에 따라  $C_{\mu}$ 의 전압의 극성은 반전된다. 또한, 상승한 고장전류가 감 소하여 전류의 방향이 바뀌는 순간에 사이리스터는 역 방향 전압으로 인하여 turn-off된다.

그림 2 역전류 주입 방식 차단기의 동작 메커니즘

Fig. 2 Operating mechanism of inverse current injecting breaker

• Step 4: 주 전송회로의 전류가 0이 됨에 따라서 S,가 turn-off된다.

### 3. 역전류 주입방식 차단기의 개선된 토폴로지 제안

역전류 주입방식 차단기의 경우 DC선로 사고 시 고장전 류 차단시간이 길다는 단점이 있다. 이는 고장전류의 상승 을 야기하기 때문에 HVDC 시스템의 신뢰성 향상을 위하여 개선되어야 할 사항이다. 따라서 본 논문에서는 역전류 주 입방식 차단기의 차단시간 및 고장전류를 감소시키기 위하 여 기존의 역전류 주입방식 토폴로지에서 변형된 토폴로지 를 제안하고자 한다. 제안하는 토폴로지의 목적은 차단동안 에 소요되는 차단시간 단축과 최대 고장전류를 감소시키기 위함이다.

#### 3.1 제안하는 역전류 주입방식 차단기 원리

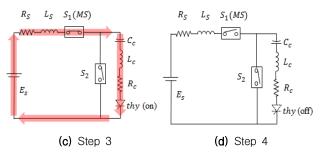

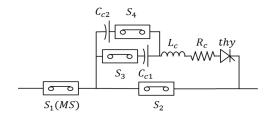

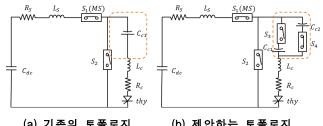

그림 3은 본 논문에서 제안하는 역전류 주입방식 차단기 의 구성을 나타낸 것이다. 제안하는 토폴로지의 경우 기존 커패시터 $(C_1)$ 와 병렬로 연결되는 커패시터 $(C_2)$ 가 추가됨에 따라 두 개의 스위치 $(S_3, S_4)$ 가 추가적으로 요구된다. 이때,  $C_{c2}$ 는  $C_{c1}$ 와 다르게 초기충전을 요구하지 않는다.

그림 3 제안된 토폴로지 구성

Fig. 3 Configuration of proposed topology

그림 4는 제안한 토폴로지를 적용하였을 시 2장에서 설명 된 차단 동작 중 step 3의 변화된 동작메카니즘을 나타낸 것이다. 제안하는 토폴로지는 기존 토폴로지에서의 차단 동 작 중 step 1부터 step 2까지는 동일하며, step 2에서  $S_9$ 의 turn-off 동작 이후  $S_3$ 와  $S_4$ 를 동시에 turn-off, turn-on 동작을 각각 수행함으로써  $C_{c1}$ 에서  $C_{c2}$ 로 고장전류를 전환시키는 방 식을 이용하였다. 이러한 동작은 차단 동작 중 발생하는 고 장전류의 크기 및 차단시간에 많은 영향을 미치게 된다.

(a) 기존의 토폴로지

(b) 제안하는 토폴로지

그림 4 Sep 3 동작메커니즘의 변화

Fig. 4 Proposed topology of equivalent model

식 (1)은 step 3에서 기존의 토폴로지에 의한 고장전류  $(i_{fault_1})$ 를 나타낸 것이며, 식 (2)는 step 3에서 제안된 토폴로지에 의한 고장전류 $(i_{fault_2})$ 를 나타낸 것이다. 시스템 저항 및 보조회로에서의 내부저항은 그 영향이 작기 때문에 고려하지 않았다.

$$i_{fault,1} = K_1 \alpha_1 Sin(\beta_1 t) + K_2 i_{3,initial}$$

(1)

여기서,  $i_{3,initial}$ : step 3에서의 초기 전류 (A)

$$\begin{split} K_1 &= V_{dc\_initial} + V_{dc1\_initial} \ , \ K_2 = L_s + L_c \qquad K_3 = \frac{C_{dc}C_{c1}}{C_{dc} + C_{c1}} \ , \\ \alpha_1 &= \sqrt{\frac{K_3}{K_2}} \ , \ \beta_1 = \sqrt{\frac{1}{K_2K_3}} \end{split}$$

$V_{de,initial}$  : step 3에서  $C_{de}$ 의 초기전압  $({

m V})$   $V_{cl,initial}$  : step 3에서  $C_{el}$ 의 초기 전압  $({

m V})$

$L_{s}$ ,  $L_{c}$  : 시스템 인덕턴스 (H)

$$\begin{split} i_{fault\_2} &= K_4 \alpha_2 \, Sin(\,\beta_2 t\,) + K_2 \, i_{3\_initial} \\ & \circlearrowleft \, 7] \, \, \& \ , \quad K_2 = L_s + L_c \ , \quad K_4 = V_{dc\_initial} \ , \quad K_5 = \frac{C_{dc} \, C_{c2}}{C_{dc} + C_{c2}} \\ & \alpha_2 = \sqrt{\frac{K_5}{K_2}} \ , \quad \beta_2 = \sqrt{\frac{1}{K_5 K_5}} \end{split}$$

#### 3.2 제안하는 역전류 주입방식 차단기의 특성

제안하는 토폴로지를 기존의 토폴로지와 비교하였을 때, 단축되는 차단시간과 최대 고장전류의 크기는 앞서 언급하였던 식 (1)과 식 (2)를 통하여 구할 수 있다. 제안된 토폴로지 내  $C_{c2}$ 의 영향만을 고려하기 위하여 그림 4의 등가회로 내 파라미터를 표 1과 같이 가정하였다.  $V_{de,initial}$ 와  $V_{c1,initial}$ 는 step 3에서  $C_{dc}$ 와  $C_{c1}$ 의 초기전압을 각각 나타낸 것이다.

표 1 등가회로 내 파라미터

Table 1 Parameters in equivalent circuit

| 파라미터                 | 값     | 파라미터                       | 값     |

|----------------------|-------|----------------------------|-------|

| $C_{dc}$ [ $\mu F$ ] | 1,000 | $V_{dc\_initial}$ [kV]     | 298.6 |

| $C_{c1}$ [ $\mu F$ ] | 300   | $V_{c1\_initial}$ [V]      | 1830  |

| $L_{c}$ [ $\mu H$ ]  | 20    | i <sub>3_initial</sub> [A] | 3100  |

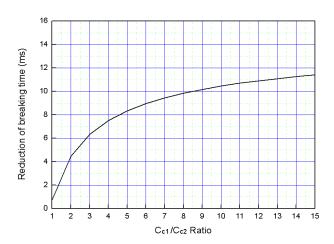

그림 5는 보조회로의 커패시터들에 대한 비 $(C_{cl}/C_{cl})$ 에 대하여 차단시간이 단축되는 정도를 나타낸 것이다. 보조회로의 커패시터들에 대한 비가 증가할수록 차단시간을 단축시킬 수 있다는 것을 알 수 있다. 즉, 제안하는 토폴로지에서 추가된 커패시터 $(C_{cl})$ 의 파라미터 값이 작아질수록 차단시간은 빨라진다. 이는 차단기 동작단계에서 step 3부터는 고장전류가  $C_{cl}$ 에서  $C_{cl}$ 측으로 고장전류가 전환됨에 따라 고로의 커패시터들에 대한 비가 증가할수록 차단시간을 단축

시킬 수 있다는 것을 알 수 있다. 즉, 제안하는 토폴로지에서 추가된 커패시터( $C_a$ )의 파라미터 값이 작아질수록 차단시간은 빨라진다. 이는 차단기 동작단계에서 step 3부터는 고장전류가  $C_a$ 에서  $C_a$ 측으로 고장전류가 전환됨에 따라 고장전류의 주파수가 커지기 때문이다. 다시 말해,  $C_a$ 는  $C_a$ 보다 작게 설계될 때, 고장전류의 주파수가 커지게 되고 영점에 도달하는 시간이 빨라지게 된다.

그림 5 R비와 차단시간 감소 관계 그래프

Fig. 5 Relation Graph of between R ratio and reduced breaking time

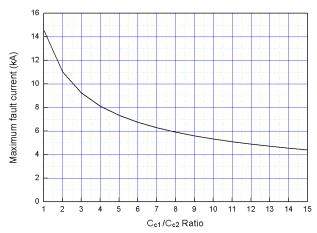

그림 6은 보조회로의 커패시터들에 대한 비 $(C_{cl}/C_{cl})$ 에 대하여 최대 고장전류를 나타낸 것이다.  $C_{cl}$ 의 파라미터 값이작아질수록 고장전류는 작아진다. 이는 차단기 동작단계에서 step 3부터는 고장전류가  $C_{cl}$ 에서  $C_{cl}$ 측으로 고장전류가전환됨에 따라 기존 커패시터의 충전전압에 의한 고장전류의 상승효과를 억제한다. 또한, 임피던스 증가시킴으로써 최대 고장전류를 감소시키는 효과를 가져 온다는 것을 알 수있다. 결과적으로,  $C_{cl}$ 의 파라미터의 값은  $C_{cl}$ 의 파라미터 보다 작게 설계될 때, 최대 고장전류는 감소하게 된다.

그림 6 R비와 최대 사고 전류 관계 그래프

Fig. 6 Relation Graph of between R ratio and maximum fault current

#### 4. 시뮬레이션 결과

#### 4.1 시뮬레이션 조건

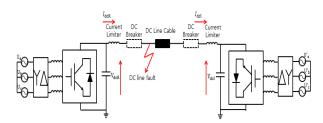

본 논문에서는 Matlab/Simulink를 이용하여 전압형 HVDC 시스템을 모델링하고, 동일 용량의 역전류 주입방식 DC차단기를 그림 7과 같이 적용하여 기존의 토폴로지 방식과 제안된 토폴로지 방식을 시뮬레이션하고 차단기 동작특성을 비교한다. 또한, 차단기 동작에 따른 전압형 HVDC 시스템의 특성을 확인한다. DC선로 사고는 고장전류의 스트레스가 가장 심한 경우를 고려하고자 정류기측과 가까운 지점에서의 사고를 가정하였다. 또한, DC사고가 발생한 직후 과전류로 인한 보호를 위하여 IGBT는 turn-off되는 것을 가정하였다. 표 2는 기존의 역전류 주입 방식과 제안한 방식에 동일하게 적용된 차단기의 파리미터 값, DC선로 사고 시간을 나타낸 것이며, 표 3은 보조회로의 커패시터들에 대한 비  $(R=C_{\rm cl}/C_{\rm cl})$ 에 따라 차단시간의 변화를 보기 위하여 시뮬레이션에 적용한 파라미터를 나타낸 것이다.

그림 7 VSC-HVDC와 DC 차단기 시스템 구성도

Fig. 7 Configuration of VSC-HVDC and DC circuit breaker

표 2 DC사고 발생 시간 및 공통 파라미터 Table 2 Fault time and common parameters

| 파라미터                            | 값     | 파라미터                      | 값   |

|---------------------------------|-------|---------------------------|-----|

| $C_{c1} \; \left[ \mu F  ight]$ | 300   | $C_{\!\!c1}$ 충전전압 $[kV]$  | 2   |

| $R_{s}$ [ $\Omega$ ]            | 1.39  | DC링크 전압[ <i>kV</i> ]      | 300 |

| $R_{\!e}\left[\Omega ight]$     | 0.002 | $I_{trip(Rectifire)}[kA]$ | 3   |

| $L_{s}$ [mH]                    | 100   | $I_{trip(Inverter)}[kA]$  | -1  |

| $L_{c} \; [\mu H]$              | 20    | Fault Time[sec]           | 3   |

표  $\mathbf{3} \ R = C_{c1}/C_{c2}$  변화에 따른  $C_{c_1}$ ,  $C_{c_2}$  파라미터

**Table 3** Ratio between  $C_{c_1}$  and  $C_{c_2}$

|                      | R=3.75 | R=5 | R=10 | R=15 |

|----------------------|--------|-----|------|------|

| $C_{c1}$ [ $\mu F$ ] | 300    | 300 | 300  | 300  |

| $C_{c2}$ [ $\mu F$ ] | 80     | 60  | 30   | 20   |

#### 4.2 시뮬레이션 결과

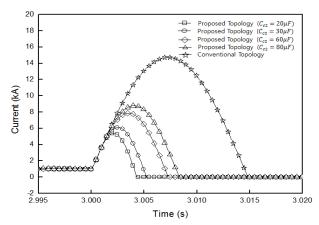

그림 8은 정류기측 DC선로 사고 시 기존 토폴로지 및 제 안하는 토폴로지 내 보조회로의 커패시터 용량 $(C_2)$ 에 따른 정류기 측 고장전류를 나타낸 것이다. 기존의 역전류 주입 차단방식의 경우 3s에 DC선로 사고가 발생 한 후 약 15kA의 최대 고장전류가 흐르고, 약 15ms 후에 고장전류가 0으로 되면서 차단되는 것을 확인할 수 있다. 반면에, 제안한 토폴로지의 차단기를 적용한 경우 사고이후  $C_2$ 가  $80\mu F$ 일 때 약 8.3kA의 최대 사고 전류가 흐르고 약 8.3ms의 후 차단되는 것을 확인할 수 있다. 또한,  $C_2$ 의 값이 각각  $60\mu F$ ,  $30\mu F$ ,  $20\mu F$ 일 경우에 전체 사고 전류 차단 시간은 약 7.3ms, 5.2ms, 4.4ms가 걸리고 최대 사고 전류 값은 각 8kA, 6.2kA, 5.5kA가 흐르는 것을 확인할 수 있다. 이는 2장에서 계산된 결과와 거의 유사함을 알 수 있으며, 제안한 토폴로지로부터 차단동안 고장전류의 주파수 및 고장전류를 감소시킬 수 있다는 것을 알 수 있다.

그림 8 DC선로 사고 시 정류기측 고장전류

Fig. 8 Fault current at rectifier side during DC fault

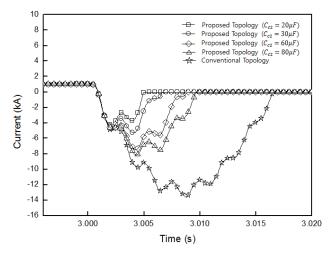

그림 9는 정류기측 DC선로 사고 시 기존 토폴로지 및 제 안하는 토폴로지 내 보조회로의 커패시터 용량 $(C_2)$ 에 따른 인버터 측 고장전류를 나타낸 것이다. 고장전류가 정상상태 전류의 방향에 대하여 반대방향으로 1kA의 전류가 흐르게되면 차단기의 트립신호는 동작하게 된다. 인버터측에서의 차단동작의 경우 상대적으로 고장위치가 정류기측에 비해 멀기 때문에 고장전류의 크기는 작아지고 차단시간은 길어지는 것을 확인할 수 있다. 또한, 정류기측 차단동작에서와 같이 보조회로의 커패시터가 작아질수록 고장전류 차단시간은 단축되고 최대 고장전류가 14kA에서 5kA까지 감소되는 것을 확인할 수 있다.

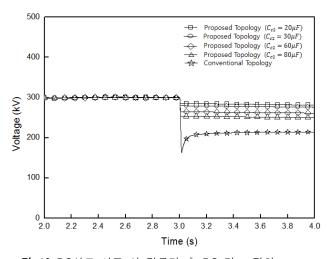

그림 10은 DC선로 사고 시 정류기측의 DC링크 전압을 나타낸 것이다. DC 링크전압은 정상상태에서 300kV로 제어되다가 3s에 DC선로 사고가 발생하는 동시에 고장점과 각스테이션과의 전위차가 커서 순간적으로 많은 전류가 DC링크 커패시터로부터 빠져나가면서 DC링크 전압은 떨어지게된다. 정류기 측에서는 기존의 역전류 주입방식의 경우 최대 약 160kV 까지 떨어지다가 사고가 차단되고 나면 200kV로 수렴하는 것을 볼 수 있다.

그림 9 DC선로 사고 시 인버터 측 차단전류

Fig. 9 Fault current at inverter side during DC fault

본 논문에서 제안한 토폴로지의 경우 차단시간이 기존의 토폴로지보다 짧기 때문에 감소된 DC링크 전압은  $C_2$ 이 20  $\sim 80\mu F$ 로 변함에 따라 약  $250 \sim 290 \mathrm{kV}$ 로 작아진 것을 확인할 수 있다. 사고판단 직후 컨버터 내부의 IGBT가 turn-off 동작하여 스테이션이 동작을 멈출 경우 얼마나 빠른 시간안에 DC링크를 고립시킬 수 있느냐에 따라 전압강하 비율이 정해지기 때문에 본 논문에서 제안한 토폴로지의 경우전압형 HVDC의 재가동시 전압 복구 면에서도 더 유리하다고 판단할 수 있다.

그림 10 DC선로 사고 시 정류기 측 DC 링크 전압 Fig. 10 DC link voltage at rectifier side during DC fault

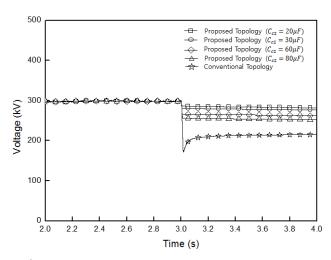

그림 11은 DC선로 사고 시 인버터측의 DC링크 전압을 나타내는 것이다. 앞서 말한 바와 같이 사고가 발생하고 차단기가 동작하는 동시에 사고판단 신호는 각 스테이션의 IGBT 소자에 들어가서 시스템을 정지시킨다. DC링크 전압은 정류기측 차단결과와 유사하게  $C_{c2}$ 가  $20\sim80\mu F$ 로 변함에따라 약  $250\sim290 \mathrm{kV}$ 로 작아진 것을 확인할 수 있다.

**그림 11** DC선로 사고 시 인버터 측 DC 링크 전압

Fig. 11 DC link voltage at inverter side during DC fault

#### 5. 결 론

본 논문에서는 기존의 역전류 주입방식 DC차단기의 차단시간 단축과 고장전류를 감소시키기 위한 토폴로지를 제안하였다. 제안된 토폴로지는 Matlab/Simulink를 이용하여 모델링되었으며, VSC-HVDC 시스템에 적용되었다. 또한, DC선로 사고 시 기존의 토폴로지에 대한 동작특성 차이를 시뮬레이션을 통하여 비교하였다. 결과적으로 제안된 토폴로지는 기존의 토폴로지에 비하여 차단동작 시 고장전류를 감소시키고, 차단시간을 단축시킬 수 있는 효과를 확인하였다. 이는 제안된 토폴로지에 추가된 회로의 동작은 차단기 내부임피던스 증가로 인한 고장전류 감소, 차단주파수 상승으로인한 차단시간의 단축에 기인한다는 것을 알 수 있다. 또한, 제안한 토폴로지 내  $C_2$ 값의 변화에 따른 비 $(R=C_1/C_2)$ 가증가할수록 그 효과가 증대된다는 것을 알 수 있다.

추후 연구에서는 본 연구에서 제안한 토폴로지를 기반으로 개폐제어에 관한 연구를 수행할 계획이다.

# 감사의 글

이 논문은 한국전력공사의 재원으로 기초전력연구원의 2013년 선정 기초연구개발과제의 지원을 받아 수행된 것임. [과제번호: R13TA14]

# References

- [1] N. Flourentzou, V. G. Agelidis, and G. D. Demetriades, "VSC-Based HVDC Power Transmission System: An Overview," IEEE Trans. Power Electronics, Vol 24, No. 3, pp. 592-602, 2009.

- [2] X. Yao, H. Sui, and Z. Xing, "The Study of VSC-HVDC Transmission System for Offshore Wind Power Farm," in Proc. International Conference on

- Electrical Machines and Systems (IECMS), pp. 314-319, 2007.

- [3] C. M. Franck, "HVDC Circuit Breaker: A Review Identifying Future Research Needs," IEEE Trans. Power Delivery, Vol. 26, No. 3, pp. 998–1007, 2001.

- [4] E.-A. Agusti, G.-B. Oriol, and J. Liang, "Operation and Control of VSC-HVDC Multiterminal Grids for Offshore Wind," in Proc. Power Electronis and Applications (EPE 2011), pp. 1-9, 2011.

- [5] F. Blaabjerg, R. Teodorescu, M. liserre, and A. Timbus, "Overview of Control and Grid Synchronization for Distributed Power Generation Systems," IEEE Trans. Industrial Electronics, Vol. 53, pp. 1398–1409, 2006.

- [6] M. Daryabak, S. Filizadeh, J. Jastskevich, and A. Davoudi, "Modeling of LCC-HVDC Systems Using Dynamic Phasors," IEEE Tans. Power Delivery, Vol. 29, No. 4, pp. 1989–1998, 2014.

- [7] J. Yang, J. Zheng, G. Tang, and Z. He, "Characteristics and Recovery Performance of VSC-HVDC DC Transmission Line Fault," in Proc. Power and Energy Engineering Conference (APPEEC 2010), pp. 1-4, 2010.

- [8] D. Gemmell, J. Dorn, D. Retzmann, and D. Soerangr, "Prospects of Multilevel VSC Technologies for Power Transmission," in Proc. IEEE/PES Trans. Distrib. Conf. Expo. pp. 1-16, 2008.

- [9] G. Asplund, K. Erksson, and K. Svensson, "DC Transmission Based on Voltage Source Converters," in Proc. CIGRE SC 14 Colloquium, 1997.

- [10] J. Candelaria and J. D. Park, "VSC-HVDC System protection: A Review of Current Methods," in Proc. IEEE PSCE, pp. 1-7, 2011.

- [11] J. Hafner and B. Jacobson, "Proactive Hybrid HVDC Breakers-A Key Innovation for Reliable HVDC Grids," in Proc. CIGRE Symposium, pp. 1-8, 2011.

- [12] C. Meyer and R. W. De Doncker, "Solid-state Circuit Breaker Based on Active Thyristor Topologies," IEEE Trans. Power Electron. Vol. 21, No. 2, pp. 450–458, 2006.

- [13] B. Y. Lee, J. K. Chung, K. Y. Park, and Y. J. Shin, "Interruption Techniques of Inverse Current Injection Type of HVDC Circuit Breaker," KIEE Summer Conference, pp. 92–94. 1997.

- [14] CIGRE Working Group B4.52, "HVDC Grid Feasibility Study," Appendix H, pp. 1-9, 2013.

- [15] Y.-B. Cho, H.-I. Son, H.-M. Kim, J. S. Kwak, and K. S. Han, "Operation Characteristic Analysis of Inverse Current Injecting Method DC Circuit Breaker in VSC based HVDC," KIEE Summer Conference, pp. 422–423, 2014.

# 저 자 소 개

# 조 영 배(Young-Bae Cho)

1987년 8월생. 2013년 인천대학교 공과대학 전기공학과 졸업. 2014년 현재 동 대학원 전기공학과 석사과정.

Tel: 032-835-4206

E-mail: gumbang2@inchoen.ac.kr

# 손 호 익(Ho-lk Son)

1987년 7월생, 2012년 인천대학교 공과대학 전기공학과 졸업. 2014년 현재 동 대학원 전기공학과 석·박사통합과정.

Tel: 032-835-4206

E-mail: shi0617@incheon.ac.kr

# 김 학 만(Hak-Man Kim)

1966년 2월생, 1998년 성균관대학교 공과 대학 전기공학과 졸업(공학박사), 2011년 일본 Tohoku(東北)대학교 정보과학연구 과 졸업(공학박사), 1996년 10월 ~ 2008 년 2월 한국전기연구원 전력연구단 선임 연구원. 현재 인천대학교 공과대학 전기

공학과 교수. 동북아 수퍼그리드 연구센터장.

Tel: 032-835-8769

E-mail: hmkim@incheon.ac.kr

# 곽 주 식(Joosik Kwak)

1972년 1월생, 1996년 충북대학교 공과대학 전기공학과 석사. 1996년~현재 한국 전력공사 전력연구원 송변전 연구소 선임 연구원.

Tel: 042-865-5881

E-mail: joosiki@kepco.co.kr

# 안 용 호(Young-Ho An)

1961년 8월생, 1984년 인천대 전기공학과 졸업. 2000년 전북대 전기공학과 졸업(석 사). 2013년 동 대학원 전기공학과 졸업 (박사), 1987년 한전 입사, 2014년 현재 한전 전력연구원 계통변전그룹장.

E-mail: anyeoh@kepco.co.kr