# Analytical Threshold Voltage Modeling of Surrounding Gate Silicon Nanowire Transistors with Different Geometries

## M. Karthigai Pandian<sup>†</sup> and N.B. Balamurugan\*

**Abstract** – In this paper, we propose new physically based threshold voltage models for short channel Surrounding Gate Silicon Nanowire Transistor with two different geometries. The model explores the impact of various device parameters like silicon film thickness, film height, film width, gate oxide thickness, and drain bias on the threshold voltage behavior of a cylindrical surrounding gate and rectangular surrounding gate nanowire MOSFET. Threshold voltage roll-off and DIBL characteristics of these devices are also studied. Proposed models are clearly validated by comparing the simulations with the TCAD simulation for a wide range of device geometries.

**Keywords**: Junction Based Cylindrical Surrounding Gate (JBCSG) silicon nanowire transistor, Rectangular surrounding gate silicon nanowire transistor, Threshold voltage, Parabolic approximation, silicon thickness, Channel Length, drain Bias.

#### 1. Introduction

The requirement for Nano electronic devices to have large computing power with less power consumption and smaller dimensions has lead to device miniaturization. There are a number of drawbacks in the downscaling process of a conventional MOSFET, such as the short channel effects and the gate-leakage-current. Hence in these conditions, Silicon Nanowire Transistors have garnered a huge attention in the modern semiconductor industry as the alternate option for the conventional MOSFETs due to their highly improved electrical and optical properties [1]. Devices based on silicon nanowires are bound to have high electrostatic control over the channel and reduced short channel effects.

Modeling of nanowire field effect transistors have been the subject of several investigation, both analytical and numerical. Analytical models are based on two assumptions, 1) an undoped semiconductor nanowire and 2) Boltzmann statistics [2-6]. These assumptions allow, in fact, for a closed form solution of Poisson's Eqs. [2, 3], that makes it possible to work out an intrinsic analytical relationship between the gate voltage and surface potential. Alternatively, the assumption is taken of a completely depleted nanowire, consistently with the investigation of Sub threshold Slope (SS) and short channel effects [7]. A new study on the gate capacitance of a surrounding gate nanowire transistor studies the acceptor type doping [8] such that the carriers are confined only within the inversion layer.

Numerical approaches, instead, account for nearly all of

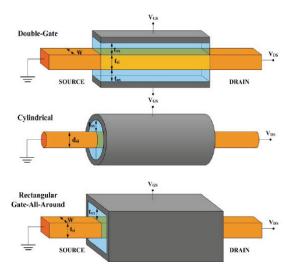

the relevant effects that exert an impact on the device behavior, including motion quantization, sub band splitting, Fermi statistics, quasi ballistic transport, surface and channel orientation, and band structure [9-11]. The classical single gate MOSFET is approaching its minimum channel length due to the limits imposed by gate oxide tunneling. For extending the scalability of CMOS technology several non classical MOSFETs have been proposed that are being the subject of intense research. Fig. 1 shows some of the non planar MOSFET devices with different geometries.

The use of several gates has shown good electrostatic control of the channel and, therefore, the possibility of higher reduction in channel length compared to traditional bulk MOSFETs. Structures such as FINFETs, Double Gate, Tri Gate, Surrounding Gate, Omega Gate and Gate-All-Around MOSFETs are preferred to planar structures as

Fig. 1. Non Planar MOSFETs with different geometric specifications

<sup>†</sup> Corresponding Author: Dept. of Electronics and Communication Engineering, Pandian Saraswathi Yadav Engineering College, Sivagangai, India. (karthickpandian@gmail.com)

<sup>\*</sup> Dept. of Electronics and Communication Engineering, Thiagarajar College of Engineering, Madurai, India. (nbbalamurugan@tce.edu,) Received: August 29, 2013; Accepted: July 17, 2014

they have a steep sub threshold voltage and reduced leakage currents for very short channel lengths [12]. Drain Induced Barrier Lowering (DIBL), threshold voltage roll-off, and off-state leakage current are greatly reduced in these devices [13, 14].

Surrounding Gate MOSFETs are one of the most promising structures beyond bulk CMOS. Since early investigations on Surrounding Gate / SOI devices [15], most recent experiments have demonstrated GAA Silicon Nanowires with controlled diameters on the order of 3-6 nm using conventional CMOS technology [16]. Theoretically, Surrounding Gate MOSFETs provide better gate electrostatic control capability than planar and double gate devices. We propose to develop a feasible physics based analytical model for the Surrounding Gate Nanowire MOSFET with two different geometries; a Junction Based Cylindrical Surrounding Gate Device and a Rectangular Surrounding Gate Device.

## 2. Modeling of Cylindrical SG Nanowire MOSFET

A number of analytical models for the Surrounding Gate devices have been proposed in the past by various research scholars. A simple threshold voltage model for a Surrounding Gate MOSFET transistor has been proposed by C.P. Auth and James D. Plummer in 1998 [17]. This model determines the channel potential using perimeter weighted summation method. Threshold voltage model for a Omega Gate Transistor was proposed by Biswajit Ray and Santanu Mahapathra in 2008 [18]. This model can be considered as the generalized model for the Surrounding Gate and Semi-Surrounding Gate Cylindrical Transistors. Te-Kuang Chiang proposed a model on surrounding gate MOSFET with localized interface charges with potential approximation using parabolic approximation in 2010 [19] and using an alternative approach of perimeter weighted summation method in 2011 [20]. M. Jagadesh Kumar et.al. have proposed a threshold voltage model for the dual material surrounding gate that includes the physical properties of both the materials used in the gate [21]. A new threshold voltage model for a short channel Junction Less Cylindrical Surrounding Gate MOSFET has been developed by T.K.Chiang in 2012 [22].

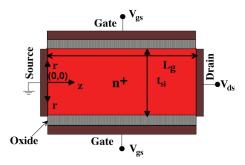

In the sub threshold operation of a Junction Based device, the channel region is fully depleted by the flat band voltage and the gate bias is used to induce the minority carriers at the semiconductor – insulator interface. Due to the 3-D channel potential,  $\varphi(r, z, \theta)$  is symmetrical in the  $\theta$  direction. Hence the 2-D Poisson equation for a Junction Based Cylindrical Surrounding Gate Transistor with a uniform impurity distribution is given by [22].

$$\frac{1}{r}\frac{\partial}{\partial r}\left(r\frac{\partial}{\partial r}\varphi(r,z)\right) + \frac{\partial^2}{\partial z^2}\varphi(r,z) = \frac{qN_A}{\varepsilon_{si}}$$

(1)

**Fig. 2**. Junction Based Cylindrical Surrounding Gate (JBCSG) MOSFET.

where  $\varphi(r,z)$  is the 2-D channel potential and  $N_A$  is the channel doping density.

Using the parabolic potential approximation method, the 2-D potential vertical to the channel is given by [22],

$$\varphi(r,z) = C_1(z) + C_2(z)r + C_3(z)r^2 \tag{2}$$

Certain assumptions are done to determine the channel potential [22]. They are as given below:

- 1) The electrical flux between the silicon film and surrounding gate oxide must be continuous.

- 2) The electrical field at r = 0 must be zero due to the symmetry of the channel potential along the r-direction.

Now the channel potential can be obtained as

$$\varphi(r,z) = \varphi_c(z) + \frac{C_{ox}(V_{gs} - V_{fb} - \varphi_s(z))}{\varepsilon_{si}t_{si}}r^2$$

(3)

Where  $V_{fb}$  is the flat band voltage,  $C_{ox}$  is the gate oxide capacitance per unit area, and  $t_{si}$  is the silicon film thickness.  $\varphi_s(z)$  and  $\varphi_c(z)$  are the surface and centre potential respectively that should satisfy the following Eq. [22].

$$\varphi_{s}(z) = \varphi_{c}(z) + \frac{C_{ox}t_{si}\left(V_{gs} - V_{fb} - \varphi_{s}(z)\right)}{4\varepsilon_{ci}}$$

(4)

In case of a Junction Based Transistor, we are concerned about the surface potential and the centre potential has to be eliminated.

Hence by substituting Eqs. (3) and (4) in Eq. (1) we get,

$$\frac{d^2\varphi_s(z)}{dz^2} - \frac{1}{\lambda^2} (\varphi_s(z) - \varphi_s) = 0$$

(5)

$\varphi_s$  is the surface potential and  $\lambda$  is the scaling length. Their values are given by,

$$\frac{1}{\lambda^2} = \frac{4C_{ox}}{\varepsilon_{ci}t_{ci}} \tag{6}$$

$$\varphi_s = V_{gs} - V_{fb} - \frac{qN_A t_{si}}{4C_{ox}} \tag{7}$$

where  $t_{ox}$  is the oxide film thickness. The general solution of the differential equation in (5) is given by,

$$\varphi_s(z) = ae^{z/\lambda} + be^{-z/\lambda} + \varphi_s \tag{8}$$

The coefficients of a and b can be determined by applying the boundary conditions as  $\varphi_s(z=0)=0$  and  $\varphi_s(z=L_{\it eff})=V_{\it ds}$ . By applying the above conditions we get,

$$a + b + \varphi_s = 0 \tag{9}$$

$$a.e^{L_{eff}/\lambda} + b.e^{L_{eff}/\lambda} + \varphi_s = V_{ds}$$

(10)

By solving and rearranging, the values of a and b are obtained as,

$$a = \frac{V_{ds} - \varphi_s (1 - e^{-L_{eff}/\lambda})}{2 \sinh(\frac{L_{eff}/\lambda}{\lambda})}$$

(11)

$$b = \frac{-V_{ds} + \varphi_s(1 - e^{\frac{L_{eff}}{\lambda}})}{2\sinh(\frac{L_{eff}}{\lambda})}$$

(12)

The surface potential is given by,

$$\varphi_s(z) = \alpha V_{gs} + \beta \tag{13}$$

$$\varphi_{s}(z) = \gamma V_{\varrho s} + \kappa \tag{14}$$

Where,

$$\alpha V_{gs} + \beta = a \tag{15}$$

$$\gamma V_{gs} + \kappa = b \tag{16}$$

And here the effective length is given by,

$$L_{eff} = L_g - L_s - L_d - 2L_D \tag{17}$$

$L_g$  is the gate length while  $L_s$  and  $L_d$  are source and drain depletion widths respectively. Now  $L_d$ , the Debye length, by accounting for the transition regions separating the drift and diffusion regions of the channel, is given by [23].

$$L_D = \sqrt{\frac{2\varepsilon_{si}KT}{q^2N_A}} \tag{18}$$

where T is the absolute temperature and K is the Boltzmann constant. The Minimum Surface Potential in (8)

is now derived from the previous equations as,

$$\varphi_{s,\min}(z) = 2\sqrt{ab} + \varphi_s = 2\varphi_B \tag{19}$$

The bulk potential  $\varphi_B$  is now given by

$$\varphi_B = \frac{KT}{q} \ln(\frac{N_A}{n_i}) \tag{20}$$

$n_i$  is the intrinsic carrier concentration of silicon.

Setting the Minimum Surface Potential (MSP) to be two times the bulk potential and solving for the gate voltage  $V_{gs}$ , the threshold voltage for the Junction Based transistor is obtained.

$$V_{th,JB} = \frac{B_{JB} + \sqrt{B_{JB}^2 - A_{JB}C_{JB}}}{A_{JB}}$$

(21)

The values of  $A_{JB}$ ,  $B_{JB}$  and  $C_{JB}$  and the associated fitting parameters are listed here.

$$A_{JB} = 1 - 4\alpha\gamma \tag{22}$$

$$B_{JB} = 2(\beta \gamma + \alpha \kappa) + (\omega + 2\varphi_B) \tag{23}$$

$$C_{JB} = (\omega + 2\varphi_B)^2 - 4\beta\kappa \tag{24}$$

$$\omega_{JB} = V_{fb} + \frac{qN_A t_{si}}{4C_{ox}} \tag{25}$$

$$\alpha = \frac{\left(e^{-L_{eff}/\lambda} - 1\right)}{2\sinh\left(\frac{L_{eff}/\lambda}{\lambda}\right)}$$

(26)

$$\beta = \frac{V_{ds} - \omega \left( e^{-L_{eff}} / \lambda - 1 \right)}{2 \sinh \left( \frac{L_{eff}}{\lambda} \right)}$$

(27)

$$\gamma = \frac{1 - e^{L_{eff}/\lambda}}{2\sinh\left(\frac{L_{eff}/\lambda}{\lambda}\right)} \tag{28}$$

$$\kappa = \frac{-V_{ds} + \omega(e^{L_{eff}/\lambda} - 1)}{2\sinh\left(\frac{L_{eff}/\lambda}{\lambda}\right)}$$

(29)

## 3. Modeling of Rectangular SG Nanowire MOSFET

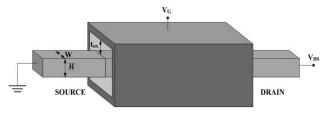

An analytical threshold voltage model for GAA Nanoscale MOSFETs considering the hot carrier induced interface charges have been proposed by Z.Ghoggali et al., in 2008 [24]. Quantum confinement and its effects on threshold voltage variations in short channel GAA devices have been studied by Y.S.Wu and Pin Su in 2009 [25]. A

**Fig. 3.** Schematic Diagram of a Rectangular Surrounding Gate Nanowire MOSFET

physically based classical model for body potential of a GAA nanowire transistor has been proposed by Biswajit Ray and Santanu Mahapathra in 2008 [26]. A quasi and analytical model for predicting the potential of a nanowire FET has been proposed by De Michielis in 2010 [27]. Here, we consider a lightly doped rectangular surrounding gate nanowire MOSFET, bound to have high gate control, in the weak inversion region, where both fixed and mobile charge densities in the channel are negligible. In modeling the threshold voltage, the quantum effects are also considered, as the quantization of the electron energy in ultra thin devices can never be ignored. One important consequence of the quantum mechanical carrier distribution, in accordance with the device behavior, occurs when the device geometries and silicon thickness are varied, so a reliable compact model for the nanowire transistors must also take into account the quantum effects resulting out of these variations.

The proposed physically based closed form model holds good for ultra thin and ultra short channel surrounding gate devices and does not employ any unphysical fitting parameter. The compact threshold voltage model is obtained by solving the 3D Poisson equation and 2D Schrodinger equations in the inversion region. These equations are then consistently solved to obtain the potential distribution and inversion charge density.

In the weak inversion regime, we have approximated the Poisson equation as Laplace equation with the inversion charge density neglected, and thus the two equations are decoupled. Assuming a flat potential on the plane perpendicular to the source-drain direction in the nanowire, neglecting the charge densities ensure that no self consistency problems arise in the nanowire. The mid gap metals are used for gate, intended to suppress the silicon gate poly depletion induced parasitic capacitances. The 3-D Poisson equation is solved to obtain the threshold voltage in the weak inversion region, including the parabolic band approximation. Hence the potential distribution in the insulator and silicon regions can be expressed as [28].

$$\frac{\delta^2 \psi(x, y, z)}{\delta x^2} + \frac{\delta^2 \psi(x, y, z)}{\delta y^2} + \frac{\delta^2 \psi(x, y, z)}{\delta z^2} = 0$$

(30)

The potential  $\Psi$  in terms of x (width), y (height) and z (length) is to be determined. The boundary conditions

defined by the physics of the device [9] are given by,

$$\psi(x, -H/2 - T_{OX}, z) = V_g$$

(31)

$$\psi(-W/2 - T_{OX}, y, z) = Vg$$

(32)

$$\frac{\delta \psi}{\delta x}\big|_{x=0} = 0 \tag{33}$$

$$\frac{\delta \psi}{\delta v}\big|_{y=0} = 0 \tag{34}$$

$$\psi(x, y, 0) = \psi_{bi} \tag{35}$$

$$\psi(x, y, L) = \psi_{bi} + V_{ds} \tag{36}$$

Where,  $V_g$  is the gate voltage,  $\psi_{bi}$  is the built in potential, L is the channel length,  $V_{ds}$  is the drain to source voltage which is negligible for low  $V_{ds}$ . For a rectangular surrounding gate device, we have to find the insulator potential on all sides of the channel under consideration. So the height and width of the channel is also taken into account. The insulator potential is now expressed as,

$$\psi(x, y, z) = \frac{V_g - \psi_{bi} - \Phi_{ms}}{T_{OX}} (x - \frac{W}{2}) + \psi_{bi}$$

for  $\frac{W}{2} < x < \frac{W}{2} + T_{OX}$  and  $0 < y < \frac{H}{2}$  (37)

$$\psi(x, y, z) = \frac{V_g - \psi_{bi} - \Phi_{ms}}{T_{OX}} \left( y - \frac{H}{2} \right) + \psi_{bi}$$

$$0 < x < \frac{W}{2} \text{ and } \frac{H}{2} < y < \frac{H}{2} + T_{OX}$$

(38)

Here  $\Phi_{ms}$  is the work function difference. By applying the superposition principle, the electrostatic potential can be now written as

$$\psi(x, y, z) = U_L(x, y, z) + U_R(x, y, z) + V_g(x, y)$$

(39)

Here  $V_g(x,y)$  is the 1-D solution of the Poisson equation that satisfies the gate boundary conditions.  $U_L$  satisfies the source boundary condition but it is bound to have a null value on the gate and drain boundaries. Similarly  $U_R$  satisfies the drain boundary condition and it is bound to have a null value on the gate and source boundaries. On further evaluation, the term  $V_g + U_L$  is found to satisfy the potential equation when  $U_R$  is on null value and in an exact repetition the term  $V_g + U_R$  satisfies the potential equation when  $U_L$  is on null value. From Eq. (30),

$$\psi_{xx} + \psi_{yy} + \psi_{zz} = 0 \tag{40}$$

By solving the above equation using LDE method we obtain the value of  $\Psi$ . The Potential equation is deduced after rigorous analytical calculations as,

for

$$\psi(x, y, z) = V_g + (V_g - \psi_{bi}) \sum_{n} \sum_{m} \rho_{nm} \sinh(\sum_{nm} (L - z)) + (V_g - \psi_{bi} - V_{ds}) \sum_{n} \sum_{m} \sinh(\sum_{nm} z)$$

(41)

Where,

$$\rho_{nm}(x,y) = -\omega_{nm}\gamma_{nm} \frac{\cos(\Lambda_n x)\cos(M_{my})}{\sinh(\sum_{nm} L)}$$

(42)

Threshold voltage for the undoped body devices is defined as the gate voltage when the integrated charge at the virtual source becomes equal to the critical charge  $(Q_T)$ . The first series term in Eq. (41) is enough to find the potential at the virtual source; it is only taken into account for the further calculations. Once the potential distribution at every point of the cross section of the channel is known we calculate the inversion charge density by using surface integral over the surface area of the channel. Hence the inversion charge can be expressed as,

$$Q = \int_{-H/2}^{H/2} \int_{-W/2}^{W/2} q n_i e^{(\psi/U_T)} dx dy$$

(43)

Where, q is the elementary charge,  $U_T$  is thermal voltage, and  $n_i$  is the intrinsic carrier concentration. The charge equation can now be approximated as,

$$Q \approx WHqn_{i,e}(\frac{\psi((3W/_{14}),(3H/_{14}),z_{c}}{U_{T}})$$

(44)

Here,  $Z_c$  is the virtual source position, which is half of the channel length for low  $V_{ds}$ . Using the inversion charge we can obtain the classical threshold model as,

$$V_{TC} = \frac{U_T \ln \frac{Q}{WHqn_i} + 2V_{bi}\rho_{11}(\frac{3W}{14}, \frac{3H}{14})\sinh(\frac{\sum_{11}L}{2})}{1 + 2\rho_{11}(\frac{3W}{14}, \frac{3H}{14})\sinh(\frac{\sum_{11}L}{2})}$$

(45)

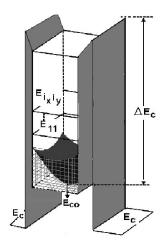

As MOSFET devices are further scaled into the deep nanometer regime, it has become necessary to include quantum mechanical effects while modeling their device behavior. The potential distribution obtained in (41) is quasi-parabolic in nature. Therefore in this paper, we approximate the actual potential as well as the square well potential since it is difficult to solve the Schrodinger equation to obtain the potential.

In the square potential well approximation, the minima of conduction band energy at the centre position is given by,

$$E_{co} = \frac{E_g}{2} - q\psi(0, 0, z_c) \tag{46}$$

**Fig. 4.** Band diagram perpendicular to the gate - square well potential of a Rectangular Gate Silicon Nanowire MOSFET

Using the above value of potential energy in (46), the Schrodinger equation becomes,

$$\frac{\hbar^2}{2m_x}\frac{\partial^2 \zeta}{\partial x^2} + \frac{\hbar^2}{2m_y}\frac{\partial^2 \zeta}{\partial y^2} + (E - E_{co})\zeta = 0 \tag{47}$$

Here  $\hbar = \frac{h}{2\pi}$  and h is the planks constant,  $\zeta$  is the wave function and E is the energy of the electron wave. The solution for this equation is obtained by variable separation method as,

$$E_{i_x i_y} = E_{co} + \frac{\hbar^2 \pi^2}{2} \left[ \frac{1}{m_x} (\frac{i_x}{I_x})^2 + \frac{1}{m_y} (\frac{i_y}{I_y})^2 \right]$$

(48)

The transverse and longitudinal masses and lengths in x and y directions tae different values based on the direction of quantization. The energy reaches its minimum when the masses reach the maximum value (48). In silicon, six energy valleys are found to be present in its band structure (two lower energy valleys, two middle energy valleys, and two higher energy valleys). If the thin film of device has equal height and width, the two lower energy valleys and two middle energy valleys combine together to produce four lower energy valleys and the other two higher energy valleys remain in their own state. Thus the charge per unit length per valley of silicon is expressed as,

$$Q = \sum_{i_x} \sum_{i_y} q \int_{E_{i_x i_y}}^{\infty} N1Df(E)dE$$

(49)

Where,  $N_{1D}$  is the 1D density-of-states and f (E) is the Fermi-Dirac distribution function. E is the energy of the electron wave. The terms  $i_x$  and  $i_y$  are positive natural numbers.

Now, the charge is given by,

Analytical Threshold Voltage Modeling of Surrounding Gate Silicon Nanowire Transistors with Different Geometries

$$Q = q \sum_{i_x} \sum_{i_y} \sqrt{\left(\frac{m_z}{2\pi\hbar^2}\right)} \int_{E_{i,j,z}}^{\infty} \frac{(E - E_{i_x i_y})^{\frac{-1}{2}}}{1 + e((E - E_F)/kT)} dE \qquad (50)$$

Where,  $m_z$  is the mass of the valley which is perpendicular to the direction of quantization. The Fermi energy level is much lower than the conduction band energy in weak inversion region. Hence the charge equation can be approximated using Boltzmann equation as,

$$Q = q \sqrt{\left(\frac{m_z}{2\pi\hbar^2}\right)} \sum_{i_x} \sum_{i_y} \int_{E_{i_x i_y}}^{\infty} \frac{e^{((E_F - E)/kT)}}{(E - E_{i_x i_y})^{1/2}} dE$$

(51)

Using (48) and (51), the total integrated charge at the virtual source can be obtained as,

$$Q = q \sqrt{\left(\frac{2kTm_{t}}{\hbar^{2}}\right)} \sum_{i_{x}} \sum_{i_{y}} \exp\left(-\frac{E_{co} + E_{1}(i_{x}, i_{y})}{kT}\right) + q \sqrt{\left(\frac{2kTm_{t}}{\hbar^{2}}\right)} \sum_{i_{x}} \sum_{i_{y}} \exp\left(-\frac{E_{co} + E_{2}(i_{x}, i_{y})}{kT}\right) + q \sqrt{\left(\frac{2kTm_{t}}{\hbar^{2}}\right)} \sum_{i_{x}} \sum_{i_{y}} \exp\left(-\frac{E_{co} + E_{3}(i_{x}, i_{y})}{kT}\right)$$

(52)

Where,

$$E_{1}(i_{x}, i_{y}) = \frac{\hbar^{2}\pi^{2}}{2} \left[ \frac{1}{m_{1}} \left( \frac{i_{x}}{W} \right)^{2} + \frac{1}{m_{t}} \left( \frac{i_{y}}{H} \right)^{2} \right]$$

$$E_{2}(i_{x}, i_{y}) = \frac{\hbar^{2}\pi^{2}}{2} \left[ \frac{1}{m_{t}} \left( \frac{i_{x}}{W} \right)^{2} + \frac{1}{m_{1}} \left( \frac{i_{y}}{H} \right)^{2} \right]$$

$$E_{3}(i_{x}, i_{y}) = \frac{\hbar^{2}\pi^{2}}{2} \left[ \frac{1}{m_{t}} \left( \frac{i_{x}}{W} \right)^{2} + \frac{1}{m_{t}} \left( \frac{i_{y}}{H} \right)^{2} \right]$$

(53)

Here the  $m_t$  and  $m_1$  are the transverse and longitudinal effective masses of the energy valleys of silicon. The lengths  $i_x$  and  $i_y$  carry distinct values contingent on the direction of quantization. Finally, the quantum threshold voltage model becomes,

$$V_{TQ} = \frac{\frac{E_g}{2q} + (\frac{kT}{q})In(\frac{Q_T}{\tau}) + 2\psi_{bi}\rho_{11}(0,0)\sinh(\frac{\sum_{11}L}{2})}{1 + 2\rho_{11}(0,0)\sinh(\frac{\sum_{11}L}{2})}$$

(54)

Where,

$$\tau = q \sqrt{(\frac{2kTm_t}{\hbar^2})} \exp(-\frac{E_1(1,1)}{kT}) + q \sqrt{(\frac{2kTm_t}{\hbar^2})} \exp(-\frac{E_2(1,1)}{kT})$$

$$+q\sqrt{(\frac{2kTm_{t}}{\hbar^{2}})\exp(-\frac{E_{3}(1,1)}{kT})}$$

(55)

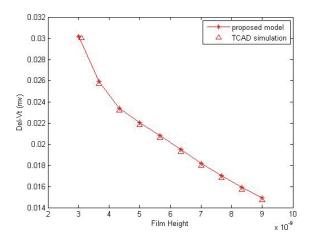

The impacts on the threshold voltage due to quantum effects is acquired by using the following equation,

$$V_{TC} = V_{TQ} + \Delta V_T \tag{56}$$

Here,  $\Delta V_T$  is the difference between the quantum threshold voltage and the classical threshold voltage.

### 4. Results and Discussions

The Junction Based Cylindrical Surrounding Gate Transistor is simulated with the following specifications for the device:  $V_{ds}$ = 0.1 V,  $N_A$ =1x10<sup>17</sup>cm<sup>-3</sup> and  $N_D$ =1x10<sup>19</sup> cm<sup>-3</sup> are the drain voltage, doped p-type silicon film and the high n-type doping densities, respectively. The model simulations are validated by comparing the MATLAB simulation results with the results of the TCAD simulations.

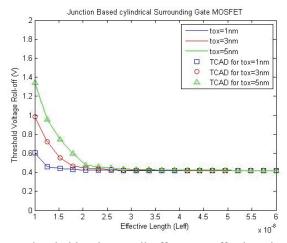

Fig. 5 shows the relation between the threshold voltage roll-off and effective channel length for varying oxide thicknesses of a cylindrical surrounding gate device. Three different oxide thicknesses of 1, 3 and 5 nm are used. The thinnest gate oxide thickness of 1 nm shows the minimum threshold voltage degradation. As the gate oxide thickness increases, the threshold voltage roll-off also increases leading to the subdued performance of the device. The threshold voltage tends to remain constant in a range of 0.4V with the effective channel length of 35nm.

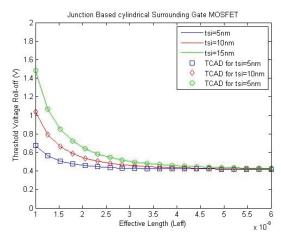

Fig. 6. shows the variation of the threshold voltage rolloff versus effective channel length for different silicon film thicknesses of a cylindrical surrounding gate device. Decreasing the effective channel length shows that the threshold voltage roll-off of the device is highly increased.

Fig.5. Threshold voltage roll-off versus effective channel length for a Junction Based Cylindrical Surrounding Gate Nanowire Transistor with different oxide thicknesses

**Fig. 6**. Threshold voltage roll-off versus effective channel length for a Junction Based Cylindrical Surrounding Gate Nanowire Transistor with different silicon thicknesses

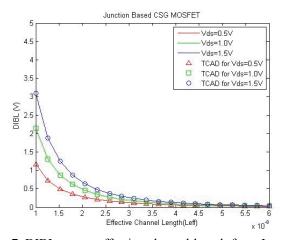

**Fig. 7.** DIBL versus effective channel length for a Junction Based Cylindrical Surrounding Gate Transistor

Three different silicon thicknesses of  $t_{\rm si} = 5$ , 10, and 15 nm are used in the simulations. Reducing thickness of the silicon film leads to the reduction of threshold voltage. As the thickness is less than 10 nm, the device tends to show abnormal variations in terms of threshold voltage. The simulations are further compared with TCAD simulations and are found to be in excellent coordination.

Any transistor whose channel length is reduced to a nanometer range, there enters the problem of short channel effects (SCE). DIBL (Drain Induced Barrier Lowering) is one among these SCE that affects the performance of the transistor. Fig. 7. shows the impact of the effective channel length on DIBL for different drain biases of a cylindrical surrounding gate device.

In Fig. 7, the minimum  $V_{ds}$  is kept as 0.1V and as they are gradually increased to higher values of 0.5, 1.0 and 1.5 V, the DIBL is plotted as the difference between the lower and higher bias values. It shows that an increasing drain bias and decreasing effective channel length will lead to the device suffering high Short Channel Effects.

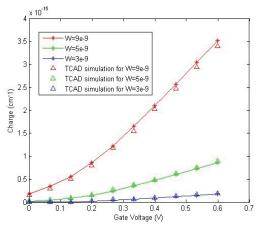

**Fig. 8**. Variation of quantum integrated charge at virtual source with gate voltage for a Rectangular Surrounding Gate Nanowire Transistor with different film widths

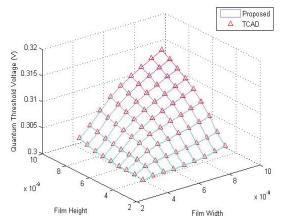

**Fig. 9.** Variation of quantum threshold voltage with film height and width for a Rectangular Surrounding Gate Nanowire Transistor (L=20nm)

Fig. 8. represents the variation of total quantum integrated charge of a rectangular surrounding gate device with the gate voltage at 0.3V for different film widths. Eq. (45) is used to obtain the integrated charge with only one energy level and one series term. It clearly shows that the decrease in the film thickness leads to the increase in the quantum threshold voltage which is actually due to the increase in energy quantization of the transistor.

Fig. 9 shows the variation of quantum threshold voltage with width and height of the film for a rectangular surrounding gate device at a channel length of 20 nm. The impact of the device dimensions like film height and width on the quantum threshold voltage of the device is explained. The short channel effects tend to decrease along with the energy quantization and this can be further explained as a result of increase in the effective band gap of silicon due to quantum effects. The effect of confinement, expressed as the difference in the threshold voltage and its variation with the channel length L, of a Rectangular surrounding gate device is illustrated in Fig. 10. The most important

thing about this gate all around nanowire transistor is that any change in one of the dimensions can be nullified by proper tuning of other dimensions as the transistor is symmetric about its height and width.

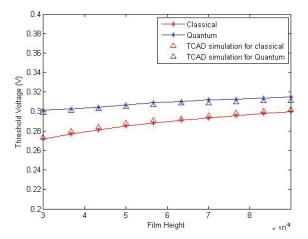

Fig. 11 shows the variation of the classical threshold voltage and quantum threshold voltage with the film height of a Rectangular surrounding gate device at a constant width of 9 nm. The value of the classical threshold voltage ranges from 0.27 V to 0.29 V for the corresponding changes in the film height. Similarly the quantum threshold voltage ranges from 0.3 V to 0.31 V. It shows that the device has a highly improved control over the threshold voltage. The process parameters are almost same for the cylindrical gate and surrounding gate devices except for the fact that radius is the main factor in the cylindrical gate device while width plays a very important role in the rectangular gate device.

As the thickness of the silicon film increases and the effective channel length decreases, threshold voltage roll-

Fig. 10. Variation of threshold voltage with film height for a Rectangular Surrounding Gate Nanowire Transistor (L= 20nm and W=9nm)

**Fig. 11.** Variation of quantum and classical threshold voltage with film height for a Rectangular Surrounding Gate Nanowire Transistor. Here L=20nm and W=9nm.

off increases in a cylindrical gate device. Similarly as the film width increases, the threshold voltage decreases in a rectangular gate device. This will lead to simultaneous increase in the off current, resulting in the performance degradation of device. In the cylindrical gate device, increase in gate oxide thickness and reduction in effective channel length leads to higher threshold voltage roll-off. In a rectangular gate device, as the film height increases and the channel length decreases, threshold voltage also decreases but the short channel effects are reduced due to energy quantization. The increase in drain bias and reducing channel length is bound to increase the short channel effects in both geometries. The major difference between the two geometries is that the rectangular gate device is bound to get affected by corner effects much more in comparison with the cylindrical gate device.

#### 5. Conclusion

A new physically based threshold voltage models for a Junction Based Cylindrical Surrounding Gate Nanowire Transistor and Rectangular Gate Surrounding Gate Nanowire Transistor have been developed. The simulations are validated by using the TCAD results. This physics based models can be extended to study the I-V characteristics of the devices affording to their simplicity and computational efficiency.

## References

- [1] Yuting Wan, Jian Sha, Bo Chen, Yanjun Wang, Zongli Wang and Yewu Wang, "Nanodevices based on Silicon Nanowires", *Recent Patents on Nanotechnology*, Vol. 3, Issue. 1, pp. 1-9, January 2009.

- [2] D.Jimenez, J.J. Saenz, B. Iniguez, J.Sune, L.F. Marsal and J. Pallares, "Modeling of Nanoscale GAA MOSFETs", *IEEE Electron Device Lett.*, Vol. 25, Issue. 5, pp. 314-316, May 2004.

- [3] D. Jimenez, B. Iniguez, J. Sune, L.F. Marsal and J. Pallares, "Continuous Analytic I-V model for Surrounding Gate MOSFETs", *IEEE Electron Device Lett.*, Vol.25, Issue.8, pp.571-573, August 2004.

- [4] B. Iniguez, D. Jimenez, J.Roig, H. A. Hamid, L. F. Marsal and J. Pallares, "Explicit Continuous model for Long Channel undoped Surrounding Gate MOSFETs", *IEEE Transactions on Electron Devices*, Vol. 52, Issue. 8, pp. 1868-1873, August 2005.

- [5] B. Yu, W.Y. Lu, H. Lu and Y. Taur, "Analytic Charge Model for Surrounding Gate MOSFETs", *IEEE Transactions on Electron Devices*, Vol. 54, Issue. 3, pp. 492-496, March 2007.

- [6] H. Borli, S. Kolberg, T.A. Fjeldly, and B. Iniguez, "Precise Modeling Framework for short channel Double-Gate and GAA MOSFETs", IEEE Trans-

- actions on Electron Devices, Vol.55, Issue.10, pp. 2678-2686, October 2008.

- [7] C. P. Auth and James D. Plummer, "Scaling theory for Cylindrical, Fully depleted, Surrounding Gate MOSFETs", *IEEE Electron Device Lett.*, Vol. 18, Issue. 2, pp. 74-76, February 1997.

- [8] FJG Ruiz, IM Tienda-Luna, A.Godoy, L. Donetti and F. Gamiz, "A Model of the Gate Capacitance of Surrounding Gate Transistors: Comparison with Double Gate MOSFETs", *IEEE Transactions on Electron Devices*, Vol. 57, Issue. 10, pp. 2477-2483, October 2010.

- [9] E. Gnani, A. Gnudi, S. Reggiani and G. Baccarani, "Quasi Ballistic Transport in Nanowire FETs", *IEEE Transactions on Electron Devices*, Vol. 55, Issue. 11, pp. 2918-2930, November 2008.

- [10] E.Gnani, A.Gnudi, M.Luisier and G.Baccarani, "Band effects on Transport Characteristics of Ultrascaled Nanowire FETs", *IEEE Transactions on Nanotechnology*, Vol.7, Issue.6, pp.700-709, November 2008.

- [11] S.Poli, M.Pala and T.Poiroux, "Full Quantum Tratment of Remote Coulomb Scattering in Silicon Nanowire FETs", *IEEE Transactions on Electron Devices*, Vol. 56, Issue. 6, pp. 1191-1198, June 2009.

- [12] T. Poiroux, M. Vinet, O. Faynot, J. Wildeiz, J. Lolivier, T.Ernst, B.Previtali and S.Delonibus, "Multiple Gate Devices :Advantages and Challenges", *Microelectronic Engineering*, Vol.80, pp. 378-385, June 2005.

- [13] S. Oh, D. Monroe and JM. Hergenrother, "Analytic Description of Short channel effects in Fully Depleted Double Gate and Cylindrical Surrounding Gate MOSFETs", *IEEE Transactions on Electron Devices*, Vol. 21, Issue. 9, pp. 445-447, September 2000.

- [14] D. Jimenez, B. Iniguez, J. Sune and J. J. Saenz, "Analog Performance of the Nanoscale Double Gate MOSFET near the Ultimate Scaling Limits", *J. App. Physics.*, Vol.96, Issue.9, pp. 5271-5276, November 2004.

- [15] J.P. Collinge, M.H. Gao, A. Romano, H. Maes and C. Claeys, "Silicon-On-Insulator Gate-All-Around Device", *IEDM Tech. dig.*, 1990, pp.595-599.

- [16] N.Singh, F.Y.Lim, W.W. Fang et.al, "Ultra Narrow Silicon Nanowire GAA CMOS Devices: Impact of Diameter, Channel Orientation and Low Temperature on Device Performance", *IEDM Tech. dig.*, 2006, pp. 547-550.

- [17] Christoper. P. Auth and James D. Plummer, "A Simple Model for Threshold Voltage of Surrounding-Gate MOSFETs", *IEEE Transactions on Electron Devices*, Vol. 45, Issue.11, pp.2381-2383, November 1998.

- [18] Biswajit Ray and Santanu Mahapatra, "A New Threshold Voltage Model for Omega Gate Cylindrical Nanowire Transistor" 21st International Conference on VLSI Design, 2008, pp. 447-452, VLSID 2008.

- [19] Chiang Te-Kuang, "A Compact Analytical Threshold-

- Voltage Model for Surrounding-Gate MOSFETs with Interface Trapped Charges", *IEEE Electron Device Letters*, VOL. 31, Issue. 8, pp. 788-790, August 2010.

- [20] Chiang Te-Kuang, "A Compact Model for Threshold Voltage of Surrounding-Gate MOSFETs with Localized Interface Trapped Charges", *IEEE Transactions on Electron Devices*, Vol. 58, Issue. 2, pp. 567-571, February 2011.

- [21] M. Jagadesh Kumar, Ali A. Orouji, and Harshit Dhakad, "A New Dual-Material SG Nanoscale MOSFET: Analytical Threshold-Voltage Model", *IEEE Transactions on Electron Devices*, Vol. 53, Issue.4, pp. 920-923, April 2006.

- [22] Chiang Te-Kuang, "A New Quasi-2-D Threshold Voltage Model for Short-Channel Junctionless Cylindrical Surrounding Gate (JLCSG) MOSFETs", *IEEE Transactions on Electron Devices*, Vol. 59, Issue. 11, pp. 3127-3129, November 2012.

- [23] Chiang Te-Kuang, "A New Quasi-2-D Threshold Voltage Model for Short-Channel Junctionless Double Gate MOSFETs", *IEEE Transactions on Electron Devices*, Vol. 59, Issue. 9, pp. 2284-2289, September 2012.

- [24] Z.Ghoggali, F.Djeffal, M.A.Abdi et.al., "An Analytical Threshold Voltage Model for Nannoscale GAA MOSFETs including effects of Hot Carrier Induced Interface Charges", *Design and Test Workshop, IDT* 2008, pp.93-97, December 2008.

- [25] Yu-sheng Wu and Pin Su, "Quantum confinement Effects in short channel GAA MOSFETs and its impact on the sensitivity of Threshold Voltage to Process Variations", *Proceedings of IEEE International Conference on SOI*, pp.1-2, October 2009.

- [26] B Ray and Santanu Mahapatra, "Modeing and Analysis of Body Potential of Cylindrical GAA Nanowire Transistor", *IEEE Transactions on Electron Devices*, Vol. 55, Issue. 9, pp. 2409-2416, September 2008.

- [27] L.De Mechielis, L.Selmi and AM.Lonescu, "A Quasi Analytical model for Nanowire FETs with Arbitrary Polygonal Cross Section", *Solid State Electronics*, Vol.54, Issue.9, September 2010.

- [28] P. Rakesh Kumar and S. Mahapthra, "Quantum threshold voltage modeling of short channel quad gate silicon nanowire transistor", *IEEE Transactions on Nanotechnology*, Vol. 10, No.1, January 2011.

M. Karthigai Pandian was born in Madurai, India in 1981. He received his Bachelors of Engineering degree from the department of Electronics and Instrumentation from Karunya Institute of Technology, Coimbatore and Masters Degree in Applied Electronics from Anna University, Chennai in

2002 and 2006 respectively. He is currently employed as an Assistant Professor at Pandian Saraswathi Yadav Engineering College, Sivagangai and he is also pursuing Ph.D degree in the Department of Electronics and communication engineering, Thiagarajar College of engineering, Tamilnadu, India under Anna University Chennai. His research interest is in the area of analytical modeling and simulation of Multi gate nanowire transistors.

**N. B. Balamurugan** received his B.E and M.E degrees, both in electronics and communication engineering from the Thiagarajar College of Engineering (TCE), Tamilnadu, India. He has obtained his Ph.D degree in nanoelectronics at Anna University, India. From 1998 to 2004, he worked as a

lecturer in R.V.S.college of engineering and technology, Tamilnadu, India. He is currently working as an Associate Professor in the Department of Electronics and Communication Engineering, Thiagarajar College of Engineering (TCE), Tamilnadu, India. He has published more than 60 research papers as sole or joint author in the field of device modeling and simulation. His research interests include analytical modeling and simulation of semiconductor device structures like Nanoscale SOI MOSFETs, Nanowire Transistors and Tunnel FETs.