# A Novel Single Phase Soft Switched PFC Converter

# Nihan ALTINTAŞ<sup>†</sup>

**Abstract** – In this study, a novel single phase soft switched power factor correction (PFC) converter is developed with active snubber cell. The active snubber cell provides boost switch both to turn on with zero voltage transition (ZVT) and to turn off with zero current transition (ZCT). As the switching losses in the proposed converter are too low, L and C size can be reduced by increasing the operating frequency. Also, all the semiconductor devices operate with soft switching. There is no additional voltage stress in the boost switch and diode. The proposed converter has a simple structure, low cost and ease of control as well. It has a simple control loop to achieve near unity power factor with the aid of the UC3854. In this study, detailed steady state analysis of the proposed converter is presented and this theoretical analysis is verified by a prototype of 100 kHz and 500 W converter. The measured power factor and efficiency are 0.99 and 97.9% at full load.

Keywords: Power factor correction, AC-DC converter, Zero current transition, Zero voltage transion

### Nomenclature

| $C_p$                 | Parasitic capacitor                |

|-----------------------|------------------------------------|

| $C_s$                 | Snubber capacitor                  |

| $D_F$                 | Boost diode                        |

| $D_I$                 | Body diode of the boost switch     |

| $D_2$                 | Body diode of the auxiliary switch |

| $D_{3,4}$             | Auxiliary diode                    |

| $D_{r1,r2,r3,r2}$     | 4 Rectifier diode                  |

| $f_{s}$               | Switching frequency                |

| $i_{ac}$              | Line current                       |

| $i_{DF}$              | Boost diode current                |

| $I_i$                 | Input current                      |

| $I_o$                 | Output current                     |

| $i_{Lsa}$ , $i_{Lsb}$ | Snubber inductor current           |

| $i_{ci}$              | Boost switch current               |

Output capacitor

$C_F$

$i_{SI}$  Boost switch current  $L_F$  Boost inductance  $L_{sa}$ ,  $L_{sb}$  Snubber inductor  $R_L$  Load

$S_1$  Boost switch  $S_2$  Auxiliary switch

$t_{fl}$  Current fall time of boost switch  $t_{r2}$  Current rise time of auxiliary switch

$t_{ZVT}$  ZVT interval  $t_{ZCT}$  ZCT interval  $v_{ac}$  Line voltage

$v_{Cp}$  Parasitic capacitor voltage  $v_{Cs}$  Snubber capacitor voltage

$V_{Csmax}$  Maximum snubber capacitor voltage

$v_{D3}$  Auxiliary diode voltage  $v_{S1}$  Boost switch voltage  $v_{S2}$  Auxiliary switch voltage

$V_i$  Rectified input voltage

$V_o$  Output voltage

$Z_{1,2}$  Resonant impedance

$\omega_{1,2,3}$  Radial resonant frequency

#### 1. Introduction

AC-DC converters have been used in the power electronic systems and introduce harmonic currents from the ac mains. These harmonic currents cause some problems such as voltage distortion, poor power factor at input ac mains and noise. Single-phase power factor correction (PFC) topologies have been used in the power electronic systems to meet harmonic current limits defined by IEC 61000-3-2 [1-3].

The boost converter is the most popular topology for PFC applications because of their high power density, low-distorted input current, fast transient response and ease of control [4]. The boost PFC converter is operated in continuous conduction mode (CCM) at medium power level application [5].

A higher power density and faster transient response can be achieved by increasing switching frequency. However, as the switching frequency rises, switching losses and electromagnetic interference (EMI) noises increase. This aim can be realized by using the soft switching (SS) techniques implemented with snubber cells instead of hard switching (HS) techniques [6, 7]. SS techniques are based on Zero Voltage Switching (ZVS), Zero Current Switching (ZCS), Zero Voltage Transition (ZVT), and Zero Current Transition (ZCT) methods [8-20].

Recently, a lot of papers have been proposed to realize soft switching for the boost PFC converter. In the basic ZVT converter [8], the main switch turns on with ZVT perfectly with the help of a snubber cell. In the basic ZCT

<sup>†</sup> Corresponding Author: Dept. of Electrical Engineering, Yildiz Technical University, Turkey (naltin@yildiz.edu.tr) Received: October 6, 2013; Accepted: April 21, 2014

converter [9], the main switch turns off under ZCS and ZVS with the help of a snubber cell. A lot of papers are developed to solve the problems in basic ZVT and ZCT converters [10-17]. In these methods, there are still some problems along with significant switching losses. In order to solve these problems, ZVT and ZCT converters which are formed by combining the ZVT and ZCT methods, are suggested in [18-20]. The main switch is turned on and off with exactly at zero voltage and zero current. Also, the auxiliary switch operates under by soft switching.

In this study, a novel single phase soft switched power factor correction (PFC) converter is developed with active snubber cell. The active snubber cell provides boost switch both to turn on with zero voltage transition (ZVT) and to turn off with zero current transition (ZCT). It has a simple control loop to achieve near unity power factor with the aid of the UC3854. The detailed steady state analysis of the proposed converter is presented and this theoretical analysis is verified by a prototype of 100 kHz and 500 W converter.

## 2. Operation Modes and Analysis

#### 2.1 Definitions and assumptions

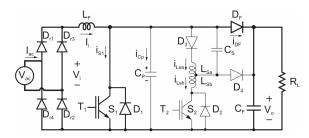

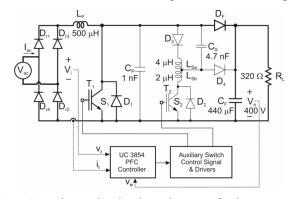

The proposed new single phase soft switched PFC converter circuit is shown in Fig. 1. In this circuit,  $v_{ac}$  is line voltage,  $i_{ac}$  is line current,  $D_{r1}$ - $D_{r4}$  are rectifier diodes,

Fig. 1. Circuit scheme of the proposed converter

$V_i$  is input voltage source,  $V_o$  is output voltage,  $L_F$  is boost inductor,  $C_F$  is output filter capacitor,  $S_1$  is boost switch and  $D_F$  is boost diode. The boost switch consists of a boost transistor  $T_1$  and its body diode  $D_1$ . In the soft switching circuit,  $S_2$  is auxiliary switch,  $L_{sa}$  and  $L_{sb}$  are snubber inductors,  $C_s$  is snubber capacitor,  $D_3$  and  $D_4$  are auxiliary diodes. The snubber capacitor  $C_p$  is assumed to be the sum of the parasitic capacitor of  $S_1$  and  $D_F$ .

In the steady-state analysis of the circuit,  $V_o$  and  $I_i$  are assumed constant for one switching cycle. Besides semi-conductor devices and resonant circuits are assumed ideal. Also, the reverse recovery times of all diodes are not taken into account.

# 2.2 Operation stages

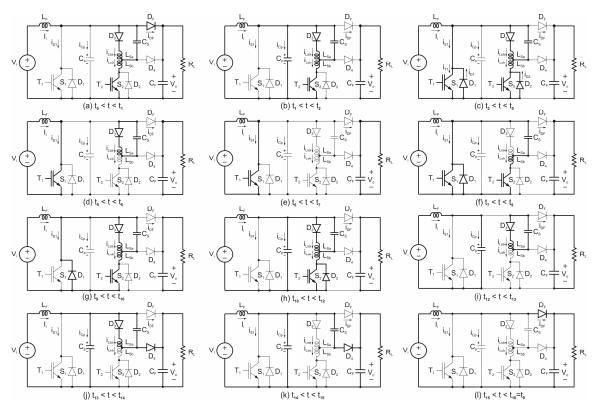

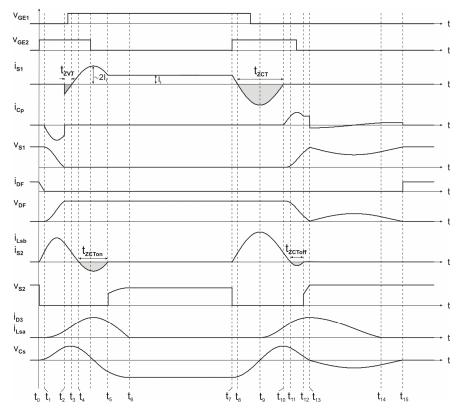

One switching period of the proposed new converter consist of 12 stages. The equivalent circuit diagrams of the operation stages are given in Fig. 2. The key waveforms

Fig. 2. Equivalent circuit schemes of the operation stages in the proposed converter

Fig. 3. The key waveforms of the proposed converter

concerning these stages are shown in Fig. 3. The detailed analysis of every stage of the proposed converter is presented below.

**Stage 1** [ $t_0 < t < t_1$ : Fig. 2(a)]: At  $t=t_0$ ,  $i_{TI}=0$ ,  $i_{T2}=0$ ,  $i_{DF}=I_p$ ,  $i_{Lsa}=0$ ,  $i_{Lsb}=0$  and  $v_{Cs}=0$  are valid. At the beginning of this stage,  $D_F$  is in the on state and conducts the input current.  $S_1$  and  $S_2$  are in the off state. At  $t=t_0$ , when the control signal is applied to the gate of  $S_2$ , a resonance starts between  $L_{sa}$ ,  $L_{sb}$  and  $C_s$ . Due to the resonance,  $C_s$  capacitor charges,  $S_2$  current rises and  $D_F$  current falls simultaneously. For this stage, the following state equations can be written generally as,

$$L_{sa} \frac{di_{Lsa}}{dt} = v_{Cs} \tag{1}$$

$$L_{sb} \frac{di_{Lsb}}{dt} = V_o - v_{Cs} \tag{2}$$

$$C_s \frac{dv_{Cs}}{dt} = i_{Lsb} - i_{Lsa} \tag{3}$$

At  $t=t_1$ ,  $i_{S2}$  reaches  $I_i$  and  $i_{DF}$  falls to zero and this stage is finished. Due to the series connected snubber inductance,  $S_2$  and  $D_3$  are turned on with ZCS. The boost diode  $D_F$  is turned off with nearly ZCS and ZVS. At the end of this mode,

$$i_{Lsa} = I_{Lsa1} \tag{4}$$

$$i_{Lsb} = I_{Lsb1} = I_i \tag{5}$$

$$v_{Cs} = V_{CsI} \tag{6}$$

can be written.

**Stage 2**  $[t_1 < t < t_2$ : Fig. 2(b)]: At  $t = t_I$ ,  $i_{TI} = 0$ ,  $i_{T2} = I_b$ ,  $i_{DF} = 0$ ,  $i_{Lsa} = I_{LsaI}$ ,  $i_{Lsb} = I_b$ ,  $v_{Cs} = V_{CsI}$  and  $v_{Cp} = V_o$  are valid.  $S_1$  and  $D_F$  are in the off state.  $S_2$  is in the on state and conducts input current  $I_i$ .

At  $t = t_1$ , a resonance starts between  $C_p$ ,  $L_{sa}$ ,  $L_{sb}$  and  $C_s$ .  $i_{Lsa}$  and  $i_{Lsb}$  current rises and the capacitor voltage of  $v_{Cp}$  decreases by the resonance. For this stage, the following state equations can be written generally as,

$$L_{sa} \frac{di_{Lsa}}{dt} = v_{Cs} \tag{7}$$

$$L_{sb} \frac{di_{Lsb}}{dt} = v_{Cp} - v_{Cs} \tag{8}$$

$$C_s \frac{dv_{Cs}}{dt} = i_{Lsb} - i_{Lsa} \tag{9}$$

$$C_p \frac{dv_{Cp}}{dt} = I_i - i_{Lsb} \tag{10}$$

At  $t = t_2$ ,  $v_{Cp}$  becomes 0 and the energy which is stored in the  $C_p$ , is transferred from capacitor to resonant circuit. At the same time,  $D_1$  turns on with ZVS and this stage ends. At the end of this mode,

$$i_{Lsa} = I_{Lsa2} \tag{11}$$

$$i_{Lsb} = I_{Lsb2} \tag{12}$$

$$v_{Cs} = V_{Cs2} \tag{13}$$

can be written.

**Stage 3** [ $t_2 < t < t_5$ : Fig. 2(c)]: At the beginning of this stage,  $i_{T1}=0$ ,  $i_{T2}=I_{Lsb2}$ ,  $i_{DF}=0$ ,  $i_{Lsa}=I_{Lsa2}$ ,  $i_{Lsb}=I_{Lsb2}$ ,  $v_{Cs}=V_{Cs2}$ and  $v_{Cp}=0$  are existent. In this mode, the resonant which is between L<sub>sa</sub>, L<sub>sb</sub> and C<sub>s</sub> is still continued. For this stage,

$$L_{sa} \frac{di_{Lsa}}{dt} = v_{Cs} \tag{14}$$

$$L_{sb} \frac{di_{Lsb}}{dt} = -v_{Cs} \tag{15}$$

$$C_s \frac{dv_{Cs}}{dt} = i_{Lsb} - i_{Lsa} \tag{16}$$

are written. In this stage three different operation modes are occurred. At t=t2, D1 is turned on and conducts the excess of i<sub>Lsb</sub> current from I<sub>i</sub>. The interval of this mode is time for the boost switch S<sub>1</sub> to turn on with ZVT. It should be noted that the gate signal of S<sub>1</sub> must be applied during this time. As a result,  $S_1$  will be turn on perfectly under ZVS and ZCS provided by ZVT. At t=t<sub>3</sub>, i<sub>Lsb</sub> drops to input current level and D<sub>1</sub> is turned off under ZCS. Just before  $D_1$  is turned off,  $S_1$  is turned on with ZVT. The boost switch current starts to rise and when it reaches to I<sub>i</sub>, the current of  $S_2$  becomes 0 at  $t=t_4$ . Just after  $t=t_4$ ,  $D_2$  is turned on. In the on state of D2, the gate signal of S2 is removed, so that  $S_2$  is perfectly turned off under ZCT. This stage ends when  $i_{D2}$  is equal to zero at the instant  $t_5$ . At the end of this stage,

$$i_{Lsa} = I_{Lsa5} \tag{17}$$

$$i_{Lsa} = I_{Lsa5}$$

(17)

$v_{Cs} = V_{Cs5}$  (18)

can be written.

**Stage 4** [ $t_5 < t < t_6$ : Fig. 2(d)]: This stage begins when D<sub>2</sub> turns off. At  $t=t_5$ ,  $i_{TI}=I_i$ ,  $i_{T2}=0$ ,  $i_{DF}=0$ ,  $i_{Lsa}=I_{Lsa5}$ ,  $i_{Lsb}=0$ ,  $v_{Cs}=V_{Cs5}$  and  $v_{Cp}=0$ . While S<sub>1</sub> conducts input current, The current through the main transistor is equal to input current. At the same time, a resonance occurs through L<sub>sa</sub>-C<sub>s</sub>-D<sub>3</sub>. For this resonance,

$$L_{sa} \frac{di_{Lsa}}{dt} = v_{Cs} \tag{19}$$

$$C_s \frac{dv_{Cs}}{dt} = -i_{Lsa} \tag{20}$$

are achieved. The energy in  $L_{\text{sa}}$  is transferred to  $C_{\text{s}}$  with this resonance. At t=t<sub>6</sub>, L<sub>sa</sub> current is equal to zero and the current direction change is blocked by D<sub>3</sub>. v<sub>Cs</sub> reaches its maximum level and this stage is finished. At the end of this mode,

$$v_{Cs} = V_{Cs6} = V_{Csmax} = \sqrt{V_{Cs5}^2 + (Z_1 I_{Lsa5})^2}$$

(21)

can be written. Where

$$Z_1 = \sqrt{\frac{L_{sa}}{C_s}} \tag{22}$$

**Stage** 5 [ $t_6 < t < t_7$ : Fig. 2(e)]: In this stage, the boost switch S<sub>1</sub> conducts I<sub>i</sub> and the auxiliary circuit is not active. This stage is the on state of the standard PWM boost converter. For this mode,

$$i_{SI} = I_i \tag{23}$$

can be written.

**Stage 6** [ $t_7 < t < t_9$ : Fig. 2(f)]: At the beginning of this stage,  $i_{Tl}=I_i$ ,  $i_{T2}=0$ ,  $i_{DF}=0$ ,  $i_{Lsa}=0$ ,  $i_{Lsb}=0$ ,  $v_{Cs}=V_{Csmax}$  and  $v_{Cp}=0$  are valid. At t=t<sub>7</sub>, when the gate signal is applied to the S<sub>2</sub>, a resonance starts between L<sub>sb</sub> and C<sub>s</sub> by the way of C<sub>s</sub>-L<sub>sh</sub>-S<sub>2</sub>-S<sub>1</sub>. For this stage, the following state equations can be written generally as,

$$L_{sb}\frac{di_{Lsb}}{dt} = -v_{Cs} \tag{24}$$

$$C_s \frac{dv_{Cs}}{dt} = i_{Lsb} \tag{25}$$

$S_2$  is turned on with ZCS through  $L_{sb}$ . The  $L_{sb}$  current rises and the boost switch current falls due to the resonance. At  $t=t_8$ , when  $i_{S2}$  reaches input current level,  $i_{S1}$  becomes zero. Just after this time, D<sub>1</sub> is turned on with ZCS and the current trough the boost switch is negative. If the gate signal of S<sub>1</sub> is removed, S<sub>1</sub> will turn off perfectly under ZVS and ZCS provided by ZCT. A new resonance occurs through the way of C<sub>s</sub>-L<sub>sb</sub>-T<sub>2</sub>-D<sub>1</sub>. D<sub>1</sub> conducts the excess of  $i_{Lsb}$  from  $I_i$ . At t=t<sub>9</sub>,  $v_{Cs}$  voltage falls to zero and  $i_{Lsb}$  reaches its maximum value and this stage finishes. At the end of this mode,

$$i_{Lsb} = I_{Lsb\,\text{max}} = \frac{V_{Cs\,\text{max}}}{Z_2}$$

(26)

is valid. Here,

$$Z_2 = \sqrt{\frac{L_{sb}}{C_s}} \tag{27}$$

**Stage** 7 [ $t_9 < t < t_{10}$ : Fig. 2(g)]: At the beginning of this stage,  $i_{TI}=0$ ,  $i_{T2}=I_{Lsbmax}$ ,  $i_{DF}=0$ ,  $i_{Lsa}=0$ ,  $i_{Lsb}=I_{Lsbmax}$ ,  $v_{Cs}=0$ and  $v_{Cp}=0$  are valid. At t=t<sub>9</sub>, while  $v_{Cs}$  starts to be positive, the diode D<sub>3</sub> is turned on with ZCS. A new resonance is occurred between L<sub>sb</sub>, L<sub>sa</sub> and C<sub>s</sub>. For this state,

$$L_{sa} \frac{di_{Lsa}}{dt} = v_{Cs} \tag{28}$$

$$L_{sb}\frac{di_{Lsb}}{dt} = V_o - v_{Cs} \tag{29}$$

$$C_s \frac{dv_{Cs}}{dt} = i_{Lsb} - i_{Lsa} \tag{30}$$

can be written. D<sub>1</sub> current becomes zero when i<sub>Lsb</sub> falls again to I<sub>i</sub>. At t=t<sub>10</sub>, D<sub>1</sub> is turned off under ZCS and this stage ends. At the end of this mode,

$$i_{Lsa} = I_{Lsa10} \tag{31}$$

$$\begin{array}{ll} i_{Lsa} = I_{Lsa10} & (31) \\ i_{Lsb} = I_{Lsb10} = I_{i} & (32) \\ v_{Cs} = V_{Cs10} & (33) \end{array}$$

$$v_{Cs} = V_{Cs10}$$

(33)

are valid. t<sub>8</sub>-t<sub>10</sub> is the on state time interval of D<sub>1</sub> and it is also equal to the ZCT time of the converter. The control signal of S<sub>1</sub> must be removed during this time and so the boost switch is turned off perfectly under ZCS and ZVS provided by ZCT.

**Stage 8**  $[t_{10} < t < t_{11}$ : Fig. 2(h)]: At  $t = t_{10}$ ,  $i_{T1} = 0$ ,  $i_{T2} = I_b$  $i_{DF}$ =0,  $i_{Lsa}$ = $I_{Lsa10}$ ,  $i_{Lsb}$ = $I_{i}$ ,  $v_{Cs}$ = $V_{Cs10}$  and  $v_{Cp}$ =0 are valid. Just after this time, a resonance occurs between C<sub>p</sub>, L<sub>sa</sub>, L<sub>sb</sub> and C<sub>s</sub> with the input current. The state equations are formed for this mode as follows.

$$L_{sa} \frac{di_{Lsa}}{dt} = v_{Cs} \tag{34}$$

$$L_{sb} \frac{di_{Lsb}}{dt} = v_{Cp} - v_{Cs} \tag{35}$$

$$C_s \frac{dv_{Cs}}{dt} = i_{Lsb} - i_{Lsa} \tag{36}$$

$$C_p \frac{dv_{Cp}}{dt} = I_i - i_{Lsb} \tag{37}$$

i<sub>Lsb</sub> continues to decrease due to the resonance and becomes zero at t=t<sub>11</sub>. The auxiliary switch current becomes negative. The control signal of S2 must be removed during this interval, in which D<sub>2</sub> is in the on state. The auxiliary switch S<sub>2</sub> is turned off perfectly under ZCS and ZVS provided by ZCT. i<sub>S2</sub> becomes zero at t=t<sub>12</sub> and this stage ends. At the end of this mode,

$$i_{Lsa} = I_{Lsa12}$$

(38)

$$v_{Cs} = V_{Cs12}$$

(39)

$$v_{Cp} = V_{Cp12} \tag{40}$$

are valid.

**Stage 9** [ $t_{12} < t < t_{13}$ : Fig. 2(i)]: At the beginning of this stage,  $i_{TI}=0$ ,  $i_{T2}=0$ ,  $i_{DF}=0$ ,  $i_{Lsa}=I_{Lsa12}$ ,  $i_{Lsb}=0$ ,  $v_{Cs}=V_{Cs12}$  and  $v_{Cp} = V_{Cp12}$  are valid. There are two different closed circuits

for this interval. For the first one, C<sub>p</sub> is charged linearly with  $I_i$  and the second one, a resonance occurs between  $L_{sa}$ and  $C_s$  via the path  $L_{sa}$ - $C_s$ - $D_3$ . For this mode,

$$L_{sa} \frac{di_{Lsa}}{dt} = v_{Cs} \tag{41}$$

$$C_s \frac{dv_{Cs}}{dt} = -i_{Lsa} \tag{42}$$

$$C_p \frac{dv_{Cp}}{dt} = I_i \tag{43}$$

can be written. The sum of the  $v_{Cp}$  and  $v_{Cs}$  voltages becomes equal to output voltage at t=t<sub>13</sub>. D<sub>4</sub> is turned on with ZVS and this mode is finished. At the end of this mode,

$$i_{Lsa} = I_{Lsa13} \tag{44}$$

$$v_{Cs} = V_{Cs13} \tag{45}$$

$$v_{Cn} = V_{Cn13} \tag{46}$$

are valid.

**Stage 10** [ $t_{13} < t < t_{14}$ : Fig. 2(j)]: At  $t = t_{13}$ ,  $i_{T1} = 0$ ,  $i_{T2} = 0$ ,  $i_{DF}$ =0,  $i_{Lsa}$ =  $I_{Lsa13}$ ,  $i_{Lsb}$ =0,  $v_{Cs}$ = $V_{Cs13}$  and  $v_{Cp}$ = $V_o$ - $V_{Cs13}$  are existent. In this stage, a resonance between L<sub>sa</sub>, C<sub>s</sub> and C<sub>p</sub> starts under the input current. At t=t<sub>14</sub>, i<sub>Lsa</sub> current becomes zero. This mode is finished. The energy stored in the L<sub>sa</sub> is transferred to the capacitors and to the load. For this mode, the following equations are derived.

$$L_{sa} \frac{di_{Lsa}}{dt} = v_{Cp} - V_o \tag{47}$$

$$C_p \frac{dv_{Cp}}{dt} = I_i - i_{Lsa} - C_s \frac{d(v_{Cp} - V_o)}{dt}$$

(48)

**Stage 11** [ $t_{14} < t < t_{15}$ : Fig. 2(k)]: At  $t = t_{14}$ ,  $i_{T1} = 0$ ,  $i_{T2} = 0$ ,  $i_{DF}=0$ ,  $i_{Lsa}=0$ ,  $i_{Lsb}=0$ ,  $v_{Cs}=V_{Cs14}$  and  $v_{Cp}=V_o-V_{Cs14}$  are valid.  $C_p$  is charged linearly with  $I_i$  and  $C_s$  is discharged. For this

$$C_p \frac{dv_{Cp}}{dt} = I_i - C_s \frac{dv_{Cs}}{dt} \tag{49}$$

$$v_{Cp} + v_{Cs} = V_o \tag{50}$$

can be written.  $v_{Cp}$  reaches  $V_o$  and  $v_{Cs}$  falls to  $0\,$ simultaneously at  $t_{15}$ .  $D_F$  is turned on with ZVS and  $D_{33}$  is turned off with ZVS, and this mode finishes.

**Stage 12**  $[t_{15} < t < t_{16}$ : Fig. 2(l)]: At  $t=t_{15}$ ,  $i_{T1}=0$ ,  $i_{T2}=0$ ,  $i_{DF}\!\!=\!\!I_i,~i_{Lsa}\!\!=0,~i_{Lsb}\!\!=\!\!0,~v_{Cs}\!\!=\!\!0$  and  $v_{Cp}\!\!=\!\!V_o$  are valid. In this stage, the boost diode continues conducting the input current and the auxiliary circuit is not active. This stage is the off state of the PWM boost converter. For this mode,

$$i_{\rm DF} = I_{\rm i}$$

(51)

can be written.

At  $t=t_{16}=t_0$ , one switching period is completed by applying the control signal to boost switch again, and new switching period is started.

#### 3. Converter Features

#### 3.1 Main futures

The proposed converter is endowed with the active snubber cell which overcomes most of the drawbacks of the conventional PFC converter. Also, it has achieved nearly unity power factor at overall load range.

- The boost switch is turned on with ZVT and turn off with ZCT, perfectly. The auxiliary switch is turned on with ZCS and turned off with ZCT

- The boost switch is not subjected to any additional voltage stress. The current stress of main switch is at acceptable levels but this is the disadvantage of this converter.

- 3) The main diode is not subjected to any additional voltage and current stresses.

- 4) The soft switching operation of the new converter is maintained for the overall line and load ranges.

- 5) The converter can operate at considerably high frequencies and acts as a normal PWM converter. Also the circulating energy is quite small.

- 6) The sum of transient intervals is a very little part of the switching cycle.

- 7) Nearly unity power factor is achieved at full load condition and even light load condition.

# 3.2 Comparison of the proposed PFC converter and the PFC converter in [20]

In the proposed PFC converter, all semiconductor devices in the circuit are switched under soft switching. The boost switch is perfectly turned on and off with ZVT and ZCT, respectively. The auxiliary switch is turned on with ZCS and turned off with ZCT. But the PFC converter in [20], the boost switch and auxiliary switch are turned off with near ZVS. So that, the turn off switching losses are occurred in this case. As a result of this, the switching frequency can be selected higher than [20] and the efficiency of the proposed converter will be higher than [20]. The soft switching capabilities of the proposed converter and the PFC converter of [20] are summarized in the Table 1.

**Table 1.** Switching states

|                  | Proposed I | PFC converter | PFC converter in [20] |          |

|------------------|------------|---------------|-----------------------|----------|

| Device           | Turn on    | Turn off      | Turn on               | Turn off |

| Boost Switch     | ZVT        | ZCT           | ZVT                   | near ZVS |

| Auxiliary Switch | ZCS        | ZCT           | ZCS                   | near ZVS |

| Boost Diode      | ZVS        | ZCS, ZVS      | ZVS                   | ZVS      |

# 4. Design Procedure

A procedure for the design of the proposed converter is presented in this section. The design of the main power circuit can be found in any standard power electronics textbook so that only the design of the snubber circuit components is presented. In this study, the average control technique is used in the control circuit.

- C<sub>p</sub> is assumed to be the sum of parasitic capacitor of the main switch and the other parasitic capacitors incorporating it.

- 2) The  $t_{ZCT}$  interval must be chosen at least as fall time of the boost switch  $(t_{fl})$ .

$$t_{ZCT} \ge t_{fl} \tag{52}$$

3) In order to turn off the auxiliary switch with ZCT, the value of  $L_{sa}$  must be at least 2 times of  $L_{sb}$  value.

$$L_{sa} \ge 2L_{sb} \tag{53}$$

4) L<sub>sb</sub> is selected to allow a current rise rate to be the maximum input current at most, within the auxiliary switch turn-on process and its current rise time.

$$\frac{V_o}{L_{sh}} t_{r2} \le I_{i \max} \tag{54}$$

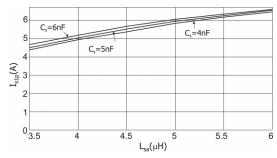

5) The value of  $C_s$  depends on the values of  $C_p$ ,  $L_{sa}$  and  $L_{sb}$ . Also, the resonance current maximum value should be higher than the input current, the  $t_{ZCT}$  operation should be provided and the total resonance

**Table 2.** Some values of the components used in experimental circuit witching states

| Component      | Parameter             | Value                    |

|----------------|-----------------------|--------------------------|

| Capacitors     | Cs                    | WIMA MKP, 4.7nF/630V     |

|                | $C_{F}$               | EPCOS, 440μF/450V        |

| Inductors      | $L_{\rm F}$           | 500μΗ                    |

|                | $L_{sa}$              | 4μΗ                      |

|                | $L_{sb}$              | 2μΗ                      |

|                | $S_1$                 | IXGR50N60C2D1 (600V-40A) |

| Semiconductors | $S_2$                 | IXGP16N60C2D1 (600V-16A) |

|                | $D_F$ , $D_3$ , $D_4$ | DSEI8-06 (600V-8A)       |

Fig. 4. Variation of maximum current through the main switch with snubber inductance  $L_{\rm sa}$  for different snubber capacitor  $C_{\rm s}$

interval should not affect the PWM operation.

In order to give an idea about the selection of the components of the snubber cell, a design example is given below. Some values of the components used in experimental circuit are given in Table 2. According to design procedure and Table 2, snubber circuit components are determined. The capacitor  $C_p$  is assumed to be the sum of the parasitic capacitor of main switch and the other parasitic capacitors incorporating it. In the experimental circuit,  $C_p$  is approximately 1 nF. The  $L_{sb}$  value is selected as 2  $\mu H$  from (54).  $L_{sa}$  is selected as 4  $\mu H$  from (53). If the maximum value of the main switch current is assumed to be twice the input current, by using the characteristic curves shown in Fig. 4, the value of  $C_s$  is selected as 4.7 nF.

# 5. Experimental Results

The experimental circuit scheme of the converter is shown in Fig. 5.

The converter is to be designed according to the following specifications: output voltage  $V_o = 400 \text{ V}$ , input voltage  $V_{ac}$ =85-265 V, output power  $P_o$ = 500 W, switching frequency  $f_s$  = 100 kHz.  $L_F$  boost inductance is designed to provide PFC and to operate in CCM.  $C_F$  output capacitor is selected to have constant voltage. The control circuit associated with the UC3854 integrated circuit is designed

Fig. 5. Experimental circuit scheme of the proposed converter

Fig. 6. Some oscillograms with the scales of 5 V/div, 1  $\mu$ s/div for only (a), 200 V/div, 2 A/div, 1  $\mu$ s/div for (b)-(g): (a) Control signals of  $S_1$  and  $S_2$ ; (b) Voltage and current of  $S_1$ ; (c) Voltage and current of  $D_F$ ; (d) Voltage and current of  $S_2$ ; (e) Voltage and current of  $S_3$ ; (f) Voltage and current of  $S_3$ ; (e) Voltage and current of  $S_3$ ; (f) Voltage and current of  $S_3$ ; (e) Voltage and current of  $S_3$ ; (f) Voltage and current of  $S_3$ ; (e) Voltage and current of  $S_3$ ; (f) Voltage and current of  $S_3$ ; (e) Voltage and current of  $S_3$ ; (f) Voltage and current of  $S_3$ ; (e) Voltage and current of  $S_3$ ; (f) Voltage and current of  $S_3$ ; (e) Voltage and current of  $S_3$ ; (f) Voltage and current of  $S_3$ ; (e) Voltage and current of  $S_3$ ; (f) Voltage and current of  $S_3$ ; (e) Voltage and current of  $S_3$ ; (f) Voltage and  $S_3$ ; (f) Voltage and

as suggested in [21]. Due to the well-known, the control circuit design procedure is not given here. UC3854A integrated circuit generates the control signal of the boost switch. The auxiliary switch control signal is produced by using the control signal of the boost switch with the help of the analog card.

In the Fig. 6(a), the control signals of the main and auxiliary switches are shown. The auxiliary switch operates twice in a one switching period of the main switch.

The voltage and current waveforms of the boost switch  $S_1$  are shown in the Fig. 6(b). It can be seen that turn on and turn off process of the  $S_1$  is realized with soft switching. There is no overlap between current and voltage waveforms of  $S_1$ . From the  $S_1$  current waveform, the body diode is turned on firstly and then the control signals of the  $S_1$  is removed during the turn on and turn off process of the switch. So, ZVT turn on and ZCT turn off processes is perfectly realized. Also, there is no any additional voltage stress on the main switch and it has got an acceptable current stress.

The boost diode is turned on under ZVS and turned off under ZCS and ZVS. It can be seen in Fig. 6(c), there is no any additional voltage and current stresses on the boost diode.

The auxiliary switch voltage and current waveforms are shown in Fig. 6(d). The auxiliary switch is operated in both ZVT and ZCT processes of the boost switch. It means that the operating frequency of the auxiliary switch is two times of the boost switch operating frequency. Also, the auxiliary switch conduction time is very short. The auxiliary switch is turned on under near ZCS due to the serial connected inductance and is turned off with ZCT perfectly due to the removal of drive signal while the body diode is conducting. By the way, there are no additional voltage stresses on the auxiliary switch while its operate under soft switching.

Fig. 6(e) shows the voltage and current waveforms of  $D_3$ . Reverse recovery current of the diode and a discharge current of the capacitor are shown in that figure.

The voltage and current waveforms of the snubber capacitor are shown in Fig. 6(f). The voltage across the snubber capacitor starts to increase when the resonance is started with the auxiliary transistor turn on in the ZVT interval of the boost switch. It becomes zero nearly half of the output voltage at the end of the ZVT interval. At the end of the ZCT interval, the capacitor voltage is equal to zero.

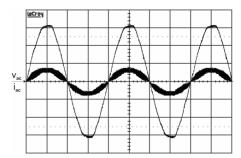

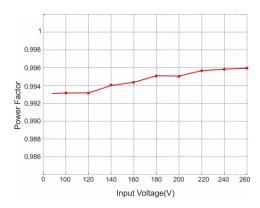

The input voltage and current waveforms are given in Fig. 7. The power factor of the proposed converter is near unity with 0.99. Also, it is seen that the proposed PFC converter operates in CCM. Fig. 8 presents the response of the power factor for universal input line voltage for full load condition. It can be observed that the proposed converter will exhibit a power factor of near 0.99 at any power line voltage between 85 and 260 V<sub>rms</sub>. The proposed converter is tested at universal input line voltage and very wide load ranges. It is observed that it keeps operating

**Fig. 7.** The input voltage and current waveforms with the scales of 100 V/div, 5 A/div and 5 ms/div.

**Fig. 8.** The input voltage and current waveforms with the scales of 100 V/div, 5 A/div and 5 ms/div.

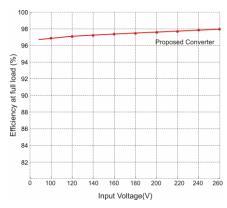

**Fig. 9.** Converter efficiency at full load and varying line voltage.

under soft switching conditions successfully for the whole line and load ranges.

In the Fig. 9, efficiency waveform of the proposed converter is given for the range of universal input line voltage at full load. The efficiency value is increasing along with the line voltage. Basically, losses depend on current in the converters. In order to obtain the same output power, the input current decreases when the input line voltage increases.

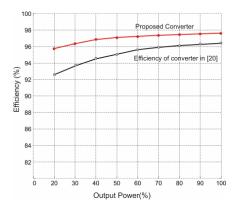

In the Fig. 10, efficiency variations of the proposed converter and the converter in [20] are given for 220  $V_{rms}$  input voltages. It can be seen that the efficiency values of the proposed converter which operates at 100 kHz are

**Fig. 10.** Efficiency curves of the proposed converter and the converter in [20].

higher than the converter in [20] which operates at 50 kHz. The main reason of the efficiency improvement is all switches operate under exact soft switching in the proposed converter. The overall efficiency of the proposed converter is measured about 97.9% at the nominal output power.

#### 6. Conclusion

In this study, a novel snubber circuit is used in the PFC converter. This snubber circuit provides ZVT turn on and ZCT turn off together for the boost switch of the converter. Also, it is implemented by using only one quasi resonant circuit without an important increase in cost and complexity. The proposed converter solves many drawbacks of the PFC converters presented earlier. All semiconductor devices in the circuit are switched under soft switching. The boost switch is not subjected to any additional voltage stress. The boost diode is not subjected to any additional voltage and current stresses. A detailed steady-state analysis of the proposed converter is presented. The theoretical analysis of the proposed converter is exactly verified by 500 W and 100 kHz prototype. The average current mode control method is used in the proposed converter. The power factor of the proposed converter is measured nearly 0.99. Additionally, at nominal output power, the converter efficiency is reach approximately 97.9%.

#### References

- [1] S. Singh, B. Singh, "PFC Bridge Converter for Voltage-controlled Adjustable-speed PMBLDCM Drive", Journal of Electrical Eng. & Tech., vol. 6, pp. 215-225, March 2011.

- [2] R. Kalpana, "Direct Single-stage Power Converter with Power Factor Improvement for Switched Mode Power Supply", Journal of Electrical Eng. & Tech., vol. 5, pp. 468-476, Sep. 2010.

- [3] B. Zhonghu, M. Chen, S. K. T. Miller, N. Yasuyuki, S. Jian, "Recent developments in single-phase power

- factor correction", Power Conversion Conference, pp. 1520 1526, 2007.

- [4] O. Garcia, J.A. Cobos, R. Prieto, P. Alou, J. Uceda, "Single Phase Power Factor Correction: A Survey", IEEE Trans. Power Electronics, vol. 18, pp. 749-755, May 2003.

- [5] C. Qiao, K.M. Smedley, "A topology Survey of Single-Stage Power Factor Corrector with a Boost Type Input Current Shaper", IEEE Trans. Power Electronics, vol. 16, pp. 360-368, May 2001.

- [6] H. Bodur, A.F. Bakan, "A New ZVT-PWM DC-DC Converter", IEEE Trans. Power Electronics, vol. 17, pp. 40-47, Jan. 2002.

- [7] H. Bodur, A.F. Bakan, "A New ZVT-ZCT-PWM DC-DC Converter", IEEE Trans. Power Electronics, vol. 19, pp. 676-684, May 2004.

- [8] G. Hua, C.S. Leu, Y. Jiang, F.C. Lee, "Novel Zero-Voltage-Transition PWM Converters", IEEE Trans. Power Electronics, vol. 9, pp. 213-219, March 1994.

- [9] G. Hua, E.X. Yang, Y. Jiang, F.C. Lee, "Novel Zero-Current-Transition PWM Converters", IEEE Trans. Power Electronics, vol. 9, pp. 601- 606, Nov. 1994.

- [10] H. Mao, F. C. Lee, X. Zhou, H. Dai, M. Cosan, D. Boroyevich, "Improved Zero-Current-Transition Converters for High-Power Applications", IEEE Trans. Industrial Application, vol. 33, pp. 1220-1232 Sep.-Oct. 1997.

- [11] J.G. Cho, J.W. Baek, G.H. Rim, I. Kang, "Novel Zero-Voltage-Transition PWM Multiphase Converters", IEEE Trans. Power Electronics, vol. 13, pp. 152-159 Jan. 1998.

- [12] C.J. Tseng, C.L. Chen, "Novel ZVT-PWM Converters with Active Snubbers", IEEE Trans. Power Electronics, vol. 13, pp. 861-869, Sep. 1998.

- [13] K.M. Smith, K.M. Smedley, "Properties and Synthesis of Passive Lossless Soft-Switching PWM Converters", IEEE Trans. Power Electronics, vol. 14, pp. 890-899 Sep. 1999.

- [14] H. Yu, B. M. Song, J. S. Lai, "Design of a Novel ZVT Soft-Switching Chopper", IEEE Trans. Power Electronics, vol. 17, pp. 101-108, Jan. 2002.

- [15] C.M. Wang, "Novel Zero-Voltage-Transition PWM DC-DC Converters", IEEE Trans. Industrial Electronics, vol.53, pp. 254-262, Feb. 2006.

- [16] W. Huang, G. Moschopoulos, "A New Family of Zero-Voltage-Transition PWM Converters with Dual Active Auxiliary Circuits", IEEE Trans. Power Electronics, vol. 21, pp. 370-379, March 2006.

- [17] P. Das, G. Moschopoulos, "A Comparative Study of Zero-Current-Transition PWM Converters", IEEE Trans. Industrial Electronics, vol.54, pp. 1319-1328 June 2007.

- [18] C. M. de O. Stein and H. L. Hey, "A true ZCZVT commutation cell for PWM converters", IEEE Trans. Power Electronics, vol. 15, pp. 185-193, Jan. 2000.

- [19] I. Aksoy, H. Bodur, A.F. Bakan, "A New ZVT-ZCT-

- PWM DC-DC Converter", IEEE Trans. Power Electronics, vol.25, pp. 2093-2105, Aug. 2010.

- [20] M. Mesh, A.K. Panda, "Increase of Efficiency of an AC-DC Power Factor Correction Boost Converter by a Novel Soft-switching Technique", Int. Journal of Electric Power Comp. and Sys., vol. 40, pp. 57-73, November 2012.

- [21] P.C. Todd, "UC3854 Controlled Power Factor Correction Circuit Design", UNITRODE Product & Applications Handbook, 1995-1996.

Nihan ALTINTAŞ She received the B.S., M.S. and Ph.D. degrees in electrical engineering from Yıldız Technical University, Turkey, in 2004, 2007 and 2012 in electrical engineering at Yıldız Technical University. Her research has been concentrated on the areas of DC-

DC converters, power factor correction techniques, and soft switching techniques in power electronics. She was also employed in three research projects concerning power electronics.