# Implementation of Excitatory CMOS Neuron Oscillator for Robot Motion Control Unit

Jing Lu<sup>1</sup>, Jing Yang<sup>1</sup>, Yong-Bin Kim<sup>1,\*</sup>, Joseph Ayers<sup>2</sup>, and Kyung Ki Kim<sup>3</sup>

Abstract—This paper presents an excitatory CMOS oscillator circuit design, neuron which can synchronize two neuron-bursting patterns. The excitatory CMOS neuron oscillator is composed of CMOS neurons and CMOS excitatory synapses. And the neurons and synapses are connected into a close loop. The CMOS neuron is based on the Hindmarsh-Rose (HR) neuron model and excitatory synapse is based on the chemical synapse model. In order to fabricate using a 0.18 um CMOS standard process technology with 1.8V compatible transistors, both time and amplitude scaling of HR neuron model is adopted. This full-chip integration minimizes the power consumption and circuit size, which is ideal for motion control unit of the proposed bio-mimetic micro-robot. The experimental results demonstrate that the proposed excitatory CMOS neuron oscillator performs the expected waveforms with scaled time and amplitude. The active silicon area of the fabricated chip is 1.1 mm<sup>2</sup> including I/O pads.

*Index Terms*—CMOS neuron, motion control unit, central pattern generator, bio-mimetic micro-robot, Hindmarsh-Rose neuron, chemical synapse model, excitatory neuron oscillator

#### I. INTRODUCTION

Biomimetic robotics is attracting the interest of growing number of robotics researchers worldwide. The advancements of robotics technologies have recently led to an increased interest towards bio-mimetic robotics in the scientific fields related to biology and to the study of living organisms.

One central topic is developing their movement control under unstructured operation environment. For underwater application, unexpected flow fluctuations and unpredicted obstacles requires the bio-mimetic robots to have life-like reaction to the dynamic environments. Another design challenge lies in untethered operation and mission duration, which requires the robots to have selfsupport energy and small body to minimize the power consumption. In order to meet these requirements, the control electronics needs to be of low power and economic in size. A number of digital bio-mimetic robot controlling schemes have been reported. However, the majority of them show poor performances in complicated environments like outer space and the bottom of the sea due to inability to adapt to dynamic environments and their discrete-time responses. Traditionally, such a robot is guided by computer and electronic programming and could only work in well-controlled environments. Furthermore, existing robots usually have a large volume and powered either by implantable batteries or power grid, which limit their working life span and working places. Nowadays, there is a growing demand for industrial, military, and scientific research to have autonomous micro-robots that have diminutive body, long lasting working time and perform their jobs in unstructured environments. Focusing on motion control

Manuscript received Feb. 1, 2014; accepted May. 8, 2014 A part of this work was presented in International SoC Design

Conference (ISOCC), Busan in Korea, November 2013. <sup>1</sup>Department of Electrical and Computer Engineering, Northeastern

University, Boston, Massachusetts, USA

<sup>&</sup>lt;sup>2</sup> Department of Biology and Marine Science Center, Northeastern

University, Boston, Massachusetts, USA

<sup>&</sup>lt;sup>3</sup> Department of Electronic and Electrical Engineering, Daegu

University, Gyeongsan, Korea

E-mail : ybk@ece.neu.edu

unit, conventional robots are mostly controlled by an algorithm based system such as finite state machines [1]. However, algorithm based robots suffer from deterministic operation in lack of anticipating all contingencies and clumsy reaction due to intrinsic discrete time control. Motivated by biological discoveries, bio-mimetic autonomous robots that have lifelike and robust movement by mimicking the control mechanisms of animals become a hot research approach [2, 3]. Excitatory neuron oscillator, as a fundamental pattern of biological motion control unit is investigated in this paper.

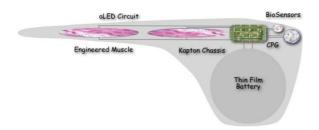

Fig. 1 illustrates the frame of a bio-mimetic micro robot that adopts CMOS neuron based motion controller [4, 5]. It is composed of biosensors, CMOS neuron based motion control unit (also called central pattern generator CPG), engineered muscle which is activated by organic light emitting diode (OLED) circuit, and powered by thin film battery, all of which are covered with Kapton chassis. In such a composition, external environment changes are received by engineered cellular sensors through exteroceptive reflexes. The sensors then release command to CPG motion control unit to generate corresponding motion patterns. OLED circuit then transfers the motion patterns and the optogeneticallyengineered muscles that respond to light will produce an undulatory movement of the body axis.

There are two basic patterns of CPG, excitatory or inhibitory. The excitatory pattern contains two neurons oscillating with the same phase through excitatory synapses. Inhibitory pattern is just the opposite, with two neurons oscillating at 180 degree of phase difference through inhibitory synapses. In this paper, excitatory

**Fig. 1.** Diagram of the proposed Cyberplasm robot. The biosensors receive external environment signals and pass them to COMS neuron based motion control unit (also called central pattern generator CPG). CPG processes those signals and outputs control signals through OLED circuit to engineered muscles to guide robot's movement. Kapton powered by thin film battery coats the robot.

pattern is achieved and verified by using 0.18um standard CMOS technology. The analog solution preserves the nature of the HR neuron model and chemical synapse model and its time and amplitude are well scaled with a great easiness to be powered by 1.8 V supply voltage.

The paper is organized as follows: First, Hindmarsh-Rose (HR) neuron model is introduced as the mathematic basis of the proposed CMOS neuron. Time and amplitude is scaled in order to meet the fabrication technology and low power requirements. After scaling, circuit implementation of the proposed CMOS neuron using 0.18um technology is presented. The chemical synapse model and its circuit implementation are described in section III. Based on the proposed neuron design, the excitatory connection of the neuron oscillator is proposed in section IV and experimental results are presented to demonstrate the performance and viability of the excitatory CMOS neuron oscillator in section V. Finally, the paper is concluded in the last section.

# **II. CMOS HINDMARSH-ROSE NEURON**

#### 1. Hindmarsh-Rose (HR) Neuron Model

There are twenty neuron models developed in the research history, the summary of the types of neuron models ranges from the simplest one to the most dedicated ones [6]. Among those, the HR model has both the biological meaning and simplicity compared to the higher order models. The mathematical expression of HR model [7] is given by

$$dx/dt = y - ax^3 + bx^2 - z + I,$$

(1)

$\frac{dy}{dt} = c - \frac{dx^2}{y},\tag{2}$

$$dz/dt = r(s(x - x_1) - z).$$

(3)

where

x is membrane potential,

y is recovery current,

z is adaptation current,

*I* is applied current,

$x_1$  is the leftmost equilibrium point of the neuron model without adaptation.

The initial conditions for state variables  $(x_0, y_0, z_0)$  are

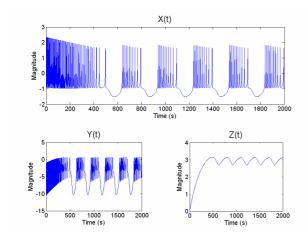

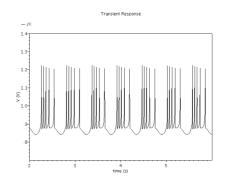

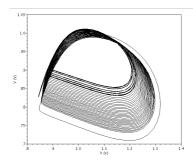

Fig. 2. MATLAB simulation result of HR model.

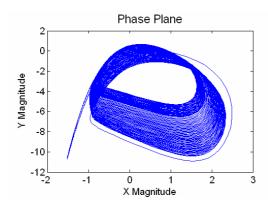

Fig. 3. The phase plane of x and y parameter.

(0,0, 0).While the coefficients of HR neuron equations are: a=1, b=3, c=1.01, d=5.0128, r=0.0021, s=3.966, and  $x_1=1.605$ . Input *I* controls different states of this neuron model. It can vary from 0 to 3.024, along with which the HR equation output changes from no spiking to infinite spiking.

Fig. 2 shows MATLAB simulation of HR's three variable x, y and z with I equals to 2. After about 500 seconds startup time, both x and y begin a tonic oscillation, which is a set of spikes followed by a rest period. The x variable is the desired output which mimics the animal's neural behavior. Eqs. (1) and (2) determine the spikes, and Eq. (3) controls the silence period after certain spikes. From (1), it is observed that variable z counteracts the effect of input I. At the same time, variable z is the integration of variable x according to (3). At first, each spike adds value to z, which has the same effect of lowing input I. This action causes the output spikes to slow down as time goes by, and finally stop after a time, called the silence period. In silence period,

because x goes low, z thus falls, which makes input I released and allows the system to be activated again and the spiking resumes again.

Fig. 3 depicts the phase plane of x and y variables, which can be an important criterion to exam the circuit simulation results. Though the three variables in the HR neuron model biologically represent current, it is more convenient to implement them in voltage mode. In the following discussion, these three variables will be treated as voltage signals without notification.

### 2. Scaling of HR Model

As shown in the vertical axis of variable *x*, *y*, *z* in Fig. 3, the magnitudes are all beyond the supply rail in the proposed implementation. Therefore, magnitude scaling is required. The slow bursting frequency requires large on-chip components. Therefore, time scaling is also required [8]. However, the scaling requires a compromise process since an aggressive time scaling may lose HR neuron's biologic meaning and cause too fast behavioral operation of a physical device. Scaled parameters are defined as:  $X = x/x_{ms}$ ,  $Y = y/y_{ms}$ ,  $Z = z/z_{ms}$  and  $T = T_s \times t$ . Applying the scaled parameters to (1) (2) and (3), new equations are obtained as follows:

$$\frac{dX}{dt} = \frac{1}{T_s} \left( \frac{y_{ms}}{x_{ms}} Y - a x_{ms}^2 X^3 + b x_{ms} X^2 - \frac{z_{ms}}{x_{ms}} Z + \frac{1}{x_{ms}} I \right),$$

(4)

$$\frac{dY}{dt} = \frac{1}{T_s} \left( c \frac{1}{y_{ms}} - d \frac{x_{ms}^2}{y_{ms}} X^2 - Y \right), \tag{5}$$

$$\frac{dZ}{dt} = \frac{1}{T_s} \left( r \left( s \left( \frac{x_{ms}}{z_{ms}} X - x_1 \frac{1}{z_{ms}} \right) - Z \right) \right). \tag{6}$$

Though the amplitude of each variable can be adjusted to a low voltage through scaling, an additional level shift voltage  $V_{\text{bias}}$  should also be added to lift all the signals above ground in this single rail supply system. Besides, a multiplier circuit is needed to produce the square and cubic term of x variable. It requires both x variable and its complementary signal, which is the mirror voltage of x variable.  $V_{\text{bias}}$  should have a minimum voltage larger than 0.7V. With the supply voltage of 1.8V,  $V_{\text{bias}}$  is set to 1V and the amplitude of x variable is confined around 400 mV. The following magnitude scaling factors are utilized:  $x_{ms} = 10$ ,  $y_{ms} = 50$ ,  $z_{ms} = 10$  Taking into account of hardware consumption and biological meaning of HR neuron model, the time factor is chosen to be  $T_s = 2.2e - 3 \text{ s} [9]$ .

## 3. Circuit Implementation of HR Model

## A. Analog Computer

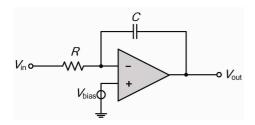

The basic building block of analog integration is shown in Fig. 4 [10], and summing job can be done automatically in the input junction.  $V_{bias}$  is the level shifted voltage. The output voltage can be expressed as:

$$V_{out} = -\frac{1}{RC} \int_0^t V_{in} dt + V_{inital}.$$

(7)

where  $V_{in}$  is the input voltage. The multiplication of R and C value determines the time factor  $T_{s.}V_{inital}$  equals to  $V_{bias.}$

From the analysis of (7), Eqs. (4)-(6) can be rewritten as (8), (9) and (10).

$$\frac{dX}{dt} = \frac{1}{R_1 C_1} L + \frac{1}{R_2 C_1} Y - \frac{1}{R_3 C_1} Z + \frac{1}{R_4 C_1} X^2 + \frac{1}{R_5 C_1} X^3,$$

(8)

$$\frac{dY}{dt} = \frac{1}{R_Y C_2} Y + \frac{1}{R_{X2} C_2} X^2 + \frac{1}{R_m C_2} M, \tag{9}$$

$$\frac{dZ}{dt} = \frac{1}{R_k C_3} K - \frac{1}{R_X C_3} X - \frac{1}{R_Z C_3} Z .$$

(10)

New parameters *L*, *M* and *K* are introduced in order to maintain input constant *I*, *c* and *x*<sub>1</sub> within the supply rail. Given new scaling factors  $(\alpha, \beta, \gamma)$ ,  $L = I / \alpha + V_{bias}$ ,  $M = c / \beta + V_{bias}$  and  $K = x_1 / \gamma + V_{bias}$ , their corresponding time factors are changed to

$$1/R_1 C_1 = \alpha / (T_s \cdot x_{ms}), \tag{11}$$

$$1/R_e C_2 = \beta/(T_s \cdot y_{ms}), \tag{12}$$

$$1/R_k C_3 = (\gamma \cdot r \cdot s)/(T_s \cdot x_{ms}). \tag{13}$$

Fig. 4. Analog integrator circuit.

The rescaling factor of  $(\alpha, \beta, \gamma)$  will be 5, 6.25, and 8, respectively. The value of *L* varies from 1 V to 1.6 V, *M* is 0.875 V and *K* is 1.8 V.

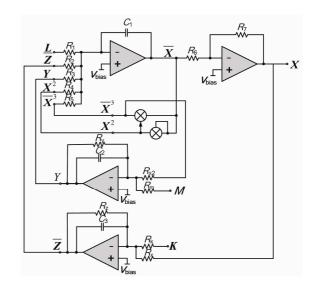

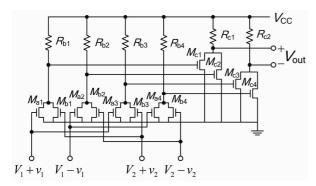

## B. CMOS neuron circuit

Fig. 5 presents the electronic neuron circuit's building blocks. Because the virtual ground voltage is now 1V, all negative voltages can be represented by a value under 1V. A signal name with a bar above it means that it is negative. Three integrators are used to produce variable (X, Y, -Z). If the capacitors are first chosen to be 1nF, the resistor values are  $R_1=165.3k\Omega$ ,  $R_2=20k\Omega$ ,  $R_3=100k\Omega$ ,  $R_{\rm m} = 618.8 {\rm k}\Omega$ ,  $R_v = 100 \mathrm{k}\Omega$ ,  $R_4=26$ k $\Omega$ ,  $R_5 = 64 \mathrm{k}\Omega$  $R_{x2}=79.8k\Omega, R_{x}=56.2k\Omega, R_{z}=222.9k\Omega, R_{k}=280.1k\Omega$ . The integrator is built using operational amplifier. Besides, additional circuit is needed to produce the square and cubic term of X signal [11]. In order to minimize on-chip area, resistors can be achieved by MOS resistors. The

Fig. 5. CMOS neuron circuit.

**Fig. 6**. Simulation results of electronic neuron with different input *L*.

Fig. 7. Phase plane of simulation results of X and Y.

Fig. 8. Square and cubic generator.

Fig. 9. Multiplier circuit.

simulation result in Fig. 6 verifies that the neuron burst is the same as the MATLAB simulation with time and amplitude scaling. Fig. 7 is a phase plane of Y versus X.

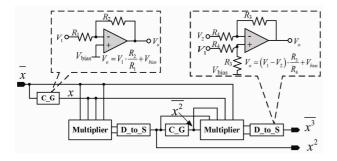

Additional circuit is required to produce square and cubic of variable x as shown in Fig. 5. The corresponding design schematic is shown in Fig. 8 with  $\bar{x}$  as the input,  $x^2$  and  $x^3$  as the outputs. Fig. 9 shows the multiplier described in [12], which is suitable for this application because it requires less area and power. However, this multiplier takes differential inputs with complementary circuits and generates differential outputs, Therefore, auxiliary blocks (complementary signal generator: C\_G and differential to single-ended converter: D\_to\_S) are necessary. Since all the transistors in the multiplier need

to work in saturation region, signal integrity is assured, but the range of the input signals and complementary ones should be constrained to make sure that the circuit operates in saturation region.

# **III. CMOS SYNAPSE CIRCUIT**

#### 1. Chemical Synapse Model

The synapse supplies the current to reshape the membrane potential of multiple electronic neurons. The bursting will be either synchronous (excitatory coupling) with depolarizing current injection or asynchronous (inhibitory coupling) with hyperpolarizing current injection. The chemical synapse model is given [13] as:

$$I = gS(t) (V_{rev} - V_{post}), \tag{6}$$

$$\frac{dS(t)}{dt} = \frac{S_{\infty} - S(t)}{\tau_{\rm S}(1 - S_{\infty})},\tag{7}$$

$$S_{\infty} = tanh\left(\frac{v_{pre} - v_{th}}{v_{slope}}\right). \tag{8}$$

where g is the maximal synaptic conductance, S(t) is instantaneous synaptic activation function,  $S_{\infty}$  is the steady-state synaptic activation,  $V_{rev}$  is the synaptic reversal potential,  $V_{pre}$  is presynaptic voltage,  $V_{post}$  is the postsynaptic voltage,  $V_{th}$  is the synaptic threshold for transmitter release,  $V_{slope}$  is the synaptic slope voltage, and  $\tau_s$  is the synaptic time constant. The current injected into the postsynaptic electronic neuron is always hyperpolarizing for excitatory synapses, which is the same as biological synapses. Similar to neuron circuit, both inputs and outputs of synapse circuit are implemented in voltage mode so as to communicate with voltage-mode electronic neuron circuit.

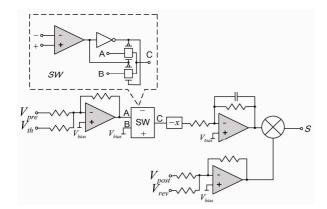

#### 2. CMOS Synapse Circuit Implementation

Fig. 10 shows the CMOS implementation of the synapse circuit. Since the maximum input amplitude to the hyperbolic tangent function is small, a simple linearization of the hyperbolic tangent function is a reasonable approximation to simplify the circuit. A multiplier is required to modulate the integrator output either above the virtual ground in excitatory synapses or below the virtual ground in inhibitory synapses.

Fig. 10. CMOS synapse circuit.

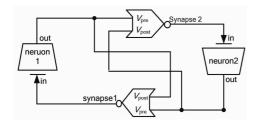

Fig. 11. Neuron oscillator diagram.

# **IV. EXCITATORY NEURON OSCILLATOR**

The proposed neuronal oscillator is shown in Fig. 11; this circuit verifies the operation of the excitatory neuron oscillation. The two synapses are identical ones and so are the two neurons. Due to the excitatory synapses employed, outputs of two electronic neurons are synchronized.

# **V. MEASUREMENT RESULTS**

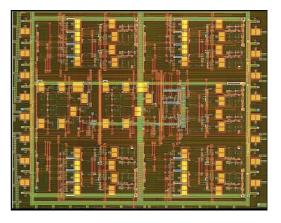

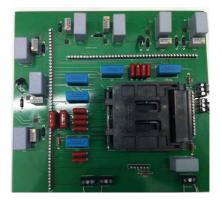

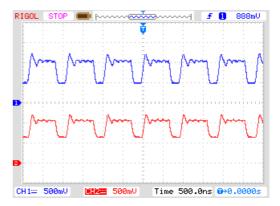

Excitatory CMOS neuron oscillator was designed and fabricated using standard CMOS 0.18um process. Fig. 12 shows the microphotograph of the test chip. There are two oscillators integrated on the chip. Biasing circuit and buffer are included for internal signal probing for test. All the circuit takes an active die area of 1.1 mm<sup>2</sup>. Fig. 13 depicts the testing printed circuit board. The black socket holds the test chip and is surrounded by external capacitors. Discrete LDOs generate individual voltages for neuron circuit. Excitatory CMOS neuron oscillator outputs are shown in Fig. 14. They show amplitude of about 500 mV, and a period of 1us. The waveforms are in accordance with the simulation results, which are one

Fig. 12. Die photo of the CMOS neuron.

Fig. 13. PCB test board of the excitatory CMOS neuron oscillator.

Fig. 14. Experimental results of excitatory CMOS neuron oscillator.

burst, followed by one silent period and fully synchronized with each other. The variation of the experiment results shows the dependency of the CMOS neuron circuit on the process, which needs further improvements.

## **VI.** CONCLUSIONS

An analog integrated circuit of excitatory neuron oscillator operating at 1.8V power supply is designed and verified using 0.18 um CMOS technology. Due to the constraint of supply rail and on-chip passive components, new scaling factors were adopted. Simulation results show that the CMOS technology implementation of HR neuron and chemical synapse models closely follows the desired models. All the circuits along with auxiliary circuits take active die area of 1.1 mm<sup>2</sup> using standard 0.18 um CMOS technology. The experiment results validate the excitatory neuron oscillator output, which is a solid part in the overall motion control unit design. This approach can be a good reference for the future low power CMOS nervous system design.

## **ACKNOWLEDGMENTS**

We acknowledge Inseok Jung's kind help for the support in setting up the simulation environment and other software assistant. This work was supported by US National Science Foundation under grant CBET-0943345.

## REFERENCES

- R. Brooks, "New approaches to Robotics," Science 253, pp. 1227-1232, 1991.

- [2] J. Ayers, J. Davis, and A. Rudolph, "Neurotechnology for biomimetic robots," MIT press, 2002.

- [3] N. Kato, J. Ayers, H. Morikawa, "Chapter 13: Architectures for adaptive behavior in biomimetic underwater robots," Bio-mechanisms of Swimming and Flying, Springer-Verlag, pp. 171-187, 2002.

- [4] http://www.cyberplasm.net.

- [5] J. Lu, J. Yang, Y. B. Kim, J. Ayers, "Low power high PVT variation tolerant central pattern generator design for a bio-bybrid micro robot," 2012 IEEE International Midwest Symposium on Circuits and Systems (MWCAS 2012), Aug. 2012, Boise Idaho, pp. 782-785.

- [6] E. Izhikevich, "Which model to use for cortical spiking neurons? In Neural Networks," IEEE Transactions on Neural Networks, vol. 15, Issue 5, pp. 1063-1070, 2004.

- [7] J. L. Hindmarsh and R. M. Rose, "A model of neuronal bursting using three coupled first order differential equations," Proc. Of the Royal Society of London, 1094, pp. 87-102.

- [8] J. Lee, Y. J. Lee, K. Kim, Y. B. Kim, and J. Ayers, "Low Power CMOS Adaptive Electronic Central Pattern Generator Design for a Biomimetic Robot." Neuroncomputing, 2007, 71:284-296.

- [9] R. D. Pinto, P. Varona, A. R. Volkovskii, et.al. "Synchronous behavior of two coupled electronic neurons," Physical Review E, vol. 62, No. 2, Aug. 2002, pp. 171-181.

- [10] J. J. Blum, "Introduction to analog computation," harcourt Brace Jovanovich, Inc., 1969.

- [11] S. Hsiao and C. Wu. "A parallel structure for CMOS four-quadrant analog multipliers and its application to a 2-GHz RF downconversion mixer," IEEE Journal of Solid State Circuits, vol. 33, Jun. 1998, pp. 859-869.

- [12] S. Hsiao and C. Wu. "A parallel structure for CMOS four-quadrant analog multipliers and its application to a 2-GHz RF down conversion mixer," IEEE Journal of Solid State Circuits, vol. 33, Jun. 1998, pp. 859-869.

- [13] R. D. Pinto, P. Varona, A. R. Volkovskii, et. al. "synchronoous behavior of two coupled electronic neurons," Physical Review E, vol. 62, No. 2, Aug. 2002, pp. 171-181.

**Jing Lu** received the B.S. and M.S. degree in Engineering from Zhejiang University in 2006 and 2010, respectively. Since 2010, she has been research assistant in the Department of Electrical and Computer Engineering at Northeastern University, USA.

Currently, she is a Ph.D. candidate at Northeastern University. Her research interest includes low power analog integrated circuit design.

Jing Yang received the B.S. and M.S. degree in physics from Shanghai Jiaotong University, Shanghai, China in 2003 and Northeastern University, Boston, MA in 2009 respectively. She is currently working toward the Ph.D. degree in electrical and

computer engineering at Northeastern University, Boston, MA. Her research interests include low-power highspeed analog circuit design, clock design and interconnect analysis.

Yong-Bin Kim was born in Seoul, South Korea in 1960. He received the B.S. degree in Electrical Engineering from Sogang University in Seoul. South Korea in 1982, the M.S. degree and Ph.D. both in Computer Engineering from New Jersey

Institute of Technology and Colorado State University in 1989 and 1996, respectively. From 1982 to 1987, Dr. Kim was with Electronics and Telecommunications Research Institute in South Korea as a Member of technical staff. From 1990 to 1993 he was with Intel Corp. as a Senior Design Engineer, and involved in micro-controller chip design and Intel P6 microprocessor chip design. From 1993 to 1996 he was with Hewlett Packard Co. Fort Collins, Colorado as a Member of Technical Staff, and involved in HP PA-8000 RISC microprocessor chip design. From 1996 to 1998 he was with Sun Microsystems, Palo Alto, California as an individual contributor, and involved in 1.5 GHz Ultra Sparc5 CPU chip design. From 1998 to 2000, he was an assistant professor in the Dept. of Electrical Engineering of University of Utah. He is currently Zraket Endowed Professor in the Department of Electrical and Computer Engineering at Northeastern University. His research focused on low power analog circuit design, high speed low power VLSI circuit design and methodology.

Joseph Ayers received BA, in Biology University of California, Riverside, 1970; Ph. D in Biology university of California, Santa Cruz, 1975. Postdoc in Neurophysiology, CNRS, Marseilles France 1975-1976. Postdoc in Neurophysiology, Neuro-

science Program, UCSD, 1976-1978. Academic Career: Assistant Professor of Biology, Department of Biology 1978-1984 Associate Professor of Biology, 1984-present. Director, Marine Science Center, Northeastern University, 1991-2001. Honors and Awards: Alfred E. Sloan Foundation Fellow, 1980-1982. NSF/CNRS, U.S.-France Exchange of Scientists Fellow, 1975-1976. NINCDS Postdoctoral Fellow, 1976-1978. Panel member NSF/NIH Computational Neuroscience Program, 2002. NSF computational Neuroscience Program 2004. Associate Editor; Journal of Counter Ordinance Technology.

**Kyung Ki Kim** received the B.S. and M.S. degree in electronic engineering from Yeungnam University, Kyeongsan, South Korea, in 1995 and 1997, respectively, and the Ph.D. degree in computer engineering from Northeastern University, Boston, MA in

2008. In 2008, he was a member of the technical staff with Sun Microsystems, Santa Clara, CA, where he was involved in the ROCK project. In 2009, he was a Senior Researcher with Illinois Institute of Technology, Chicago. He is currently an Assistant Professor at Daegu University, Gyeongsan, South Korea. His current research focused on nanoscale CMOS design, high-speed low-power VLSI design, analog VLSI circuit design, electronic CAD, asynchronous circuit, and nanoelectronics.