논문 2014-51-8-4

## FinFET 게이트 저항 압축 모델 개발 및 최적화

(FinFET Gate Resistance Modeling and Optimization)

이 순 철\*. 권 기 원\*\*. 김 소 영\*\*

(SoonCheol Lee, Kee-Won Kwon, and SoYoung Kim<sup>©</sup>)

요 약

본 논문에서는 실제 공정을 반영한 FinFET의 게이트 저항 압축모델을 개발하였다. 삼차원 소자 시뮬레이터 Sentaurus를 사용하여, Y-parameter 해석 방법을 적용하여 게이트 저항을 추출하여 제안하는 모델을 검증하였다. FinFET 게이트의 전기장 이 수평·수직 방향으로 형성됨을 고려하여 모델링함으로써, FinFET 게이트 저항의 비선형성을 반영하였다. 현재 제작되고 있 는 FinFET에서 게이트가 두 물질(Tungsten, TiN)로 적충된 구조일 수 있음을 고려하여, 비저항이 서로 다른 물질을 적충 시 킨 구조에 대한 압축 모델을 개발하였다. 제안하는 모델을 사용하여, 게이트의 기하학적 구조 변수 변화에 따른 게이트 저항이 최소가 되는 fin의 수를 제안하였다. BSIM-CMG에 제안하는 모델을 구현한 후, ring-oscillator를 설계하고, 게이트 저항이 고 려되지 않았을 때와 고려되었을 때의 각단의 신호지연을 회로 시뮬레이터를 통해 비교하였다.

#### Abstract

In this paper, the compact model for FinFET gate resistance is developed. Based on the FinFET geometry and material, the value of the gate resistance is extracted by Y-parameter analysis using 3D device simulator, Sentaurus. By dividing the gate resistance into horizontal and vertical components, the proposed gate resistance model captures the non-linear characteristics. The proposed compact model reflects the realistic gate structure which has two different materials (Tungsten, TiN) stacked. Using the proposed model, the number of fins for the minimum gate resistance can be proposed based on the variation of gate geometrical parameters. The proposed gate resistance model is implemented in BSIM-CMG. A ring-oscillator is designed, and its delay performance is compared with and without gate resistance.

Keywords: FinFET, 압축모델, ring oscillator, 신호지연

### I. 서 론

통신 시스템의 주파수가 높아질수록, 아날로그/RF

접수일자: 2014년05월06일, 수정일자: 2014년07월29일

수정완료: 2014년07월30일

회로의 성능 평가에 기생성분이 차지하는 비중이 커지 고 있다. 이 기생 성분들 중에 게이트 저항은 입력 임피 던스, 차단주파수(ft), 최대진동주파수(fmax), 신호지연에 영향을 주는 요소이다. 기본적으로 게이트 저항은 channel의 길이와 폭의 scaling에 의하여 값의 변화폭이 크게 된다. 기존 평판형 MOSFET의 경우, 압축모델인 Berkeley Short-channel IGFET Model (BSIM)[1]과 PennState Philips (PSP)<sup>[2]</sup>에 게이트 저항이 모델링되어 있지만, 소자가 점점 scaling-down화 되면서 발생하는 단채널 효과(Short Channel Effect)나 DIBL(Drain induced Barrier Lowering)등의 악화현상을 극복하기 위한 대안으로 각광받고 있는 FinFET<sup>[3~5]</sup>은 두 압축모 델에 반영되어 있지 않다. PSP에 구현된 평판형

학생회원, \*\* 정회원, 성균관대학교 정보통신대학 (College of Information and Communication Engineering, Sungkyunkwan University)

$<sup>^{\</sup>odot}$  Corresponding Author(E-mail: ksyoung@skku.edu)

<sup>※</sup> 본 연구는 지식경제부 및 한국산업기술평가관리원 의 산업원천기술개발사업(정보통신)의 일환으로 수 행하였음.[10039174, 22nm급 이하 파운드리 소자 및 PDK 기술 개발]

<sup>※</sup> 본 논문은 IDEC CAD Tool 지원을 받아 수행된 것

MOSFET의 게이트 저항 모델은 식(1)과 같다.

$$R_g = \frac{\rho}{NF} \cdot \left[ \frac{1}{3} \cdot \frac{W}{NGCON \cdot L \cdot T} + \frac{T}{L \cdot W} \right] \tag{1}$$

$\rho$ 는 게이트의 비저항이며, 게이트의 기하학적 구조를 결정하는 변수인 폭(W), 두께(T), 길이(L)에 대한 함수로 모델링 되어있다. NF는 finger의 수, NGCON은 contact이 게이트의 윗면 한쪽 끝부분에 위치한 single sided contact 또는 양쪽 끝부분에 위치한 double sided contact을 뜻하며, single sided의 경우 1, double sided의 경우 4로 설정된다. 1/3은 distributed gate coefficient <sup>[6]</sup> 로서, 일반 도선과 같이 전기장이 수평방향으로만 형성될 경우 1로 근사 할 수 있지만, MOSFET의 게이트와 같이 전기장이 수평·수직 방향으로 형성이되면 1/3로 근사 할 수 있다.

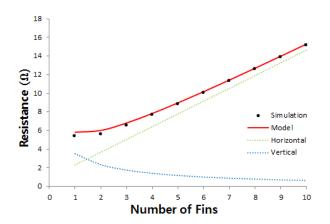

BSIM의 모델은  $R_g$ 는 W의 증가에 따라 단순 선형 성을 띄는데 비해, PSP의 모델은 그림 1과 같이 저항성

그림 1. 수평과 수직 방향의 전류 흐름에 따른 저항성 분

Fig. 1. Resistance components of horizontal and vertical direction

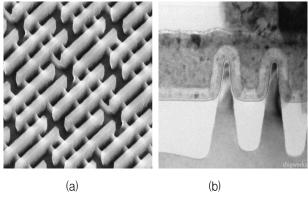

그림 2. (a) Intel 22 nm급 FinFET SEM사진<sup>(8)</sup> (b) 게이트 단면도의 TEM사진<sup>(9)</sup>

Fig. 2. (a) A tilted SEM picture of Intel 22 nm FinFET (b) TEM picture for cross-section of gate.

분을 수평 방향과 수직 방향으로 나누어 다항식으로 표현함으로써, 비선형성을 띄는 게이트 저항 특성을 보다정확성 있게 구현하였다. 반면, multi-gate FET의 압축모델인 BSIM-CMG<sup>[7]</sup>에는 fin의 수에 비례하는 선형증가로  $R_g$ 가 간략히 모델화 되어 있지만, 사용자가  $R_g$ 의 값을 설정해 주어야 하며, 비선형성을 띄는 실제 게이트 저항 특성을 반영하지 못한다. 그러므로, PSP의 모델과 같이 실제 비선형 특성을 가지고, FinFET의 기하학적 구조를 반영한 새로운 게이트 저항 모델을 필요로하며, 본 논문에서는 실제공정 구조를 반영한 압축모델을 제안한다.

그림 2의 (a)는 본 연구에서 해석할 multi-fin구조를 보여주고, (b)는 게이트의 단면구조를 보여주고, fin과 oxide위에 metal 게이트가 형성되어 있고, 그 위에 tungsten을 적층시킨 구조이다. Metal 게이트와 tungsten은 각각 poly-Si과 silicide로 대체될 수도 있는 데, 공정 기술마다 제각각 다른 물질을 사용 한다는 것 을 반영하여, 비저항이 서로 다른 물질1과 물질2로 간주 하여, 시뮬레이션 및 모델링을 진행 하였다.

Synopsys 社의 삼차원 소자 시뮬레이터 Sentaurus [10]를 이용하여 시뮬레이션 하였고, Y-파라미터 해석을 통해, FinFET 게이트의 기하학적 변수 변화에 따른 저항값을 추출하였다[11~13]. 본 논문에서 제안하는 게이트저항의 압축모델을 Verilog-A를 통해, BSIM-CMG에구현 후, ring-oscillator를 설계하여, inverter의 신호지연을 분석하였다. 게이트 저항이 고려되었을 때, 신호지연의 변화를 파악하고, 게이트의 기하학적 변수 변화에따른, 신호지연이 최적화 되는 fin의 수를 제안한다.

# II. 게이트 구조 및 Y-parameter Analysis를이용한 저항 추출

게이트와 channel사이에 위치한 oxide는 절연체 역할을 하고 있기 때문에 DC측정을 통해서는 게이트의 저항값을 추출하기 불가능하다. 이러한 점을 고려하여, AC 측정방법인 주파수에 따른 Y-파라미터 해석을 적용시켜 게이트저항을 추출하기로 한다.

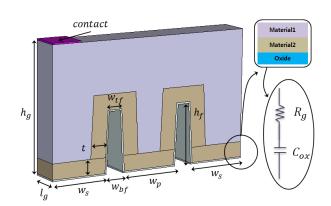

본 논문에서는 Intel 22 nm 급 FinFET의 구조를 반영하였고, 모델링을 위한 기하학적 변수들은 그림 3에 도시 되었으며, 게이트를  $R_g$ 와  $C_{ox}$ 의 직렬로 등가모델화 하여 Y-파라미터 해석을 통해 식(2)와 식(3)을 거쳐

그림 3. 시뮬레이션에 사용한 gate 구조

Fig. 3. Gate structure for simulation.

표 1. 시뮬레이션에 사용된 표준 변수 값 Table 1. standard parameter value for simulation.

| parameter | Value | Parameter | Value |

|-----------|-------|-----------|-------|

| $h_g$     | 84 nm | $w_{tf}$  | 8 nm  |

| $h_f$     | 40 nm | $w_{bf}$  | 12 nm |

| $w_s$     | 47 nm | t         | 10 nm |

46 nm

$w_p$

$l_g$

20 nm

그림 4. Y-parameter analysis를 이용한 Gate 저항 추출 결과

**Number of Fins**

Fig. 4. Gate resistance extraction results using Y-parameter analysis.

최종적인 게이트 저항값을 추출하였다.

$$Y_{11} \cong \omega^2 C_{ox}^2 R_g + j\omega C_{ox} \tag{2}$$

$$R_g = \frac{Re\{Y_{11}\}}{Im\{Y_{11}\}^2} \tag{3}$$

시뮬레이션에 사용된 FinFET 구조에 대한 변수들은

표 1에 표기된 바와 같고, 그림 3에 보인 물질1은 tungsten을 물질2는 TiN(Titanium Nitride)을 사용하였다. Tungsten과 TiN의 비저항은 각각  $\rho_1$ 과  $\rho_2$ 로 정의하고 값은  $5.7~\mu\Omega\cdot cm$ ,  $30~\mu\Omega\cdot cm$  이다. 표 1의 변수에 대한 FinFET 구조의 게이트 저항은 그림 4와 같다. fin의 수가 증가할수록 점점 선형성을 띄는 것을 볼 수있는데, 평판형 MOSFET에서 게이트의 폭이 증가할때와 유사한 경항을 가진다.

# III. 실제 공정을 고려한 FinFET Gate 저항 모델링 및 검증, 분석

그림 3에 나타낸 것처럼, FinFET의 구조에서는 effective channel width에 관계된 변수 외에도, fin과 fin사이의 길이, fin의 높이 등 평판형 MOSFET보다 더욱 많은 기하학적 변수들이 정의된다. 본 연구에서는, 실제 공정에서처럼 FinFET 게이트가 두 물질로 적 충된 구조를 반영하고, 게이트 저항의 비선형성을 만족시키기 위해, 수평과 수직 방향으로 나누어 모델링하되, 전류의 확산이 하나의 물질만을 통과하는 경우와두 물질이 적충된 부분을 통과하는 경우로 분할하여근사 모델링을 진행 하였다. 게이트 contact의 폭은 22 nm 이며, single sided contact 기준으로 시뮬레이션 및 모델링을 하였고, PSP의 NGCON과 같은 변수를 도입하여, double sided contact일 경우의 게이트 저항을 나타내었다.

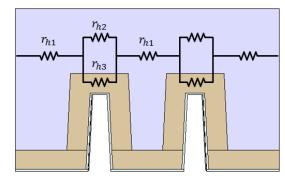

우선, 수평 성분 저항의 등가모델은 그림 5와 같다. 수평 성분 저항의 단면적은 fin의 높이가 변해도 영향 을 받지 않는다는 것이, 본 논문이 제안하는 모델링의

그림 5. 수평 저항 성분의 등가모델

Fig. 5. Equivalent circuit model of horizontal resistance component.

중요한 특징으로서, 전체 게이트에서 fin의 높이를 제외한 부분, 즉,  $(h_g-h_f)$ 과 게이트 길이 $(l_g)$ 의 곱으로 단면적을 나타낼 수 있다. 그림 5에 저항을 표시한 것처럼, 전류의 확산이 물질 $_1$ 만을 통과하는 경우 $(r_{h1})$ 를 식(4)로 나타내었고, 물질 $_1$ 과 물질 $_2$ 가 적충된 부분 $(r_{h2},r_{h3})$ 에 대한 경우를 식(5)와 식(6)으로 나타내어 병렬계산한 후,  $r_{h1}$ 과의 직렬 연결을 통해 최종적인 수평저항을 식(7)과 같이 근사 하였다.

$$r_{h1} = \frac{k+\beta-2w_f}{(h_g-h_f)} \cdot \frac{\rho_1}{3 \cdot l_g} \tag{4} \label{eq:final_relation}$$

$$r_{h2} = \left(\frac{\alpha \cdot n}{h_g - (h_f + t)} + \frac{2w_f \cdot n}{h_g - (h_f + t/2)}\right) \cdot \frac{\rho_1}{3 \cdot l_g} \quad (5)$$

$$r_{h3} = \left(\frac{\alpha \cdot n}{t} + \frac{2w_f \cdot n}{t/2}\right) \cdot \frac{\rho_2}{3 \cdot l_q} \tag{6}$$

$$R_h = r_{h1} + (r_{h2} || r_{h3}) \tag{7}$$

식(4)~식(6)의 n은 fin의 수를 의미하며,  $\alpha$ ,  $\beta$ ,  $\gamma$ , k,  $w_f$ 는 길이의 단위를 가지고 각 모델링에 공통으로 포함된 부분을 함축하여 나타내기 위해, 아래와 같이 식(8)~식(12)과 같다. 이 변수들은 수직 저항 성분의 모델링에도 사용된다.

$$\alpha = 2(t + ox) + w_{tf} \tag{8}$$

$$\beta = (n-1)(w_n + 2ox + w_{bf}) + (1-n)\alpha \tag{9}$$

$$\gamma = 2(w_s + ox) + n \cdot w_{bf} + (n-1)(w_n + 2ox) \quad (10)$$

$$k = 2(w_s + ox) + w_{bf} - \alpha$$

(11)

$$w_f = w_{bf} - w_{tf} \tag{12}$$

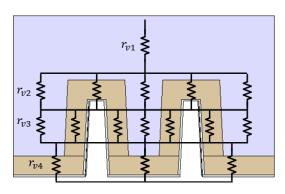

수직 성분 저항의 등가모델은 그림 6과 같다. 수평 저항 성분과 마찬가지로, n은 fin의 수를 의미한다. 수직 저항 성분은 fin의 폭으로 인한 단면적 손실을 고려해야 함으로써, 더욱 분할하여 모델링할 필요성이 있다. 그림 6에 저항을 표시한 것처럼, 전류의 확산이 하나의물질만을 통과하는 경우 $(r_{v1},\ r_{v4})$ 를 식(13)과 식(16)으

그림 6. 수직 저항 성분의 등가모델

Fig. 6. Equivalent circuit model of vertical resistance component.

로, 물질 $_1$ 과 물질 $_2$ 가 적충된 부분 $(r_{v2}, r_{v3})$ 에 대한 경우를 식(14)와 식(15)로 표현하고, 분할하여 구한 각각의 수직 성분들을 식(17)과 같이 직렬 연결하여, 수직 저항을 근사 모델화 할 수 있다.

$$r_{v1} = \frac{h_g - (h_f + t)}{\gamma} \cdot \frac{\rho_1}{l_g} \tag{13}$$

$$r_{v2} = \left(\frac{t \cdot \rho_1}{k \cdot l_g} \| \frac{t \cdot \rho_2}{\alpha \cdot n \cdot l_g} \| \frac{t \cdot \rho_1}{\beta \cdot l_g} \right) \tag{14}$$

$$r_{v3} = \left(\frac{(h_f - t)\rho_1}{k \cdot l_g} \| \frac{(h_f - t)\rho_2}{2n \cdot t \cdot l_g} \| \frac{(h_f - t)\rho_2}{\beta \cdot l_g} \right) \quad (15)$$

$$r_{v4} = \left(\frac{t}{(k+2t)} \parallel \frac{t}{(\beta+2t)(n-1)}\right) \cdot \frac{\rho_2}{l_g} \tag{16}$$

$$R_v = r_{v1} + r_{v2} + r_{v3} + r_{v4} (17)$$

Single sided contact일 경우의 최종적인 게이트 저항은 식(18)과 같이 수평 저항과 수직 저항의 합으로 나타내어 비선형성을 만족시켰다.

$$R_{q(s)} = R_h + R_v \tag{18}$$

그림 7은 시뮬레이션과 제안하는 모델의 결과를 비교한 그래프로, 모델의 값은 수평, 수직방향의 합을 나타낸다. 그림 7의 결과를 보면 상대적으로 적은 fin의 개수에서 큰 오차가 발생한다. 이유는, 게이트의 contact 폭에따라 저항값이 변하기 때문인데, 다수의 fin으로 확장시킬수록, contact 폭의 영향에 둔감해져서 게이트 저항의

그림 7. 제안한 모델과 시뮬레이션(Sentaurus) 결과 비교

Fig. 7. Comparison of the proposed model and simulation.

변화가 거의 발생하지 않는다. 통상적으로, 충분한 effective channel width를 확보하기 위해 2~3 fin 이상을 사용한다는 것을 감안하면, Sentaurus 시뮬레이션 결과와 매우 잘 일치함을 보여주고 있다. 물론, 6~7 fin 이상을 사용한다면, 그림 7의 초록색 점선과 같이 수평성분의 모델만을 사용해도 10% 이내의 오차를 유지할 수있지만, 그 이하의 fin을 사용 하였을 때, 정확도를 향상시키기 위해서는 수직성분의 모델을 함께 고려해 주어야 한다. 즉, 소수의 fin에서는 수평・수직 저항의 비중

이 비슷하지만, 다수의 fin에서는 수직 저항의 비중이 점점 줄어들어 수평 저항이 게이트 저항의 값을 거의 지배한다.

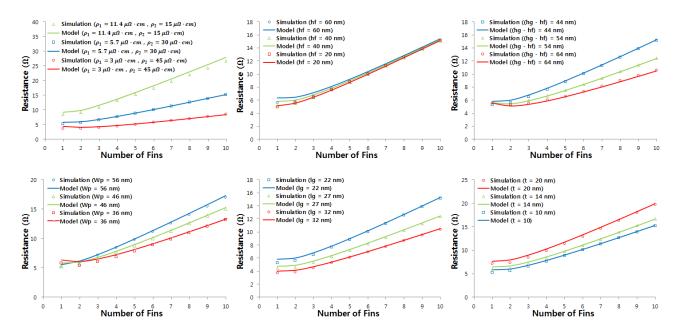

그림 8은 비저항 및 여러 변수들의 변화에 따른 시뮬 레이션과 제안하는 모델의 비교 결과를 보여주고 있다. 앞서, 공정 기술에 따라 비저항이 다른 물질이 사용될 수 있음을 언급 하였는데, 실제 공정 $(\rho_1 < \rho_2)$ 의 조건하 에, 비저항을 변화시켜도 시뮬레이션과의 오차는 7%를 넘지 않았다.  $H_t$ 와 수직 저항의 비례관계에 따라,  $H_t$ 의 변화는 소수의 fin에서 영향이 크지만, 다수의 fin으로 확장시킬수록 최종적인 게이트 저항의 변화가 미미해짐 을 보여주며, 모델과 시뮬레이션 값이 거의 일치한다. 반 면,  $w_p$ 와  $(h_q - h_f)$ 의 변화는 각각 수평 저항의 길이와 단면적에 비례함으로, 소수의 fin보다는 다수의 fin에서 게이트 저항의 변화가 뚜렷한데, 모델은 이런 현상을 잘 반영하여 시뮬레이션의 결과를 잘 따르고 있다. 그 외에 도, 단면적에 영향을 주어, 게이트 저항과 반비례관계를 형성하는  $l_a$ 와, 물질 $_2$ 의 적층높이(t)를 변화시킨 결과 역 시, 시뮬레이션 값과 잘 일치하며, 그림 8의 모든 결과는 최대 7% 이내의 오차를 보였다.

Gate contact이 양쪽에 위치한 double sided contact 의 경우는 게이트의 폭에 관계된 변수 $(w_s,\ w_p,\ w_f)$ 들을 2등분하여, 그 두개를 병렬 연결한 것으로 정의 될

그림 8. Geometrical parameter의 변화에 따른 Sentaurus 시뮬레이션 결과와 모델의 결과 비교

Fig. 8. Simulation and model comparison depending on the change of geometrical parameters.

그림 9. (a) Double sided contact 구조 (b) Single sided contact과 double sided contact의 모델 및 시뮬레이션 결과 비교

Fig. 9. (a) Geometry for double sided contact (b) Comparing model with simulation for single and double sided contact.

수 있는데, 식(19)와 같이 간단히 정리될 수 있다.

$$R_{g(d)} = R_{g(s)}(\frac{w_s}{2}, \frac{w_p}{2}, \frac{w_f}{2}) \cdot \frac{1}{2} = \frac{R_h}{4} + R_v$$

(19)

그림 9는 double sided contact에 대한 시뮬레이션과 모델의 비교 결과로서, 같은 기하학적 변수를 가지더라 도 contact을 single sided 또는 double sided로 선택함에 따라, 게이트 저항이 최소가 되는 fin의 수는 달라짐을 보여주고 있다. 표 1의 구조에 대해서는, single sided contact일 경우, 1-fin에서 게이트저항이 최소가 되고, double sided contact일 경우는 3-fin에서 최소가 됨을 알 수 있다.

### IV. Gate Resistance를 고려한 delay 분석

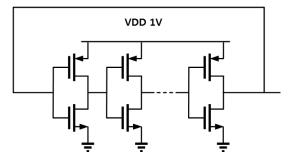

Verilog-A를 이용하여, BSIM-CMG에 내재된 게이트 저항 모델을 본 논문에서 제안하는 모델로 수정 한 후, ring-oscillator를 설계하고, 게이트 저항이 고려되지 않 았을 때와 고려되었을 때의 inverter 신호지연을 회로 시뮬레이터인 Hspice를 통해 측정 비교 하였다.

그림 10은 게이트 저항이 신호지연에 미치는 영향을 분석하기 위해, BSIM-CMG로 구현한 17단 ring-oscillator 회로도이다. Inverter 첫 번째 단과 마지막 단의 input rising이 50%가 될 때의 시간을 측정하여, 그차를 구한 후, ring-oscillator에 사용된 inverter의 수를 나누어, 단일 inverter의 평균 propagation delay를 구하였다. Delay에 영향을 미치는 intrinsic/fringing 커패시턴스, 소스/드레인 저항 등의 기생성분은 기존의 BSIM-CMG에 내재되어진 모델이 사용되었다.

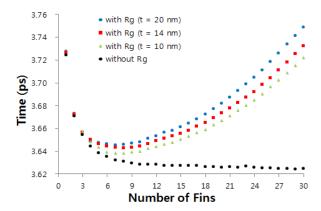

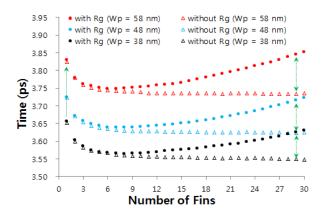

그림 11은 게이트 저항이 고려되기 전과 고려된 후의 결과를 보여주고 있다. 동일한 effective channel width

그림 10. 17단 링 오실레이터 회로도

Fig. 10. A schematic of 17-stage ring-oscillator.

그림 11. 단일 Inverter의 propagation delay

Fig. 11. Propagation delay of sole inverter using BSIM-CMG.

와 intrinsic/fringing 커패시턴스 값이 사용되기 위해, 전 체적인 게이트의 구조를 물질2의 두께(t)만을 변화시켜 비교하였다. Fin수의 증가는 effective channel width의 증가를 의미 하므로, 소스/드레인 저항은 fin수와 병렬관 계를 형성하여 반비례 관계를 띄게 되고, 반대로, intrinsic/fringing 커페시턴스는 직렬관계를 형성하여 fin수에 비례 하게 된다. 그림 11에 보여진바와 같이, 게 이트 저항이 고려되지 않았을 경우, fin의 수가 늘어나면 서 소스/드레인 저항이 감소하고 전류가 늘어남에 따라 신호지연는 감소한다. 하지만, 다수의 fin이 사용되면서 커패시턴스의 영향이 상대적으로 소스/드레인 저항 보 다 커지게 되고, 신호지연의 감소폭이 점점 줄어들면서 신호지연 값이 거의 일정하게 된다. 여기에 게이트 저항 을 추가하여 고려하면, 다수의 fin이 사용될 경우, 오히 려 신호지연가 점점 증가하는 경향을 띄게 되어, 신호지 연가 최소값을 가지게 되는 fin의 수를 추적할 수 있다. 표 1의 구조에 대해서 게이트 저항이 고려될 경우, 신호 지연은 7-fin에서 최소가 되었다.

그림 12는 fin과 fin사이의 거리 $(w_p)$ 를 변화시켰을 때의, 신호지연 비교 결과이다. Intrinsic 커패시턴스와 소스/드레인 저항은  $w_p$ 와 무관하지만, fringing 커패시턴스와 게이트 저항은  $w_p$ 와 비례관계를 가진다. 그래 프에서도 보여 지듯이,  $w_p$ 의 증가는 fringing 커패시턴스와 게이트 저항의 증가를 초래하여, 1-fin에서도 신호지연가 상승함을 확인 할 수 있고, 그림 11의 결과와 마찬가지로 fin의 수가 점점 증가함에 따라 신호지연은

그림 12.  $w_p$ 의 변화에 따른 단일 Inverter의 propagation delay

Fig. 12. Propagation delay of sole inverter depending on variation of  $\boldsymbol{w}_{p}$ .

감소하다가 증가하는 경향을 보인다. 단,  $w_p$ 가 증가할 수록 게이트 저항이 증가하는 것처럼, 다수의 fin에서 신호지연의 증가폭도 점점 커지게 된다.

본 논문에서 제안하는 게이트 저항 모델식을 추가하여 고려한 것만으로, inverter의 propagation delay 경향성이 바뀌는 것을 확인 할 수 있고, 신호지연이 최소가되는 fin의 수를 예측 가능하게 된다.

### Ⅴ. 결 론

본 논문에서는, FinFET의 기하학적 구조에 맞는 게 이트 저항의 압축 모델 개발을 위해, Intel 22 nm 급 FinFET의 구조와 물질을 반영하여, 실제 공정과 일치 하는 게이트 저항의 압축 모델을 제안 하였다. 게이트 저항의 추출을 위해 삼차원 소자 시뮬레이터 Sentaurus 사용하였고, Y-파라미터 해석을 적용하였다. FinFET 게이트의 전기장이 수평·수직 방향으로 형성됨 을 고려하여, 저항성분 또한 수평·수직 방향으로 나누 어 모델링함으로써, FinFET 게이트 저항의 비선형성을 만족하였다. 또한, Intel 22 nm 급 FinFET처럼 게이트 가 두 물질(Tungsten, TiN)로 적층된 구조일 수 있음 을 고려하여, 비저항이 서로 다른 물질을 적층 시킨 구 조에 대한 FinFET 게이트 압축 모델을 개발하였다. Fitting coefficient 없이, 전류의 확산이 하나의 물질을 통과하는 경우와 두 물질이 적층된 부분을 통과하는 경 우로 분할하여 근사 모델링하는 것만으로도, 최대오차 는 7%이내를 만족하였고, 개발한 모델을 사용하여, 게 이트의 기하학적 구조 변수 변화에 따른 게이트 저항이 최소가 되는 fin의 수를 파악 할 수 있게 되었다.

본 논문이 제안하는 방법과 같이, 저항을 수평·수직 방향으로 나누되, 전류의 확산과 물질의 적층 관계를 고려하여 분할한다면, Intel 22 nm 급 FinFET 게이트 와는 다른 적층 구조에 대해서도 모델링이 가능하고, 아울러, 두 물질이 적층된 구조뿐만이 아닌, 세 물질 이 상이 적층된 게이트 구조에 대해서도 비선형성을 만족 하는 모델링이 가능하다.

Verilog-A를 이용하여, BSIM-CMG에 내재된 게이트 저항 모델을 본 논문에서 제안하는 모델로 수정 한 후, ring-oscillator를 설계하고, 게이트 저항이 고려되지 않 았을 때와 고려되었을 때의 inverter의 신호지연을 회로 시뮬레이터 Hspice를 통해 측정 비교 하였다. 게이트 저 항 모델을 추가하여 고려한 것만으로, 단일 inverter의 신호지연 경향성이 바뀌는 것을 확인 할 수 있었고, 신 호지연이 최소가 되는 fin의 수를 예측 가능하게 되었다. 제안한 모델은 게이트 저항에 민감한 고주파 회로의 설 계의 정확도를 높이는데 사용될 수 있을 것이다.

#### REFERENCES

- [1] BSIM4v4.7 MOSFET Model User's Manual, 2011.

- [2] PSP 103.1 Reference Manual, 2009.

- [3] K. W. Lee, SeokSoon Noh, NaHyun Kim, KeeWon Kwon, and SoYoung Kim, "Comparative study of analog performance of multiple fin tri-gate FinFETs," International Conference on Electronics, Information and Communication, 2012.

- [4] W. Yang and J. G. Fossum, "On the feasibility of nanoscale triple gate CMOS transistors," IEEE Trans. Electron Devices, vol. 52, no. 6, pp. 1159–1164, Jun. 2005.

- [5] SeokSoon Noh, Kee-Won Kwon, SoYoung Kim, "Analysis of Process and Layout Dependent Analog Performance of FinFET Structures using 3D Device Simulator," Journal of the Institute of Electronics Engineers of Korea, vol. 50, no. 4,

- pp. 35-42, April, 2013.

- [6] B. Razavi, R.-H. Yan, and K. F. Lee, "Impact of distributed gate resistance on the performance of MOS devices," IEEE Trans. Circuit Syst., vol. 41, no. 11, pp. 750-754, Nov 1994.

- [7] BSIM-CMG 107.0.0 Multi-Gate MOSFET Compact Model Technical Manual, 2013.

- [8] Chris Auth, "22-nm Fully-Depleted Tri-Gate CMOS Transistors," IEEE. CICC, Sept 2012.

- [9] Dick James, "Intel Ivy Bridge Unveiled-The First Commercial Tri-Gate, High-k, Metal-Gate CPU." IEEE. CICC, Sept 2012.

- [10] Synopsys Sentaurus Device User Guide Ver.E–2010.12.

- [11] C. Enz and Y. Cheng, "MOS Transistor modeling for RF IC Design," IEEE Trans. Solid-State Circuits, vol. 35, no. 2, pp. 186-201, Feb 2000.

- [12] Y. Cheng, and M. Matloubian, "High Frequency Characterization of Gate Resistance in RF MOSFETs," IEEE Electron Devices. Letters, vol. 22, no. 2, pp. 98–100, Feb. 2001.

- [13] In-Man Kang, "Analyses for RF parameters of Tunneling FETs," Journal of the Institute of Electronics Engineers of Korea, vol. 49, no. 4, pp. 143–147, April, 2012.

저 자 소 개

이 순 철(학생회원) 2012년 경상대학교 전자공학과 졸업 2012년~현재 성균관대학교 정보통신대학 석사과정 <주관심분야: Device Simulation and Modeling>

권 기 원(정회원)

2001년 Stanford University

재료공학과 박사 졸업.

2001년~2006년 삼성전자(주)

DRAM개발실 수석연구원

2007년~현재 성균관대학교

정보통신대학 부교수

<주관심분야 : 메모리IP, 아날로그/디지털 Mixed mode 설계>

김 소 영(정회원)-교신저자 1997년 서울대학교 전기공학부 학사 졸업. 1999년 Stanford University 전기공학과 석사 졸업. 2004년 Stanford University 전기공학과 박사 졸업.

2004년~2008년 Intel Corporation 2008년~2009년 Cadence Design Systems 2009년~현재 성균관대학교 정보통신대학 반도체시스템공학과 부교수