J. Adv. Navig. Technol. 18(3): 229-235, Jun. 2014

## 아날로그 전치왜곡기를 이용한 고효율 전력증폭기

# High Efficiency Power Amplifier using Analog Predistorter

최 장 헌<sup>1</sup>·김 영<sup>1\*</sup>·윤 영 철<sup>2</sup>

## Jang-hun Choi<sup>1</sup> · Young Kim<sup>1\*</sup> · Young-Chul Yoon<sup>2</sup>

<sup>1</sup>Department of Electronic Engineering, Kumoh National Institute of Technology, Gyungsangbuk-do, 730-701, Korea

## [요 약]

본 논문은 고효율 고선형 특성을 얻기 위하여 신테라사가 제공한 디지털로 제어되는 아날로그 전치왜곡 칩을 이용한 도허티 전력증폭기를 설계하였다. 여기서 사용된 아날로그 전치왜곡기는 입력과 출력신호를 비교하여 출력의 혼변조 신호 특성을 개선하기 위하여 입력 신호의 크기와 위상을 조절함으로서 선형성을 개선시켰다. 또한, 도허티 전력증폭기를 설계하여 이용함으로써 고효율의 특성을 얻었다. 제작된 전력증폭기는 중심주파수 2150 MHz에서 평형증폭기와 비교하여 11% 이상의 효율 개선 효과와 출력 전력 100W 이하에서 인접채널 전력을 15 dB 이상 개선시켰다.

## [Abstract]

This paper presents the Doherty power amplifier with a digitally controlled analog predistorter circuit of Scintera Corp. to produce high power efficiency and high linearity performance. The analog predistorter improves the linearity performance because of controlling amplitude and phase values of input signal in order to improve intermodulation performance of power amplifier. Also, the power amplifier is designed by the Doherty technology to obtain the high efficiency performance. To validate the Scintera's analog predistorter, we are implemented the power amplifier with Doherty method at center frequency 2150 MHz. Compared with the balanced amplifier, the power amplifier is improved above 11% enhanced efficiency and more than 15 dB ACPR improvement.

**Key word**: Analog predistorter, Doherty amplifier, Power efficiency, Linearity, Intermodulation distortion.

## http://dx.doi.org/10.12673/jant.2014.18.3.229

This is an Open Access article distributed under the terms of the Creative Commons Attribution Non-CommercialLicense(http://creativecommons

.org/licenses/by-nc/3.0/) which permits unrestricted non-commercial use, distribution, and reproduction in any medium, provided the original work is properly cited.

Received 13 May 2014; Revised 23 June 2014 Accepted (Publication) 11 June 2014(30 June 2014)

\*Corresponding Author; Young Kim

**Tel:** +82-54-478-7506 **E-mail:** youngk@kumoh.ac.kr

<sup>&</sup>lt;sup>1</sup>금오공과대학교 전자공학과

<sup>&</sup>lt;sup>2</sup>관동대학교 전자정보통신공학부

<sup>&</sup>lt;sup>2</sup>Department of Electronic Engineering, Kwandong University, Gangwon-do, 210-701, Korea

#### │. 서 론

현대 무선통신 시스템은 대역폭의 증가와 많은 데이터 처리를 요구하고 있다. 하지만, 광대역 신호를 처리하는데 있어 전력증폭기 설계는 비선형 특성을 만들어내는 메모리 효과 때문에 매우 어렵다[1]-[3]. 또한, 디지털 신호 전송에 필요한 전력 증폭기는 혼변조 신호가 존재하는 효율적인 증폭기와 혼변조 신호가 없는 비효율적인 증폭기 사이에서 선택하여야 한다[4]-[8]. 그리고, CDMA-2000, WCDMA 그리고 LTE 시스템에 사용되는 전력증폭기는 매우 높은 PAR (peak-to-average ratio)를 갖는 신호를 처리해야 한다. 기지국 전력증폭기는 왜곡이 없고 매우 높은 PAR을 갖는 신호를 선형적으로 증폭하는 것이 필요하며 이때 전력증폭기는 A 또는 AB급으로 동작시켜 신호의 피크 전력으로부터 많은 양을 백-오프하여 동작시킨다[9].

기지국 전력증폭기의 주요 요구사항중 하나는 높은 효율을 확보하는 것으로, 냉각 용량과 시스템의 크기를 줄여 운영비용을 절감하기 위해서 고효율의 전력증폭기를 요구하고 있다. 기존의 전력증폭기는 백-오프 동작에 의해서 낮은 효율을 갖고 있기 때문에 효율 증가기술은 매우 중요하다. 또한, 광대역 신호에서 높은 효율과 고선형성을 갖은 전력증폭기 설계 기술은 현재매우 중요한 이슈가 되어있다. 전력 증폭기의 효율적인동작은 배터리 사용 시간 증가와 설계비용을 감소시키지만, 증폭기의 혼변조 성분은 무선 시스템의 인접 채널에 간섭 신호를 보내는 문제를 야기 시킨다.

본 논문에서는 기지국 전력증폭기의 요구조건인 고효율과 선형성을 만족시키기 위해서, 고효율 증폭기인 도허티 증폭기로 주 증폭기를 설계하고 선형성을 개선하기 위해서 신테라사(Scintera)의 디지털로 제어되는 아날로그 전치왜곡 선형화기[10]를 사용하여 고효율, 고선형성을 갖는 증폭기에 대해서 서술할 것이다.

## Ⅱ. 본 론

여기서는 전치왜곡기의 기본 개념과 신테라사의 아날로그 전치왜곡기의 동작원리에 대해서 살펴본다.

## 2-1 전치왜곡 방식[1]

전력 증폭기는 디지털 변조된 신호의 진폭과 위상 변화에 정보를 갖고 있는 입력 신호를 증폭해주는 역할을 하는데, 증폭 기의 트랜지스터 비선형성 특성은 입력 신호의 크기와 위상을 왜곡시키게 된다.

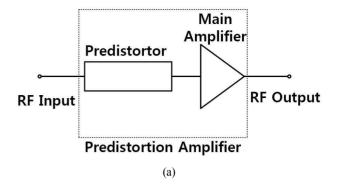

그림 1. (a) 전치왜곡기의 기본 구성도 (b) 전치왜곡기 사용 후 이득의 변화

**Fig. 1.** (a) Basic configuration of predistorter and (b) Gain variation after using predistorter.

이러한 왜곡 성분들은 전력증폭기의 스펙트럼 효율의 열화 와 출력의 왜곡으로 인하여 데이터 에러의 증가와 인접채널의 간섭을 가져온다.

전력증폭기의 출력에서 크기와 위상 왜곡을 나타내는 AM/AM과 AM/PM 왜곡은 입력 신호의 크기에 따라서 변화한다. 만일 측정이나 시뮬레이션을 통해 출력에서 나타나는 왜곡된 성분 값을 예측할 수 있다면, 전력증폭기 입력에서 정확히보상해줌으로서 출력 왜곡 현상을 상쇄할 수 있으며, 이러한 개념을 전치왜곡이라고 한다.

그림 1(a)에서 전력증폭기의 입력에 전치왜곡기를 두어 증폭기 출력 신호의 크기와 위상 변화를 예측하여 입력 신호를 미리 왜곡 시키는 방법을 나타내고 있으며, 그림 1(b)는 입력 신호가 증가하면 증폭기의 이득이 줄어드는 것을 전치왜곡기는 반대로 이득을 증가시킴으로서 사용 입력 조건에서 이득이 감소가 되는 것을 막아 높은 전력에서도 일정한 이득이 나오도록 한것이다. 이것은 전치왜곡기가 동일한 입력 전력으로 보다 높은 선형적인 출력 전력을 얻을 수 있는 것을 나타내며, 동일한 혼변조 규격을 기준으로 출력 전력이 증가함으로서 전력 증폭기의 효율을 높일 수 있음을 나타낸 것이다.

#### 2-2 신테라사의 전치왜곡기[10]

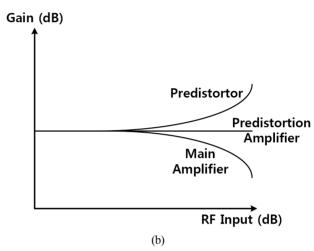

신테라사의 전치왜곡기는 전력증폭기의 비선형 성분의 출력 신호를 선형화 시키는 아날로그 전치왜곡 장치로 디지털 영역에서 처리된 신호를 이용하여 RF/아날로그 영역으로 전치왜 곡시키는 알고리즘을 이용한 것이다. 신테라 선형화 칩을 이용한 증폭기의 전체 블럭도는 그림 2에 나타냈다. 이 그림에서 보면 신테라 선형화 칩은 입력 신호와 왜곡된 출력 신호를 받아서그 신호를 비교하여 전력 증폭기의 비선형성을 개선할 수 있도록 전치왜곡 신호 처리하여 증폭기 입력 측에 넣어주는 역할을 한다.

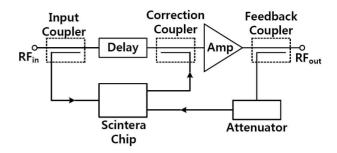

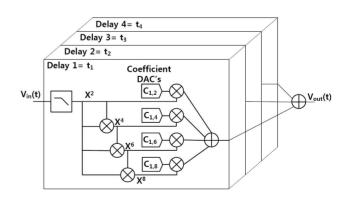

그림 3은 신테라 전치왜곡 칩 구조 및 기능 블럭도를 나타낸 것으로 먼저, 콜렉션 프로세서에서는 입력 신호를 직각 위상 변 환기를 이용하여 동 위상(I)과 직각 위상(O) 신호를 만든다. 또 한, 입력 신호는 볼테라(Volterra) 시리즈 발생기로 입력되어 입 력신호의 전력을 검출하고 이것을 이용하여 입력 신호에 따른 비선형 변환에 적용할 수 있는 짝수 항 혼변조 성분을 만들 수 있도록 이용된다. 이론적으로 볼테라 시리즈는 무한대의 보정 항을 사용할 수 있지만 비용과 실제적인 구현 때문에 네 개의 구역으로 나누어진 탭을 가진 항으로 구현하였다. 이들 탭은 혼 변조 신호의 9차 항 까지 보정할 수 있는 다항식으로 구성되어 있다. 이러한 볼테라 모델은 전력증폭기가 동작하는 주파수 범 위에서 전력증폭기의 혼변조 신호가 대칭적인 구조를 갖고 있 으며 그것의 이득이 평탄하다는 가정에서 사용된 것이다. 또 한, 이 모델은 입력되는 신호 대역폭에서 정합된 AM/AM 과 AM/PM 특성을 갖고 있으며, 전력증폭기의 제한된 메모리 효 과와 일정한 AM/AM 과 AM/PM 의 리플과 변화량을 갖고 있 다는 가정 아래에서 동작되도록 설계된 것이다. 또, 그림 4는 콜렉션 프로세서에 존재하는 볼테라 시리즈 발생기의 블록도 로서 전력증폭기가 갖고 있는 메모리 효과를 보상하기 위해서 0 에서 300 nsec까지의 지연 범위에서 서로 계수가 다른 볼테라 시리즈 발생기 네 개를 만들어 메모리 효과를 보상하도록 하는 블럭도를 나타낸 것이다. 여기서 사용되는 계수들은 전력증폭 기의 혼변조 신호를 개선하기 위한 적응 알고리즘 의해서 디지 털 신호처리기에서 개별적으로 만들어지고 제어된다. 디지털 제어기 메모리의 각 항에 대해서 짝수 항 콜렉션 기능이 더해진 신호들은 직각 위상 변환기에서 만든 신호들과 곱해져 전치왜 곡된 동 위상과 직각 위상 신호들을 만들어 낸다. 이렇게 전치 왜곡된 동 위상 과 직각 위상 신호는 원래의 크기와 위상이 결 합된 출력신호로 변환되고 신호의 이득을 조절하여 출력된다. 이러한 기능을 하는 콜렉션 프로세서는 출력에서 발생하는 혼 변조 신호의 어떤 위상이나 크기에 대해서도 만족할 수 있도록 360° 벡터 변조기를 사용하여 혼변조 신호를 제어하도록 하였 다. 또한, 디지털 콘트롤러는 전력증폭기 출력신호를 피드백하 여 이 신호로부터 추출된 크기와 위상 정보를 바탕 분석하여 계 수들이 적응할 수 있도록 제어한다. 이것은 출력 신호의 혼변조 신호가 선형화되어 혼변조 신호의 에러가 최소가 되도록 계수 를 최적화가 되도록 지속적으로 제어한다.

그림 2. 신테라 전치왜곡 칩을 이용한 선형화 증폭기 블럭도

**Fig. 2.** Linearization amplifier block diagram using Scintera predistortion chip.

그림 3. 신테라 전치왜곡 칩 구조와 기능 블럭도

**Fig. 3.** Scintera predistortion chip architecture and functional block diagram.

그림 4. 볼테라 시리즈 발생기 블럭도

Fig. 4. Volterra series generator block diagram.

231 www.koni.or.kr

#### Ⅲ. 실험결과

#### 3-1 도허티 증폭기의 특성

본 논문에서 사용한 전력증폭기는 (주)케이알에프의 KAS 2145-20WS-PRK, WCDMA 28 W 출력되는 전력 증폭기로 사용 주파수는 2150 ~ 2170 MHz이다. 여기서 사용된 전원은 27 V이며, 드라이브용 트랜지스터는 프리스케일사의 MMG15241 과 MRF6S21010을 사용하였으며, 주 증폭기는 MRF8S21120을 이용하여 도허티 증폭기로 구현하였다. 측정한 효율은 주 증폭기와 드라이브 증폭기의 전류를 합산하여 계산하였고, 측정 신호는 단일 톤으로 증폭기의 이득과 효율을 측정하였으며, WCDMA 2-캐리어 (± 5 MHz 옵셋, WCDMA 3GPP Test Model 1, 64 DPCH, PAPR 6.5 dB @ 0.01%) 신호로 ACPR(Adjacent Channel Power)과 IM3 (3rd Order Intermodulation Distortion)를 측정하였다.

제작된 도허티 증폭기는 그림 5에 나타내었다. 이 그림에서 ① 영역은 입력 신호를 받는 입력 커넥터와 이득을 조절할 수 있는 가변저항, 그리고 증폭기의 주위 온도에 따른 이득을 조정 하기 위한 조정 소자와 1차 드라이브 증폭기인 MMG15241로 구성되어 있다. ② 영역에서는 2차 드라이브 증폭기인 MRF6S21010으로 구성되어 있다. ③ 영역에서는 본 논문의 주 증폭기인 도허티 증폭기가 MRF8S21120 으로 구성되어 있으며 그림의 아래쪽은 캐리어 증폭기이며, 그림의 위쪽은 피킹 증폭기이다. 그리고 도허티 결합 이후에 출력신호의 검출 및 피드백하기 위한 결합기가 있다. ④ 영역은 증폭기의 출력부분으로 출력단의 반사계수에 따른 특성 차이를 방지하고자 아이솔레이터를 사용하였으며 반사된 신호를 측정하기 위한 반사파 커넥터가 있다. 마지막으로 ⑤ 영역에서는 전원커넥터와 출력신호 피드백 커넥터가 있다.

먼저 증폭기에 2150 MHz 단일 톤 입력시 소모 전류 와 효율특성은 표 1에 나타내었다. 이 표에서 효율을 보면 출력이 높아질수록 효율이 좋아지는 것을 관찰 할 수 있다. 이것은 전력트랜지스터가  $P_{1dB}$ 인 330 Watts 지점에 가까울수록 효율이 좋아짐을 알 수 있다.

그림 5. 제작된 도허티 증폭기

Fig. 5. Fabricated Doherty amplifier.

표 1. 도허티 증폭기의 단일 톤 특성 (@ 2150 MHz)

**Table. 1.** Single tone characteristics of Doherty amplifier (@ 2150 MHz).

| 출력 [W] | 입력[dBm] | 이득 [dB] | 소모전류 [A] | 효율    |

|--------|---------|---------|----------|-------|

|        |         |         |          | [%]   |

| 2.0    | -18.8   | 51.8    | 2.1      | 3.52  |

| 3.2    | -16.8   | 51.8    | 2.32     | 5.05  |

| 5.0    | -14.8   | 51.8    | 2.6      | 7.14  |

| 8.0    | -13.0   | 52.0    | 2.94     | 10.01 |

| 12.6   | -11.1   | 52.1    | 3.46     | 13.48 |

| 20.0   | -9.1    | 52.1    | 4.22     | 17.51 |

| 31.6   | -7.1    | 52.1    | 5.2      | 22.52 |

| 50.1   | -5.1    | 52.1    | 6.56     | 28.30 |

| 63.1   | -4.2    | 52.2    | 7.52     | 31.08 |

| 79.4   | -3.3    | 52.3    | 8.6      | 34.21 |

| 100.0  | -2.4    | 52.4    | 10       | 37.04 |

| 125.9  | -1.5    | 52.5    | 11.68    | 39.92 |

| 158.5  | -0.6    | 52.6    | 13.76    | 42.66 |

| 199.5  | 0.4     | 52.6    | 16.36    | 45.17 |

| 251.2  | 1.7     | 52.3    | 19.8     | 46.99 |

| 281.8  | 2.5     | 52.0    | 22       | 47.45 |

| 316.8  | 3.5     | 51.5    | 24.24    | 48.32 |

| 331.1  | 5.1     | 50.1    | 25.32    | 48.44 |

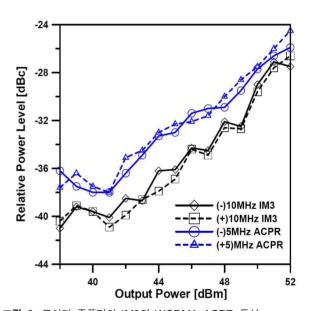

그림 6. 도허티 증폭기의 IM3와 WCDMA ACPR 특성

**Fig. 6.** 3rd order intermodulation distortion and WCDMA ACPR characteristic of Doherty amplifier.

또한, 그림 6은 혼변조와 ACPR 특성을 나타낸 것으로 2-톤 시험은 2155 MHz 와 2165 MHz를 입력시켜서 3차 혼변조 신호의 특성을 보았고, 2160 MHz WCDMA 1FA신호를 입력하여 ACPR 특성을 관찰하였다. 이 그래프를 보면 중심주파수에서 ± 10 MHz 이격된 지점에서 3차 혼변조 신호가 거의 동일하게 측정되었고 그 값은 -42 dBc ~ -27 dBc 까지 변화함을 보여주고 있으며, ACPR 특성도 중심주파수 에서 ± 5 MHz 이격된 지점에서 거의 동일하게 측정되었고 그 값은 -37 dBc ~ -24 dBc 까지 변화함을 보여주고 있다.

#### 3-2 신테라 칩을 적용한 도허티 증폭기의 특성

그림 5의 도허티 증폭기에 신테라 전치왜곡 선형화 칩 SC1889A를 적용한 결과를 살펴보면 먼저, 그림 7은 신테 라 전치왜곡 선형화 칩을 적용하여 제작된 아날로그 선형 화기 부분의 PCB를 나타낸 것이다.

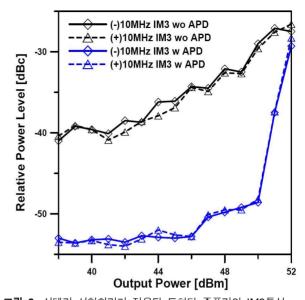

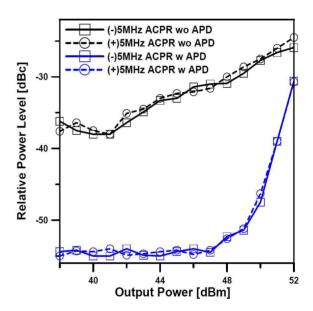

선형화기가 적용된 증폭기의 단일 톤 시험은 주파수 2150 MHz에서 증폭기의 이득, P<sub>IdB</sub>, 그리고 효율을 측정하 기 위한 실험으로 신테라 선형화 칩 적용과 관계없이 표 1 의 특성과 동일하게 측정되었다. 그림 8는 2-톤 실험 결과 를 나타낸 것으로, 2-톤 시험은 2155 MHz 와 2165 MHz의 CW 신호를 입력시켜서 3차 혼변조 신호의 특성을 나타낸 것 으로 신테라 선형화 칩의 존재 유무에 따라서 전력증폭기 의 특성을 확인한 것이고, 그림 9는 2160 MHz WCDMA 1FA 신호를 입력하여 선형화기 칩을 사용하였을 때와 사용 하지 않았을 때의 ACPR 특성을 나타낸 것이다. 이 그래프를 보면 2-톤 중심주파수에서 ± 10 MHz 이격된 지점에서 3차 혼 변조 신호 특성 개선 정도를 나타낸 것으로 100W 지점에서 15 dBc 이상 개선된 것을 관찰 할 수 있다. 또한, ACPR 특성은 WCDMA 신호 중심주파수 에서 ± 5 MHz 이격된 지점에서 ACPR 개선 정도를 보야준 것으로 특히 출력이 100W 되는 지 점까지는 -50 dBc 이하를 유지 하는 것을 볼 수 있다. 이것은 신테라 선형화 칩이 전력 증폭기가 100 W 출력에서 IM3와 ACPR 특성을 15 dB 이상 선형화 시키는 것을 알 수 있다.

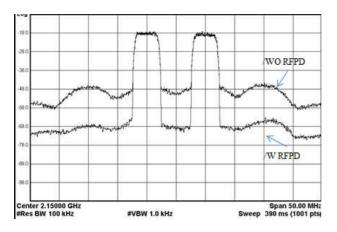

그림 10은 WCDMA 2FA 신호 (2145 MHz, 2155 MHz) 입 력시 출력이 49 dBm일 경우 도허티 증폭기의 신테라 선형 화 칩 존재 유무에 따른 출력 결과를 나타낸 것이다. 이 그 래프를 살펴보면 신테라 선형화 칩이 전력증폭기의 ACPR 을 15 dB 이상 개선시킴을 알 수 있다.

그림 7. 제작된 신테라 선형화기 (SC1889A)

Fig. 7. Fabricated Scintera linearizer (SC1889A).

그림 8. 신테라 선형화기가 적용된 도허티 증폭기의 IM3특성

Fig. 8. 3rd order intermodulation distortion characteristics of Doherty amplifier with Scinterra linearizer.

그림 9. 신테라 선형화기가 적용된 도허티 증폭기의 WCDMA ACPR 특성

Fig. 9. WCDMA ACPR characteristics of Doherty amplifier with Scinterra linearizer.

233 www.koni.or.kr

그림 10. 신테라 선형화기가 적용된 도허티 증폭기의 WCDMA 2FA 신호에서 ACPR 특성 (@49 dBm)

Fig. 10. WCDMA 2FA ACPR characteristics of Doherty amplifier with Scinterra linearizer (@49 dBm)

#### | ₩. 결 론

본 논문에서는 전력증폭기의 주요 요구사항인 높은 효율과 고선형성을 만족하는 도허티 증폭기와 신테라 선형화 칩을 사용하여 설계하였다.

이 증폭기는 기존 AB급 전력증폭기 보다 11% 이상 효율을 개선하였다. 또한, 신테라사의 전치왜곡 칩(SC1889A)을 사용하여 도허티 증폭기에 적용하였을 때 2-톤 경우의 IM3와 WCDMA 1FA 신호의 ACPR은 15 dBc 이상 개선하였다.

신테라 선형화 칩은 작은 소비전력으로 고성능의 선형화 특성을 보이며, 집적화된 칩으로 되어있어 구성이 간단하다. 따라서 전력증폭기의 고효율, 고선형화 및 소형화에 적합하며 차세대의 전력증폭기 선형화기로 유용하게 사용될 것이다.

## 감사의 글

본 연구는 금오공과대학교학술연구비에 의하여 연구된 논 문임.

## 최 장 헌 (Jang-Hun Choi)

2014년 2월 : 금오공과대학교 전기및전자공학과 (공학석사) 1999년 6월~ 2010년 10월 : 세원텔레텍(주) 통신연구소 Group Leader

2011년 2월 ~ 현재 : ㈜케이알에프 대표이사

※관심분야: RF 및 Microwave 전력 증폭기 및 선형화기 설계

## 참고문헌

- [1] S. C. Cripps, Advanced Techniques in RF Power Amplifier Design, Norwood MA: Artech House, 2002.

- [2] Joel Vuolevi and Timo Rahkonen, *Distortion in RF power Amplifier*, Norwood, MA: Artech House, 2003.

- [3] Guillermo Gonzalez, Microwave Transistor Amplifiers Analysis and Design, 2nd ed. Upper Saddle River, NJ: Prentice-Hall, 1997.

- [4] Y. S. Lee and Y.H. Jeong, "A high-efficiency class-E GaN HEMT power amplifier for WCDMA applications," *IEEE Microwave and Wireless Components Letters*, Vol. 17, No. 8, pp. 622-624, Aug. 2007.

- [5] Y.S. Lee, M.W. Lee, and Y.H. Jeong, "A 1 GHz GaN HEMT based class E power amplifier with 80% efficiency," *Microwave and Optical Technology Letters*, Vol. 50, No. 11, pp. 2989-2992, Nov. 2008.

- [6] T.Mury and V.F. Fusco, "Inverse class-E amplifier with transmission line harmonic suppression," *IEEE Transactions on Circuits and Systems I, Regular Papers*, Vol. 54, No. 7. pp. 1555-1561, Jul. 2007.

- [7] F.H. Raab, "Class F amplifiers with maximally flat waveforms," *IEEE Transactions on Microwave Theory* and Techniques, Vol. 49, No. 6, pp.1162-1166, Jun. 2001.

- [8] Y.Y. Woo, Y. Yang, and B. Kim, "Analysis and experiments for high efficiency class F and inverse class F power amplifiers," *IEEE Transactions on Microwave Theory and Techniques*, Vol. 54, No. 5, pp.1969-1974, May. 2006.

- [9] Y.S. Lee, M.W. Lee, G.B. Choi, and Y.H. Jeong, "New an predistorter using mixing peration for independent control of IM3 components," *Microwave* and Optical Technology Letters, Vol. 49, No. 10, pp. 2552-2555, Oct. 2007.

- [10] Scintera Homepage http://www.scintera.com

김 영 (Young Kim)

-1988년 2월 : 서강대학교 전자공학과 (공학석사), 2002년8월 : 서강대학교 전자공학과 (공학박사)

1988년 1월 ~ 1993년 5월 : 이즈텔시스템즈(주) 연구소 선임연구원 1993년 6월 ~ 1998년 2월 : 삼성전자(주) 정보통신사업본부 선임연구원

1998년 3월 ~ 2003년 2월 : 두원공과대학교 정보통신과 조교수 2003년3월 ~ 현재 : 금오공과대학교 전자공학부 교수

※관심분야: RF 및 Microwave 회로해석 및 설계, 전력 증폭기 및 선형화기 설계

윤 영 철 (Young-Chul Yoon)

1978년 2월: 서강대학교 전자공학과 (공학사) 1982년 2월: 서강대학교 전자공학과 (공학석사) 1989년 2월: 서강대학교 전자공학과 (공학박사)

1987년 9월 ~ 현재 : 관동대학교 전자정보통신공학부 교수

※관심분야: RF 및 Microwave 회로설계

235 www.koni.or.kr