http://dx.doi.org/10.6113/TKPE.2014.19.3.283

## Si MOSFET과 GaN FET Power System 성능 비교 평가

안정훈<sup>1</sup>, 이병국<sup>1</sup>, 김종수<sup>†</sup>

# Comparative Performance Evaluation of Si MOSFET and GaN FET Power System

Jung-Hoon Ahn<sup>1</sup>, Byoung-Kuk Lee<sup>1</sup>, and Jong-Soo Kim<sup>†</sup>

Abstract - This paper carries out a series of analysis of power system using Gallium Nitride (GaN) FET which has wide band gap (WBG) characteristics comparing to conventional Si MOSFET-used power system. At first, for comparison of each semiconductor device, the switching-transient parameter is quantitatively extracted from released information of GaN FET. And GaN FET model which reflect this dynamic property is configured. By using this model, the performance of GaN FET is analyzed comparing to Si MOSFET. Also, in order to enable a representative assessment on the power system level, Si MOSFET and GaN FET are applied to the most common structure of power system, full-bridge, and each power systems are compared based on various criteria, such as performance, efficiency and power density. The entire process is verified with the aid of mathematical analysis and simulation.

**Keywords:** gallium nitride FET (GaN FET), wide band gap device (WBG device), high electron mobility transistor (HEMT), power system, phase-shift full bridge converter (PSFB converter)

#### 1. 서 론

더 높은 효율과 전력 밀도를 갖는 Power System의 구현은 전력전자분야의 영원한 목표이다. 이러한 요구는다양한 토폴로지의 탐구와 새로운 제어 방법의 연구를통하여 일부 만족되기도 하지만, 정작 괄목할만한 변화나 개선은 사용하는 전력반도체 소자의 진보에 종속되어 왔다. 기존의 Si 반도체 소자는 거대한 시장과 축적된 제조기술에 힘입어 가장 낮은 가격에 신뢰성과 활용도가 높은 장치로서 각광 받아왔다. 그러나 현재 전력전자분야의 토폴로지 연구 및 제어 기술수준은 이미 Si소자로 구현 할 수 있는 가장 높은 영역까지 포화되어있다. 따라서, 그 이상의 Power System 구현은 Si 소자고유의 물성적 한계에 닿아 어려움이 있으며, 초소형화및 고효율화를 지향하는 미래형 Power System을 위해

서는 반도체 소자 자체의 연구 및 적용이 필수적이다. 이러한 견지에서 SiC 등 WBG 특성을 갖는 반도체 소 자의 연구 및 개발에 큰 기대가 모아지고 있다.

특히, 최근 차세대 에너지 절감 반도체로 각광받고 있 는 GaN 반도체는 WBG 특성을 통하여 낮은 온-저항과 고주파수 운전, 그리고 우수한 고온특성 등 많은 강점이 있다<sup>[1]-[2]</sup>. 미국과 유럽의 경우 WBGS-RF, NEXT, KORRIGAN, MANGA 그리고 MORGAN 등의 프로젝 트를 통하여 GaN 반도체 자체의 연구 및 GaN 반도체 를 활용한 고효율 고전력밀도 전원 장치 개발을 중장기 계획으로 갖고 집중적으로 연구하고 있다<sup>[2-8]</sup>. 또한, Yole Development사의 시장분석 자료에 따르면 GaN 반도체 소자의 시장은 2016년에는 5억 달러 규모로 급 성장 할 것으로 예측하고 있다<sup>[9]</sup>. 그러나 GaN 반도체 및 GaN Power System을 향한 국제적 관심과는 대조적 으로 국내의 관심과 연구의 정도는 매우 미흡하다. 더욱 이. 현재 GaN 반도체의 과도특성 정보는 공급업체에서 도 정량적으로 제공하거나 명시하지 않아 GaN FET Power System의 연구 뿐 아니라 GaN FET 자체의 연 구에도 어려움을 주고 있다.

본 논문에서는 먼저 GaN FET의 공개된 정보를 바탕으로 스위칭 과도 특성과 관련된 명시되지 않은 파라미

Paper number: TKPE-2014-19-3-11

Print ISSN: 1229-2214 Online ISSN: 2288-6281

<sup>†</sup> Corresponding author: jskim2@daejin.ac.kr, Div. of Electric, Electronic and Communication Eng., Daejin University Tel: +82-31-539-1916 Fax: +82-31-539-1916

<sup>&</sup>lt;sup>1</sup> Dept. of Electrical Eng., Sungkyunkwan University Manuscript received Dec. 30, 2013; accepted Mar. 18, 2014 — 본 논문은 2013년 추계학술대회 우수추천논문임

터들을 정량적으로 추출하는 방법을 제시하였다. 또한, 추출한 파라미터를 근거로 GaN FET의 손실 및 발열특성을 분석하고 Si MOSFET과 비교하였다. 분석 결과를 바탕으로 GaN FET으로 구성된 Power System을 모의하고 종합적인 평가가 가능한 시뮬레이션 플랫폼을 구축하였다. 일련의 분석 과정을 통하여 기존의 Si MOSFET Power System 대비 GaN FET Power System의 장점과 가능성 그리고 최적 설계점을 밝힌다.

#### 2. GaN FET 특성 분석

#### 2.1 GaN FET의 물성적 특성

표 1은 기존의 Si나 SiC 소자와 비교하여 GaN 소자의 물성적 특성을 나타낸다. 이종 간의 접합을 의미하는 Heterojunction 구조인 GaN FET의 밴드갭 에너지 (Eg)는 3.4 eV로 Si소자의 세배이며, 기존의 와이드 밴드갭 특성을 갖는 SiC 소자보다도 높은 에너지 준위를 갖는다. 임계 항복전압은 Si소자의 11배로 SiC 소자보다도 높으며, 드리프트 속도는 다른 어떤 재질의 특성보다 높다. 이러한 고유 성질 때문에 GaN 소자는 동일한 임계 항복전압을 갖는 경쟁소자들 가운데 가장 낮은 도통저항 (RDS(ON))을 갖는다. 뿐만 아니라, 2층 구조의 전자가스 (2DEG, two-dimensional electron gas)를 포함하는 GaN 소자는 SiC 소자와 비교하여 월등하게 높은 전자의 이동도를 가지는 소자이며 (HEMT, High Electron Mobility Transistor), 이는 매우 작은 사이즈의 소자 구현이 가능함을 의미한다<sup>[10]</sup>.

GaN을 활용한 FET은 JFET와 유사하게 게이트 전원이 인가되지 않은 상태에서 도통되는 공핍모드 (depletion-mode) FET가 먼저 개발되었으며, 일반적인 상태에서 차단되는 강화모드 (enhanced-mode) FET가 뒤이어 개발되었다. 현재 주로 연구되고 있는 eGaN FET은 강화모드 FET을 의미하며, 구조적으로는 그림 1과 같이 Si 웨이퍼위에 얇은 AIN (Aluminum Nitride)층과 AIGaN (Aluminum Gallium Nitride)층 사이에 GaN층을 성장시켜 얻어진다. 이러한 eGaN FET은 N-channel MOSFET과 동작이 유사하여 기존의 게이트 구동 논리를 그대로 사용할 수 있다는 점에서 이점이 있다.

#### 2.2 eGaN FET vs. Si MOSFET

eGaN FET과 Si MOSFET의 성능 비교를 위하여 비 숫한 정격의 두 소자 [EPC2001 (100 V, 25 A), IPA180N10N3 G (100 V, 28 A)]를 선정하였다. eGaN FET의 정량화 되지 않은 과도 상태 파라미터를 추출하기 위해서 Datasheet에 공개된  $V_{ds}$  대 기생 커페시턴스 그래프와  $V_{gs}$  대  $I_D$  그래프를 이용한다. 이때, 반도체 소자의 기생 커페시턴스는 역으로 걸리는 전압 ( $V_{ds}$ )이 낮아질수록 급격히 중가하는 양상이 있으며, 해당 변화를 연산에 근사적으로 반영하기 위하여  $V_{ds}$ 가 5 V인 경우

Fig. 1 Physical structure of eGaN FET

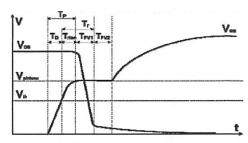

(a) Turn-On Transient Curve

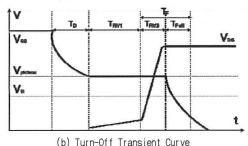

Fig. 2 Transient Curve

Table 1 Material properties of GaN, SiC, and Si

| Parameter                   | GaN      | Si   | SiC |

|-----------------------------|----------|------|-----|

| E <sub>G</sub> (eV)         | 3.4      | 1.12 | 3.2 |

| $E_{BR}$ (MV/cm)            | 3.3      | 0.3  | 3.5 |

| $V_S$ (x $10^7$ cm/s)       | 2.5      | 1.0  | 2.0 |

| $\mu$ (cm <sup>2</sup> /Vs) | 990-2000 | 1500 | 650 |

와 50 V인 두 경우로 나누어 전체 커패시턴스의 변화를 표 2로 단순화 하였다. 또한,  $V_{gs}$  대 Id 그래프로부터 Id 가 20 A일 때의 Transconductance를 22.68로 얻을 수 있다. eGaN FET 구동을 위한  $V_{gs(th)}$ 는 1.4 V로 Si MOSFET과 비교하여 두 배 가량 낮기 때문에 게이트 전압  $(V_{g})$ 과 게이트 저항  $(R_{g})$ 을 각각 적합한 수준  $(5 V, 2.5 \Omega)$ 으로 정하였다.

그림 2의 과도상태 곡선은 각각 Turn-on 과도상태와 Turn-off 과도상태를  $V_{DS}$ 가 낮은 영역의 시정수와  $V_{DS}$ 가 높은 영역의 시정수로 나누어 근사화한 그래프이다. 이때, Turn-on 과도상태 곡선 그림 2(a)과 식 (1-7)의 과정을 통하여 Turn-on 과도시간  $(T_r)$ 을 구할 수 있다. 먼저, 소자의  $V_{gS(th)}$ 와 Transconductance를 통하여 식 (1)의 과정으로 밀러평면의 전압  $V_{plateau}$ 를 구할 수 있다.

Table 2 Parasitic capacitances of each switch

| Parasitic<br>Capacitor | eGaN FET |         | Si MOSFET |         |  |

|------------------------|----------|---------|-----------|---------|--|

|                        | Vds=5 V  | 1300 pF | Vds=5 V   | 1350 pF |  |

| $C_{iss}$              | Vds=50 V | 450 pF  | Vds=50 V  | 1800 pF |  |

| $C_{\rm oss}$          | 450 pF   |         | 226 pF    |         |  |

| $C_{rss}$              | Vds=5 V  | 25 pF   | Vds=5 V   | 11 pF   |  |

|                        | Vds=50 V | 154 pF  | Vds=50 V  | 350 pF  |  |

$$V_{plateau} = V_{gs(th)} + \frac{I_D}{G_{fs}} = 1.4 + \frac{20}{22.68} = 2.382[V]$$

(1)

이때, 밀러평면 도달 시간  $T_P$ 와 문턱전압 도달 시간  $T_D$ 는  $V_{DS}$ 가 50 V인 조건에서의 시정수를 사용하여 각각 식(2), (3)을 통하여 구할 수 있으며,  $I_D$ 가 증가하는 시간 (Vds가 대폭 감소하는 시간, Trise)를  $T_P$ 와  $T_D$ 의 연산을 통하여 식(4)와 같이 구할 수 있다.

$$\begin{split} &V_{gs(th)} & \qquad \qquad (3) \\ &= V_g \times \left\{ 1 - e^{-\frac{T_D}{R_G C_{iss1}}} \right\} = V_g \times \left\{ 1 - e^{-\frac{T_D}{R_G (C_{gs} + C_{gd1})}} \right\} \\ &T_{rise} = T_P - T_D = 0.728 - 0.401 = 0.327 [ns] \end{split} \tag{4}$$

밀러평면의 지속시간 중 Vds전압이 급격히 떨어지는 구간  $(T_{fvl})$ 을 구하기 위하여, 먼저 밀러평면 구간에 흐르는 게이트 전류  $(i_{G,plateau})$ 를 식 (5)를 통하여 구한다. 그리고, 이 구간에서의  $V_{DS}$ 의 전압 변화율이  $V_{DG}$ 의 전압변화율과 동일함을 이용하여  $C_{gd}$ 의 관계식 (6)을 이용하여  $T_{fvl}$ 을 계산한다.

$$i_{G,plateau} = \frac{V_G}{R_G} \times \left\{ e^{-\frac{T_P}{R_G C_{iss1}}} \right\} = \frac{5}{2.5} \times \left\{ e^{-\frac{0.728}{2.5 \times 0.45}} \right\} = 1.047 [A]$$

$$T_{fv1} = \frac{V_D C_{gd1}}{I_{G,plateau}} = \frac{50 \times 0.025}{1.047} = 1.182 [ns]$$

(6)

이렇게 구해진  $T_{fvl}$ 에 앞서 구한  $T_{rise}$ 을 더하여 전체 Turn-on 과도 시간  $(T_r)$ 을 구할 수 있다 (식 (7)). 동일 한 방식의 역순으로 Turn-off 과도시간  $(T_f)$ 도 그림 2(b)의 과도곡선을 고려하여 계산한다 (식 (8)).

$$T_r = T_{rise} + T_{fv1} = 0.327 + 1.182 = 1.509 [ns] \tag{7} \label{eq:7}$$

$$T_f = T_{fall} + T_{rv2} = 0.520 + 1.182 = 1.702[ns]$$

(8)

본 과정은  $V_{DS}$ 의 변화에 따른 기생커패시턴스의 변화를 두 단계로 단순화하였기 때문에 실제 실험결과와 오

Table 3 Major parameter of GaN FET and Si MOSFET

| Para                       | meter   | eGaN FET |       | Si MOSFET |         |

|----------------------------|---------|----------|-------|-----------|---------|

| Pro                        | duct    | EPC      | 2001  | IPA180N   | V10N3 G |

| $R_{DS}$                   | S(ON)   | 0.00     | 8 Ω   | 0.02      | 29 Ω    |

| Tr [ns]                    | Tf [ns] | 1.509    | 1.702 | 3.388     | 6.958   |

| $\mathrm{Q}_{\mathrm{RR}}$ | [nC]    | (        | )     | S         | 14      |

| V                          | SD      | 1        | .8    | 0         | .9      |

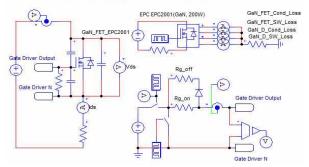

#### **GaN FET Characteristics Test Scheme**

Fig. 3 Evaluative simulation model of GaN FET

차가 발생할 수 있으나 실제 기생커패시턴스가 특이 전압에서 급격하게 변하는 것을 고려하면 근사적으로 타당한 과정이라 할 수 있다. 또한, 실제 실험결과와의 다소간의 오차가 상대적인 비교에 미치는 영향을 무시하기 위하여, 비교대상인 Si MOSFET (IPA180N10N3 G)의 경우도 동일한 방법과 유사한 조건으로 과도시간을 구하였다. 다만, Si MOSFET의  $V_{gs,th}$  및  $V_{gs,max}$ 가 GaNFET와 비교하여 상대적으로 높기 때문에 합리적인 비교를 위하여 Si MOSFET의 게이트 전압  $(V_g)$  조건은 15 V로 상향 조정하고, 게이트 저항  $(R_g)$ 의 경우도 7.5 Q으로 높여서, 게이트 전류가 GaN FET과 동일하게 최대 2 A를 넘지 않도록 하였다. 여기에 소자의 손실과 관련된 주요 파라미터들을 함께 정리하면 최종적으로 두 소자의 차이를 표 3으로 정량화 할 수 있다.

본 연구에 적합한 시뮬레이션 툴은 다양한 소자의 특성을 모사하여 상호간의 비교평가에 유리하며, 궁극적으로는 Power System간의 비교를 목적으로 개별소자의관점뿐 아니라 전력변환장치의 관점에서 다양한 제어전략과 토폴로지로의 적용이 자유로워야 한다. 동시에반도체 소자의 손실을 세분화 하여 소자의 장단점을 분석적으로 표현해줄 수 있어야 한다. 따라서, 사용한 시뮬레이션 툴은 이러한 요구 조건과 기존 연구결과[11-13]를 반영하여 Psim으로 선정하였으며, 표 3의 파라미터를반영하여 그림 3과 같이 eGaN FET (EPC2001)의 시뮬레이션 모델을 구현하였다. 또한, 동일한 방식으로 Si MOSFET (IPA180N10N3 G)을 모델링하여 대조군으로하였다. 해당 모델은 Thermal Module을 이용하여 손실

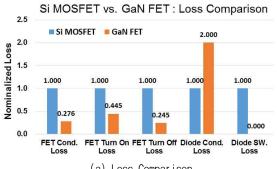

(a) Loss Comparison

(b) Thermal Properties Comparison ( $R_{th,etc}$ =1.21 $^{\circ}$ C/W)

Fig. 4 Comparison of Si MOSFET and eGaN FET

분석이 가능하고, 3-state-MOSFET을 이용하여 과도 특성을 검증할 수 있도록 구성하였다. 이때, 두 반도체 소자에 대하여 게이트 구동회로나 PCB Lavout 등의 외 적조건은 가장 이상적인 조건으로 동일하게 통제하며, 이 과정에서 기생 인덕턴스의 영향은 무시하였다.

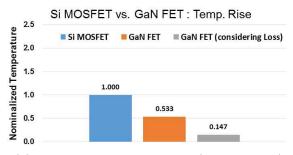

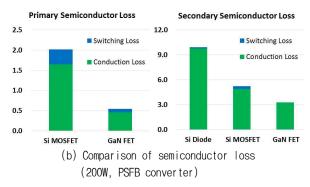

그림 4의 그래프는 Si MOSFET (IPA180N10N3 G)의 성능을 기준으로 정규화하여 eGaN FET (EPC2001)의 성능을 비교한 결과이다. 그림 4(a)은 두 소자에서 발생 할 수 있는 손실을 세분화 하여 비교하였다. 도통손실은 eGaN FET의 낮은 R<sub>DS(ON)</sub>의 영향으로 기존 발생 손실 의 72% 가 감소하고, 턴-온/오프 스위칭 손실은 빠른스 위칭 속도로 인하여 각각 기존 발생 손실의 55%, 75% 가 감소하였음을 확인할 수 있다. 특히, ZVS Turn-on 하는 공진형 컨버터의 경우 Turn-on 손실을 무시할 수 있기 때문에 기존 Si MOSFET 소자를 eGaN FET로 대체할 경우 기존 발생 손실의 75% 가량이 저감될 것 으로 기대된다.

역병렬 다이오드의 경우 eGaN FET의 역병렬 다이오 드의 정방향 강하 전압  $(V_{SD})$ 이 오히려 높아 도통손실 이 증가하는 단점이 있으나, 반면에 Qrr이 없기 때문에 역회복 과도 손실이 전혀 발생하지 않는다. 따라서, 역 전류 도통구간이 많은 전원장치에서 최대 효과를 얻기 위해서는 다이오드 도통 구간을 최소화 할 수 있는 동 기정류 방식의 적용이 유리하며, 이 경우 낮은 R<sub>DS(ON)</sub>과 역회복 손실이 없는 이점을 동시에 가져갈 수 있다.

그림 4(b)는 두 소자의 발열특성을 비교한 것으로 동 일한 방열조건 (R<sub>th,etc</sub>=1.21 ℃/W) 및 손실조건에서

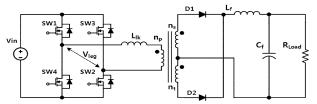

Fig. 5 ZVS PSFB converter schematic

Table 4 Design specification of 200W ZVS PSFB converter

| Parameter   | Electrical Value         | Specification      |

|-------------|--------------------------|--------------------|

| Vin / Vo    | 50 Vdc / 14 Vdc          | fs=100 kHz         |

| Lf          | 11 uH                    | CH270060           |

| Cf          | 120 uF                   | BXA 220 uF<br>35 V |

| Transformer | 44:18:18<br>(Center-tap) | EE2525             |

| Rectifier   | _                        | DSEI 2x 61         |

eGaN FET은 접합과 케이스 사이의 열 저항이 낮기 때 문에 기존 Si MOSFET 발열량의 절반 수준일 것으로 예상된다. 여기에 동일 조건에서 발생하는 소자의 손실 이 eGaN FET의 경우 상대적으로 낮은 것을 반영하면 eGaN FET은 Si MOSFET의 1/7배 이하의 낮은 발열이 기대된다. 이는 eGaN FET의 방열을 위해 할당해야 하 는 기구부의 부피와 무게가 큰 폭으로 감소 할 수 있음 을 의미하며, 단가적인 측면과 함께 고 전력밀도의 전원 장치 구성에 유리하다.

#### 3. GaN FET Power System

#### 3.1 대조군 시료 설계 및 시뮬레이션 플랫폼 구성

$$L_{f} = \frac{(1 - 2D) \times R_{fullLoad}}{4 \times f_{s} \times LoadRatio}$$

(9)

$$C_{f} = \frac{(1-2D)}{32 \times L_{f} \times f_{s}^{2} \times Ripple Ratio}$$

(10)

$$L_{lkg} = (\frac{8}{3} \times Coss + C_{TR}) \times V_i^2 \div I_{pk}^2$$

(11)

GaN FET Power System을 구성하고 대표성을 갖는 성능평가를 위하여 일반적인 사양의 컨버터를 설계한다. 출력전압은 다양한 디지털 부하 구동에 적합한 14 V로 정하고 각각의 스위치는 위상천이 방식으로 영전압 스 위칭 하도록 전체 회로를 그림 5와 같이 구성하였다.

현재 상용화 되어 있는 GaN FET의 종류와 정격이 매우 한정적인 것을 감안하여 입력전압은 일반적인 사 양보다 다소 낮은 50 V로, 출력전력은 200W급으로 낮 추어 시스템을 구성하여 모의 평가하도록 한다. 이때. 대상 컨버터는 최대부하의 10% 까지 CCM 동작하고, 25% 부하까지 ZVS동작 하도록 식(9-11)을 이용하여 주 요 소자를 설계하였다[14-16].

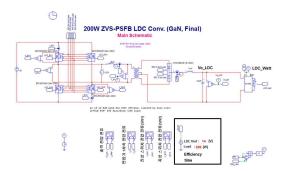

(a) 200W GaN power system simulation main schematic

Loss Analysis

(b) Loss calculation block

Fig. 6 Simulation configuration

GaN FET Power System과 Si MOSFET Power System의 형평성 있는 비교를 위하여 반도체 소자를 제외한 모든 사양은 동일하게 통제 하며, 각각의 Power System에 적용할 소자로는 앞선 2장에서 분석한 EPC2001 (100 V, 25 A), IPA180N10N3 G (100 V, 28 A)를 사용하기로 한다. 최종으로 결정한 주요 전기적 파라미터 및 상세 사양은 표 4로 요약된다.

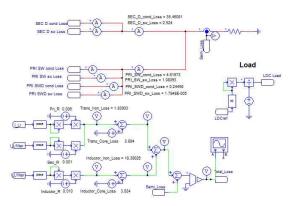

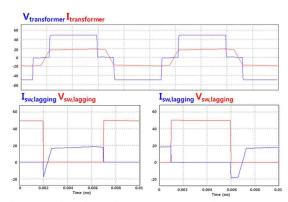

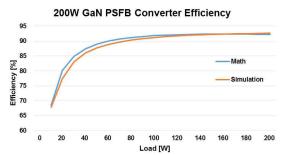

각 부의 손실 (스위치, 정류기, 인덕터, 변압기 등)과 전체 컨버터의 효율을 예측 할 수 있는 시뮬레이션 플 랫폼을 P-sim9.0의 Thermal Module과 연산 블록을 사용하여 그림 6과 같이 구축하였다. 그림 6(a)의 파워부 회로는 진상 및 지상 스위치의 ZVS 동작을 포함하여 설계 사양의 위상천이 컨버터를 모의 하였으며 주요 파 형은 그림 7과 같다. 그림 6(b)의 손실계산 블록은 실시 간으로 파워부의 전압, 전류 정보와 각 소자의 상세정보 를 바탕으로 손실과 효율을 계산하도록 구성하였다. 그 림 8은 200W GaN Power System의 수식적으로 계산하여 얻어진 효율과 시뮬레이션 결과 효율을 비교한 그래 프이며 두 결과의 평균오차는 1% 미만으로 일치하였다.

#### 3.2 Si MOSFET vs. GaN FET Power System

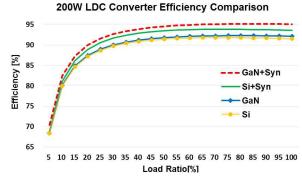

그림 9(a)는 반도체 구성에 따른 Power System의 효율곡선을 나타낸다. Si MOSFET을 사용한 경우와 비교하여, GaN FET을 사용한 경우 최대 부하에서 0.5% 가

Fig. 7 Major simulation waveform of PSFB converter

Fig. 8 Efficiency of 200W GaN power system : mathematic result vs. simulation result

량의 효율향상을 보였다. 이때, 2차측 정류부를 각각의 반도체 소자를 사용하여 동기정류 할 경우에는 GaN FET Power System의 최대효율은 95.18% 로 93.47%의 효율을 갖는 Si MOSFET Power System과 비교하여 2% 가량의 두드러진 효율 향상을 보였다. 또한, 그림 9(b)의 세부 손실 그래프를 통하여 GaN FET의 경우 GaN FET의 경우 도통손실과 더불어 스위칭 손실이 기존 대비 큰 비율로 감소하며, 고주파수 운전에 용이함을 알 수 있다.

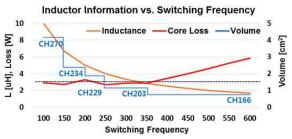

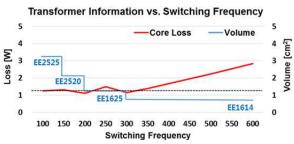

고주파 운전이 용이한 GaN FET Power System의 최적 주파수를 찾기 위하여 각 소자의 효율 및 부피 그 리고 동작주파수의 상관관계를 구하였다. 그림 10(a), (b)의 분석결과는 동작 주파수를 기준 주파수 100 kHz 에서부터 600 kHz까지 증가시킬 때 인덕터와 변압기의 효율과 부피관계를 보여준다. 설계시 고려한 코어는 창 성 사 분말자성 코어 중 High Flux 코어로서 동일한 코 어 부피에서 권선 당 얻을 수 있는 인덕턴스의 최대값 이 높은 재질로 선정하였다. 코어의 크기는 최대 부하를 기준으로 DC Bias 현상으로 인한 L값의 저하현상을 고 려한 최종값이 설계수치가 되도록 하며, 인덕터에 인가 되는 최대 에너지를 감당하는 가장 부피가 작은 코어로 선정하였다. 코일의 선경은 동손을 고려하여 전류밀도가 400~600 A/cm2 범위에 위치하는 표준 AWG 규격의 코 일로 하였다. 또한, 변압기 코어는 TODA ISU 사 EE 코어로서 최대 전달 에너지와 창면적을 만족하는 최저 부피의 코어로 선정하였다.

(a) System efficiency according to power system configuration

Fig. 9 Efficiency comparison of 200W LDC power system

동작 주파수가 증가하면 인덕터의 전기적인 인덕턴스 값은 연속적으로 감소하지만, 실제 코어가 이산적으로 존재하기 때문에 부피는 이산적으로 감소한다. 반면에 손실은 코어사이즈의 감소와 동작 주파수의 증가라는 상반요소에 의하여 굴곡이 있는 증가함수로 나타난다.

커패시터의 경우 Samyoung 사의 BXA Series를 기준하여 부피를 반영하였다. 출력 커패시터의 전기적 사양(커패시턴스)은 동작 주파수의 증가에 따라 감소하며, 내압정격이 동일한 경우 부피도 함께 감소하게 된다. 100 kHz 의 경우 220 uF, 35 V (H10 규격)에서 600 kHz의 경우 4.7 uF, 35 V (D56 규격)으로 줄어들게 된다.

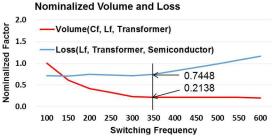

그림 10(c)는 기존 Si MOSFET Power System의 주요소자 (인덕터, 커패시터, 변압기, 반도체소자)의 부피와 손실로 정규화 한 GaN FET Power System의 성능을 보여준다. GaN FET Power System의 동작 주파수가 일정 이상 증가할 경우 부피는 포화되는 반면 손실은 계속 증가하므로 동작 주파수에 따른 손익이 존재한다. 본 논문의 조건에서는 350 kHz 이상으로 동작시킬경우에는 주요소자의 부피의 감소율이 매우 떨어지므로, 350 kHz로 동작시킬 때 가장 효율적인 설계라고 할 수있다. 이렇게 설계된 GaN FET Power System은 기존Si MOSFET Power System과 비교하여 주요소자의 손실을 25% 저감하면서도, 주요소자의 부피를 기존대비 80% 가량 줄일 수 있다.

(a) Switching frequency vs. inductance, volume and loss of inductor

(b) Switching frequency vs. volume and loss of transformer

(c) Optimal design point of GaN power system

Fig. 10 Optimal design point of GaN power system

#### 4. 결 론

본 논문에서는 미래형 반도체로 평가 받는 와이드 밴드 갭 소자 GaN FET을 이용하여 Power System을 설계하고, 성능을 선행적으로 모의 평가하였다. 먼저 GaN FET 데이터 시트에 제공된 제한적 정보로부터 스위칭손실 및 발열량 계산이 가능하도록 과도상태 파라미터를 추출하는 방법을 이론적으로 제시하고, GaN Power System을 모의할 수 있는 시뮬레이션 플랫폼 구축을 통하여 성능을 비교 하였다. GaN FET Power System은 낮은 도통손실과 더불어 고주파 운전에 용이하며, 본 논문의 분석 결과를 바탕으로 대상 시스템의 동작 주파수를 결정할 경우 기존 Si MOSFET Power System 대비 25% 가량 주요 소자의 손실을 줄이면서도 80% 가량의 부피 저감이라는 고효율 고전력 밀도 시스템의 구현이가능하다.

이 논문은 2013년도 정부(매래창조과학부)의 재원으로 한국연구재단의 지원을 받아 수행된 기초연구사업임. (No. NRF-2013R1A1A1076109)

#### References

- [1] Kaminski. N, "State of the Art and Future of Wide Band-Gap Devices," *in Proc, EPE '09 13th European Conference on*, Barcelona, 2009.

- [2] S. J. Pearton et al. "GaN Electronics for High Power, High Temperature Applications," *Electrochem. Soc. Interface*, Vol. 9, No. 2, pp. 34–39, 2000.

- [4] M.J. Rosker et al., "NEXT Program," Dec 3th, 2008.

- [5] M. Rosker et al., "The DARPA Wide Band Gap Semiconductors for RF Applications (WBGS-RF) Program," CS MANTECH Conf., Tampa, Florida, USA, May 18th-21st, 2009.

- [6] DGA, "European Scenario for GaN and SiC for Microwave Applications," Apr. 27th, 2010.

- [7] S. Delage, "MORGAN-Materials for Robust Gallium Nitride," June 2009.

- [8] S.L. Delage, "UltraGaN Project: Breakthrough in GaN Devices Thanks to InAlN/GaN Heterostructure," 2nd EU FET-Clustee Meeting, Nov. 13th-16th, 2007.

- [9] Strategy Analytics, "GaN Power Market to Rise to \$10 Million in 2012, Says Yole," Mar. 7th, 2012.

- [10] Alex Lidow, Johan Strydom, "Gallium Nitride (GaN) Technology Overview," white paper of EPC(WP001), Dec. 27th, 2012.

- [11] Powersim, "PSIM User's Guide," pp. 35-53, May 2010.

- [12] W. Y. Sung, D. G. Woo, Y. S. Kim, and B. K. Lee, "Advanced Simulation Model for Loss Analysis of Converters in Electric Vehicles," *IEEE Vehicular Power and Propulsion Conference (VPPC2012)*, Seoul, Korea, pp. 1206–1210, Oct. 9–12, 2012,

- [13] Muhlethaler, J., Kolar, J.W., Ecklebe, A., "Loss modeling of inductive components employed in power electronic systems," *Power Electronics and ECCE Asia (ICPE & ECCE)*, 2011 IEEE 8th International Conference on, pp. 945–952, May 30-June 3 2011.

- [14] G. B. Koo, G. W. Moon, and M. J. Youn, "Analysis and Design of Phase Shift Full Bridge Converter With Series-Connected Two Transformers," *IEEE Transactions on Power Electronics*, Vol 19, No. 2, pp. 411–419, Mar. 2004.

- [15] Y. K. Lo, C. Y Lin, M. T. Hsieh, and C. Y. Lin, "Analysis and Design of Phase Shift Full Bridge Converter With Series-Connected Two Transformers," *IEEE Transactions on Industrial Electronics*, Vol 58, No. 6, pp. 2572–2575, Jun. 2011.

- [16] Y. C. Hsieh, and C. S. Huang, "Li-ion battery charger based on digitally controlled phase-shifted full-bridge converter," *IET Transactions on Power Electronics*, Vol 4, No. 2, pp. 242–247, Jul. 2009.

#### 안정훈(安正熏)

1986년 1월 30일생. 2011년 성균관대 전자전기공학과 졸업. 2013년 동 대학원 전자전기컴퓨터공학과 졸업(석사). 2013년~현재동 대학원 전자전기컴퓨터공학과 박사과정.

#### 이병국(李秉國)

1968년 12월 25일생. 1994년 한양대 전기공학과 졸업. 1996년 동 대학원 전기공학과 졸업(석사). 2001년 미국 Texas A&M University 전기공학과 졸업(공박). 2002년~2003년 Postdoctoral Research Associate, Texas A&M

University. 2003년~2005년 한국전기연구원 산업전기연구단 전력 전자그룹 선임연구원(팀장). 2006년~현재 성균관대 정보통신공 학부 부교수. 2004년~현재 IEEE Senior Member, IEEE VPPC2012 General Chair. 당 학회 기획이사.

### 김종수(金鍾秀)

1975년 3월 5일생. 2008년 성균관대 대학원 전자전기컴퓨터공학과 졸업(석사). 2011년 동 대학원 전자전기컴퓨터공학과 졸업(공 박). 2011년~2012년 서일대 전기과 강의전 담교수. 2012년~2013년 삼성종합기술원

MD연구소 Power Lab 전문연구원. 2013년~현재 대진대 전기 전자통신공학부 조교수. 당 학회 학술위원.