# ICT 융복합 꼬명을 위한 멀티엘 다각영 LED 및 패키지 기술

김자연<한국광기술원 선임연구원> · 권민기<조선대학교 교수> · 아종욱<엘이디에스티㈜ 대표이사> · 박노준<엘이디에스티㈜ 부설연구소장>

### 1. 개 요

글로벌 LED 시장을 선도하기 위한 국가 LED산업 제품기술 로드맵은 LED 원 플랫폼 패키지 요소기술 부터 LED-유무선통합 제어솔루션과 휴먼감성LED 시스템 개발까지를 최종 목표로 두고 있으며, 최근에 는 실내외 조명뿐만 아니라 수송기기, 정보 디스플레 이, 농수산, 바이오, 무선통신 등 ICT 분야와의 융복 합 조명기술에 대한 연구가 활발히 이루어지고 있다.

그러나 LED 산업 밸류 체인을 관통하는 가장 중요 한 기술은 LED가 기존 조명 시장을 극복할 수 있는 경쟁력을 갖는 방향이며 특히 사용된 반도체의 품질 과 전류주입의 효율에 따라 결정되는 내부양자효율 외에 빛을 외부로 방출시키는 광 추출효율 향상기술 을 그 핵심 기술이라고 할 수 있을 것이며 고출력을 내기 위해 칩의 크기가 증가함에 따른 발열을 제어하 는 기술 또한 중요하다. 조명에 응용하기 위해서는 색 재현성, 연색성 등 및 신뢰성 또한 충분히 높아져야 하다.

본고에서는 최근까지 소개된 다양한 광 추출효율 기술을 설명하고 다양한 chip shaping을 통한 고효율, 고연색성. 고신뢰성 멀티셀 다각형 LED 패키지 기술 을 중점적으로 다루고자 한다.

# 2. 광 추출효율 향상 기술

LED 의 성능을 평가하는 주요 요소 중의 하나가 효율이다. 여기서 효율이라 함은 제작된 소자에 전기 적 에너지를 공급해 주었을 때 광에너지로 변화해 주 는 정도를 나타낸다. 이러한 LED 소자의 효율은 그림 1과 같이 내부양자효율, 외부추출효율, 패키지효율의 곱(LEDefficiency=ninjection×ninternal×nexternal×n package)으로 표현될 수 있다.

전류주입효율은 광자를 생성하는 활성층 내로 전자 및 정공이 주입되는 효율로 나타내며 금속 및 반도체 사이의 work function 차이에 의한 장벽에 의해 발생 하는 shottky barrier에 의해 영향을 받는다.

따라서 반도체와 금속층 사이에 Ohmic 접합의 구 성이 중요하다. 또한 주입된 전자 및 홀이 활성층으로 이동할 때 반도체 내의 밴드 구조 및 반도체 층의 저 항 등이 영향을 준다. 내부양자효율은 활성층으로 주 입된 전자와 정공이 비발광재결합 없이 발광 재결합 을 하는지의 효율을 나타낸다. 특히 결함에 의한 손실, 양자우물 구조의 설계 및 압전 효과에 의한 전자와 전 공 분포 외곡 등의 문제 해결이 중요하다.

광 추출 효율은 활성층에서 발생한 빛이 전반사에 의해 기판을 포함한 화합물 반도체 등 내부에 갇히게 되지 않고 외부로 빠져나오는지에 관한 효율을 나타 낸다. 또한 투명전극, 패키지 재료 등에 의해 발생한 빛이 흡수 되면 광추출 효율의 감소가 발생한다. 패키 지 효율을 소자화 된 LED의 발광 효율은 열방출 및 광학설계 등을 통하여 극대화시킬 수 있다.

그림 1. LED 효율과 에피 박막성장, 칩 제조 및 패키 징 공정

LED 소자의 효율을 높이기 위해서는 내부 양자 효 율 및 광 추출효율 개선이 필요하다. 고출력 chip에 서 기존 조명을 대체 할 만큼 경쟁력을 갖는 150 lm/W까지 성능을 얻기 위해서는 적어도 내부양자효 율 약 90%, 광 추출효율이 약 90%를 얻어야 가능하 다. 표 1은 향후 150lm/W를 얻기 위한 각 단계별 효 율을 나타낸다.

LED에서 광추출 효율이 낮은 원인은 LED 내부의 다중양자우물(multiquantum well)에서 발생한 빛 이 외부로 방출될 때. 질화갈류(굴절률=2.5)과 공기 (굴절률=1)와의 굴절률(refractive index) 차이로 인해 빛이 방출 될 수 있는 임계각(critical angle)이

감소하여 내부 전반사(total internal reflection)에 의한 빛의 손실이 발생하게 된다. 이는 LED의 광 추 출효율이 낮아지는 문제를 야기시키고 결국 LED의 광효율을 감소시키는 결정적인 원인을 제공한다.

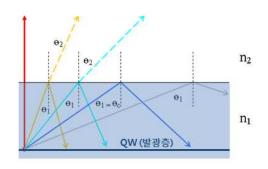

그림 2는 질화갈륨을 기반으로 하는 LED 내부에서 발생된 빛의 진행경로에 대한 개략도이며 Snell의 법 칙에 의한 계산과 같이 LED 내부에서 발생된 빛의 임 계각은 약 23°에 지나지 않으므로 발생된 빛의 극히 일부만 LED 밖으로 방출된다.

표 1. 150lm/W를 얻기 위한 백색 LED 성능 지표

| 구분                              | 150lm/W |

|---------------------------------|---------|

| Light extraction Efficiency (%) | 90      |

| Internal Quantum Efficiency (%) | 90      |

| External Quantum Efficiency (%) | 80      |

| Forward Voltage(V)              | 2.9     |

| Wall-Plug Efficiency(%)         | 75      |

From Snell's Law  $n_1 \sin \Theta_1 = n_2 \sin \Theta_2$  $\Theta_c = \sin^{-1}(n_2/n_1)$  $= 23.6^{\circ}$  $n_1(GaN) = 2.5$  $n_2(air) = 1$

그림 2. GaN에서 전반사 현상과 Snell's Law에 의해 계산된 임계각

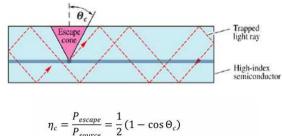

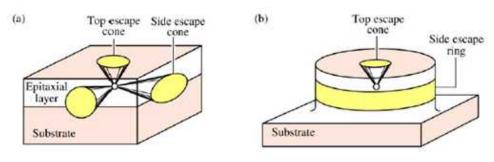

내부 전반사의 임계각은 탈출 콘(escape cone)에 의해 정의 될 수 있는데 탈출 콘 내부의 빛은 공기 중 으로 탈출할 수 있으나, 탈출 콘 외부로 진행하는 빛 은 내부 전반사를 겪으며 LED 내부에 갇혀 소멸 된 다. 이때 escape efficiency는 그림 3과 같이 계산 될 수 있으며 LED 내부에서 공기 중으로 빛이 진행 하는 경우 escape efficiency는 4.18%이고, LED 내부 에서 기판으로 사용되는 sapphire(굴절률=1.9)로 빛이 진행하는 경우 escape efficiency는 17.5%가 된다.

$$\approx \frac{1}{2} \left[ 1 - \left( 1 - \frac{{\Theta_c}^2}{2} \right) \right] = \frac{1}{4} {\Theta_c}^2 = \frac{1}{4} \frac{{n_0}^2}{{n_s}^2}$$

그림 3. GaN의 escape cone과 trapped light ray 의 예시와 escape efficiency의 계산 식

질화갈륨 발광다이오드의 경우, 높은 굴절율의 차 이 (n<sub>GaN</sub>=2.5, n<sub>air</sub>=1)로 인하여 내부양자효율에 비해 광추출 효율이 낮으며 이러한 문제점을 해결하기 위 하여 표면 거칠기, PSS(Patterned Sapphire substrate), Nanostructure, 광결정 (Photonic crystal) 등을 이용한 광추출 효율 향상 기술이 보고되고 있다.

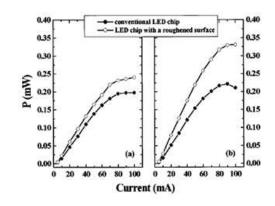

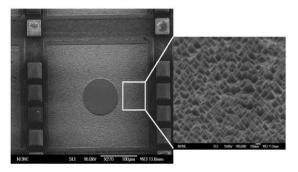

Surface texturing은 LED의 표면에 요철을 형 성시킴으로써 내부 전반사를 감소 시켜 광 추출 효율 을 향상 시킬 수 있으며 LED의 표면이 되는 p-GaN 에 metal cluster를 형성시켜 microroughening을 구현하는 방법이 소개된 바 있다. 그 결과 conventional LED 칩 보다 microroughened top surface LED칩의 light output power가 향상되었 으며 conventional LED 칩 대비 microroughened top surface LED의 light output power는 front side에서 52.4%, backside에서 30% 향상되었다.

그림 4. 두 가지 타입 LED 칩의 Output power.

(a) Backside에서 측정된 LED 칩의 utput power. (b) Front side에서 측정된 LED 칩 의 Output power.

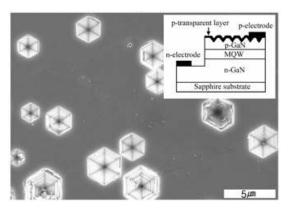

다른 방법으로는 KOH in ethylene glycol(KE) 용액을 이용하여 p-GaN 층을 선택적 wet etching 하는 연구가 진행된 바 있다. KE 용액을 이용한 p-GaN etching 표면은 그림 5과 같이 육각형의 etch pits이 발생하며, conventional LED 칩 대비 etched LED 칩의 light output power가 29.4% 향상되었다. 하지만 이러한 표면 요철 형성 기술은 p-GaN 층의 품질(quality)을 저하시켜 전기적 특성 저하에 원인이 될 수 있다.

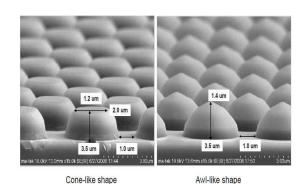

또한 LED의 광추출 효율을 향상시키기 위한 방법 으로 사파이어 기판 표면에 일정한 형태로 패터닝 (Patterning)하는 방법이 등장해 LED 내부에서 전 반사되어 소멸되는 빛을 굴절율과 반사각도 변화를 이용하여 광 추출 효율을 개선하기도 하였다. PSS 표면 가공 기술은 사파이어 기판 표면에 일정한 형태의 형상과 깊이로 패터닝을 식각하여 사파이어 기판 쪽 으로 진행하는 빛이 산란되게 함으로 내부에 갇히지 않고, 추출될 수 있는 확률을 높여 준다. 일반적으로 라인, 메쉬, 반구 형태의 굴곡을 사파이어 표면에 형 성한다. 그림 6은 반구 형태의 굴곡 이미지를 보여준다.

그림 5. KE 용액으로 etching 된 p-GaN 표면의 SEM 이미지

그림 6. PSS 의 SEM 이미지

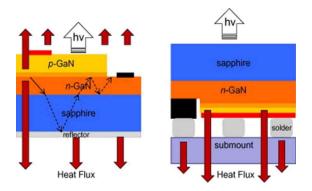

플립칩 LED는 수평형 LED의 단점을 일부분 보완 한 구조이다. 그림 7은 플립칩 LED의 단면 구조를 보여준다. 플립칩 LED의 기본 구조는 수평형 LED 칩을 submount에 본딩 한다는 점이 크게 다른다. n-GaN과 p-GaN의 접촉은 각각 submount사이 솔 더를 형성함으로써 만들어 진다. 플립칩은 n-GaN 표면위에 반사막을 형성하기 때문에 MQWs에서 생 성된 광자중 submount쪽으로 향하는 광자를 다시

반사시켜 외부로 방출하는 역할을 한다. 플립칩에 존 재하는 반사막과 사파이어의 굴절률이 GaN 층보다 낮기 때문에 임계각이 커지게 되어 광추출 효율이 향 상된다는 장점을 갖는다.

또한 submount 물질로 열전도도가 좋은 금속 기 판이나 실리콘 기판을 사용함으로써 MQWs에서 발 생한 열을 외부로 빼주는데 용이 하다. 이로 인하여 수평형 LED보다는 공정은 조금 복잡하지만 높은 광 출력과, 열에도 안정적인 LED를 제작 할 수 있다는 장점이 있다. 하지만, 플립칩 LED도 여전히 전류 밀 집현상이나 식각 공정 시에 발생하는 MQWs의 면적 감소 등의 문제점은 여전히 남아있어. 대면적 LED 칩이나 고출력 LED칩을 제작 할 시 극복해야할 문제 점들이 남아있다.

그림 7. 수평형 구조와 플립칩 구조 단면도 및 빛과 열 의 방출 메커니즘

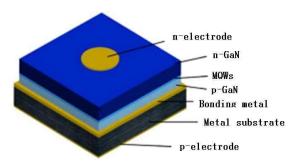

한편, 수직형 LED는 수평형 LED의 구조적인 문 제를 상당부분 극복한 구조이다. 수직형 LED는 고출 력 LED 칩을 제작 할 때 사용되며, 그림 8는 수직형 LED의 단면 구조를 보여준다. 수직형 LED의 구조 에서 가장 큰 변화는 사파이어 기판이 제거되었다는 점이다.

그림 8. 수직 구조를 갖는 수직형 LED의 단면도

사파이어 기판은 Laser Lift Off (LLO)를 통해 제거되며 n-GaN이 노출된다. 사파이어 기판대신 GaN layer를 지지해줄 기판으로 submount가 사용 되었으며, 재료는 금속, 실리콘, 세라믹 등을 사용한 다. 열전도도와 전기전도도가 높은 물질을 사용함으 로써 외부로의 열 방출 특성이 우수하며, submount를 통하여 p-GaN으로 전공을 공급할 수 있다.

또한 n-GaN 전극과 p-GaN 전극이 수직 방향에 존 재하고 있어서 전류가 수직방향으로 흐르게 되고 이 때문에 앞에서 언급했던 전류 밀집 현상을 상당부분 극복할 수 있다. 한편 p-GaN층에 은(Ag)을 기반으로 하는 반사막을 형성함으로써 submount로 향하는 광 자의 대부분을 다시 위로 반사시켜 외부로 방출하게 하여 광 추출 효율이 상승하며 n-GaN을 노출시키기 위한 식각공정이 없기 때문에 실직적인 Active layer 인 MQWs의 면적 손실을 피할 수 있다. 이러한 이유 로 수직형 LED는 대면적, 고효율 LED 칩을 만들기에 적합하다. 수직형 LED는 수평형 LED박막을 위아래 반전 시켜 놓았기 때문에, 위로 노출된 면이 질소면 (N-face)이 된다.

평평한 GaN의 질소면은 그림 9과 같이 식각 공정 을 사용하여 쉽게 뿔(cone)을 형성 할 수 있다. 형성 된 뿔은 특정한 패턴이 없으며, 크기와 높이가 각각 다른 모습을 취한다. 표면에 뿔을 형성 시키면, 광자 가 외부로 빠져나갈 수 있는 각도를 넓혀주어 광 추출 향상에 많은 도움이 된다.

그림 9. 식각을 이용한 n-GaN 표면 뿔(cone) 생성

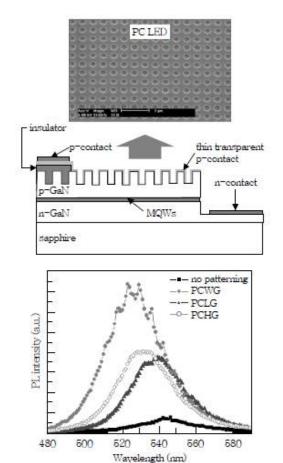

그림 10. Photonic Bandgap Crystal의 구조와 발광 효율 증가 그래프

광결정(Photonic crystal) PBC(Photonic Band gap Crystal) 기술은 p-GaN 표면에 Photonic Band gap이

그림 11. Geometric shape의 변화에 따른 escape cone의 변화

그림 12. 사각형, 삼각형, 평행사변형에서 진행하는 light ray의 변화 양상

있는 광결정구조를 형성하여 빛의 경로를 제어함으로 써 광추출 효율을 크게 증가시키는 기술이다. 이 방법 은 p-GaN 전극 접촉 부분으로 방출되는 파장을 고려 한 이론적 설계를 바탕으로 나노 형상의 주기적 패턴 을 다양한 나노 패터닝 방법과 ICP-RIE 식각 공정에 의하여 형성한다. 그림 10에서는 PBC 기술을 포함한 LED의 구조와 발광 효율의 향상 그래프를 보여주고 있다.

이때, 최대 광 추출 효율은 패턴 깊이와 크기에 의 해 결정되지만 전기적 특성까지 개선되는 것은 아니 며, p-GaN 층의 낮은 전기 전도도에 의해 광 추출 효 율 면에서는 일정 두께 이상을 요구하지만 동작 전압 등과 같은 전기적 특성을 고려한 최적의 설계 조건이 필요하다. 청색 LED 소자의 경우 광 추출 효율을 최 대 30% 이상 증가시킬 수 있지만 현재 상용화가 이루 어지지 않고 있으며, 향후 고휘도/고출력 LED 성능 향상을 위해 기술 개발이 필요하다.

# 3. Chip Shaping 기술을 이용한 다각형 LED

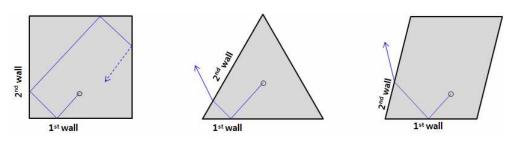

앞에서 소개한 봐와 같이 광추출 효율을 증가시 키기 위해 표면 거칠기, PSS, 광결정 등 많은 방 법이 있다. 하지만 대부분 표면으로 진행하는 빛의 탈출이나 빛의 경로를 바꾸는데만 초점을 맞추고 있고 측면으로 진행하는 빛을 제어하여 탈출 시키 는 기술은 부족하다. 예를들어 그림 11과 같이 기 존의 사각형 칩의 모양이 다른 형태로 변하게 되면 임계각의 형태도 변하게 된다. 칩의 모양이 원기둥 형태로 변하게 된다면 그 칩의 임계각은 그림 11 (b)의 형태로 변하게 된다. 이를 통해 측면 방향으 로 광자의 탈출 효율이 크게 증가하는 것을 알 수 있다.

LED 칩의 모양이 삼각형. 평행사변형. 오각형 그 리고 육각형의 모양으로 변하게 되면, 그림 12에서 2nd wall의 각이 변하여 사각형 칩에서는 전반사가 일어나던 조건에서 다각형 칩에서는 전반사 일어나지 않는 현상을 관찰 할 수 있다. 즉 LED 칩의 side wall angle이 변함에 따라 내부 전반사가 일어날 수 있는 확률을 낮추어 LED 칩의 광 추출효율 향상에 기인 할 수 있다.

사각형 칩 보다 각이 증가하게 되는 오각형과 육각 형의 경우 모서리 wall의 증가로 인해 모서리 wall에 서의 광 추출이 증가하게 된다. 즉, LED 칩의 발광층 에서 모서리 wall로 향하는 방향을 갖는 빛은 내부 전반사의 영향을 거의 받지 않으며, 모서리 wall이 증가하는 만큼 광 추출의 확률을 증가시킬 수 있다. 삼각형의 경우 모서리 wall의 개수가 감소하게 되지 만, 모서리 angle이 90°보다 작아짐에 따라 모서리 wall 부근의 발광층에서 발생된 빛의 critical angle 이 증가하여 광 추출 확률이 증가된다.

먼저, chip shape에 따른 광 추출효율을 알아보기 위하여 삼각형, 사각형, 오각형, 육각형의 총 4가지 shape에 대한 시뮬레이션을 하였다. 시뮬레이션에 사용된 LED의 구조는 실제 실험을 위해 제작한 LED와 동일한 구조로 설계하였다. 표 2는 다각형 LED의 광 추출효율과 그 증가값을 정리한 결과이다. 여기서 emitted power는 활성층에서 발광하는 빛이 고 collected power 는 LED 밖으로 탈출한 빛을 말 한다. 이 비율을 가지고 LED 구조의 광추출 효율을 구하였다. 시뮬레이션 결과 사각형 LED보다 다각형 LED에서의 광 추출효율이 더 높은 것을 확인 할 수 있다.

표 2. 다각형 LED의 광추출 효율

|            | Emitted power | Collected power | System efficiency |

|------------|---------------|-----------------|-------------------|

| Quadrangle | 0.4 W         | 0.0955 W        | 23.88%            |

| Triangle   | 0.4 W         | 0.1155 W        | 28.88%            |

| Pentagon   | 0.4 W         | 0.1124 W        | 28.10%            |

| Hexagon    | 0.4 W         | 0.1159 W        | 28.89%            |

일반적으로 사용하는 2 inch wafer에서 사각형 LED를 제작할 경우 가로, 세로 방향으로 scribing 을 하여 사용할 수 없는 영역(Dead space)없이 2 inch wafer 전체를 사용할 수 있다. 하지만 다각형 칩의 특성상 여러 방향으로 scribing을 진행해야 하 는 구조적 한계가 있다. 이에 따라 육각형 LED에서 는 약 33 % 의 dead space, 오각형 LED는 약 50 % 이상의 dead space가 발생하게 된다. 하지만 삼 각형 LED의 경우 가로, 세로, 대각선 방향으로 scribing을 하기 때문에 사각형 LED와 같이 dead space가 없이 칩 분리가 가능하다는 장점이 있다.

따라서 본 연구에서는 삼각형과 사각형 LED의 특 성을 비교하였다. 그림 13은 사각형과 삼각형 LED 의 전류-전압 곡선 및 입력 전류에 대한 광출력 결과 를 보여준다. 그림에서 보는 것처럼 전기적 특성 및 전류 주입 및 퍼짐 특성은 거의 비슷한 것을 알 수 있 고 광출력이 크게 증가되는 것을 알 수 있다.

그림 13. 사각형과 삼각형 LED의 전류-전압 곡선 및 입력 전류에 대한 광출력 결과

이렇게 삼각형 LED가 사각형 LED에 비해 광효율 이 크게 증가된 이유는 측면으로 추출된 빛의 양이 크 게 증가했기 때문이다. 따라서 측면으로 진행하는 빛 을 효율적으로 꺼내는 것은 광추출 효율을 높이는데 매우 중요한 기술이라고 판단된다.

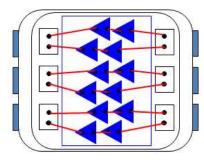

## 4. 다각형 LED을 이용한 멀티셀 패키지 기술

멀티셀 LED 패키지는 그림 14와 같이 고출력을 내 기 위한 대면적 chip이 가지는 열에 의한 휘도 및 수 명 감소, 신뢰성 등의 문제점을 해결하기 위해 작은 크기의 chip 을 여러 개 어레이 형태로 배열함에 따라 광휘도의 향상과 더불어 저전류 구동으로 인해 열이 감소되어 수명 개선 및 신뢰성의 장점을 가지는 패키 지이다. 특히 다각형 chip의 경우 전극 방향을 다양하 게 조절 할 수 있고, 다양한 모양으로 배열이 가능하 여 멀티셀 패키지에 적합하다.

그림 14. 표면 실장용 멀티셀 다각형 LED 패키지

그러나 기존 사각형 chip 에 비해 넓은 측면 배광 을 갖기 때문에 효율을 최적화하기 위해서는 패키지 의 디자인, 형광체의 특성 및 분포가 중요하다. 또한 충분히 빛을 꺼낼수 있는 굴절률과 모양을 갖는 봉지 재가 중요하다. 신뢰성 개선을 위해서는 고내열성 봉 지재 기술, 고열전도성 접착제 기술, 봉지/접착제 고 분자합성 기술 등을 들 수 있는데 열적, 광적 안정성 이 떨어질 경우 형광체를 이용한 백색 LED의 수명에 영향을 주게 되며 LED 봉지재의 투과율은 패키지의 효율 및 최종 제품의 신뢰성에 직접적인 영향이 있는 만큼 이를 해결하기 위한 노력이 필요하다.

한편, 다이 본딩을 위해서는 열전달 특성의 개선을 위해 에폭시에 은 분말을 혼합하는 형태 및 Au-Sn 고 온 솔더 형태의 원천 기술과 리드프레임의 Bonding

기술, 수분에 의한 신뢰성 문제도 해결해야할 과제이 다. 고연색성을 확보하기 위해서는 녹색/황색 형광체 기술과 적색 형광체 합성 기술, 양자점/나노/glass ceramic 형광체 기반 기술의 확보가 필요하다.

향후 최적의 광학, 회로 디자인, 방열 설계를 기반 으로 고연색 멀티셀 다각형 LED 패키지를 이용한 다 양한 분야의 ICT융복합 조명의 개발이 예상된다.

#### 참고문헌

- [1] S. Nakamura and G. Fasol, The Blue Laser Diode: GaN based Light Emitter and Laser, Springer, Berlin (1997).

- (2) E. Fred Schubert, Light-Emittind Diodes (2003).

- (3) Eunjin Jung, Seongjun Kim, and Hyunsoo Kim, "Effects of Temperature on Current Crowding of GaN-Based Light-Emitting Diodes, IEEE Electron Device Letters, 34, 277 (2013)

- [4] H. Kim, S-I. Park, H. Hwang, and N.-M. Park, "Lateral current transport path, a model for GaN-based lightemitting diodes: Applications to practical device designs", Appl. Phys. Lett., 81, 1326 (2002).

- (5) O. B. Shchekin, J. E. Epler, T. A. Trottier, T. Margalith, D. A. Steigerwald, M. O. Holcomb, P. S. Martin, and M. R. Krames, "High performance thin-film flip-chip InGaN-GaN light-emitting diodes" Appl. Phys. Lett., 89, 071109 (2006).

- [6] H. S. Kim, K. K. Kim, K. K. Choi, H. K. Kim, J. O. Song, J. H. Cho, K. H. Baik, C. S. Sone, Y. J. Park, and T. Y. Seong, "Design of high-efficiency GaN-based light emitting diodes with vertical injection geometry" Appl. Phys. Lett., 91, 023510 (2007).

- [7] Chih-Chiang Kao, H. C. Kuo, K. F. Yeh, J. T. Chu, W. L. Peng, H.W. Huang, T. C. Lu, and S. C. Wang, "Light-Output Enhancement of Nano-Roughened GaN Laser Lift-Off Light-Emitting Diodes Formed by ICP Dry Etching" IEEE Photon Technol. Lett., 19, 11 (2007).

- [8] W. K. Wang, D. S. Wuu, S. H. Lin, P. Han, R. H. Horng, T. C. Hsu, D. T. C. Huo, M. J. Jou, Y. H. Yu, and A. Lin, "Efficiency improvement of near-ultraviolet InGaN LEDs using patterned sapphire substrates" IEE Quantum Electronics., 41, 11 (2005).

- [9] C. Huh, K. S. Lee, E. J. Kang, and S. J. Park, "Improved light-output and electrical performance of InGaN-based light-emitting diode by micririughening of the p-GaN surface" J. Appl. Phys., 93, 9383 (2003).

- (10) Seok-In Na, Ga-Young Ha, Dae-Seob Han, Seok-Soon Kim, Ja-Yeon Kim, Jae-Hong Lim, Dong-Joon Kim, Kyeong-Ik Min, and Seong-Ju Park, "Selective Wet Etching of p-GaN for Efficient GaN-Based Light-Emitting Diodes" IEEE Photon Technol. Lett., 18, 1512 (2006).

- [11] Ja-Yeon Kim, Min-Ki Kwon, Jae-Pil Kim, and Seong-Ju Park "Enhanced Light Extraction From Triangular GaN-Based Light-Emitting Diodes" IEEE Photon Technol. Lett., 19, 1865

- [12] Stuart E. Brinkley, Charistopher Lalau Keraly, Junichi Sonoda,

#### 특집: LED · ALED조명 및 BIPV 숲·복합 기술 동향

Claude Weisbuch, Jim S. Speck, Shuji Nakamura, and Steven P. DenBaars "Chip Shaping for Light Extraction Enhancement of Bulk c-Plane Light- emitting Diodes" Applied Physics Express, 5, 032104 (2012).

- [13] J. Y. Kim, M. K. Kwon, S. J. Park, S. H. Kim, and K. D. Lee, "Enhancement of light extraction from GaN-based green light-emitting diodes using selective area photonic crystal," Appl. Phys. Lett., 96, (2010).

- [14] "Enhanced light extraction of GaN based blue light-emitting diode with SiO2/ITO photonic crystal structure", M. K. Kwon, J. Y. Kim, K. S. Kim, G. Y. Jung, W. Lim, S. T. Kim and S. J. Park, ECS J. Solid State Sci. Technol., 2, 13 (2012).

#### ◇ 저 자 소 개 ◇─

#### 김자연(金孶娟)

1978년 3월 9일생. 2002년 2월 전북대학 교 신소재공학과 졸업. 2004년 2월 전 북대학교 반도체과학기술학과 졸업(석 사). 2008년 8월 광주과학기술원 신소재공

학과 졸업(박사) 2008년 10월~2011년 1월 박사 후 연구 원(Univ. of California, Davis). 2011년 2월~현재 한국광기 술원 차세대소자연구센터 선임연구원.

주요관심분야: LED 소자 및 패키지, 차세대 광원, 나노

공정 기술 개발, 유연 소자

E-mail: jykim@kopti.re.kr

#### 권민기(權珉沂)

1979년 2월 16일생. 2001년 2월 전북 대학교 화학공학과 졸업. 2003년 2월 전북대학교 반도체과학기술학과 졸업 (석사). 2008년 2월 광주과학기술원

신소재공학과 졸업(박사). 2008년 2월~8월 박사 후 연구 원(광주과학기술원). 2008년 10월~2010년 2월 박사 후 연 구원(Univ. of California, Davis). 2010년 3월~현재 조선 대학교 광기술공학과 교수.

주요관심분야: LED 소자 및 패키기, 차세대 조명 및 나 노 소자

#### 안종욱(安鍾煜)

1960년 3월 17일생. 1988년 2월 원광 대학교 전자공학과 졸업. 1999년 2월 전북대학교 경제학과 졸업(석사). 1987~2002년 (주)한국고덴시 관리총

괄이사. 2002~ 2003년 (주)나노반도체코리아 전무이사. 2003년~현재 엘이디에스티(주) 대표이사. 2013년 12월 차세대 세계일류상품 인증.

주요관심분야: 초고연색 LED 및 파워소자, 의료용, 식 물성장용, UV, IR, 근자외광 백색소자 및 기타 특수 LED

#### 박노준(朴魯埈)

1968년 5월 21일생. 1993년 2월 원광대 학교 전자공학과 졸업. 2004년 8월 원광 대학교 전자공학과 졸업(박사). 1995~ 2011년 원광대학교 공과대학 강사. 2006

~2011년 전기응용신기술연구센터 연구교수. 2010~2011년 CMD, ICAE 조직위원. 2011~2012년 한국조명연구원 선임연구원. 2012년~현재 전라북도 과학기술위원. 2012 년~현재 엘이디에스티(주) 부설연구소장.

주요관심분야 : LED융복합기술, 열해석, Bluetooth LE/NFC 마이크로로케이션 및 메타물질