# A 12b 100 MS/s Three-Step Hybrid Pipeline ADC Based on Time-Interleaved SAR ADCs

Jun-Sang Park<sup>1</sup>, Tai-Ji An<sup>1</sup>, Suk-Hee Cho<sup>1</sup>, Yong-Min Kim<sup>1</sup>, Gil-Cho Ahn<sup>1</sup>, Ji-Hyun Roh<sup>2</sup>, Mun-Kyo Lee<sup>2</sup>, Sun-Phil Nah<sup>3</sup>, and Seung-Hoon Lee<sup>1</sup>

Abstract—This work proposes a 12b 100 MS/s 0.11 um CMOS three-step hybrid pipeline ADC for highspeed communication and mobile display systems requiring high resolution, low power, and small size. The first stage based on time-interleaved dualchannel SAR ADCs properly handles the Nyquist-rate input without a dedicated SHA. An input sampling clock for each SAR ADC is synchronized to a reference clock to minimize a sampling-time mismatch between the channels. Only one residue amplifier is employed and shared in the proposed ADC for the first-stage SAR ADCs as well as the MDAC of back-end pipeline stages. The shared amplifier, in particular, reduces performance degradation caused by offset and gain mismatches between two channels of the SAR ADCs. Two separate reference voltages relieve a reference disturbance due to the different operating frequencies of the front-end SAR ADCs and the back-end pipeline stages. The prototype ADC in a 0.11 µm CMOS shows the measured DNL and INL within 0.38 LSB and 1.21 LSB, respectively. The ADC occupies an active die area of 1.34 mm<sup>2</sup> and consumes 25.3 mW with a maximum SNDR and SFDR of 60.2 dB and 69.5 dB. respectively, at 1.1 V and 100 MS/s.

Index Terms—Analog-to-digital converter (ADC), pipeline, time-interleaved, hybrid, SAR ADC

E-mail: hoonlee@sogang.ac.kr

### I. Introduction

The development of multimedia consumer electronics and communication systems enables the implementation of high-definition (HD) quality videos on mobile devices. Those systems require essentially analog-to-digital converters (ADCs) with a resolution of 12b level and a conversion rate exceeding 75 MS/s to convert analog signals including RGB information into digital signals. Pipeline ADCs have been used to meet these specifications [1-5]. In the conventional pipeline ADCs, a dedicated input sample-and-hold amplifier (SHA) has been employed to reduce a sampling-time mismatch between the first-stage multiplying digital-to-analog converter (MDAC) and the flash ADC. For low power and small chip area, various SHA-free pipeline ADCs have been proposed [6-12]. However, previously reported SHA-free ADCs partially resolve the problems by a sampling-time mismatch with extra digital logic or inventive layout techniques for sampling networks.

Successive-approximation register (SAR) ADCs properly process high-frequency input signals without a SHA due to the built-in sample-and-hold function. However, the internal clock speed for the SAR logic is proportionally increased with a required resolution. In conventional 12b SAR ADCs, the internal clock operates 13 times as fast as the conversion rate of the overall ADC. The resulting insufficient sampling, holding, and signal-settling times strictly limit the conversion rate [13-16]. Meanwhile, since the number of capacitors in the SAR ADCs is increased exponentially with a resolution, a unit capacitor size needs to be scaled down to reduce the die area. But using a small unit capacitor leads to linearity

Manuscript received Jun. 4, 2013; accepted Jan. 16, 2014

<sup>&</sup>lt;sup>1</sup> Department of Electronic Engineering, Sogang University, Seoul, Korea.

<sup>&</sup>lt;sup>2</sup> Samsung Thales Co., Ltd, Yongin, Korea.

<sup>&</sup>lt;sup>3</sup> Agency for Defense Development, Daejeon, Korea

degradation, caused by the parasitic capacitance and capacitor mismatch [13]. Recently, a two-step pipelined SAR ADC has been proposed to overcome the limitations of conversion rate and linearity, but it is still difficult to apply directly to high-speed conversion [17].

The proposed 12b 100 MS/s hybrid pipeline ADC employs dual-channel time-interleaved 4b SAR ADCs in the front-end stage for 4 most significant bits (MSBs) while single-channel pipeline back-end stages decide 8 least significant bits (LSBs). The dual-channel and timeinterleaving configuration with a 4b resolution enables the SAR ADCs properly to process the Nyquist-rate input without a SHA during a half clock period of 100 MHz level. The proposed ADC employs and shares only one amplifier for the residue amplifiers of the first-stage SAR ADCs as well as the MDAC of the remaining pipeline stages. Particularly, the shared residue amplifier for the dual-channel SAR ADCs reduces performance degradation due to offset and gain mismatches between the channels with small chip area and low power consumption.

The input sampling clock for the dual-channel SAR ADCs is synchronized to a reference clock to minimize a sampling-time mismatch. However, the different operating frequencies of the front-end SAR ADCs and the back-end pipeline stages can result in disturbance of on-chip reference voltages. The reference disturbance is considerably relaxed by separating only reference voltage drivers, while other reference current and voltage functional blocks are shared to minimize a mismatch between two reference voltages. On-chip clock circuits generating 400 MHz for the SAR ADCs are internally implemented for various system applications.

This paper is organized as follows. The architecture and operation of the proposed hybrid pipeline ADC are briefly described in Section II. The proposed design techniques and detailed circuit implementation are discussed in Section III. The measured results of the prototype ADC are summarized in Section IV and the conclusion is given in Section V.

### II. ARCHITECTURE

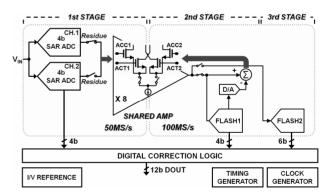

The proposed 12b 100 MS/s three-step hybrid pipeline ADC based on time-interleaved SAR ADCs is shown in Fig. 1. The proposed ADC consists of two 4b SAR

ADCs, a single shared amplifier, 4b and 6b flash ADCs (FLASH1, FLASH2), a 4b MDAC, a digital correction logic (DCL), on-chip current and voltage references, a timing circuit, and an on-chip clock generator. The internally generated 400 MHz clock is used for SAR operation of the 50 MS/s SAR ADCs, to decide 4b digital codes during a half period of 50 MHz. The 4b 50 MS/s digital codes from the first-stage dual-channel SAR ADCs are combined into 4b 100 MS/s digital codes in the DCL.

An interpolation technique is applied to both of the two flash ADCs, and a two-step reference selection scheme is used in the back-end FLASH2 to enhance power efficiency and reduce chip area [18, 19].

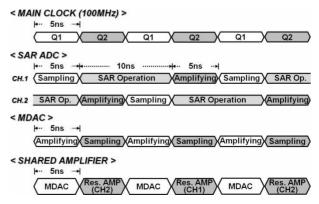

The timing diagram of major circuit blocks such as SAR ADCs, an MDAC, and a shared amplifier is shown in Fig. 2. Since the first stage of the proposed ADC is implemented as the SAR ADCs with dual-channel, time-interleaving, and 4b-resolution characteristics, there is enough room for sampling and holding times compared to the conventional single-channel high-resolution high-speed SAR ADCs.

The shared amplifier operates for the second-stage

Fig. 1. Proposed 12b 100 MS/s hybrid pipeline ADC.

Fig. 2. Timing diagram of major functional circuit blocks.

MDAC during every Q1 phase, and as residue amplifiers for the first-stage dual-channel SAR ADCs alternately during Q2 phase. Since a single amplifier with the same operating condition is shared for residue amplification of the dual-channel SAR ADCs, performance degradation caused by offset and gain mismatches between channels is minimized.

Each channel of the SAR ADCs samples an analog input during Q1 phase by turns and converts the sampled analog input to 4b digital codes through SAR operation. A residue voltage of the first-stage SAR ADC is generated after SAR operation. The shared amplifier amplifies this residue voltage by 8, and transfers it to the second-stage FLASH1 and MDAC during Q2 phase. The other processes are the same as the conventional pipeline ADCs.

### III. CIRCUIT DESCRIPTION

### 1. Proposed Time-Interleaved SAR ADCs

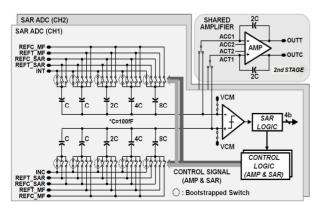

For sufficient sampling and holding times at 100 MHz, time-interleaved dual-channel SAR ADCs are employed in the first stage of the proposed ADC, as shown in Fig. 3.

The performance of time-interleaved ADCs tends to be degraded by a sampling-time mismatch between channels. To solve this drawback, the proposed SAR ADCs employ a single clock-edge sampling scheme which synchronizes the falling edge of a sampling clock in each channel with an external 100 MHz reference clock. A clock skew between the external 100 MHz reference clock and the internally generated 50 MHz clock is relaxed by well-matched symmetrical layout and circuit design strategy, instead of using additional delay

Fig. 3. Time-interleaved dual-channel SAR ADCs.

control circuits as discussed in [20]. In addition, two pairs of reference voltages are selectively used for stable operation of the reference voltage circuits; one reference voltage pair (REFT\_SAR, REFC\_SAR) for low-resolution and high-speed SAR operation, the other (REFT\_MF, REFC\_MF) for high-resolution and nominal-speed residue amplification.

The input switches of the first-stage SAR ADCs with a gate-bootstrapping circuit sample a front-end analog input signal with low distortion and minimize a sampling mismatch between two channels. By adopting a pipeline topology at the back-end stages, the first-stage SAR ADCs only handle a 4b resolution. Thus, the number of the required unit capacitors is much smaller than that of the conventional high-resolution SAR ADCs. As a benefit of using the pipeline architecture, a sufficient large unit capacitor (100 fF) is used, considering the kT/C noise, instead of using an excessively small-sized unit capacitor for small chip area. As a result, the potential linearity degradation coming from the capacitor mismatch and parasitic capacitance of the SAR ADCs is alleviated.

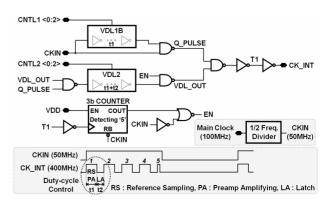

A 400 MHz high-speed clock is needed in the proposed dual-channel SAR ADCs to decide 4b digital codes during a half period of a 50 MHz clock. The 400 MHz clock is internally generated by the on-chip clock generator, as shown in Fig. 4. Based on the 1/2 frequency divider, a 50 MHz clock, CKIN, is generated and synchronized to an external 100 MHz main clock. For the required SAR operation, a 400 MHz clock, CK\_INT, is created by the CKIN, two simple delay cells of VDL1B and VDL2, and some digital logic gates. The 3b counter terminates clock generation immediately after detecting the fifth rising edge of the CK INT, which

Fig. 4. Proposed on-chip clock generator for 4b SAR ADCs.

indicates the completion of SAR operation. Moreover, a reference-sampling (RS) and preamp-amplifying (PA) time,  $t_1$ , is configurable with the CNTL1<0:2>, while a time interval of the CK\_INT,  $t_1$ + $t_2$ , is controlled with the CNTL2<0:2> for more stable SAR ADC operation.

### 2. Single Shared Amplifier for two SAR ADCs and one MDAC

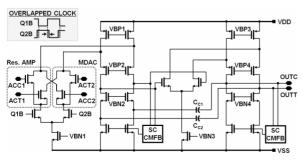

The shared amplifier in the proposed ADC has a twostage folded-cascode topology with a swing range over 1 Vp-p, a high DC gain, and two input differential pairs to properly deal with three operation modes, as shown in Fig. 5. The three operation modes consist of two residue amplifications for the SAR ADCs and one residue amplification for the MDAC.

The matching characteristic is not so much critical between residue amplifiers in the first stage and an amplifier of the second-stage MDAC. However, the mismatch between two residue amplifiers in the firststage SAR ADCs can cause some serious performance degradation. The mismatch in the time-interleaving structures primarily consists of offset and gain mismatches of amplifiers [8]. The problems are fairly removed in the proposed ADC by sharing a single amplifier with the same input differential pair. In the common case of using three input differential pairs for three different operation modes of two SAR ADCs and one MDAC, separate 50 MHz clock lines and switches are required to select each input pair with separate feedback capacitors. In the proposed ADC, only two input differential pairs are employed in the amplifier for three operation modes; one shared input differential pair for residue amplifications of the dual-channel SAR ADCs in the first stage (ACC1, ACT1), and the other input differential pair for the second-stage MDAC

Fig. 5. Shared two-stage amplifier of the proposed ADC.

(ACC2, ACT2), as shown in Figs. 3 and 5. No more extra circuit is required in the shared amplifier, minimizing the mismatch that may occur between two channels. The input differential pairs of the shared amplifier are turned on and off alternately, by using the switches with slightly overlapped clocks, Q1B and Q2B, to prevent the input differential pairs from turning off simultaneously.

## 3. On-chip Reference with Separate Drivers to Isolate High-speed Switching Noise from the SAR ADCs

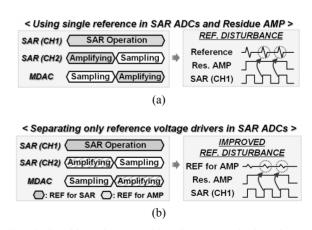

The proposed hybrid pipeline ADC operates with two different clock frequencies; one for the dual-channel SAR ADCs with high-speed operation of 400 MHz, and the other for residue amplifications with high-resolution and nominal-speed operation of 100 MHz. In the case of sharing a single reference voltage, as observed in usual pipeline ADCs, a reference disturbance problem can occur due to high-speed SAR switching noise during residue amplification, as shown in Fig. 6(a). The reference voltage during residue amplification needs to be settled within a half LSB of a 12b resolution in a half period of a 100 MHz clock. However, the switching noise by high-speed operation of the SAR ADCs directly affects the reference voltage for residue amplification. The proposed separate reference voltage techniques considerably reduce the reference disturbance, as shown in Fig. 6(b).

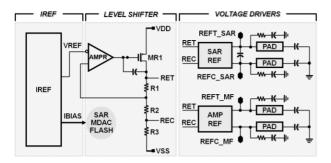

To minimize the mismatch between the reference voltages for SAR operation and residue amplifications, a current reference generator (IREF) and a level shifter are

**Fig. 6.** On-chip reference with using (a) a single reference voltage, (b) separating reference voltage drivers.

Fig. 7. On-chip reference circuit with separate voltage drivers.

shared, and only reference voltage drivers are separated, as shown in Fig. 7. The signal settling targets of the reference voltages for the SAR ADCs and the MDAC are much different, which are a 4b accuracy at 400 MHz and a 12b accuracy at 100 MHz, respectively. Considering the different operation targets, apart from a small-sized on-chip RC filter at each reference output node, an extra decoupling capacitor of 150 pF is added between the output nodes, REFT\_SAR and REFC\_SAR, of the reference voltage drivers for high-speed SAR operation.

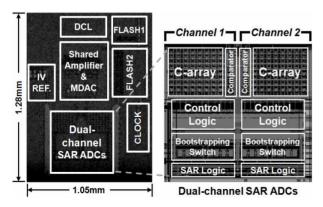

#### IV. MEASUREMENT RESULTS

The prototype 12b 100 MS/s ADC is implemented in a 0.11  $\mu m$  CMOS technology, as shown in Fig. 8. The ADC occupies an active die area of 1.34 mm², including on-chip MOS decoupling capacitances of 500 pF to stabilize supply and reference voltages. The proposed dual-channel SAR ADCs are laid out adjacently and symmetrically to minimize not only offset and capacitor mismatches, but also a sampling-time mismatch between channels without any calibration scheme.

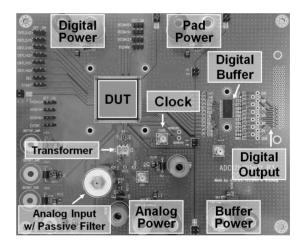

An evaluation board to measure the performance of

**Fig. 8.** Die photo of the prototype ADC and layout of the dual-channel SAR ADCs.

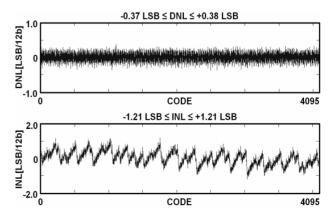

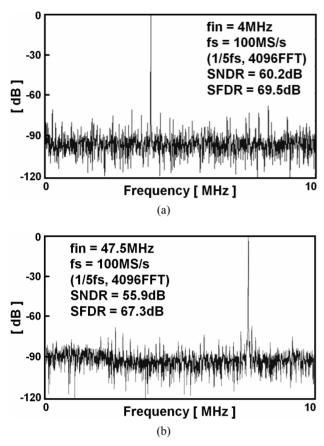

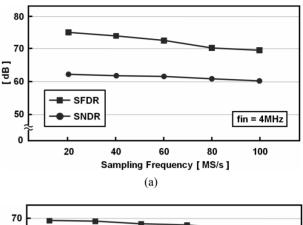

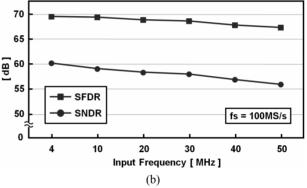

the prototype ADC is shown in Fig. 9. Passive filters and a transformer are employed just before an analog input terminal of the ADC to reduce the undesired noise and harmonics of a signal generator and to convert a singleended input signal into a differential signal. Separate power supplies for analog and digital circuits are used to minimize the signal interference caused by the digital supply noise. The prototype ADC dissipates 25.3 mW at 100 MS/s with a 1.1 V supply voltage. The measured differential non-linearity (DNL) and integral nonlinearity (INL) are within 0.38 LSB and 1.21 LSB, respectively, as shown in Fig. 10. Signal spectrums at 100 MS/s with an input sine wave of 4 MHz and 47.5 MHz, respectively, are plotted in Fig. 11. Digital outputs are down-sampled by a factor of 5 with the on-chip decimator to reduce the influence of noise from the measurement board during high-speed operation. The signal-to-noise-and-distortion ratio (SNDR) and the spurious-free dynamic range (SFDR) in Fig. 12(a) are

Fig. 9. Evaluation board for the prototype ADC.

Fig. 10. Measured DNL and INL of the prototype ADC.

**Fig. 11.** Measured FFT spectrums of the ADC at 100 MS/s with (a) fin of 4 MHz, (b) fin of 47.5 MHz (1/5 fs down sampled).

measured with sampling frequencies from 20 MS/s to 100 MS/s for a differential sinusoidal input frequency of 4 MHz. While a sampling frequency increases to 100 MHz, the SNDR and SFDR are maintained above 60.2 dB and 69.5 dB, respectively. The SNDR and SFDR variations with increasing input frequencies at a sampling rate of 100 MS/s are illustrated in Fig. 12(b). The SNDR and SFDR are maintained over 55.9 dB and 67.3 dB at the Nyquist input frequency. The SNDR decreases by approximately 4 dB at the Nyquist input frequency compared with the SNDR at the 4 MHz input. The main sources of the SNDR degradation are clock jitter, skew, or distortion caused by signal-dependent delay and finite aperture time [21].

The overall ADC performance is summarized in Table 1, and previously reported 12b SAR ADCs and pipeline ADCs are compared with the proposed hybrid pipeline ADC in Table 2. The figure of merit (FoM), defined as (1), of the prototype ADC is 0.50 pJ/conversion-step, including the power consumption of the on-chip reference generator.

**Fig. 12.** Measured SFDR and SNDR of the ADC versus (a) fs, (b) fin.

Table 1. Performance summary of the prototype ADC

| Resolution        | 12b                                                            |                       |  |  |  |

|-------------------|----------------------------------------------------------------|-----------------------|--|--|--|

| Conversion Rate   | 100 MS/s                                                       |                       |  |  |  |

| Process           | Dongbu HiTek 0.11 μm CMOS                                      |                       |  |  |  |

| Supply            | 1.1 V                                                          |                       |  |  |  |

| Input Range       | 1.0 Vp-p                                                       |                       |  |  |  |

| DNL               | -0.37 LSB / +0.38 LSB                                          |                       |  |  |  |

| INL               | -1.21 LSB / +1.21 LSB                                          |                       |  |  |  |

| SNDR / SFDR       | 60.2 dB / 69.5 dB (@ fin=4 MHz)                                |                       |  |  |  |

|                   | 55.9 dB / 67.3 dB (@ fin=50 MHz)                               |                       |  |  |  |

| Power Consumption | with I/V Reference                                             | without I/V Reference |  |  |  |

| Tower Consumption | 25.3 mW                                                        | 21.8 mW               |  |  |  |

| Active Die Area   | $1.34 \text{ mm}^2 (= 1.05 \text{ mm} \times 1.28 \text{ mm})$ |                       |  |  |  |

$$FoM = \frac{Power}{2^{ENOB} \times f_S} \tag{1}$$

The sampling rate of the proposed ADC is higher than that of previously reported 12b SAR ADCs. The proposed hybrid pipeline ADC without an input SHA shows similar dynamic performances at the Nyquist input frequency with competitive power consumption compared to previously reported 12b pipeline ADCs. The dynamic performance of the proposed ADC is similar to

|           | Speed<br>(MS/s) | Supply (V) | Power<br>(mW)        | SNDR<br>@Nyq.<br>(dB) | FoM (pJ/conv.) | Process         | Structure                         |

|-----------|-----------------|------------|----------------------|-----------------------|----------------|-----------------|-----------------------------------|

| This work | 100             | 1.1        | 25.3                 | 55.9                  | 0.50           | 0.11 μm<br>CMOS | Hybrid<br>Pipeline                |

| [13]      | 45              | 1.2        | 3.0                  | 67.1<br>(w/cal.)      | 0.04           | 0.13 μm<br>CMOS | SAR                               |

| [17]      | 50              | 1.3        | 3.5<br>(w/o<br>ref.) | 64.4                  | 0.05           | 65 nm<br>CMOS   | SAR-<br>assisted<br>Pipeline      |

| [1]       | 100             | 1.0        | 24.0                 | 56.0                  | 0.47           | 0.13 μm         | Pipeline<br>w/ SHA<br>(version 1) |

| [1]       | 100             | 1.0        |                      |                       | İ              | CMOS            | Pineline                          |

49.0

58.0

56.2

0.83

0.65

1 04

w/o SHA

(version 2)

Pipeline

Pipeline

0.13 µm

**CMOS**

90 nm

**CMOS**

19.0

42.0

55.0

100

100

[3]

[4]

1.2

Table 2. Comparison of previously reported 12b ADCs

that of the version 1 of [1] despite not employing the SHA. Even though both the proposed ADC and the version 2 of [1] are equally based on the SHA-less topology, the former shows a significant improvement of the dynamic performance compared to the latter. Moreover, the proposed design techniques are expected more effective particularly in nanometer CMOS processes where it is difficult to design a high-gain analog amplifier unlike easily obtainable digital logic.

### V. CONCLUSIONS

This work proposes a 12b 100 MS/s hybrid pipeline ADC using SAR and pipeline topologies together. The first stage of the proposed ADC based on dual-channel time-interleaved SAR ADCs for 4 MSBs properly handles the Nyquist-rate input at high speed without a dedicated SHA while the remaining pipeline stages with high-speed flash ADCs decide 8 LSBs. Only one amplifier is employed and shared in the proposed ADC for the first-stage dual-channel residue amplifications and the MDAC of the remaining pipeline stages. The shared residue amplifier for the SAR ADCs prevents performance degradation caused by the amplifier mismatch between channels with low consumption. A potential reference disturbance occurring from the operating speed difference of two SAR ADCs and one MDAC is much reduced by separating reference voltage drivers. The proposed hybrid pipeline ADC is

implemented in a 0.11  $\mu m$  CMOS and occupies an active die area of 1.34 mm<sup>2</sup>. The measured DNL and INL are within 0.38 LSB and 1.21 LSB, respectively. The ADC shows a maximum SNDR of 60.2 dB and a maximum SFDR of 69.5 dB at 100 MS/s with a 4 MHz input. The proposed ADC consumes 25.3 mW at 100 MS/s and a 1.1 V supply voltage.

### ACKNOWLEDGMENTS

This work was supported by a grant-in-aid of Samsung Thales, the Basic Science Research Program through the National Research Foundation of Korea (NRF) funded by the Ministry of Education (grant number 2013R1A1A2004829), and the MSIP (Ministry of Science, ICT & Future Planning), Korea, under the ITRC (Information Technology Research Center) support program (NIPA-2014-H0301-14-1007) supervised by the NIPA (National IT Industry Promotion Agency).

### REFERENCES

- [1] B. W. Koo, et al, "A single amplifier-based 12-bit 100MS/s 1V 19mW 0.13μm CMOS ADC with various power and area minimized circuit techniques," *IEICE Trans. on Electronics*, vol. E94-C, no. 8, pp. 1282-1288, Aug. 2011.

- [2] C. Jack, B. Lane, and H. S. Lee, "A zero-crossing based 12b 100MS/s pipeline ADC with decision boundary gap estimation calibration," in Symp. VLSI Circuits Dig. Tech. Papers, June 2010, pp. 237-238.

- [3] Y. J. Kim, et al, "A 0.31pJ/conversion-step 12-bit 100MS/s 0.13μm CMOS A/D converter for 3G communication system," *IEICE Trans. on Electronics*, vol. E92-C, no. 9, pp. 1194-1200, Sept. 2009.

- [4] T. Ito, et al, "55-mW 1.2-V 12-bit 100-MSps pipelined ADCs for wireless receivers," in Proc. Eur. Solid-State Circuits Conf., Sept. 2006, pp. 540-543.

- [5] C. Grace, P. Hurst, and S. Lewis, "A 12-bit 80-MSample/s pipelined ADC with bootstrapped digital calibration," *IEEE J. Solid-State Circuits*, vol. 40, no. 5, pp. 1038-1046, May 2005.

- [6] J. Treichler and Q. Huang, "A 11.1-bit ENOB 50-MS/s pipelined A/D converter in 130-nm CMOS without S/H front end," in Proc. Eur. Solid-State Circuits Conf., Sept. 2010, pp. 374-377.

- [7] P. Huang, et al., "SHA-less pipeline ADC converting 10th Nyquist band in-situ clock-skew calibration," *in Proc. CICC*, Sept. 2010, pp. 1-4.

- [8] H. C. Choi, et al, "A 1.2-V 12-b 120-MS/s SHA-free dual-channel Nyquist ADC based on midcode calibration," *IEEE Trans. on Circuits and Systems I*, vol. 56, no. 5, pp. 894-901, May 2009.

- [9] B. G. Lee and R. Tsang, "A 10-bit 50 MS/s pipeline ADC with capacitor-sharing and variable-gm opamp," *IEEE J. Solid-State Circuits*, vol. 44, no. 3, pp. 883-890, Mar. 2009.

- [10] Y. D. Jeon, et al., "A 4.7mW 0.32mm<sup>2</sup> 10b 30MS/s pipelined ADC without a front-end S/H in 90nm CMOS," *in ISSCC Dig. Tech Papers*, Feb. 2007, pp. 456-457.

- [11] J. Li, et al., "A 1.8-V 22-mW 10-bit 30-MS/s subsampling pipeline CMOS ADC," *in Proc. CICC*, Sept. 2006, pp. 513-516.

- [12] D. H. Hwang, et al, "A Range-Scaled 13b 100MS/s 0.13μm CMOS SHA-Free ADC Based on a Single Reference," *Journal of Semiconductor Technology* and Science, vol. 13, no. 2, pp. 98-107, Apr. 2013.

- [13] W. Liu, P. Huang, and Y. Chiu, "A 12-bit, 45-MS/s, 3-mW redundant successive-approximation-register analog-to-digital converter with digital calibration," *IEEE J. Solid-State Circuits*, vol. 46, no. 11, pp. 2661-2672, Nov. 2011.

- [14] W. Liu, P. Huang, and Y. Chiu, "A 12b 22.5/45MS/s 3.0mW 0.059mm<sup>2</sup> CMOS SAR ADC achieving over 90dB SFDR," *in ISSCC Dig. Tech Papers*, Feb. 2010, pp. 380-381.

- [15] H. W. Chen, et al., "A 3mW 12b 10MS/s sub-range SAR ADC," *in Proc. Asian Solid-State Circuits conf.*, Nov. 2009, pp. 153-156.

- [16] J. Kang and M. Flynn, "A 12b 11MS/s successive approximation ADC with two comparators in 0.13μm CMOS," *in Symp. VLSI Circuits Dig. Tech. Papers*, June 2009, pp. 240-241.

- [17] C. Lee and M. Flynn, "A SAR-assisted two-stage pipeline ADC," *IEEE J. Solid-State Circuits*, vol. 46, no. 4, pp. 859-869, Apr. 2011.

- [18] K. Kusumoto, A. Matsuzawa, and K. Murata, "A 10-b, 20-MHz, 30-mW pipelined interpolating CMOS ADC," *IEEE J. Solid-State Circuits*, vol. 28, pp. 1200-1206, Dec. 1993.

- [19] S. Limotyrakis, et al, "A 150MS/s 8b 71mW time-interleaved ADC in 0.18µm CMOS," *in ISSCC Dig.*

- Tech. Papers, Feb. 2004, pp. 258-259.

- [20] H. J. Kim, et al, "Time-Interleaved and Circuit-Shared Dual-Channel 10 b 200 MS/s 0.18 μm CMOS analog-to-digital convertor," *IEEE Trans. on Very Large Scale Integration (VLSI) Systems*, vol. 21, no. 12, pp. 2206-2213, Dec. 2013.

- [21] M. Shinagawa, Y. Akazawa and T. Wakimoto, "Jitter analysis of high-speed sampling systems," *IEEE J. Solid-State Circuits*, vol. 25, no. 1, pp. 220-224, Feb. 1990.

Jun-Sang Park received the B.S. and M.S. degrees in Electronic Engineering from Sogang University, Seoul, Korea, in 2012 and 2014, where he is currently pursuing the Ph.D. degree. His current interests are in the design of high-resolution

low-power CMOS data converters, PMICs, and very high-speed mixed-mode integrated systems.

**Tai-Ji An** received the B.S. degree in electronic engineering from University of Seoul, Korea, in 2007, and the M.S. degree in electronic engineering from Sogang University in 2013. From 2007 to 2011, he was with Luxen Technologies, Korea, where

he had developed various power-management and analog integrated circuits. He has been in the Ph.D. program at Sogang University since 2013. His current interests are in the design of high-resolution low-power CMOS data converters, PMICs, and very high-speed mixed-mode integrated systems.

**Suk-Hee Cho** received the B.S. degree in electronics and information engineering from Korea University, Jochiwon, Korea, in 2012. He is currently pursuing the M.S. degree in electronic engineering of Sogang University, Korea. He is a

scholarship student supported by LG electronics. His current interests are in the design of high-resolution CMOS data converters, PMICs, and very high-speed mixed-mode integrated systems.

Yong-Min Kim received the B.S. and M.S. degrees in Electronic Engineering from Sogang University, Seoul, Korea, in 2012 and 2014, respectively. Since February 2014, he has been with Silicon Works, Korea. His current interests are in the design

of DC-to-DC converters and high-resolution low-power CMOS data converters, very high-speed mixed-mode integrated systems.

**Gil-Cho Ahn** received the B.S. and M.S. degrees in electronic engineering from Sogang University, Seoul, Korea, in 1994 and 1996, respectively, and the Ph.D. degree in electrical engineering from Oregon State University, Corvallis, in 2005.

From 1996 to 2001, he was a Design Engineer at Samsung Electronics, Kiheung, Korea, working on mixed analog & digital integrated circuits. From 2005 to 2008, he was with Broadcom Corporation, Irvine, CA, working on mixed-signal circuits. Currently, he is an Associate Professor in the Department of Electronic Engineering, Sogang University. His research interests include high-speed, high-resolution data converters and low-voltage, low-power mixed-signal circuits design.

**Ji-Hyun Roh** received the M.S. degree in electrical & electronic engineering from Yonsei University, Seoul, Korea, in 2012. In 1996, he joined the Samsung Electronics, Korea. Since 2000, he has been a member of Samsung Thales, Korea

where his research interests include electronic warfare.

**Mun-Kyo Lee** received the Ph.D. degree in electronic engineering from Dongguk University, Seoul, Korea, in 2009. In 2009, he joined Samsung Thales, Korea where his research interests include electronic warfare, radar and millimeter-wave radiometer.

**Sun-Phil Nah** received the M.S. degree from Chungnam National University of Daejeon, Korea, in 1987. In 1991, he joined ADD, Korea where his research interests include electronic warfare, SIGINT.

**Seung-Hoon Lee** received the B.S. and M.S. degrees in electronic engineering from Seoul National University, Korea, in 1984 and 1986, respectively, and the Ph.D. degree in electrical and computer engineering from the University of Illinois,

Urbana-Champaign, in 1991. He was with Analog Devices Semiconductor, Wilmington, MA, from 1990 to 1993, as a Senior Design Engineer. Since 1993, he has been with the Department of Electronic Engineering, Sogang University, Seoul, where he is currently a Professor. His current research interests include design and testing of high-resolution high-speed CMOS data converters, CMOS communication circuits, integrated sensors, and mixed-mode integrated systems. Dr. Lee is a member of the editorial board and the technical program committee of many international and domestic journals and conferences including the IEEK Journal of Semiconductor Devices, Circuits, and Systems, the IEICE Transactions on Electronics, and the IEEE Symposium on VLSI Circuits. Since 2006, he has been organizing various industry-university mutual cooperative programs with many companies such as Samsung Electronics, SK Hynix, and LG Electronics. In 2010, he founded Analog IP Research Center supported by the Ministry of Science, ICT & Future Planning, Korea.