http://dx.doi.org/10.6113/TKPE.2014.19.1.71

# 3상 비엔나 정류기 입력 전압 센서리스 제어

이상리<sup>1</sup>, 김학원<sup>†</sup>, 조관열<sup>1</sup>, 황순상<sup>2</sup>, 윤병철<sup>2</sup>

# Input Voltage Sensorless Control for 3 Phase Vienna Rectifier

Sang-Ri Lee<sup>1</sup>, Hag-Wone Kim<sup>†</sup>, Kwan-Yuhl Cho<sup>1</sup>, Soon-Sang Hwang<sup>2</sup>, and Byung-Chul Yoon<sup>2</sup>

**Abstract** - In this paper, a new grid voltage estimation algorithm without voltage sensors is proposed for the three-phase vienna rectifier. Generally, input voltage sensor circuits increase size and cost of the PWM rectifier. In order to reduce the cost and size and in order to increase reliability from the electrical noise, grid voltage estimation scheme without input voltage sensor is highly required. In this paper, the grid voltage estimation algorithm is proposed by a simple MRAS(Model Reference Adaptive System) observer without input voltage sensors. The validity of the proposed method is proven by simulation and experiment on the three-phase vienna rectifier system.

Keywords: vienna rectifier, MRAS(Model Reference Adaptive System)

#### 1. 서 론

3상 3레벨 비엔나 정류기는 단방향의 전력 변환이 요구되는 AC/DC 컨버터의 입력 전류 고조파 저감을 위한 회로로 검토되고 있다. 3레벨 비엔나 정류기는 2레벨 3상 PWM 정류기에 비해 출력 전압 총 왜곡율 (Total Harmonic Distortion, 이하 THD)가 작아서, 계통으로부터 입력되는 전류 THD를 작게 할 수 있다. 또, 스위치전압스트레스가 DC 링크 전압의 절반으로, 선간 전압 380Vrms 입력 계통에서도 전력용 반도체 스위치소자로 MOSFET를 사용하여 스위칭 주파수를 키울 수 있고 IGBT에 비해 스위칭 손실이 작아 컨버터의 고효율화에 유리한 장점을 가지고 있어, 단방향 전력 흐름을 위한 정류기로 연구되고 있다<sup>[1]-[4]</sup>.

일반적으로 3상 PWM 정류기는 계통 측 전압을 계측 하여 위상 정보를 PLL 방식으로 획득하고, 획득된 계통 위상 정보를 이용하여 입력 전압과 입력 전류의 역률을

보정하여 준다. 일반적으로 계통 전압을 계측하기 위해 저주파 변압기나 고가의 절연이 가능한 연산 증폭기를 사용한다. 절연이 가능한 연산 증폭기는 고가이므로 통 상적으로 저가의 저주파 변압기를 통하여 입력 전압을 계측하게 된다. 입력 전압을 계측하기 위한 저주파 변압 기는 일정 이상의 전압 강하가 생기거나 일정 이상의 전력 넘어 증가된 전류가 변압기를 통해 흐르게 되면 변압기의 온도가 올라가 포화가 될 수 있으며 포화가 되면 선형 특성을 잃게 되어 입력 전압을 왜곡하여 계 측 할 수 도 있으며 저주파 변압기를 사용하면 시스템 의 체적이 증가되는 등의 단점을 가지고 있다. 이런 단 점을 극복하기위하여 입력 전압 Sensorless PWM 정류 기의 제어에 대한 연구가 진행되어왔다[5]-[8]. 그러나 이 들 방법들은 정상 상태에서 전압 관측 및 계통 위상 관 측에 대한 언급은 되어 있으나, PWM 정류기가 동작 개 시될 때인 과도상태 제어에 필요한 입력 전압 및 계통 위상에 관측에 대한 언급이 없다. 일반적으로 계통의 전 압 및 위상 관측 방법은 계통 전압 관측기를 사용하여 계통의 전압을 관측하고 계통의 위상을 추정하는 방법 이 일반적이다. 관측기의 원리는 PWM 정류기 플랜트 (Plant) 방정식으로부터 인가된 입력에 따른 상태를 관 측하여 원하는 정보를 얻는 방식으로 PWM 정류기의 출력 전압에 대한 정보가 필요하다. 그러나 PWM 정류 기의 동작이 개시될 때는 인가된 입력이 없어 초기 계

본 논문에서는 모델 적응 기법을 이용한 계통 전압의

통의 전압이나 계통의 위상이 관측이 불가능하다.

Paper number: TKPE-2014-19-1-10

Print ISSN: 1229-2214 Online ISSN: 2288-6281

<sup>&</sup>lt;sup>†</sup> Corresponding author: khw@ut.ac.kr, Dept. of Control & Instrumentation Eng., Korea Nat'l Univ. of Transportation Tel: +82-43-841-5322 Fax: +82-43-841-5320

Dept. of Control & Instrumentation Engineering, Korea Nat'l Univ of Transportation.

<sup>&</sup>lt;sup>2</sup> DongAh Elecomm, Power Supply Research Lab., Gyeonggi, ROK

Manuscript received Oct. 17, 2013; accepted Dec. 15, 2013 — 본 논문은 2013년 전력전자학술대회 외부장학금 수혜논문임

크기 및 위상을 관측하는 방법을 제안한다. 제안한 방식을 적용한 대상은 3레벨 3상 정류기인 비엔나 정류기에 적용한다. 제안한 모델 적응 기법의 방법은 입력 전압 인가가 없는 초기 상태에서도 계통의 위상의 관측이 가능하여, 정상 상태 뿐 아니라 과도상태에서도 계통의 전압 및 위상을 관측할 수 있어 쉽게 비엔나 정류기의 동작을 제어할 수 있다. 2장에서는 제어 대상이 되는 비엔나 정류기에 대하여 설명하고, 3장에서는 제안하는 입력 전압추종기법에 대하여 논한다. 그리고 4장에서는 모의해석 및 실험을 통하여 제안한 방법의 타당성을 입증한다.

## 2. 비엔나 정류기

## 2.1 비엔나 정류기 동작 원리

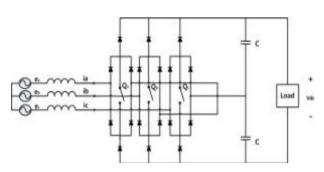

그림 1은 비엔나 정류기 회로를 나타낸다.  $e_{abc}$ 는 3상 교류 입력 전압원이 되며,  $Q_{abc}$ 는 스위치에 인가되는 전압, 전류에 대하여 4상한 동작이 가능하도록 MOSFET를 이용한 반도체 스위치로 구성하고 Diode는 3상의 정류 다이오우드를 의미한다. 비엔나 정류기에서 사용되는 반도체 소자는 18개의 정류용 다이오우드와 3개의 MOSFET가 사용된다. 비엔나 정류기의 동작은 스위치가 켜질 경우  $i_{abc}$ 의 방향에 상관없이 출력 단자 전압은 0V가 되고, 스위치가 꺼진 경우  $i_{abc}$ 의 방향이 양과 음에 따라 각각  $V_{dc}/2$ ,  $-V_{dc}/2$ 의 값을 가지게 된다. 식(1)은 스위칭 함수에 따른 출력 단자 전압을 나타낸다.

$$V_{xo(x\,=\,a,b,c)} = -\,sign \big( i_{x\,(x\,=\,a,b,c)} \big) S_{x\,(x\,=\,a,b,c)} \frac{V_{dc}}{2} \eqno(1)$$

3레벨 3상 비엔나 정류기 출력 단자 전압은  $V_{dc}/2$ ,  $-V_{dc}/2$ , 0의 3가지 상태를 갖게 된다. 이에 비해 2레벨 3상 PWM 정류기의 출력 단자 전압은  $V_{dc}/2$ ,  $-V_{dc}/2$ 의 두가지 상태만을 가진다. 이로 인해 3레벨 3상 비엔나 정류기는 2레벨 3상 PWM 정류기에 비해 출력 전압의 THD를 상당히 저감할수 있는 장점을 가지고 있다<sup>[3]</sup>.

또한 내압이 낮은 스위치를 사용할 수 있어 재료비를 낮출 수 있으며, 낮은 내압의 스위치를 사용하므로 전력 용 반도체 소자의 손실을 줄일 수 있어 높은 효율을 얻 을 수 있는 장점이 있다.

Fig. 1 Vienna rectifier circuit

Table 1 Diode status of vienna rectifier by the switching state

| $S_{abc}$ | $i_{abc}$     | $D_{1,3,5}$ | $D_{2,4,6}$ | Pole Volt.  |

|-----------|---------------|-------------|-------------|-------------|

| 1         | Don't<br>care | OFF         | OFF         | 0V          |

| 0         | $i_{abc}>0$   | On          | OFF         | $V_{dc}/2$  |

|           | $i_{abc}$ <0  | OFF         | ON          | $-V_{dc}/2$ |

## 2.2 비엔나 정류기 제어 기법

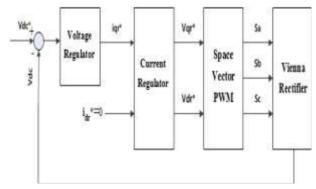

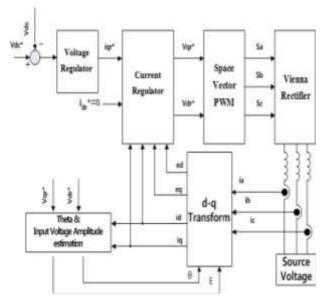

그림 2는 비엔나 정류기를 포함한 일반적인 3상 PWM 정류기의 제어 블록이다. 3상을 사용하는 모든 AC/DC 컨버터는 듀얼 루프(Dual Loop) 형태로 전압 제 어기와 전류 제어기를 사용한다. 전압 제어기는 외부 루 프(Outer Loop) 이며 전류 제어기는 내부 루프(Inner Loop)가 된다. 3상의 전압과 전류를 제어하기 위해 dq좌 표 변환하여 제어한다. 본 논문에서 q축은 유효 전력 축 이며, d축은 q축과 90° 위상 차이를 갖는 무효 전력 축 이다. 전압 제어기와 전류 제어기는 정상상태 오차를 제 거하기 위해 출력 전압과 입력 전류를 제어하며, 제어기 는 PI 제어기를 사용하여 제어한다. 전압제어기를 통해 q축 전류 명령이 출력 되며, 전류 제어기를 통해서 dq축 의 전압 지령으로 출력되어 PWM 함수의 입력이 된다. PWM 함수는 전압 명령을 사용하여 비엔나 정류기의 스위칭 상태를 결정한다. 3레벨 컨버터인 비엔나 정류기 는 입력 전압 및 4상한 스위치 조합에 의한 스위칭 벡 터의 선택이 어렵고, 선택된 각각의 벡터의 인가 시간 계산이 복잡하기 때문에 공간 벡터를 계산하기 어렵다. 본 논문에서는 단일 반송파를 이용한 공간 벡터(Space Vector )PWM방식을 사용하였다<sup>[3]</sup>.

## 3. 입력 전압 추정 기법

3상 비엔나 정류기는 입력 전압, 입력 전류, 출력 전압을 계측한다. 입력 전류와 출력 전압은 각 각 전류제어기와 전압제어기에 궤환(Feedback)되어 제어한다. 입력 전압은 계통 전압의 위상을 연산하고 전류 제어 시

Fig. 2 Control block diagram of PWM rectifier

전향 보상을 위해 필요하다. 이 절에서는 기존 방법인 계통 전압 센서를 이용하여 계통 전압의 위상을 추정하는 방법과 본 논문에서 제안하는 입력 전압 센서리스 입력 전압을 추정 기법에 대해서 다룬다.

#### 3.1 기존의 계통 위상 관측 기법

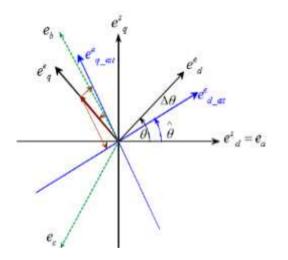

3상 비엔나 정류기는 제어기를 통해 전압과 전류를 제어하기 위해 dq축의 변환이 필요하다. dq 변환을 하기 위해서는 계통 전압의 위상 정보가 필요하게 되는데 위상 정보는 PLL(Phase Locked Loop)제어 기법을 통해 추종하는 방법이 일반적이다. 위치 정보를 검출해낼수 있는 좌표축의 관계를 그림3에 나타내었다. a, b, c 좌표계는 a,b,c축으로 나타내어지며 서로  $120^\circ$  위상 차이를 가진다. 정지 좌표계인  $e^s_d$  축은 a축과 동일한 축이며,  $e^s_q$ 은  $e^s_d$ 축보다  $90^\circ$  앞선다. 동기 좌표계는 입력 전압의 주파수에 따라 회전하는 좌표계이며,  $e^e_q$ 은 유효전력 축의 전압의 크기이고,  $e^e_d$ 는 무효전력 축의 전압의 크기이며,  $e^e_d$ 는  $e^e_q$ 보다  $90^\circ$  뒤진다.  $e^e_{d-est}$ ,  $e^e_{q-est}$ 은 제어기를 통해 추정된 동기 좌표축의 전압을 의미하며,  $\Delta\theta$ 만큼의 오차를 가지고 있다고 가정한다. 식 (2)는  $e^e_{d-est}$ 와  $\Delta\theta$ 의 관계이다.

$$e_{d-est}^{e} = -E\sin(\theta - \hat{\theta}) \approx -E\Delta\theta \tag{2}$$

Fig. 3 dq-axis of grid voltage

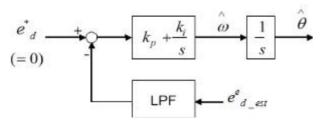

Fig. 4 PLL block diagram

식 (2)를 보면  $e^e_{d-est}$ 은 실제 계통의 위상과 추정된 위치 정보가 일치하게 되면 0이 된다. 그림4는 계통의 위상 정보 검출을 위한 블록도이다. d축 전압의 명령을 0으로 하고, 현재 제어기가 알고 있는 d축 전압이 0이 되면 계통의 위상 정보를 획득할 수 있다. 이를 위해 d축 전압 명령과 추종하는 d축 전압의 차를 PI제어기를 거쳐 계통의 주파수 정보인  $\hat{\omega}$ 를 얻고, 이 값을 적분 시켜 계통의 위상 정보를 검출한다. 식 (3)은 계통 주파수를 위한 식이며, 식 (4)는 위상 정보 획득을 위한 식이다.

$$\hat{\omega}(s) = \left(k_p + \frac{k_i}{s}\right) \left(-\hat{e}_{dr}(s)\right) \tag{3}$$

$$\hat{\theta}(s) = \frac{1}{s}\hat{\omega}(s) = -\frac{1}{s}\left(k_p + \frac{k_i}{s}\right)\hat{e}_{dr}(s) \tag{4}$$

PLL을 통해 추종한 계통 위상 정보를 통해 다시 dq 변환 하여 d축 전류 명령을 0으로 제어하여, 계통 전압 과 입력 전류를 같은 위상으로 제어할 수 있게 된다.

## 3.2 제안된 입력 전압 추정 기법

제안된 입력 전압 검출 알고리듬을 포함한 비엔나 정류기 제어 블록도는 그림 5과 같다. 제안하는 계통 전압검출 알고리듬은 전동기 구동을 위한 센서리스 방식인 Matsui 방식을 응용하여 개량하였으며[11], dq변환을 통해 나온 입력 전류의  $i_{dq}^e$ 와  $v_{dq}^e$ 를 사용하여 모델 기반적응 제어 기법을 통해  $e_{dq}^e$  추종한다. 또한 안정적인 PWM 동작을 얻기 위하여 계통의 전압 크기(Amplitude) 관측기의 응답 특성을 빠르게 할 수 있도록 제어기 이득을 크게 설정하였다. 계통 전압 센서리스알고리듬은 식 (5)는 비엔나 정류기의 입력 전압 방정식을 나타낸다. 식 (5)에서  $e_{abc}$ 는 입력 전압이며,  $i_{abc}$ 는 입력 전류이고,  $v_{abc}$ 는 비엔나 정류기 출력 전압이고, L은 입력 인덕터이다. 식 (5)를 동기 좌표계로 변환하면식 (6)과 같다.

$$e_{abc} = L \frac{di_{abc}}{dt} + v_{abc} \tag{5}$$

$$e_{dq}^{e} = L \frac{di_{dq}^{e}}{dt} + \begin{pmatrix} 0 - \omega \\ \omega & 0 \end{pmatrix} + v_{dq}^{e}$$

(6)

여기서,  $\omega$ 는 계통 전압의 각주파수이다. 입력 전압  $e_{dq}$ 의 동기 좌표계 식은 식(7)과 같다.

$$e_{dq}^{e} = \begin{bmatrix} -e_{m}\sin(\Delta\theta) \\ e_{m}\cos(\Delta\theta) \end{bmatrix}$$

(7)

여기서  $\Delta \theta$ 는 계통의 위상과 비엔나 정류기가 알고있는 계통의 위상 차이로  $\theta - \hat{\theta}$ 이다. 식 (7)을 식 (6)에 대입하여  $i_{dq}^e$ 의 변화율에 대한 식으로 정리하면 다음 식 (8)을 나타낼 수 있다.

$$\frac{di_{dq}^{e}}{dt} = \begin{bmatrix} -e_{m}\sin\left(\Delta\theta\right) \\ L \\ e_{m}\cos\left(\Delta\theta\right) \\ L \end{bmatrix} + \begin{pmatrix} 0 - \omega \\ \omega & 0 \end{pmatrix} i_{dq}^{e} - \frac{v_{dq}^{e}}{L}$$

(8)

본 논문에서는 입력 전압을 계측하지 않고 계통의 위상을 관측하기 위해 모델 기반 적응제어 기법(Model Reference Adative System)을 사용한다. 센서리스 계통위상 감지 알고리듬을 수행하기 위해서는 식 (8)을 이상적인 모델로 가정한 모델식을 정의하여야하며 식 (9)와 같다.

$$\frac{di_{dqM}^e}{dt} = \left[\frac{\hat{e}_m}{L_0}\right] + \left(\frac{0 \hat{\omega}}{-\hat{\omega}}\right) i_{dq}^e - \frac{v_{dq}^e}{L_0} \tag{9}$$

식 (9)는  $L_0$ 는 입력 인덕터의 공칭 파라미터이며,  $i_{dqM}^e$ 는 제어기의 모델에 의하여 계산된 모델 전류이며,  $\hat{\omega}$ 는 제어기로 추정한 계통 전압의 각주파수이다. 모델 전류의 식은 실제 입력 전압의 위치 정보와 추종하고 있는 위치 정보가 일치하다고 가정하여 추종하는 위치 오차  $\Delta\theta$ 는 0으로 하여 세운 식이다. 식(10)은 모델 전류의 변화율을 이산형태의 식으로 나타내었다.

$$\frac{di_{dqM}^{e}(kT)}{dt} = \frac{di_{dqM}^{e}(kT) - di_{dq}^{e}((k-1)T)}{T}$$

(10)

Fig. 5 Control block diagram with proposed grid voltage detection algorithm

식 (10)에서 T는 샘플링타임을 의미하며, k번째 샘플링 시점의 모델 전류 계산 시 사용되는 (k-1)번째 모델 전류는 실제  $i_{dq}^e$ 전류를 사용한다<sup>[9]</sup>. 실제 입력 인덕터값이 공칭 인덕터와 일치하다고 가정하면 식 (8)과 식 (9)로부터 입력 전압 회전좌표계 dq변환식을 식(11)과 같이나타낼 수 있다.

$$L\left(\frac{di_{dq}^{e}}{dt} - \frac{di_{dqM}^{e}}{dt}\right) = \begin{bmatrix} -e_{m}\sin(\Delta\theta) \\ e_{m}\cos(\Delta\theta) - \hat{e_{m}} \end{bmatrix}$$

(11)

여기서  $\Delta\theta$ 는  $\theta-\hat{\theta}$ 이다.  $\Delta\theta$ 가 작다고 가정하고 식 (11)에서 입력 전압의 회전좌표계 d축을 정리하면 식 (12)와 같이 위치 정보를 관측할 수 있는 식으로 정리할 수 있으며, 입력 전압의 회전좌표계 q축을 정리하면 식 (13)과 같이 입력 전압 크기에 대한 식으로 정리할 수 있다.

$$\theta - \hat{\theta} = -\frac{L}{\hat{e}_{m}} \left( \frac{di_{d}^{e}}{dt} - \frac{di_{dM}^{e}}{dt} \right) \tag{12}$$

$$e_m - \hat{e}_m = L \left( \frac{di_q^e}{dt} - \frac{di_{qM}^e}{dt} \right) \tag{13}$$

식 (12)와 식 (13)를 디지털 방식에 직접 적용하기 위해서는 이산형태의 식으로 정리하면 아래의 식 (14),(15)와 같다.

$$\theta(kT) - \hat{\theta}(kT) = -\frac{L}{\hat{e}_{m}(kT)} \left( \frac{di_{d}^{e}(kT)}{dt} - \frac{di_{dM}^{e}(kT)}{dt} \right)$$

(14)

$$e_m(kT) - \hat{e}_m(kT) = L \left( \frac{di_q^e(kT)}{dt} - \frac{di_{qM}^e(kT)}{dt} \right)$$

(15)

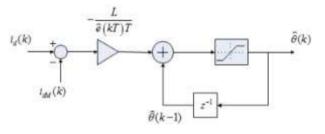

Fig. 6 Estimation block diagram of grid voltage phase angle

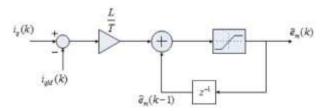

Fig. 7 Estimation block diagram of grid voltage amplitude

식 (14)와 식 (15)는 식 (12)과 식 (13)의 위치 정보와 입력 전압 크기를 감지하는 식의 이산형태의 식이다.

$$i_{dM}^{e}\!\left(kT\right)\!=i_{d}^{e}\!\left(\left(k-1\right)T\right)\!+\frac{T}{L}\!\left(\omega L i_{q}^{e}\!\left(\left(k-1\right)T\right)\!-v_{d}^{e}\!\left(kT\right)\right) \quad (16)$$

$$i_{qM}^{e}(\!\left(k\,T\right)\!=i_{q}^{e}(\left(k-1\right)T\!)\!+\!\frac{T}{L}\!\left(\hat{e}_{m}^{}-\omega L\!i_{d}^{e}\!\left(\left(k-1\right)T\!\right)\!-v_{q}^{e}\!\left(k\,T\!\right)\right) \tag{17}$$

식 (16)과 식 (17)는 위치 정보과 입력 전압 크기 추종 하기 위해 필요한 모델 전류의 이산형태의 식이다.

$$\hat{\theta}(kT) = \hat{\theta}((k-1)T) - \frac{L}{\hat{e}_m(kT)T} \left( i_d^e(kT) - i_{dM}^e(kT) \right) + \hat{\omega}(kT)T \qquad (18)$$

$$\hat{e}_{m}(kT) = \hat{e}_{m}((k-1)T) + \frac{L}{T} \left( i_{q}^{e}(kT) - i_{qM}^{e}(kT) \right) \tag{19}$$

앞서 구한 식 (14)와 식 (15)를 이용하면 식 (18)과 식 (19)과 같은 디지털 방식으로 위치 정보 추정식과 입력 전압 크기 추정 식으로 나타낼 수 있다. 모델 전류를 구하는 식 (16), (17)과 위상 및 역기전력 추정식은 샘플링시간 T에 따른 영향을 고려할 수 있으나, 일반적으로 계통 전압의 기본과와 PWM 주과수의 차가 충분히 크므로 샘플링 타임에 의한 이산화 오차는 매우 작다고할 수 있다. 그림 6과 그림 7은 각각 위치 정보 추정 블록도와 입력 전압 크기 추정 블록도이다.

# 3.3 다이오우드 정류 모드에서 계통 위상 추정

비엔나 정류기는 QA, QB, Qc를 스위칭하기 전에는 다 이오우드 정류기로 동작한다. 비엔나 정류기가 안정적으 로 기동하기 위해서는 다이오우드 정류기 모드에서도 계통 전압의 위상이 추정 가능하여야한다. 일반적으로 모델 기반 관측기를 기반으로 한 경우 모델 전류를 계 산하기 위해서 관측 대상에 입력된 입력 정보가 필요하 다. 만약 모델 정보가 없을 때는 모델 기반 적응 기법의 관측기의 적용이 불가능하다. 그러나 본 논문에서 제안 된 전압 센서리스 알고리듬은 다이오우드 정류기 동작 모드에서도 계통의 위상 관측이 가능하다. 이는 본 논문 에서 제안된 계통의 위상 관측이 d축의 모델을 이용하 기 때문에 가능하다. 다이오우드 정류기는 항상 입력 전 압이 DC 링크 전압보다 높아야 입력 전류가 계통에서 인입된다. 입력 전압이 DC 링크보다 작으면 다이오우드 는 차단된다. 이는 다이오우드 정류기 동작시 인가되는 d축 전압이 0이 됨을 의미하며, 이에따라 다이오우드 정 류기 모드에서도 계통 위상의 추정이 가능함을 알 수 있다.

## 4. 모의 해석 및 실험 결과

본 장에서는 입력 전압 센서가 없는 비엔나 정류기를 시뮬레이션과 실험을 통해 타당성을 입증한다.

Table 2 Condition for simulation & experiment

| Rated Power         | 4.5 kW          |  |

|---------------------|-----------------|--|

| Rated Input Voltage | 220 Vrms/ 60 Hz |  |

| DC Link Voltage     | 680 V           |  |

| Input Inductance    | 1.1 mH          |  |

| Out Capacitance     | 1360 uF         |  |

| Switction Frequency | 50 kHz          |  |

#### 4.1 시뮬레이션 결과

표 2는 입력 전압 센서가 없는 비엔나 정류기 제어를 위한 시뮬레이션 파라미터이다. 본 논문에서는 PSIM을 이용하여 시뮬레이션을 하였다.

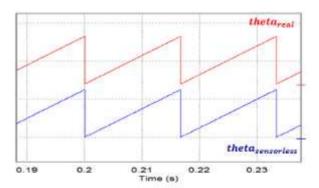

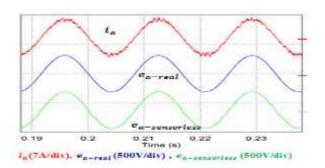

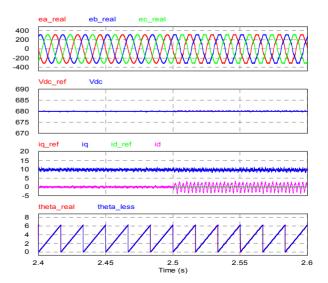

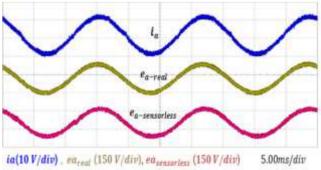

본 논문에서 제안한 알고리듬을 검증하기위해 기존의 전압 센서를 이용한 PLL제어기법의 관측된 계통 위상과 비교한다. 그림 8는 기존의 PLL제어기법을 사용하였을 때 위치 정보와 제안하는 센서리스 알고리듬의 위치정보를 시뮬레이션을 통해 비교한 결과이다. 그림 8에서알 수 있는바와 같이, 제안하는 센서리스 위상 추정방법은 기존의 전압 센서를 통하여 계통의 위상을 추정하는방법과 동일한 결과를 나타냄을 알 수 있다. 그림 9는 PWM 정류기 모드로 동작될 때 a 상 입력 전류와 기존의 제어기법을 통한 a상 입력 전압, 제안하는 알고리듬을 통한 a상 입력 전압이다. 그림 9에서 알 수 있는바

Fig. 8 Simulation waveform for grid voltage phase estimation

Fig. 9 Comparison of input a phase current and input a phase voltage, sensorless voltage. (PWM rectifier)

와 같이 실제 입력 전압과 센서리스로 알고리듬을 통하여 추정된 입력 전압이 일치하는 것을 알 수 있다.

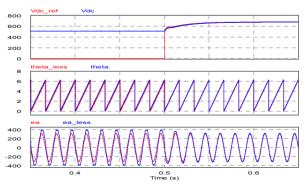

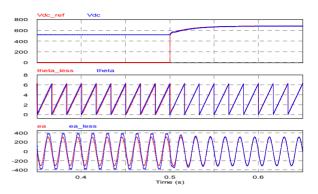

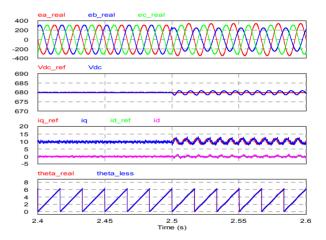

제안하는 알고리듬은 MRAS관측기를 이용하여 입력 전압을 추종하므로 파라미터 변동의 영향을 받을 수 있 다. 그림 10와 그림 11는 입력 인덕터의 파라미터가 각 7 + 20% 오차와 -20% 오차를 가질 경우, 센서리스 기동에 대한 모의 해석 결과이다. 그림의 제일 위 파형 은 비엔나 정류기의 출력 전압을, 가운데 파형은 입력 전압의 위상 정보를, 그리고 마지막 파형은 센서리스로 추정한 A상의 계통 전압을 나타낸다. 그림에서 알 수 있는 바와 같이 입력 인덕터의 ±20% 변동에도 위치 정보를 잘 추종해내며, 입력 전압을 추종함을 알 수 있 다. 이는 비엔나 정류기의 L 필터에 인가되는 전압이 매 우 작은 값이므로 약간의 파라미터 오차가 존재하더라 도 대부분의 모델 전류를 결정하는 것은 계통 전압의 크기와 위상이기 때문이다. 그림 12과 그림 13는 본 알 고리듬의 신뢰성을 확인하기 위하여 계통 전압의 불평 형 조건과 계통 전압의 왜곡 조건에서 센서리스 알고리 듬의 감지 및 제어가 잘 되는 지 모의해석을 실시한 결 과이다. 그림 14는 입력 전압 불평형의 경우 입력 전압 센서리스 알고리듬의 제어 상태를 나타낸다. 입력 전압 의 불평형은 a상의 전압 크기는 110%로 변경하였으며, b상은 입력 전압의 80%로 변경하였고, c상의 전압크기 는 변경하지 않았다. 입력 전압의 불평형은 2.5초에 시 작되며, 입력 전압의 불평형이 발생하여 DC 링크 전압 의 맥동이 증가 하였고, 입력 da축 전류의 맥동 또한 증 가를 하였지만, DC링크 전압과 입력 전류가 제어됨을 알 수 있다. 그림 15는 계통 전압이 왜곡이 발생하는 경 우의 제어 상태를 나타낸다. 계통 전압의 왜곡을 발생시 키기 위하여 입력 전압에 고조파를 실었으며, 5차, 7차, 11차 고조파를 각각 3%, 4%, 2%로 하여 계통 전압에 왜곡을 주었다. 계통 전압의 왜곡은 2.5초에 시작되며, 왜곡이 발생하여 입력 d축 전압의 맥동이 증가하여 위 치 정보의 오차가 발생되었지만, DC 링크 전압과 입력 전류가 제어되었다.

모의해석 해석 결과 본 논문에서 제안한 계통 전압

Fig. 10 Simulation results for the inductor parameter +20% error

센서리스 알고리듬은 파라미터 변동(±20%)과 입력 전 압의 불평형과 왜곡이 발생하였을 경우에도 계통 전압 을 잘 추종하고 비엔나 정류기 시스템을 잘 제어함을 확인하였다.

Fig. 11 Simulation results for the inductor parameter -20% error

Fig. 12 Simulation results for unbalanced source voltage condition

Fig. 13 Simulation results for distorted source voltage

#### 4.2 실험 결과

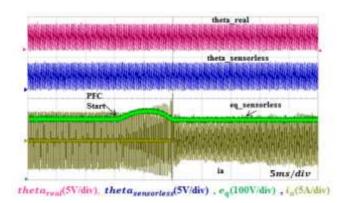

실험 파라미터는 시뮬레이션과 동일한 파라미터를 사용하였다. 그림 14는 실제 위치 정보와 제안하는 알고리듬을 통해 추종되는 위치 정보, 제안하는 알고리듬을 통해 추종된  $e_q^e$ 전압을 나타낸다. 기존의 방법으로 시스템을 동작 시키며, 동작 시키는 중에 제안하는 알고리듬을 동작하는데, 이때의 전체 파형은 그림 14(a)의 파형이다. 그림 14(a)에서 제안하는 알고리듬을 도중에 동작을 시켜도 위치 정보와  $e_q^e$ 전압을 빠르게 추종해나가는 것을 알 수 있다. PFC가 시작이 될 때 생기는  $e_q^e$ 전압의 오버슛 현상을 PFC시작 후 과도 상태에서 생기는 입력 전류의 오버슛에 의한 현상이다. 그림 14(b)는 그림 14(a)

Fig. 14 Experiment waveform of theta estimation and eq (a) The entire waveform

(b) The expansion waveform

Fig. 15 Experiment waveform of theta estimation and eq, ia

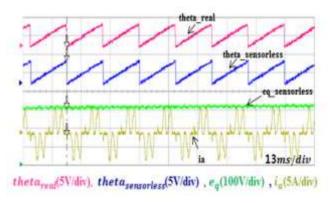

의 확대 파형이며, 제안하는 알고리듬을 동작시켜도 빠른 속도로 추종해나가는 것을 알 수 있다. 그림 15, 16, 17는 실제 위치 정보, 제안하는 알고리듬을 통해 추종된 위치 정보와  $e^e_q$ 전압, a상 입력 전류의 파형을 비엔나 정류기 기동 시에 나타낸 것이다. 그림 15은 전체적인 파형이며, PFC 동작시 과도 상태에서 a상 입력 전류가 비선형적으로 증가하게 되고( $i^e_q$ 는 증가), 이로 인해  $e^e_q$  전압이 과도상태시 오버슛을 갖는 것을 알 수 있다. PFC 동작시  $i^e_a$  또한 비선형적으로 증가하여 위치정보의 오차를 발생 시킬 수 있다. 그림 16은 PFC 동작 초기의

Fig. 16 Experiment waveform of theta estimation and eq, ia (PFC start initial state)

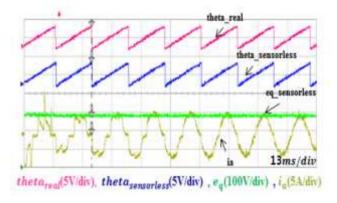

Fig. 17 Experiment waveform of theta estimation and eq, ia (Reach steady-state)

Fig. 18 Comparison of input a phase current and input a phase voltage, sensorless voltage. (PFC mode)

실제 위치 정보, 제안하는 알고리듬을 통해 추종되는 위치 정보와  $e_q^e$ 전압, a상 입력 전류의 파형이며, PFC 동작 초기 입력 전류가 크게 증가하지 않으므로 위치 정보의 오차는 발생하지 않는다. 이는 3.3절에서 설명한이유에 기인한다. 그림 17은 PFC 동작 후 과도 상태를지나 정상 상태에서의 파형이다. a상 입력 전류가 정현파 형태로 제어가 되며, 실제 위치 정보와 제안하는 알고리듬을 통한 위치 정보는 일치하는 것을 알 수 있다. 그림 18은 PWM 동작 중 a상 입력 전류와 a상 실제 전압, 제안된 센서리스 알고리듬을 통해 구한 a상 입력 전압의 비교한 파형이다. 그림에서 알 수 있는바와 같이 a상 입력 전류와 실제 a상 입력 전압, 제안된 센서리스알고리듬을 통해 추종되는 a상 입력 전압의 거의 일치하는 것을 알 수 있다.

## 5. 결 론

본 논문에서는 3상 비엔나 정류기 입력 전압 센서리스 제어 알고리듬을 제안하였다. 제안한 입력 전압 센서리스 제어 알고리듬을 시뮬레이션 및 실험을 통하여 기존의 입력 전압 센서가 있는 비엔나 정류기 제어 알고리듬과 동일한 제어가 가능한 것으로 입증하였다. 또, 입력 전압을 계측 하지 않고 회전좌표계 dq축 전류에 대해 추종하기 위해 기준이 되는 모델 전류를 세우는 MRAS 관측기법을 적용하여 입력 전압 인가가 없는 초기 상태와 PFC 동작시 발생하는 과도상태에서도 입력전압을 추종하였으며 추종된 입력 전압을 통해 위치 정보와 입력 전압 크기를 추종하였다. 본 논문에서 제안한 3상 비엔나 정류기 입력 전압 센서리스 제어 알고리듬적용하면 입력 전압을 계측하는 데에 드는 가격과 시스템 체적을 낮추는 역할을 할 수 있을 것이다.

본 논문은 교육부의 재원으로 한국연구재단의 지원을 받아 연구한 논문입니다. (NO.2013011487) 본 논문은 산업통상자원부의 재원으로 한국에너 지 기술 평가원의 지원을 받아 수행한 연구과제입 니다. (NO. 20114010203030)

#### References

- [1] Byung-chul Yoon, Hag-Wone Kim, Kwan-Yuhl Cho, "Carrier Comparison PWM for Voltage Control of Vienna Rectifier," *Journal of the Korea Academia-Industrial cooperation Society*, Vol. 12, No. 10, pp. 4561–4568, Dec. 2011.

- [2] Sang-Ri Lee, Hag-Wone Kim, Kwan-Yuhl Cho, Byung-Kuk Lim, "A Basic Study on The Vienna Rectifier

- Control Algorithm without Input Voltage Sensor," *Annual Conference of the KIPE*, pp. 115–116, Jun. 2012.

- [3] Byung-chul Yoon, Hag-Wone Kim, Kwan-Yuhl Cho, Byung-Kuk Lim, "A single-carrier comparison PWM for Voltage Control of Vienna Rectifier," *The Transactions of the Korean Institute of Power Electronics*, Vol. 17, No. 2, pp.129–134, Apr. 2012.

- [4] Rixin Lai, Fei Wang, Rolando Burgos, Dushan Boroyevichm Dong Jiang, and Di Zhang, "Average Modeling and Control Design for VIENNA-Type Rectifiers Considering the DC-Link Voltage Balance," *IEEE Trans. on Power Electronics*, Vol. 24, No. 11, pp. 2509–2522, Nov. 2009.

- [5] B.-H. Kwon, J.-H. Youm, and J.-W. Lim, "A line-voltage-sensorless synchronous rectifier," *IEEE Trans. Power Electron.*, Vol. 14, pp. 966-972, Sep. 1999.

- [6] T. Ohnuki, O. Miyashita, P. Lataire, and G. Maggetto, "Control of a three-phase PWM rectifier using estimated AC-side and DC-side voltages," *IEEE Trans. Power Electron*, Vol. 14, pp. 222 - 226, Mar. 1999.

- [7] T. Ohnishi and K. Fujii, "Line voltage sensorless three phase PWM converter by tracking control of operating frequency," in Proc. Power Conversion Conf., pp. 247 -252, 1997.

- [8] Ralph Kennel, Pawel Szczupak, "Sensorless Control of 3 Phase PWM Rectifier," in Proc. IECON, pp. 2493–2498, 2005.

- [9] Hee-Keun Shin, Byoung-Woong An, Hag-Wone Kim, Kwan-Yuhl Cho, and Shin-Myung Jung, "Switch Open Fault Detection and Tolerant Operation Method for Three Phase PWM Rectifier," *The Transactions of the Korean Institute of Power Electronics*, Vol. 17, No. 3, pp. 266–273, June 2012.

- [10] Keun-Woo Han, Xiao Dong Qiu, Young-Gook Jung, Young-Cheol Lim, "Source Voltage Sensorless Three-Phase Z-source PWM Converter," *Annual Conference of the KIPE*, pp. 115–116, Nov. 2012.

- [11] Nobuyuki Matsui, "Sensorless PM Brushless DC Motor Drives," *IEEE Trans. on Industrial Electronics*, Vol. 43, No. 2, pp. 300–308, April 1996.

- [12] Hung-Seok Chu, Chang-Gun Cheon, Jin-Woo Ahn, Cheul-U Kim, "Sensorless Control of Three Phase Converter using estimated Input Phase-Voltage and DC-link Voltage," *Annual Conference of the KIPE*, pp. 227-230, Jul. 2001.

## 이상리(李相梨)

1987년 12월 9일생. 2012년 충주대 제어계 측공학과 졸업. 2012년~2014년 2월 한국교 통대 대학원 제어계측공학과 졸업. 2014년 ~현재 ㈜동아일렉콤 연구원.

#### 김학원(金學源)

1968년 3월 30일생. 1989년 고려대 전기공학과 졸업. 1991년 한국과학기술원 전기및전자공학과 졸업(석사). 2005년 동 대학원전기및전자공학과 졸업(공박). 1991년~2008년 LG전자(주) 디지털 어플라이언스 연구소

책임연구원. 2008년~현재 한국교통대 제어계측공학과 부교수. 당 학회 총무이사.

# 조관열(趙官烈)

1964년 2월 20일생. 1986년 서울대 전기공학과 졸업. 1988년 한국과학기술원 전기및전자공학과 졸업(석사). 1993년 동 대학원전기및전자공학과 졸업(공박). 1993년~2004년 LG전자(주) DA연구소 책임연구원. 2004

년~현재 한국교통대 제어계측공학과 교수. 당 학회 편집위원장.

# 황순상(黃淳相)

1971년 10월 5일생. 2010년 충주대 정보제 어공학과 졸업. 2012년 3월~2014년 2월 한국교통대 대학원 정보제어공학과 석사(졸업). 1995년~현재 ㈜동아일렉콤 전원연구소 책임연구원.

#### 윤병철(尹炳喆)

1985년 11월 1일생. 2010년 충주대 정보에 어공학과 졸업. 2010년~2012년 2월 대학원 제어계측공학과 졸업(석사). 2012년~현재 ㈜동아일렉콤 연구원.