# A Study on Characteristic Improvement of IGBT with P-floating Layer

## Sinsu Kyoung\*, Eun Sik Jung\* and Ey Goo Kang<sup>†</sup>

**Abstract** – A power semiconductor device, usually used as a switch or rectifier, is very significant in the modern power industry. The power semiconductor, in terms of its physical properties, requires a high breakdown voltage to turn off, a low on-state resistance to reduce static loss, and a fast switching speed to reduce dynamic loss. Among those parameters, the breakdown voltage and on-state resistance rely on the doping concentration of the drift region in the power semiconductor, this effect can be more important for a higher voltage device. Although the low doping concentration in the drift region increases the breakdown voltage, the on-state resistance that is increased along with it makes the static loss characteristic deteriorate. On the other hand, although the high doping concentration in the drift region reduces on-state resistance, the breakdown voltage is decreased, which limits the scope of its applications. This addresses the fact that breakdown voltage and on-state resistance are in a trade-off relationship with a parameter of the doping concentration in the drift region. Such a trade-off relationship is a hindrance to the development of power semiconductor devices that have idealistic characteristics. In this study, a novel structure is proposed for the Insulated Gate Bipolar Transistor (IGBT) device that uses conductivity modulation, which makes it possible to increase the breakdown voltage without changing the on-state resistance through use of a P-floating layer. More specifically in the proposed IGBT structure, a P-floating layer was inserted into the drift region, which results in an alleviation of the trade-off relationship between the on-state resistance and the breakdown voltage. The increase of breakdown voltage in the proposed IGBT structure has been analyzed both theoretically and through simulations, and it is verified through measurement of actual samples.

Keywords: IGBT, P-floating, Power device

#### 1. Introduction

IGBT is a switching device widely used in the contemporary industry because of its various advantages. IGBT combines the structures of both Metal-Oxide-Semiconductor Field Effect Transistor (MOSFET) and Bipolar Junction Transistor (BJT), in such a way that utilizes the advantages both [1]. MOSFET is a voltage control device that has the advantage of a rapid switching speed. BJT is a two-carrier device with the advantage of the superior on-state characteristic. As such, IGBT has both the advantages of being a voltage control device and a twocarrier device. Besides, due to conductivity modulation that uses high level injection, the on-state resistance does not rely on doping concentration of the N-drift region in IGBT [2]. However, in order to obtain a high breakdown voltage, the length of the N-drift region should be increased. As this elongated N-drift region increases the length of the carrier's flow path, the on-state resistance also increases. Therefore, in IGBT, there exists a trade-off relation between the breakdown voltage and the on-state resistance

Received: August 27, 2013; Accepted: January 1, 2014

which is mediated by the length of the N-drift region [3].

To put it another way, if we were to increase the breakdown voltage in the IGBT device of constant length of the N-drift, we can decrease the on-state resistance by decreasing the length of the N-drift and can make a device with a breakdown voltage that satisfies the design requirement [4]. Moreover, decreasing the length of the N-drift region is very important because it improves the heat emitting characteristic which has a close association with the reliability of the device. Thus, suggesting the structure for the improvement of the breakdown voltage would be very important for improving the margin in the case of IGBT with the same on-state resistance or for improving on-state characteristic and the reliability in the case of IGBT with the same breakdown voltage.

Therefore, this study suggests a novel IGBT structure with a higher breakdown voltage that maintains the same length of N-drift region as that of a conventional IGBT. The study also suggests the fabrication method.

#### 2. Suggestion of the Novel Structure

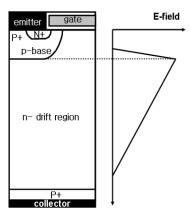

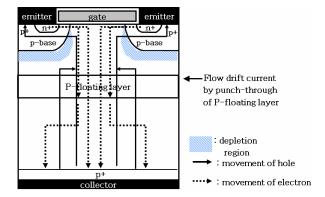

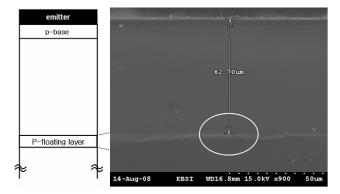

Fig. 1 shows the conventional IGBT structure and the novel IGBT structure proposed in this paper. The structure

<sup>†</sup> Corresponding Author: Department of Photovoltaic Engineering, Far East University, Korea (keg@kdu.ac.kr)

<sup>\*</sup> Department of Electrical Engineering, Korea University, Korea (odin11@korea.ac.kr)

of the proposed IGBT takes the form of inserting a P-floating layer in the N-drift region of the conventional IGBT. As shown in Fig. 1(a), the conventional IGBT has an electric field distribution with the shape of triangle in the off-state [1]. On the contrary, the proposed structure of IGBT has a region with negative charge of depletion region due to P-floating layer in the off-state. So, the electric field which was decreasing from P-base–N-drift junction begins to increase in the P-floating layer and it changes the electric field distribution to increase the whole area. According to the relation of electric field and voltage, the area increase of electric field distribution implies the increase of breakdown voltage.

(a) Conventional IGBT

(b) Proposed IGBT

**Fig. 1.** Structures of the conventional IGBT and proposed IGBT and each's electric field distribution in the off-state

## 3. Theoretical Analysis

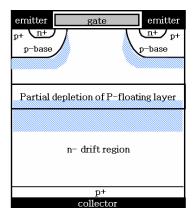

This study conducts an analysis by inserting a P-floating layer in the proposed IGBT in both the on-state and off-state, and then examines the improved characteristics of the proposed IGBT by comparing it to the electrical characteristics of a conventional IGBT.

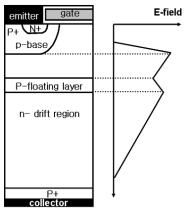

**Fig. 2.** The charge distribution of the proposed IGBT structure in the off-state

**Table 1.** The regional division of N-drift region by charge distribution

| Region no. | Setting of regions                                                  | Division of coordinates |

|------------|---------------------------------------------------------------------|-------------------------|

| (1)        | From P-base to the line before P-floating layer                     | $0 \le x \le d$         |

| (2)        | The whole region of P-floating layer                                | $d \le x \le d+t$       |

| (3)        | From the line after P-floating layer to the end of depletion region | $d+t \le x \le W_d$     |

#### 3.1 Off-state analysis

In the condition where a voltage is not applied to the gate, if a higher voltage is applied to the collector than to the emitter, the P-base–N-drift junction turns to a state of reverse bias and the IGBT turns to the off-state. According to the relation of electric field and voltage shown in Eq. (1), the breakdown voltage is determined by the electric field distribution:

$$E = -\frac{dV}{dx} \tag{1}$$

Besides, according to the Poisson equation shown in Eq. (2), the electric field relies on the charge distribution. Thus, in order to analyze the breakdown voltage, we have to analyze the charge distribution:

$$\frac{dE}{dx} = \frac{q}{\varepsilon} (p + N_d - n - N_a) \tag{2}$$

In order to analyze the electric field, the study researched the charge distribution in the structure of proposed IGBT according to the vertical depth. This is shown in Fig. 2 and Table 1.

The electric field distribution can be obtained by entering the charge distribution of each region divided in Table 1 into the Poisson equation. First, the electric field in Region (1) can be expressed as Eq. 3.

$$E(x) = E(0) - \frac{qN_d}{\varepsilon_s} x = E_{max} - \frac{qN_d}{\varepsilon_s} x$$

(3)

In Eq. 3, E(0) is the electric field in P-base–N-drift junction and as it has the maximum value, it can be indicated as  $E_{max}$ .  $N_d$  is the doping concentration of the N-drift region, and  $\epsilon_s$  is the permittivity of silicon.

In the same way, the electric field of Eq. 4 can be obtained using Poisson's equation for Region (2).

$$E(x) = E_{max} - \frac{qN_d}{\varepsilon_s} d + \frac{qN_p}{\varepsilon_s} (x - d)$$

(4)

$N_p$  is the doping concentration of P-floating layer. For the sake of continuity with Region (1), we used the condition of x=d as the boundary condition in Eq. 3. In the same way, when we use the condition of x=d+t as the boundary condition in Eq. 4, the electric field in Region (3) can be indicated as:

$$E(x) = E_{max} + \frac{qN_p}{\varepsilon_s}t - \frac{qN_d}{\varepsilon_s}(x - t)$$

(5)

In  $x=W_d$ , which is the edge part of the depletion region, the electric field becomes zero. Therefore,  $E_{max}$  is indicated as:

$$E_{max} = \frac{qN_d}{\varepsilon_s} (W_d - t) - \frac{qN_p}{\varepsilon_s} t \tag{6}$$

By entering the  $E_{max}$  of Eq. 6 into Eq. 3, Eq. 4 and Eq. 5, the electric field distribution across the whole region can be described as:

$$E_{max} = \begin{cases} \frac{qN_d}{\varepsilon_s} (W_d - t - x) - \frac{qN_p}{\varepsilon_s} t & (0 \le x \le d) \\ \frac{qN_d}{\varepsilon_s} (W_d - t - d) + \frac{qN_p}{\varepsilon_s} (x - t - d) & (d \le x \le d + t) \end{cases}$$

(7)

$$\frac{qN_d}{\varepsilon_s} (W_d - x) \qquad (d + t \le x \le W_d)$$

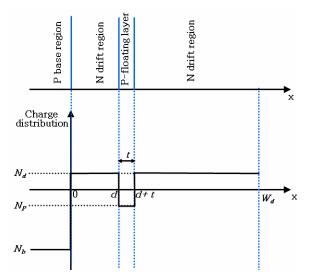

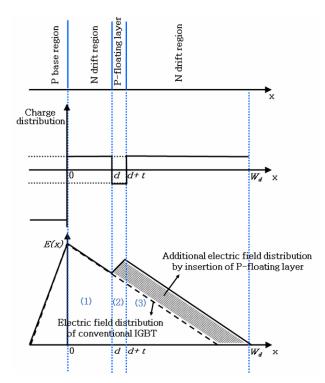

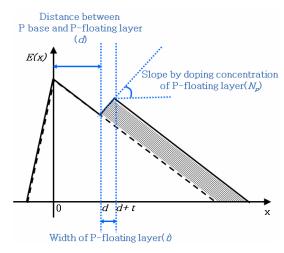

Based on Eq. 7, the electric field distribution is shown in Fig. 3. As shown in Fig. 3, in Region (1) (which is the region ranging from the bottom to the bottom line of the P-floating layer) of the proposed IGBT structure, the electric field decreases according to the vertical depth by the donor ion with positive charge as in the conventional IGBT. However in Region (2) (which is P-floating layer), the electric field is found to be increasing according to the

**Fig. 3.** Electric field distribution for the off-state of the proposed IGBT structure

vertical depth by the acceptor ion with negative charge. The increased electric field decreases by the donor ion in Region (3) (which is the region where depletion layer ends) as in Region (1).

For comparison, we indicated the electric field distribution of the conventional IGBT in Fig. 3 with a dashed line. When we compared the electric field distribution in the conventional IGBT structure with that of the proposed IGBT, the P-floating layer of the proposed IGBT structure reversed the slope of the electric field and generated an additional field distribution as large as the hatched area.

According to Eq. 1, the level of voltage applied to the depletion region equals the integration value of the electric field distribution. Therefore, when the width of depletion region  $(W_d)$  has the maximum value, the voltage becomes the breakdown voltage of IGBT. Thus, we can see that, compared to the conventional IGBT, the proposed IGBT structure with the P-floating layer that forms an additional electric field distribution increases the breakdown voltage. Besides which, the level of the increasing breakdown voltage can be changed depending on the design of P-floating layer.

### 3.2 On-state analysis

When a positive voltage higher than the threshold voltage is applied to the gate and a higher voltage is applied to the collector than to the emitter, a channel connecting the N-drift region with the N source in the P-

base is generated and the IGBT turns to the on-state. The injected holes from the collector, along with the flow of electrons, pass through the N-drift region and flow to the emitter's contact through the P-base. As both the electrons and the holes of IGBT generate current, it is therefore a two carrier device and suitable for controlling a high current

For this reason, in the device proposed in this study, the added P-floating layer should not interrupt the flow of electrons and holes. In that the P-floating layer does not prevent the flow of electrons and holes, the P-floating layer should be depleted completely and there should be the phenomenon of punch-through. When the P-floating layer is completely depleted, electrons and holes can pass through P-floating layer as a drift current. As shown in Fig. 4, when the P-floating layer is completely depleted, all electrons and holes can pass through it.

If the P-floating layer is not completely depleted, the P-floating layer and the N-drift region become the same state with the PN junction state with reverse bias. Then, an electric field is applied to P-floating layer – N-drift junction and the current does not flow. Fig. 5 shows the state of the depletion region when the current does not flow

**Fig. 4.** Diagram showing the carrier flow of the proposed IGBT structure in the on-state

**Fig. 5.** Diagram showing the distribution of the depletion region when the current does not flow in the onstate of the proposed IGBT structure

in the proposed IGBT structure due to the incomplete depletion of the P-floating layer and a subsequent punch-through in the on-state does not occur.

Therefore, when designing the structure of proposed IGBT, it is important to completely deplete the P-floating layer and make the punch-through happen in the on-state. For this reason, we need to model the condition in which the punch-through occurs and all the electrons and holes pass through the P-floating layer. In the P-floating layer, the conditions for punch-through can be induced through general PN junction theories. Upon application of a voltage, if the width of the depletion region formed in P-floating layer-N-drift junction exceeds the width of P-floating layer, the P-floating layer can be completely depleted. When we posit  $V_{app}$  as the applied voltage to P-floating layer – N-drift junction, a conditional expression such as that shown in Eq. 8 can be deduced.

$$W_p = \sqrt{\frac{\varepsilon_s(V_{bi} + V_{app})}{q} \left(\frac{N_d}{N_d(N_d + N_p)}\right)} > t$$

(8)

When the design of the proposed IGBT structure satisfies Eq. 8, the P-floating layer is completely depleted and the punch-through phenomenon occurs. This enables the current to flow and the width of P-floating layer is restricted by Eq. 8.

#### 4. Simulation

For the validity of theoretical analysis on the proposed structure, this study used the TSUPREM-4 process simulation tool and the MEDICI device simulation tool to design the IGBT structure and analyze the electrical characteristics. We used the design parameters shown in Eq. 7 to determine improvements to the characteristics of the IGBT structure to conduct the optimization process.

#### 4.1 Design parameter

In Eq. 7 and Fig. 3, we can see that the width t of the P-floating layer, the doping concentration N<sub>p</sub>, and the distance d between the P-floating layer and the P-base all determine the area of the additional electric field distribution. This means that the increased level of breakdown voltage of the proposed IGBT is determined by 3 design parameters of the P-floating layer. In order to understand the breakdown voltage determined by the design parameters, the influence of the electric field distribution of the design parameters is indicated as:

As stated earlier, the 3 kinds of design parameter are not only important for the breakdown voltage but also for the on-state. As the P-floating layer should be completely depleted, the width t of the P-floating layer and the doping concentration  $N_{\rm p}$  are restricted by Eq. 8. That is, if t and

**Fig. 6.** Change of the electric field distribution depending on the design parameters of the P-floating layer

$N_p$  are excessively increased in order to increase the breakdown voltage, the P-floating layer cannot be depleted completely and therefore the current may not flow in the on-state. As this is a condition in which the device does not normally operate, it is impossible to use this as the switching device.

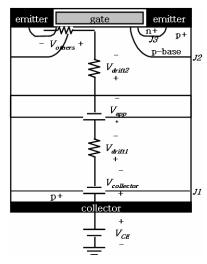

Similar to other design parameters, there also exists a restriction in the distance d between the P-floating layer and the P-base. The more distance d decreases, the region of the increasing electric field distribution becomes wider and the breakdown voltage increases. However, the onstate characteristic limits the minimum value of distance d. In order to understand the limitations of the distance d, the voltage drop for each region in the on-state is shown in Eq. 9 and Fig. 7.

$$\begin{split} V_{CE} &= V_{collector} + V_{N-drift1} + V_{app} \\ &+ V_{N-drift2} + V_{channel} + V_{N-emitter} \end{split} \tag{9}$$

If we posit  $V_{app}$  as the voltage applied to the P-floating-N-drift junction, we can see that  $V_{app}$  is applied after the voltage consumption of  $V_{N\text{-drift}1}$  from Eq. 9 and Fig. 7. As the  $V_{N\text{-drift}1}$  is determined by the resistance of the N-drift region, it can be expressed as in Eq. 10.

$$V_{N-driftl} = I_{on} R_{N-driftl} = I_{on} \frac{1}{q \mu_n N_d} \frac{l_l}{A}$$

(10)

As shown in Eq. 10, if the distance  $l_1$  between the collector and the P-floating layer increases, the resistance increases, which increases  $V_{N\text{-drift}1}$ . Conclusively, this leads to the decrease of  $V_{app}$  and also decreases the depletion region of the P-floating layer, to make punch-through not occur. For this reason, a limitation occurs in the distance between P-floating layer and the collector. This means that there's a limitation in the distance d between P-floating layer and P-base.

**Fig. 7.** Voltage drop configuration between the collector and the emitter of the proposed IGBT structure in the on-state and its equivalent circuit.

**Table 2.** A comparison design parameters in the structures of the conventional IGBT and the proposed IGBT

| Design parameter    |                                  | Conventional       | P-floating                                                                             |

|---------------------|----------------------------------|--------------------|----------------------------------------------------------------------------------------|

|                     | t(µm)                            | -                  | 2/4/6                                                                                  |

| P-floating<br>layer | $N_p(cm^{-3})$                   | -                  | $4 \times 10^{13} / \\ 8 \times 10^{13} / \\ 1.6 \times 10^{14} / \\ 4 \times 10^{14}$ |

| (                   | Cell pitch(μm)                   | 24                 |                                                                                        |

| Cha                 | annel length(μm)                 | 1.8                |                                                                                        |

| N-drift             | width(µm)                        | 215                |                                                                                        |

| IN-UIIII            | Concentration(cm <sup>-3</sup> ) | 8×10 <sup>13</sup> |                                                                                        |

| Gate                | Oxide thickness(µm)              | 0.1                |                                                                                        |

|                     | width(µm)                        | 14                 |                                                                                        |

| P-base              | width(µm)                        | 3.5                |                                                                                        |

| P-base              | Concentration(cm <sup>-3</sup> ) | 2×10 <sup>18</sup> |                                                                                        |

| P-contact           | width(µm)                        | 0.4                |                                                                                        |

| P-contact           | Concentration(cm <sup>-3</sup> ) | 4×10 <sup>19</sup> |                                                                                        |

| N-emitter           | width(µm)                        | 0.32               |                                                                                        |

|                     | Concentration(cm <sup>-3</sup> ) | $1 \times 10^{20}$ |                                                                                        |

| P-collector         | width(µm)                        | 1                  |                                                                                        |

|                     | Concentration(cm <sup>-3</sup> ) | $1 \times 10^{18}$ |                                                                                        |

To summarize, the breakdown voltage can be increased through the regulation of the 3 design parameters of the P-floating layer. However, the design parameters are restricted by the on-state characteristic.

In order to compare the structures of the conventional IGBT and the proposed IGBT, all the design parameters are shown in Table 2.

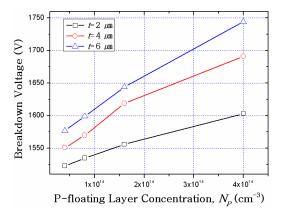

Through the parameters given in Table 2, we set the electrical characteristics obtained from the conventional IGBT design as references for comparison. Further, for the optimization of the proposed IGBT, this study demonstrates the electrical characteristics that result from a change in width t of the P-floating layer and the doping concentration  $N_{\rm p}$  as in Fig. 8.

As shown in Fig. 8, with the increase in the width t of

**Fig. 8.** Change of breakdown voltage according to the width and concentration of P-floating layer

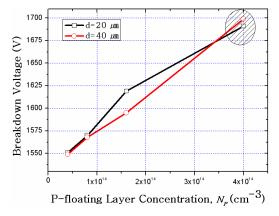

**Fig. 9.** Change of the breakdown voltage in accordance with the distance between the P-floating layer and the P-base.

the P-floating layer and in the doping concentration  $N_p$ , the breakdown voltage also increases. However,  $N_p$  and t are limited by the on-state characteristic. If  $N_p$  is bigger than  $4.0\times10^{14} \text{cm}^{-3}$ , the P-floating layer of the proposed IGBT does not punch through, and it cannot turn on. For the same reason, t also cannot exceed 6µm. This is a result consistant with the theoretical analysis. For the case when the distance d between the P-base and the P-floating layer is  $20\mu m$  and  $40\mu m$ , the change depending on  $N_p$  is shown in Fig. 9.

In the doping concentration range of the P-floating layer where the on-state is guaranteed, we can see that it has the bigger breakdown voltage of d=20 $\mu$ m. This is consistant with the prediction of the theoretical analysis. However, in the case when N<sub>p</sub>=4.0×10<sup>14</sup>cm<sup>-3</sup>, which does not turn-on, it shows a bigger breakdown voltage of d=40 $\mu$ m. This result is contrary to the theoretical analysis. We can conclude that the theoretical analysis is only valid in the condition where punch-through occurs and the IGBT becomes turned on through the complete depletion of the P-floating layer.

Lastly, in the case when it had the highest breakdown voltage guaranteeing that the the proposed IGBT structure turns on, was the case where t=6 $\mu$ m and N<sub>p</sub>=1.6×10<sup>14</sup>. The

**Table 3.** Comparison of the electrical characteristics in the conventional IGBT structure and the proposed IGBT structure.

| Structure    | Breakdown voltage | On-state voltage drop |

|--------------|-------------------|-----------------------|

| Conventional | 1486V             | 1.8V                  |

| Suggested    | 1644V             | 1.8V                  |

comparison of electrical characteristics in this case is shown in Table 3.

Compared to the conventional IGBT structure, the breakdown voltage of the proposed IGBT structure with a P-floating layer can increase by as much as 158V. As well, as was predicted in theoretical analysis, the on-state voltage drop can be maintained at a constant 1.8V. The result is meaningful because it proved the validity of the theoretical analysis on the proposed IGBT structure through the simulation.

## 5. Experiments

As the analysis of electrical characteristics through simulation hypothesized the ideal case, the non-idealistic effects and costs that occur in the course of the fabrication process should be considered.

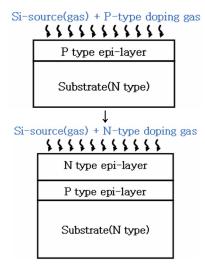

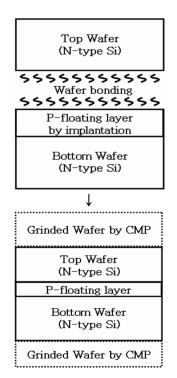

#### 5.1 Fabrication method

The additional fabrication that the proposed IGBT structure in this paper requires is the process for inserting the P-floating layer,. The two kinds of fabrication method used to insert a P-floating layer into the N-drift region are shown in Figs. 10 and Fig. 11. These are epitaxy and wafer bonding with CMP (Chemical Mechanical Polishing). Epitaxy requires a high level of technology and many special requirements. This increases the cost of fabrication. On the other hand, using wafer bonding and CMP is

Fig. 10. P-floating fabrication using the epitaxy process

**Fig. 11.** P-floating fabrication using wafer bonding and CMP

**Fig. 12.** SEM image of a P-floating IGBT structure fabricated for the measurement

relatively cheaper. However the defects and traps caused by the wafer bonding process increases resistance in onstate operation, and can be the cause of leakage of current in off-state operation. Therefore we have to examine the change in the electrical characteristics caused by the non-idealistic effects through the actual fabrication process. For this, we fabricated both the conventional IGBT structure and the proposed IGBT structure using wafer bonding and CMP, and then examined the fabrication state of the samples as shown in Fig. 12 through the vertically cut Scanning Electron Microscope (SEM) image. In addition, by comparing the electrical characteristics of the proposed IGBT structure and the conventional IGBT structure through the fabricated sample, we identified the improvement of the proposed IGBT structure.

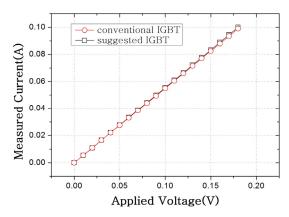

**Fig. 13.** Result of measuring the I-V curve of the conventional IGBT structure and the proposed IGBT structure

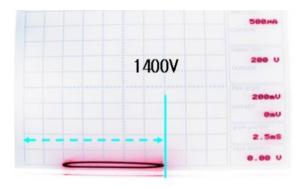

(a) Breakdown voltage of the conventional IGBT structure

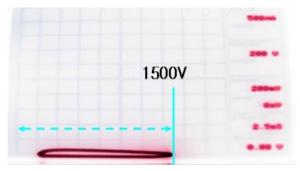

(b) Breakdown voltage of the proposed IGBT structure

**Fig. 14.** Result of measuring the breakdown voltage of the conventional IGBT and the proposed IGBT structures

#### 5.2 Results of measurement

Fig. 13 shows the I-V curve for the analysis of the onstate characteristic. As the slope of the I-V curve implies the resistance, we can see from Fig. 13 that the conventional IGBT structure and the proposed IGBT structure have almost the same on-state resistance. This indicates that any traps and defects, which can be expected to be caused by the wafer bonding process, have hardly influenced the onstate characteristic. Fig. 14 shows the result of the measurement of the offstate for the Breakdown voltage measurement. As shown in Fig. 14, the conventional IGBT structure showed a breakdown voltage of 1400V, and the proposed IGBT structure showed a breakdown voltage of 1500V. This indicates that the P-floating layer in the proposed structure increased the breakdown in the actually fabricated structure as was predicted by the theoretical analysis and simulation, and that it also operated well in the on-state. In the actual fabricated device, the proposed IGBT structure a higher the breakdown voltage than that of the conventional IGBT structure by as much as 100V.

However, this increase in the range of the breakdown voltage shows the result of a smaller increase than the expected increase of 158V from the simulation. The reason that the increased range of breakdown voltage was reduced compared to the simulation would be the influence of current leakage caused by the traps and defects from the wafer bonding process. However, even though we consider the decrease in the improvement of the breakdown voltage due to non-idealistic effects, the improvement of the breakdown voltage by 100V is sufficiently significant to be declared an electrical characteristic improvement.

#### 6. Conclusion

This paper suggests an IGBT structure that inserts a P-floating layer in the N-drift region in order to moderate the trade-off relation between the on-state resistance and breakdown voltage of a conventional IGBT.

The P-floating layer of the proposed IGBT structure changes the electric field distribution in the off-state and increases the breakdown voltage. Subsequently, P-floating layer is completely depleted in the on-state and does not influence the flow of electrons and holes to maintain the on-state resistance constantly.

This characteristic of the proposed IGBT structure is examined through theoretical analysis and simulation. In order to consider the non-idealistic effects, it is also examined through experimental data created by actual fabrication of the device. In each stage, the constant on-state resistance and increased breakdown voltage are shown, and the actual device shows an increase in the breakdown voltage of 100V. This indicates that the proposed IGBT structure shows a significant increase in its electrical characteristics and also in its real conditions, and it moderates the trade-off relation between the breakdown voltage andits on-state resistance.

This improvement can decrease power dissipation through low on-state resistance. As the suggested IGBT structure has an identical breakdown voltage to the conventional IGBT structure, the suggested IGBT structure can have a lower on-state resistance than the conventional IGBT structure. According to Ohm's Law and the formulae of power consumption, the suggested IGBT structure

dissipates small amounts of power compared to the conventional IGBT structure.

Also, fabrication methods that insert a P-floating layer are suggested in this paper. The method used in this paper is wafer bonding and CMP. It is meaningful that the method of wafer bonding and CMP is cheaper than epitaxy. This paper proposes a novel IGBT structure that has an increased breakdown voltage and a fabrication method that is not only cheaper, but also does not cause the electrical characteristics to deteriorate.

## Acknowledgements

This work (Grants No.C0123748) was supported by Business for Cooperative R&D between Industry, Academy, and Research Institute funded Korea Small and Medium Business Administration in 2013.

#### References

- B. J. Baliga, "Power semiconductor devices", PWS Publishing Company, 1996

- [2] Maasayasu ISHIKO, "A Novel PT-IGBT with a p-/n+ Buffer Layer", ISPSD, pp. 341-344, 2003

- [3] Moriaki Mizuno, "A 3-mW 1.0-GHz silicon-ECL dual-modulus prescaler IC", IEEE J. solid-state circuit, vol. 27, no. 12, pp. 1794-1798, Dec. 1992.

- [4] Jong-Seok Lee, Ey-Goo Kang, Man Young Sung, "Shielding region effects on a trench gate IGBT", Microelectronics Journal Vol. 39, p. 57, 2008

- [5] Yoshiyuki Hattori, Kyoko Nakashima, Makoto Kuwahara, Tomoyuki Yoshida, Shoichi Yamauchi and Hitoshi Yamaguchi, Proceedings of International symposium on Power Semiconductor Devices & ICs, Kitakyushu(2004), pp.189-192

- [6] E.G. Kang, S.H. Moon and M.Y. Sung, Microelectronics journal, Vol. 32, Issue. 8(2001), pp. 641-647.

- [7] E.G. Kang and M.Y. Sung, Solid-State Electronics, Vol.46, Issue.2(2002), pp. 295-300.

- [8] E.G. Kang, S.H. Moon, S.S. Kim and M.Y. Sung, Transactions on Electrical and Electronic Materials, Vol. 2, No.1(2001), pp.32-38.

- [9] E.G. Kang and M.Y Sung, Transactions on Electrical and Electronic Materials, Vol. 2, No. 3(2001), pp.33-37.

- [10] J.S. Lee, H.H. Shin, H.S. Lee, E.G. Kang and M.Y. Sung, International conference on Power Electronics, (2007), pp.62-65.

- [11] J.S. Lee, E.G. Kang and M.Y. Sung, Microelectronics journal, Vol.39, Issue. 1(2008), pp.57-62.

- [12] Y.H. Kim, H.S. Lee, S.S. Kyung, Y.M. Kim, E.G. Kang and M.Y. Sung, Integrated Circuit Design and

- Technology and Tutorial (2008), pp. 71-74.

- [13] S.S Kyoung, J.S. Lee, S.H Kwak, E.G. Kang and M.Y. Sung, Electron Device letters, IEEE, Vol. 30, Issue.1 (2009), pp. 82-84.

- [14] S.J. Hwang, J.I. Lee, E.G. Kang and M.Y. Sung, Integrated Circuit Design and Technology and Tutorial (2008), pp. 13-16.

- [15] J.S. Lee, H.H Shin, H.S. Lee, E.G. Kang and M.Y. Sung, International Workshop on Physics of semi-conductor Devices(2007), pp. 799-802.

- [16] E. G. Kang, S. H. Moon and M.Y. Sung, TENCON Vol. 1(2001), pp. 473-479.

**Sinsu Kyoung** He received the B.S. and M.S. degree in Electrical Engineering from Korea University, in 2006 and 2009. He is the head of research center in Power Cube Semiconductor Co. Especially, he is interested in Power semiconductor device and silicon carbide device.

Eun Sik Jung He received Ph.D. in Electrical Engineering from Korea University. His research interests include readout integrated circuit for uncooled IR detector and high-voltage power devices. Now, He is the chief executive officer in MapleSemi Co.

**Ey Goo Kang** He received M.S and Ph.D. degree in Electrical Engineering from Korea University. He is currently the professor in dept. of photovoltaic Engineering at Far East University. His research interests are Smart Power Devices and Power IC.