# 단상 계통연계형 인버터의 SRF-PLL 옵셋 오차로 인한 전류 맥동 저감에 관한 연구

(A Study on Current Ripple Reduction Due to Offset Error in SRF-PLL for Single-phase Grid-connected Inverters)

황선환\* · 황영기 · 권순걸\*\*

(Seon-Hwan Hwang · Young-Gi Hwang · Soon-Kurl Kwon)

#### **Abstract**

This paper presents an offset error compensation algorithm for the accurate phase angle of the grid voltage in single-phase grid-connected inverters. The offset error generated from the grid voltage measurement process cause the fundamental harmonic component with grid frequency in the synchronous reference frame phase lock loop (PLL). As a result, the grid angle is distorted and the power quality in power systems is degraded. In addition, the dq-axis currents in the synchronous reference frame and phase current have the dc component, first and second order ripples compared with the grid frequency under the distorted grid angle. In this paper, the effects of the offset and scaling errors are analyzed based on the synchronous reference frame PLL. Particularly, the offset error can be estimated from the integrator output of the synchronous reference frame PLL and compensated by using proportional-integral controller. Moreover, the RMS (Root Mean Square) function is proposed to detect the offset error component. The effectiveness of the proposed algorithm is verified through simulation and experiment results.

Key Words: Single-phase Grid-connected Inverter, Offset Error, Integrator Output, Root Mean Square

Tel: 055-249-2744, Fax: 0505-999-2161

E-mail: seonhwan@kyungnam.ac.kr

접수일자 : 2014년 8월 14일 1차심사 : 2014년 8월 21일 심사완료 : 2014년 9월 23일

#### 1. 서 론

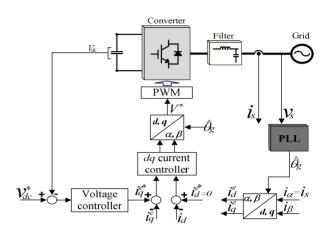

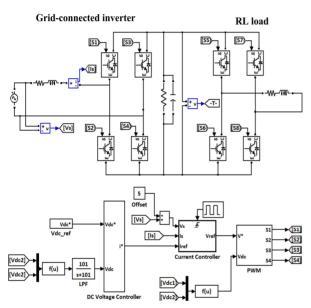

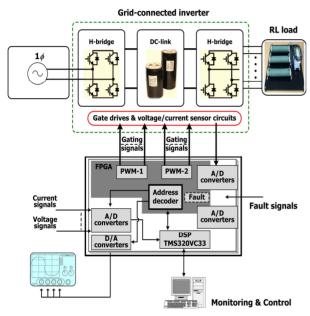

계통연계형 인버터의 경우, 소형 풍력, 태양광 발전 및 가정용 연료전지 등과 같은 신재생에너지의 상용화와 더불어 분산전원 시스템에 대한 기술 개발의 필요성 증대로 인하여 소형 분산발전 시스템의 핵심장치로서 역할이 매우 중요하다고 할 수 있다[1-5]. 일반적으로 단상 계통연계형 인버터의 운전을 위해서는 그림 1에서 볼 수 있듯이 계통전원의 위상 및 크기 검

<sup>\*</sup> 주저자 : 경남대학교 전기공학과 조교수

<sup>\*\*</sup> 교신저자 : 경남대학교 전기공학과 교수

<sup>\*</sup> Main author: Dept. of Electrical Eng., Kyungnam Univ., Korea

<sup>\*\*</sup> Corresponding author: Dept. of Electrical Eng., Kyungnam Univ., Korea

출을 위한 위상 동기 루프(PLL: Phase Locked Loop) 제어, 전원측 전류제어, 직류단 전압제어 및 전력품질 개선 알고리즘 등이 요구된다. 이러한 단상 계통연계형 인버터의 주요 구성 요소 중 PLL 제어는 계통전원의 위상각에 대하여 동기화를 위해 사용되므로 전력 변환 시스템의 전력 품질, 안정성 및 신뢰성에 영향을 미칠 수 있다[4-8].

단상 계통연계형 인버터의 PLL 제어와 관련된 이전의 연구는 주로 계통전압 고조파, 주파수 변동 또는 위상 변동과 같은 왜곡과 과도 상태에서 PLL 제어 시스템의 성능 향상을 위해 진행되었다[6-9].

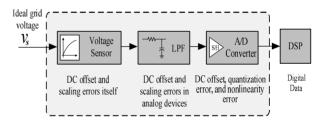

그러나 그림 2에서 볼 수 있듯이 계통전압을 측정함에 있어 전압센서와 아날로그 신호처리 경로에서 발생하는 오차로 인해 PLL 제어시스템의 성능에 큰 영향을 미칠 수 있다[10-12]. 이는 계통전원과의 위상 동기화 문제로 전체 시스템의 동적 성능이 저하될 수 있다. 계통전압은 일반적으로 전압센서, 연산 증폭기를이용한 매칭회로, 필터회로 및 A/D 컨버터 등을 통해측정된다. 그 결과 전압센서, 아날로그 소자 및 A/D 컨버터의 비선형 등으로 인해 회로를 잘 설계하더라도 옵셋과 스케일 오차가 발생할 수 있다.

이와 관련된 기존 연구에서는 동기 좌표계 PLL 제어 루프내의 동기 좌표계 dq축 전압 성분에 대한 옵셋 및 스케일 오차 분석을 통해 전원 주파수의 1배 맥동 성분 발생함을 보였으며, 그로 인해 추정된 전원 위상 각이 왜곡됨을 확인하였다[12]. 또한 옵셋 오차의 검출 방법으로 적분 기법을 제시하였으나, 2회의 적분 동작을 요구하고 맥동 성분에 따라 적분 구간을 가변시켜 검출 동작을 수행해야하는 특징이 있다.

본 논문에서는 단상 계통연계형 인버터의 SRF-PLL 기법 적용시 계통전압을 측정함에 있어서 발생되는 옵셋 및 스케일 오차로 인한 왜곡된 전원 위상각이 동기 좌표계 dq축 전류와 상전류 맥동에 미치는 영향을 살펴보았다. 그 결과 새로운 옵셋 오차 보상 알고리즘을 제안하였다. 제안한 알고리즘은 SRF-PLL의 적분기 출력을 검출 신호로 선정하였고, RMS기법을 통해서 옵셋 오차를 검출하였다. 또한 검출된 옵셋 오차 성분은 비례-적분 제어기에 의해 옵셋 오차를 추종하여 보상해 줌으로서 출력 상전류와 동

기 좌표계 d축 전류에 포함된 직류 성분, 전원 주파수 1배 및 2배 맥동을 제거할 수 있다. 시뮬레이션 및 실험을 통하여 제안된 옵셋 오차 검출 및 보상 알고리즘의 타당성을 검증하였다.

그림 1. 기존 단상 계통연계형 인버터의 블록도 Fig. 1. Block diagram of conventional single-phase grid-connected inverters

그림 2. 계통전압의 측정경로 Fig. 2. Measurement path of grid voltage

## 2. 본 론

#### 2.1 SRF-PLL 옵셋 오차로 인한 영향

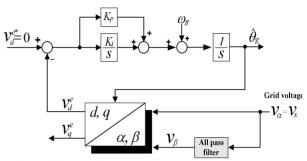

그림 3은 단상 계통연계형 인버터의 SRF-PLL 제어를 위해 전역필터(All Pass Filter: APF)를 사용하여 90° 위상 지연시킨 후 발생된 가상의 전압과 동기 좌표계를 이용한 PLL 구조를 나타내고 있다[12].

계통전원의 전압은 전압센서를 통해서 측정 되는데, 전압센서의 비선형성과 측정 경로상의 아날로그 소자 양(+)과 음(-)의 전압 불균형 및 연산 증폭기 자체의 특성으로 인하여 옵셋 오차를 피할 수 없다. 또한 실제 운전 상태에서 온도 변화에 따른 옵셋의 변동이 발생하게 된다. 옵셋 오차를 포함한 정지 좌표계 dq축 의 전원전압은 식 (1)과 같이 표현할 수 있다[12].

$$\begin{bmatrix} v_{d\_error}^s \\ v_{d\_error}^s \end{bmatrix} = \begin{bmatrix} -V_m \sin\theta_g + \Delta_O \\ V_m \cos\theta_g + \Delta_O \end{bmatrix}$$

(1)

여기서  $\Delta_O$ 는 옵셋 오차,  $V_m$ 은 전원 전압의 최대값,  $\theta_g$ 는 전원 위상각,  $v_{dq\_error}^s$ 는 정지 좌표계 dq축 전원 전압이다.

식 (1)의 정지 좌표계 dq축 전원전압을 추정된 전원 위상각  $\hat{\theta_g}$ 으로 좌표 변환하면 식 (2)와 같이 동기 좌표계 dq축 전원전압을 나타낼 수 있다.

$$\begin{bmatrix} v_{d\_error}^e \\ v_{q\_error}^e \end{bmatrix} = \begin{bmatrix} \cos \hat{\theta_g} & \sin \hat{\theta_g} \\ -\sin \hat{\theta_g} & \cos \hat{\theta_g} \end{bmatrix} \begin{bmatrix} v_{d\_error}^s \\ v_{q\_error}^s \end{bmatrix}$$

$$= \begin{bmatrix} \Delta_O \cos \hat{\theta_g} + \Delta_O \sin \hat{\theta_g} \\ V_m - \Delta_O \sin \hat{\theta_g} + \Delta_O \cos \hat{\theta_g} \end{bmatrix}$$

(2)

식 (2)에서 알 수 있듯이 SRF-PLL 제어 루프의 동기 좌표계 dq축 전압  $v_{dq\_error}^e$ 은 전원 주파수의 1배 맥동을 포함하게 되며 그로 인해 추정된 전원 위상각  $\hat{\theta_g}$ 이 왜곡된다[12]. 그 결과 왜곡된 전원 위상각을 기준으로 전류제어를 수행할 경우, 계통측 상전류  $i_s$ 가 왜곡되어 시스템 제어 성능을 저하시키게 된다.

왜곡된 전원 위상각으로 상전류를 좌표 변환하여 동기 좌표계 dq축 전류로 정리하면 식 (3)과 같다.

식 (3)으로부터 동기좌표계 dq축 전류  $i_{q\_error}^e$ 와  $i_{q\_error}^e$ 에 옵셋 오차 성분을 포함한 전원 주파수의 1배 맥동이 발생됨을 알 수 있다.

$$\begin{bmatrix} i_{d\_error}^e \\ i_{q\_error}^e \end{bmatrix} = \begin{bmatrix} \cos\theta + \Delta_O & \sin\theta + \Delta_O \\ -\sin\theta + \Delta_O & \cos\theta + \Delta_O \end{bmatrix} \begin{bmatrix} -I_m \sin\theta \\ I_m \cos\theta \end{bmatrix}$$

$$= \begin{bmatrix} I_m \Delta_O (\cos\theta - \sin\theta) \\ I_m \Delta_O (\cos\theta - \sin\theta) + I_m \end{bmatrix}$$

$$(3)$$

식 (3)의 왜곡된 동기 좌표계 dq축 전류로부터 정지 좌표계로 역변환하게 되면 식 (4)와 같이 상전류  $i_{da_{error}}^{s}$ 에 각각 옵셋 오차 성분을 포함한 직류 성분, 전원 주파수 1배 및 2배 맥동이 나타남을 확인할 수 있다.

## 2.2 SRF-PLL 스케일 오차로 인한 영향

그림 3. 단상 PLL의 구조 Fig. 3. Structure of single-phase PLL

$$\begin{split} \begin{bmatrix} i_{d_{-error}}^s \\ i_{q_{-error}}^s \end{bmatrix} &= \begin{bmatrix} \cos\theta + \triangle_O & -\sin\theta + \triangle_O \\ \sin\theta + \triangle_O & \cos\theta + \triangle_O \end{bmatrix} \begin{bmatrix} I_m \triangle_O (\cos\theta - \sin\theta) \\ I_m \triangle_O (\cos\theta - \sin\theta) + I_m \end{bmatrix} \\ &= \begin{bmatrix} 2I_m \triangle_O - I_m \triangle_O \sin2\theta + 2I_m \triangle^{2o} (\cos\theta - \sin\theta) - I_m \sin\theta \\ I_m \triangle_O + I_m \triangle_O \cos2\theta + 2I_m \triangle^{2o} (\cos\theta - \sin\theta) + I_m \cos\theta \end{bmatrix} \end{split}$$

스케일 오차는 계통전압의 크기와 샘플링된 전압의 크기 차이를 말한다. 기본적으로 전압센서의 출력은 A/D 컨버터의 입력 범위를 만족해야 하며, 이를 위해서는 입력 범위에 맞게 이득을 조절해야 한다. 이러한 과정에서 스케일 오차가 발생될 수 있으며, 전압센서와 아날로그 소자의 비선형성에 의해서도 야기될 수 있다[12].

계통전원의 전압을 측정하는 경로에서 포함되는 스케일 오차 성분을  $\Delta_S$ 이라고 하면, 스케일 오차가 포함된 동기 좌표계 dq축 전원전압은 식 (5)와 같이 나타낼 수 있다.

$$\begin{bmatrix} v_{d\_error}^e \\ v_{q\_error}^e \end{bmatrix} = \begin{bmatrix} \cos \hat{\theta}_g & \sin \hat{\theta}_g \\ -\sin \hat{\theta}_g & \cos \hat{\theta}_g \end{bmatrix} \begin{bmatrix} v_{d\_error}^s \\ v_{q\_error}^s \end{bmatrix}$$

$$= \begin{bmatrix} -(1 + \Delta_S) V_m \sin (\theta_g - \hat{\theta}_g) \\ (1 + \Delta_S) V_m \cos (\theta_g - \hat{\theta}_g) \end{bmatrix}$$

$$= \begin{bmatrix} 0 \\ (1 + \Delta_S) V_m \end{bmatrix}$$

(5)

식 (5)로부터 전원 위상각  $\theta_g$ 과 추정된 전원 위상각  $\hat{\theta_g}$ 의 차이가 작은 경우, 스케일 오차  $\Delta_S$ 는 옵셋 오차에 의한 식 (2)와 달리 동기 좌표계 d축 전압 성분에는 존재하지 않으며, 동기 좌표계 q축 전압의 크기에만 영향을 나타내고 있다. 스케일 오차는 계통측 상전류 및 동기 좌표계 dq축 전류에 맥동 성분을 야기하지 않기에 본 논문에서는 옵셋 오차 성분만을 고려하여 검출 및 보상하는 연구를 수행하고자 한다.

# 2.3 제안된 SRF-PLL 옵셋 오차의 보상 알 고리즘

옵셋 오차를 보상함에 있어 SRF-PLL 제어 루프의 동작 특성상 동기좌표계 d축 전압의 경우 '0'으로 전압을 제어하기 때문에 동기 좌표계 q축 전압 또는 동기좌표계 전류 성분을 이용하는 것보다 옵셋 오차를 검출하기 용이하다. 특히 SRF-PLL의 동기좌표계 d축 전압 제어 루프내의 적분항을 관찰하면 옵셋 오차 성분을 안정적으로 검출할 수 있다. 따라서, 본 논문에서는 SRF-PLL 제어 루프의 동기좌표계 d축 전압의 적분기 출력 신호를 맥동 성분을 검출을 위한 기준 신호로 선정하였다. 식 (6)은 옵셋 오차를 포함한 동기 좌표계 d축 전압의 적분기 출력값을 표현하고 있다.

$$\begin{split} \boldsymbol{v}_{d\_integ}^{e} &= K_{i} \int_{0}^{t} (\boldsymbol{v}_{d\_error}^{e}) dt = K_{i} \int_{0}^{t} (\boldsymbol{\Delta}_{O} \cos \widehat{\boldsymbol{\omega}_{g}} t + \boldsymbol{\Delta}_{O} \sin \widehat{\boldsymbol{\omega}_{g}} t) dt \\ &= K_{i} \frac{\boldsymbol{\Delta}_{O}}{\widehat{\boldsymbol{\omega}_{g}} t} \sin \widehat{\boldsymbol{\omega}_{g}} t - K_{i} \frac{\boldsymbol{\Delta}_{O}}{\widehat{\boldsymbol{\omega}_{g}} t} \cos \widehat{\boldsymbol{\omega}_{g}} t \end{split} \tag{6}$$

여기서

$$K_{1}=K_{i}\frac{\Delta_{O}}{\widehat{\omega_{g}}}$$

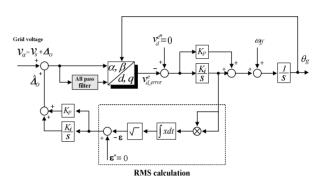

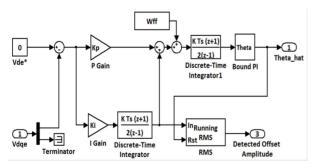

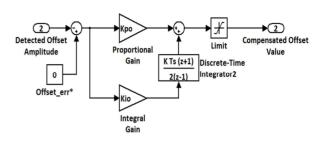

그림 4에서 볼 수 있듯이 SRF-PLL 내의 적분기 출력항으로부터 검출된 맥동 성분은 RMS기법을 이용하면 맥동 성분에 관계없이 직류 신호의 크기로 나타낼 수 있다. 따라서 그림 4와 같이 적분기 출력항에 포

함된 전원 주파수 1배 맥동 성분을 RMS 기법을 이용하여 직류 신호로 변환 및 검출하고 PI 제어기를 통하여 옵셋 오차를 보상함으로서 동기 좌표계 dq축 전류와 상전류에 포함된 옵셋 오차로 인한 직류 및 맥동성분을 제거할 수 있다. 따라서 동기 좌표계 d축 전압의 적분기 출력항  $v_{d_integ}^e$ 에 대한 RMS 기법은 식 (7)과 같이 정의된다.

그림 4. 제안한 옵셋 오차 보상 알고리즘의 블록도 Fig. 4. Block diagram of the proposed offset error compensation algorithm

$$\epsilon = \sqrt{\frac{1}{T} \int_0^t (v_{d\_integ}^e)^2 dt}$$

$$= \sqrt{\frac{1}{T} \int_0^t (K_1^2 \sin^2 \widehat{\omega_g} t - 2K_1^2 \sin \widehat{\omega_g} t \cos \widehat{\omega_g} t + K_1^2 \cos^2 \widehat{\omega_g} t) dt}$$

$$= \sqrt{K_1^2} = K_1$$

$$(7)$$

식 (7)에서 볼 수 있듯이 동기 좌표계 d축 전압의 적분기 출력항에 RMS 기법을 적용하였을 경우, 옵셋 오차를 포함한 직류 성분이 직접적으로 검출됨을 확인할 수 있다. 검출된 옵셋 오차 성분  $\epsilon$ 를 이용하여 PI제어기를 구성하면 옵셋 오차를 보상할 수 있다.

#### 2.4 시뮬레이션 결과

제안한 옵셋 오차 검출 및 보상 알고리즘의 타당성을 검증하기 위하여 Matlab의 Simulink를 사용하여그림 5에서 알 수 있듯이 단상 계통연계형 인버터, 단상 PLL, 전압 및 전류 제어기 등을 포함한 시뮬레이션을 구현하였다. 그림 6은 측정된 계통전압의 정보를

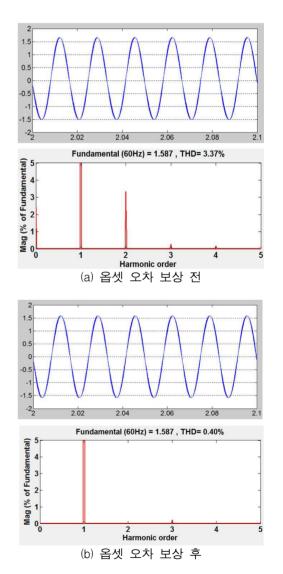

이용한 SRF-PLL 제어 블록도를 보여주고 있다. 전원 위상각 PI 제어기의 적분기 출력이 RMS 함수를 기반으로 옵셋 오차 검출 동작을 수행하고 있음을 알 수 있다. 또한 검출된 옵셋 오차 성분은 그림 7의 PI 제어기 동작에 의해 옵셋 오차가 '0'으로 수렴할 수 있도록 보상을 수행하게 된다. 그림 8은 제안된 옵셋 오차 보상 알고리즘의 타당성을 증명하기 위한 시뮬레이션 파형이며, 계통 전원전압의 2%에 해당하는 옵셋 오차 보상 알고리즘을 적용한 전후에 대하여 비교분석하였다.

그림 5. 단상 계통연계형 인버터의 시뮬레이션 Fig. 5. Simulation of single-phase grid-connected inverter

그림 6. RMS 기법을 포함한 단상 PLL 블록도 Fig. 6. Block diagram of single-phase PLL with RMS method

그림 7. 제안한 옵셋 오차 보상 알고리즘 블록도 Fig. 7. Block diagram of proposed offset error compensation algorithm

그림 8. 옵셋 오차 보상 전후의 계통측 상전류 및 FFT Fig. 8. FFT and grid-side phase current with/without offset error compensation

그림 8 (a)는 보상 전 상전류와 FFT 분석 결과로써 직류 성분과 전원 주파수 2배의 고조파를 포함하고 있음을 알 수 있다. 하지만 제안한 옵셋 오차 검출 및 보상 알고리즘을 통하여 기본파 이외의 직류 및 고조파성분이 크게 감소되었고 결과적으로 THD가 3.37%에서 0.4%로 개선됨을 확인할 수 있었다.

#### 2.5 실험결과

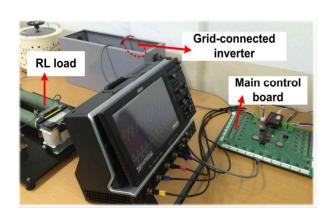

그림 9. 단상 계통연계형 인버터의 시스템 구성 Fig. 9. Configuration of single-phase arid-connected inverter

그림 10. 단상 계통연계형 인버터의 실험장치 Fig. 10. Experimental setup of single-phase grid-connected power inverter

본 논문에서 제안한 단상 계통연계형 인버터의 SRF-PLL 옵셋 오차 보상 알고리즘을 검증하기 위해 그림 9와 같이 시스템을 구성하여 실험을 수행하였으며 실험에 사용된 단상 계통연계형 인버터의 실험장 치는 그림 10에 나타내었다. 기본 구성 및 시스템 제정수는 표 1에 상세히 기술되어 있다.

표 1. 단상 계통연계형 인버터의 사양 Table 1. Specifications of single-phase grid-connected inverter

| Parameter           | Value      |

|---------------------|------------|

| Rated power         | 3kW        |

| Grid voltage        | 220V, 60Hz |

| DC link capacitance | 5240uF     |

| Reactor inductance  | 5mH        |

| Sampling period     | 100us      |

| Switching frequency | 10kHz      |

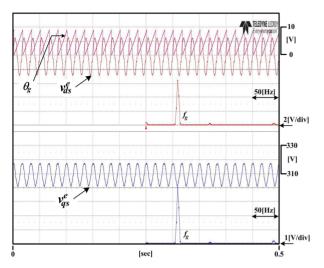

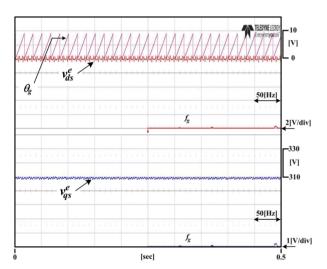

그림 11과 그림 12는 전원전압의 2%에 해당하는 옵셋 오차 보상 전·후의 단상 PLL의 동기 좌표계 dq축 전원전압과 FFT 결과를 보여주고 있다. 그림 11에서 알 수 있듯이 옵셋 오차로 인하여 SRF-PLL 동기 좌표계 dq축 전압에 상당한 크기의 전원 주파수 1배 맥동 성분을 포함하고 있다. 그러나 제안한 옵셋 오차 검출 및 보상 알고리즘을 적용한 후 맥동 성분이 현저히 줄어듦을 그림 12를 통하여 확인할수 있다. 감소된 SRF-PLL 내의 동기 좌표계 dq축 전압의 1배 맥동 성분의 크기는 각각 약 92%와 94%로 크게 감소되었다.

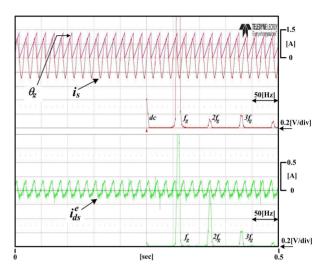

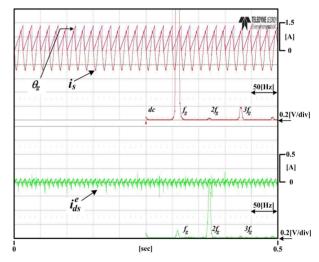

그림 13과 그림 14는 옵셋 오차로 인해 왜곡된 전원 위상각으로 동기 좌표계 PI 전류제어를 수행할 경우의 상전류와 동기 좌표계 đ축 전류에 미치는 영향과 그에 따른 FFT 결과를 보여주고 있다. 그림 13에서 알 수 있듯이 옵셋 오차로 인해 계통측 상전류에는 직류 성분과 전원 주파수의 2배 맥동 그리고, 동기 좌표계 đ축 전류에는 전원 주파수의 1배 맥동이 존재하고 있으며 이는 식 (3)과 식 (4)의 결과와 동일함을 알 수 있다.

반면 그림 14는 제안한 옵셋 오차 보상 알고리즘

그림 11. 옵셋 오차 보상 전의 계통 위상각과 동기 좌표계 *do*축 전압파형

Fig. 11. Grid angle and synchronous *dq*-axis voltage waveforms before offset error compensation

Fig. 12. Grid angle and synchronous *dq*-axis voltage waveforms after offset error compensation

을 적용하였을 경우의 실험 파형으로 보상 전과 비교하여 상전류와 동기 좌표계 d축 전류에 포함된 직류 성분과 전원 주파수 1배 및 2배의 고조파 성분이크게 감소하였다. 보상 전 대비 상전류에 포함된 직

그림 13. 옵셋 오차 보상 전의 상전류와 동기 좌표계 d축 전류파형

Fig. 13. Phase current and synchronous d-axis current waveforms before offset error compensation

그림 14. 옵셋 오차 보상 후의 상전류와 동기 좌표계 d축 전류파형

Fig. 14. Phase current and synchronous d-axis current waveforms after offset error compensation

류 성분은 약 80%, 2배 맥동 성분은 약 70%, 동기 좌표계 *d*축 전류 1배 맥동성분은 약 94% 줄어듦을 알 수 있다.

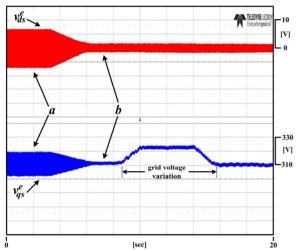

그림 15는 계통전압 변동에 따른 제안한 알고리즘의

동작 특성을 보여주고 있다. 구간 'a'인 경우 옵셋 오차 보상 전 동기 좌표계 dq축 전압에는 1배 맥동 성분을 포함하고 있으며, 보상 후 1배 맥동 성분이 감소하고 있음을 그림 15의 구간 'b'에서 알 수 있다. 옵셋 오차 보상 동작 중 약 4.5%의 계통전압 변동이 야기되었음 에도 맥동 크기의 변동없이 보상 알고리즘이 정상적 으로 동작함을 알 수 있다.

그림 15. 계통전압 변화에 따른 옵셋 오차 보상 후의 동기 좌표계 *dq*축 전압파형

Fig. 15. Synchronous *dq*-axis voltage waveforms after offset error compensation under grid voltage variation

### 3. 결 론

본 논문에서는 단상 계통연계형 인버터의 SRF-PLL 기법을 이용한 전원 위상각을 추종함에 있어 계통전압의 아날로그 신호처리과정에서 발생되는 옵셋 및 스케일 오차로 인한 왜곡된 전원 위상각이 동기 좌표계 dq축 전류와 상전류의 맥동에 미치는 영향을 분석하였다. 또한 이를 검출 및 보상하기 위한 새로운 옵셋 오차 검출 및 보상 알고리즘을 제안하였다. 제안한 알고리즘은 RMS기법을 통해서 옵셋 오차를 검출하고 검출된 옵셋 오차 성분은 PI제어기에 의해 옵셋 오차를 추종하여 직접 보상해 줌으로서 출력 상전류와 동기 좌표계 dq축 전류에 포함된 직류 성분과 전원 주파수 1배 및 2배 맥동

성분을 제거할 수 있다. 시뮬레이션 및 다양한 실험을 통하여 제안된 옵셋 오차 보상 알고리즘의 타당성을 검증하였다.

이 논문은 2013년도 정부(미래창조과학부)의 재원으로 한국연구재단의 지원을 받아 수행된 기초연구사업 (No.NRF-2013R1A1A1013670)의 연구결과임.

#### References

- [1] H. E. Park, E. S. Kim, and J. H. Song, "A SRF power flow control method for grid-connected single-phase inverter systems", JIEIE, vol. 24, no. 5, pp. 129-135, May 2010.

- (2) W. C. Lee, "Maximum power point tracking control for a grid-tie photovoltaic inverter", JIEIE, vol. 23, no. 5, pp. 72–79, May 2009.

- [3] S. M. Jung, Y. S. Bae, T. S. Yu, S. W. Choi, and H. S. Kim, "Single-phase utility-integrative for residential fuel cell generation system", KIPE, vol. 12, no. 1, pp. 81-88, Feb. 2007.

- [4] Y. Xue, L. Chang, S. B. Kjaer, J. Bordonau, and T. Shimizu, "Topologies of single-phase inverters for small distributed power generators: an overview," IEEE Trans. Power Electron., vol. 19, no. 5, pp. 1305-1314, Sept. 2004.

- (5) S. B. Kjaer, J. K. Pedersen, and F. Blaabjerg, "A review of single-phase grid-connected inverters for photovoltaic modules," IEEE Trans. Ind. Applicat., vol. 41, no. 5, pp. 1292 1306, Sept./Oct. 2005.

- [6] S. M. Silva, B. M. Lopes, B. J. C. Filho, R. P. Campana, and W. C. Bosventura, "Performance evaluation of PLL algorithms for single-phase grid-connected systems," in Proc. IAS, 2004, vol. 4, pp. 2259 2263.

- [7] P. Rodriguez, J. Pou, J. Bergas, J. I. Candela, R. P. Burgos, and D. Boroyevich, "Decoupled double synchronous reference frame PLL for power converters control," IEEE Trans. Power Electron., vol. 22, no. 2, pp. 584-592, March 2007.

- [8] M. Ciobotaru, R. Teodorescu, and F. Blaabjerg, "A new single-phase PLL structure based on second order generalized integrator," in Proc. PESC, 2006, pp.1-6.

- [9] S. J. Lee, J. K. Kim, and S. K. Sul, "A new phase detecting method for power conversion systems considering distorted conditions in power system," in Proc. IAS, 1999, vol. 4, pp. 2167 2172.

- (10) M. Ciobotaru, R. Teodorescu, and V. G. Agelidis, "Offset rejection for PLL based synchronization in grid-connected converters," in Proc. APEC, 2008, pp. 1611 1617.

- [11] M. Karimi-Chartemani, S. A. Khajehoddin, P. K. Jain, A. Bakhshai, and M. Mojiri, "Addressing DC component in PLL and notch filter algorithms," IEEE Trans. Power Electron., vol. 27, no. 1, pp. 78 86, Jan. 2012.

[12] S. H. Hwang, L. Liu, H. Li, J. M. Kim, "DC offset error compensation for synchronous reference frame PLL in single-phase grid-connected converters," IEE Trans. Power Electron., vol. 27, no. 8, pp. 3467–3471, April 2012.

# ◇ 저자소개 ◇-

## **황선환**(黃善煥)

1978년 7월 15일생. 2004년 부산대 전기 공학과 졸업. 2006년 동 대학원 전기 공학과 졸업(석사). 2011년 동 대학원 전기공학과 졸업(박사). 2011~2012년 플로리다 주립대 CAPS 박사후연구원. 2012년~현재 경남대 전기공학과 조교수.

#### 황영기(黃榮基)

1974년 부산대 화학공학과 졸업. 1979년 고려대 대학원 화학공학과 졸업(석사). 1986년 동 대학원 화학공학과 졸업(박사). 1988~1989년 영국 Univ. of Exeter Post Doc. 1996~1997년 미국 Univ. of Washington 교환교수. 현재 경남대 전기공학과 교수.

#### 권순걸(權純杰)

1951년 10월 19일생. 1973년 영남대 전기 공학과 졸업. 1980년 부산대 대학원 전기 공학과 졸업(석사). 1990년 영남대 대학원 전기공학과 졸업(박사). 현재 경남대 전기 공학과 교수.