# Optimization of Material and Process for Fine Pitch LVSoP Technology

Yong-Sung Eom, Ji-Hye Son, Hyun-Cheol Bae, Kwang-Seong Choi, and Heung-Soap Choi

For the formation of solder bumps with a fine pitch of 130 µm on a printed circuit board substrate, low-volume solder on pad (LVSoP) technology using a maskless method is developed for SAC305 solder with a high melting temperature of 220°C. The solder bump maker (SBM) paste and its process are quantitatively optimized to obtain a uniform solder bump height, which is almost equal to the height of the solder resist. For an understanding of chemorheological phenomena of SBM differential scanning calorimetry, measurement, and physical flowing of SBM paste are precisely characterized and observed during LVSoP processing. The average height of the solder bumps and their maximum and minimum values are 14.7 µm, 18.3 μm, and 12.0 μm, respectively. It is expected that maskless LVSoP technology can be effectively used for a fine-pitch interconnection of a Cu pillar in the semiconductor packaging field.

Keywords: Maskless bumping, Sn/3.0Ag/0.5Cu, fine pitch, solder powder, resin, PCB.

#### I. Introduction

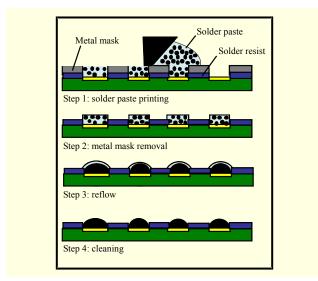

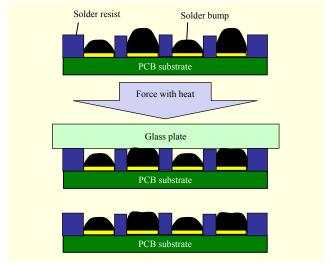

For highly integrated semiconductor packaging fields, such as mobile phone and high resolution display, the number of electrical interconnections has been rapidly increasing [1]. The pitch of the electrical interconnection of the solder bumps between a silicon device and a printed circuit board (PCB) substrate is becoming narrower and narrower. Several methods for performing solder bumps on a PCB with a fine pitch have been applied, including screen printing, solder jetting, electroplating, micro-ball placement, Super Juffit, and Super Solder. To obtain high-quality solder bump, an electroplating method using a lithography process is best, despite its high cost. As low-cost solder bumping technologies, the Super Juffit and Super Solder methods work well [2], [3]. However, they are still in the development stage. If the pitch of solder bump on a PCB is larger than 130 µm, the screen printing method is suitable because of its low processing cost, although its yield decreases along with the pitch of the solder bump. Figure 1 shows the conventional solder on pad (SoP) process used to form solder bumps on a PCB. As shown in Fig. 1, the first step of the conventional screen printing method to obtain a solder bump on a PCB is to print a normal solder paste composed of solder powder and flux on the metal pad of the PCB substrate using a metal mask. After the screen printing process, the metal mask is removed and a reflow process is conducted to achieve a solder bump with a hemispherical shape. The residue of flux covered on the solder bumps, shown in Step 3 of Fig. 1, should be removed by the solvent. It is generally known that if the pitch of a solder bump on a PCB is equal to or smaller than 130 µm, the yield from the screen printing process is very low because of the adhesion between a solder paste and the metal mask itself, shown in Steps 1 and 2 of Fig. 1 [4]. Therefore,

Manuscript received Nov. 26, 2012; revised Apr. 24, 2013; accepted May 10, 2013.

This work was supported in part by the KEIT, Components and Materials Technology Development Project of MKE/KEIT [10037039, Development of Advanced Ultra Thin MCP PCB Module & Embedded PCB SiP Module], the IT R&D program of MKE/KEIT (Grant No. 10041416, the core technology development of light and space adaptable new mode display for energy saving on 7 inch and 2 W), and the R&D program of ISTK [Development of an image-based, real-time inspection and isolation system for hyperfine faults].

$Yong-Sung Eom \ (phone: +82 \ 42 \ 860 \ 5547, \ yseom@etri.re.kr), \ Ji-Hye Son \ (jhson87@etri.re.kr), \ Hyun-Cheol Bae \ (hcbae@etri.re.kr), \ and \ Kwang-Seong Choi \ (kschoi@etri.re.kr) are with the Components & Materials Research Laboratory, ETRI, Daejeon, Rep. of Korea. \\$

Heung-Soap Choi (scheung@hongik.ac.kr) is with the Department of Mechanical & Design Engineering, Hongik University Sejong, Sejong, Rep. of Korea.

http://dx.doi.org/10.4218/etrij.13.1912.0007

Fig. 1. Conventional SoP process to form solder bump on PCB substrate.

fine-pitch solder bumps should be generated without the use of a metal mask or high-cost electroplating process.

In previous research, the low-volume SoP (LVSoP) process conducted on a silicon substrate was investigated regarding the chemorheological phenomena of solder bump maker (SBM) material as well as processing parameters, including temperature cycle and environment condition, from a qualitative viewpoint [5]-[8]. In [8], a low-volume solder bump with a fine pitch had an advantage for an electrical interconnection with a Cu pillar without any solder bridge occurring between neighboring bumps during the flip chip bonding process [9].

In the present research, LVSoP technology on a PCB substrate with a pitch of 130 µm is introduced from a quantitative perspective. The term "low volume" indicates that the height of the solder bump with a hemispherical shape on a PCB is equal to or lower than the thickness of the solder resist. For optimization of the LVSoP process, the following three kinds of processing parameters are selected: the diameter of solder powder of SBM mixed with resin matrix, the thickness of SBM material after the screen printing process, and the kind of deoxidizing agent to remove oxide from the solder powder. A mechanism to remove the oxide layer formed on the solder powder through the use of a deoxidizing agent was previously researched in detail [10]-[14].

# II. Materials and Experiment

# 1. Materials

SBM paste is produced by mixing a resin matrix with solder

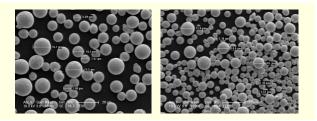

Fig. 2. SEM pictures of Sn/3.0Ag/0.5Cu solder powders: (a) type 6 and (b) type 7.

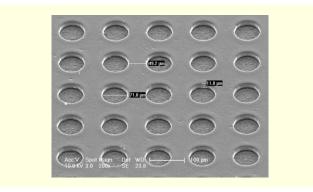

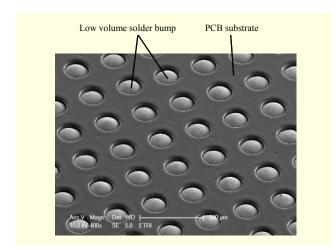

Fig. 3. SEM image of PCB substrate used.

powder without any solvent materials. Two different Sn/3.0Ag/0.5Cu solder powders are used, types 6 and 7. The average diameters of solder powder types 6 and 7 are 5 µm to 16 μm and 2 μm to 11 μm, respectively, as shown in Fig. 2. The resin matrix is composed of a base resin, a deoxidizing agent in a powder state, and some additives. Two different types of deoxidizing agents, A and B, based on a carboxylic material are used. All chemical components of SBM resin are mixed in silicon oil bath at 100°C for 10 minutes. For the SBM paste, the mixing ratio between solder and powder is 30:70 in volumetric percent, and the mixing process is conducted using a paste mixer with a revolution and rotation method at room temperature for one minute. The viscosity of the SBM with both types of solder powders is measured at 25°C at 10 rpm using a Brookfield machine. Figure 3 shows an SEM image of a PCB substrate with a square matrix structure of Cu pads. The total number of Cu pads covered by organic solderability preservatives is 625 (25×25). The pitch of each pad is 130 μm, and the diameter of each pad is 70 µm. The thickness of the solder resist performed on the metal pads in PCB is 15 µm, as shown in Fig. 3.

# 2. Experiment

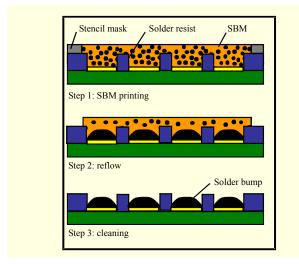

To characterize the chemical phenomena of SBM resin and SBM paste during the LVSoP processing, differential scanning calorimetry (DSC) thermograms are conducted at a heating rate of 10°C per minute in a nitrogen environment. Figure 4 shows a schematic of the LVSoP process with SBM using the screen printing method. In Step 1, SBM paste is printed onto the whole PCB substrate by controlling the paste thickness with a 200-mesh stencil mask 80 µm in thickness. The thickness of the printed SBM paste is controlled by stencil masks M1 and M2 with emulsion thicknesses of 15 µm and 40 µm, respectively. The total thickness of the stencil mask is determined through a summation of mesh and emulsion thicknesses. For the reflow process in Step 2 of Fig. 4, the temperature of PCB at which the SBM is printed is increased up to 240°C at a heating rate of 2°C per second, held for 10 seconds, and then cooled to room temperature at a cooling rate of 1°C per second. The oxygen content of 15,000 ppm as the environmental condition is maintained during the given

Fig. 4. Schematic of LVSoP process with SBM.

Fig. 5. Schematic of coining process with load of 2.5 g/bump and temperature of 200°C for 30 s.

reflow process. As shown in Step 3 of Fig. 4, after the reflow process, the residue resin and solder particles are cleaned off in the following processes: application of acetone for 30 seconds, methanol in an ultrasonic bath for 10 seconds, and compressed air blowing. The height of solder bumps (625) achieved through the LVSoP process is automatically measured through the principle of white light scanning interferometry (WSI). To obtain a uniform height of solder bumps, a coining process is conducted using a flip chip bonder. Figure 5 shows a schematic of the coining process. A glass plate is placed on the PCB substrate with low volume solder bumps. A force of 2.5 g per bump and a temperature of 200°C are applied for 30 seconds, as shown in Fig. 5.

# III. Results and Discussion

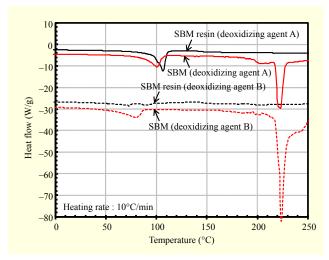

The measured viscosity of SBM paste used is about 30,000 cps at 25°C and 10 rpm for all of the experiments. For the characterization of SBM paste during the SoP processing, the dynamic DSC thermogram is conducted at a heating rate of 10°C per minute for the SBM paste and the SBM resin without solder powder, as shown in Fig. 6. To remove the oxide layer on the solder powder, two kinds of deoxidizing agents, A and B, are used to produce the SBM paste. For both the SBM resins and pastes, small endothermic peaks are observed at around 100°C and 80°C for deoxidizing agents A and B, respectively. On the other hand, the large endothermic peaks at around 220°C corresponding to the melting temperature of Sn/3.0Ag/0.5Cu solder are detected for SBM pastes with deoxidizing agents A and B. It is inferred that the small endothermic peaks around 100°C and 80°C are caused by the melting of deoxidizing agents A and B, respectively. It is believed that the deoxidizing agents are completely melted

Fig. 6. DSC thermograms of SBMs and SBM resins.

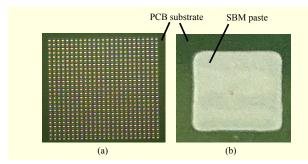

Fig. 7. Optical photographs of PCB substrates: (a) before and (b) after the printing process.

during the mixing time of the SBM resin at the given mixing temperature. However, a small amount of deoxidizing agents may be changed to precipitate a solid state from a liquid state during the cooling process. From Fig. 6, it is inferred that these precipitates are detected as small endothermic peaks around the melting temperatures of the deoxidizing agents. As explained previously in Step 3 of Fig. 4, the residue of SBM resin and solder powder should be clearly removed during the cleaning process. In the temperature range of 25°C to 240°C for LVSoP processing, no exothermic peaks indicating a chemical reaction are observed, as shown in Fig. 6. Therefore, it is believed that the residue of SBM resin remains in a liquid state after the reflow process illustrated in Step 2 of Fig. 4.

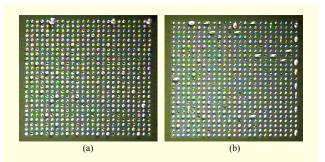

Figure 7 shows optical photographs of PCB substrates before and after the screen printing process. All areas of the Cu pads are completely covered by SBM paste using stencil mask A or B, as explained previously. After the screen printing process with SBM paste including solder type 7 and deoxidizing agent A, the thickness of the printed SBM with stencil mask A is about 35 µm and with stencil mask B is about 65 µm. For the reflow process depicted in Step 2 of Fig. 4, the temperature increases up to 240°C at a heating rate of 2°C per second and is maintained for 10 seconds under a 15,000-ppm oxygen environment. During this LVSoP processing time, it is clearly observed that the solder particles located in the upper side of SBM layer do not participate in building the solder bump through the coalescence and wetting of solder particles. Only the solder particles located in the lower side of SBM layer near the Cu pads, as shown in Step 2 of Fig. 4, are wetted on the Cu pads to form low-volume bumps. Therefore, it is identified that movement of solder particles does not occur because no solvent materials are used for SBM paste.

The optimization of the LVSoP processing parameters, such as the kind of deoxidizing agent, the diameter of the solder powder, and the printed thickness of the SBM paste according to the stencil mask, is conducted as shown in Table 1 and Figs. 8 through 11. To investigate the effects of deoxidizing agents, SBM paste made using solder powder type 6 is printed

Table 1. Optimization of processing parameters for Figs. 8 to 11.

| Figure | Stencil mask | Deoxidizing agent | Solder powder  |

|--------|--------------|-------------------|----------------|

| 8      | M2           | A, B              | Type 6         |

| 9      | M2           | A                 | Type 6, Type 7 |

| 10     | M1           | A                 | Type 6, Type 7 |

| 11     | M1, M2       | A                 | Type 7         |

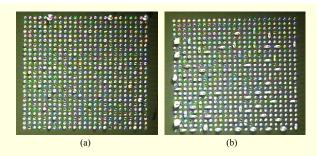

Fig. 8. Optical photographs of solder bumps on PCB after SoP processing with stencil mask M2 and solder powder type 6, with deoxidizing agents (a) A and (b) B.

Fig. 9. Optical photographs of solder bumps on PCB after SoP processing with stencil mask M2 and deoxidizing agent A, with solder powder types (a) 6 and (b) 7.

with stencil mask M2, as shown in Fig. 8. For a characterization of the deoxidizing effect according to the diameter of the solder powder, deoxidizing agent A and stencil mask M2 are used for the SBM printing process, related to Fig. 9. From Fig. 8, it is clearly understood that both deoxidizing agents can effectively remove the oxide from the solder powder. However, deoxidizing agent A shows relatively more stable LVSoP results than deoxidizing agent B. From Fig. 9, it is observed that the deviation of bump height with solder powder type 7 is lower than that with solder powder type 6. It is inferred that this lower deviation of bump height shown in Fig. 9(b) is caused by the more uniform diameter of solder powder type 7 compared to type 6.

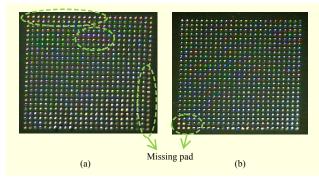

To get a lower deviation of bump height, stencil mask M1 with an emulsion thickness of 15 µm is used, as shown in

Fig. 10. Optical photographs of solder bumps on PCB after SoP processing with stencil mask M1 and deoxidizing agent A, with solder powder types (a) 6 and (b) 7.

Fig. 11. Optical photographs of solder bumps on PCB after SoP processing with deoxidizing agent A and solder powder type 7, with stencil masks (a) M1 and (b) M2.

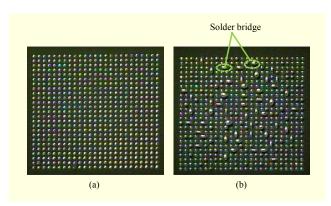

Fig. 12. SEM image after LVSoP processing.

Fig. 10. Notably, the phenomenon of a solder bridge forming between adjacent bumps is completely eliminated when using solder powder type 6 or type 7. However, many Cu pads are left without solder bumps when the LVSoP process is applied with solder powder type 6. To understand the mechanism of

Fig. 13. Measured height of solder bumps.

Fig. 14. SEM image after coining processing.

solder wetting coalescence according to the thickness of the printed SBM layer, SBM paste composed of solder type 7 and deoxidizing agent A is used, as reflected in Fig. 11. From the optical observation and measurement of solder bump height after LVSoP processing, it is clear that the best combination of LVSoP processing is deoxidizing agent A, solder powder type 7, and stencil mask M1, as shown in Fig. 11(a). To obtain a low-volume solder bump with the most uniform height equal to the thickness of the solder resist, all of the chemical components and processing parameters are precisely regulated.

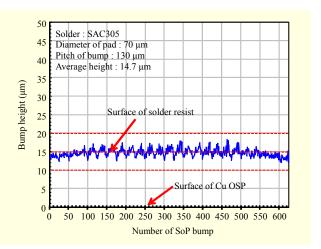

Figure 12 shows an SEM image of low-volume solder bump after LVSoP processing. As shown in Fig. 12, it is clear that the heights of the solder bumps are almost equal to the thickness of the solder resist, at 15  $\mu$ m. Using WSI technology, the heights of the solder bumps are automatically measured, as shown in Fig. 13. The bump height values of 0  $\mu$ m and 15  $\mu$ m on the y-axis indicate the surfaces of the Cu pad and the solder resist, respectively. The average, maximum, and minimum heights of the measured low-volume solder bumps are 14.7  $\mu$ m, 18.3  $\mu$ m,

and 12.0 µm, respectively.

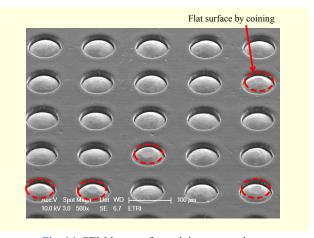

Figure 14 shows an SEM image of low-volume solder bump after the coining process. As shown in Fig. 14, there are several compressed marks with flat surfaces at the top of the solder bumps that are higher than the thickness of the solder resist. As mentioned in section I, we conclude that it is possible to use a low-volume solder bump with an average height of 15  $\mu$ m to join with the Cu pillar without electrical shortage owing to the solder bridge between adjacent solder bumps during the flip chip bonding process.

## IV. Conclusion

Low-volume solder on pad (LVSoP) technology with SAC305 solder for a 130-µm fine pitch on a PCB substrate was developed and quantitatively investigated using a maskless technology. From the LVSoP process with the use of a stencil mask to control the thickness of the SBM paste, low-volume solder bumps on all of the Cu pads were completely performed without any missing bumps. The measured average height of the low-volume solder bumps (25×25=625) was about 15 μm, which was almost equal to the height of the solder resist. A flip chip bonding process between the PCB substrate with lowvolume solder bumps and the silicon device having Cu pillars without solder caps will be investigated in the near future. As one of the key solutions for fine-pitch interconnection with a Cu pillar for a flip chip bonding process, it is believed that LVSoP technology can be effectively used in semiconductor packaging.

## Acknowledgement

The authors would like to thank Jeong-Hyun Noh for supporting the sample preparation and measurement.

# References

- [1] S.C. Johnson, "Flip-Chip Packaging Becomes Competitive," Semiconductor Int., May 2009.

- [2] C.P. Wang, *Materials for Advanced Packaging*, Springer Science Business Media LLC, 2009.

- [3] K. Hikasa and H. Irie, "Advanced Solder Bumping Technology Through Super Solder," *IEEE/CPMT Int Electron. Manufact. Technol. Symp.*, 1997, pp. 48-55.

- [4] M. Gerber et al., "Next Generation Fine Pitch Cu Pillar Technology – Enabling Next Generation Silicon Nodes," Proc. Electron. Compon. Technol. Conf., 2001, pp.612-618.

- [5] K.-S. Choi et al., "Novel Bumping Material for Solder-on-Pad Technology," *ETRI J.*, vol. 33, no. 4, Aug. 2011, pp. 637-640.

- [6] K.-S. Choi et al., "Novel Maskless Bumping for 3D Integration," ETRIJ., vol. 32, no. 2, Apr. 2010, pp. 342-344.

- [7] K.-J. Sung et al., "Novel Bumping and Underfill Technologies for 3D IC Integration," *ETRI J.*, vol. 34, no. 5, Oct. 2012, pp. 706-712.

- [8] K.-S. Choi et al., "Novel Bumping Process for Solder on Pad Technology," ETRIJ., vol. 35, no. 2, Apr. 2013, pp. 340-343.

- [9] R. Agarwal et al., "Cu/Sn Microbumps Interconnect for 3D TSV Chip Stacking" Proc. Electron. Compon. Technol. Conf., 2010, pp. 858-863.

- [10] Y.-S. Eom et al., "Characterization of Polymer Matrix and Low Melting Point Solder for Anisotropic Conductive Film," *Microelectron. Eng.*, vol. 85, no. 2, Feb. 2008, pp. 327-331.

- [11] Y.-S. Eom et al., "Electrical Interconnection with a Smart ACA Composed of Fluxing Polymer and Solder Powder," *ETRI J.*, vol. 32, no. 3, June 2010, pp. 414-420.

- [12] Y.-S. Eom et al., "Characterization of a Hybrid Cu Paste as an Isotropic Conductive Adhesive," *ETRI J.*, vol. 33, no. 6, Dec. 2011, pp. 864-870.

- [13] J.-W. Baek et al., "Chemo-Rheological Characteristic of a Self-Assembling Anisotropic Conductive Adhesive System Containing a Low-Melting Point Solder," *Microelectron. Eng.*, vol. 87, no. 18, Oct. 2010, pp. 1968-1972.

- [14] K.-S. Jang et al., "Catalytic Behavior of Sn/Bi Metal Powder in Anhydride-Based Epoxy Curing," *J. Nanosci. Nanotechnol.*, vol. 9, no. 12, 2009, pp. 7461-7466.

Yong-Sung Eom received his BS from the School of Aerospace and Mechanical Engineering at Korea Aerospace University and his MS from the Department of Aerospace Engineering at the Korea Advance Institute of Science and Technology (KAIST), Seoul, Rep. of Korea, in 1988 and 1991, respectively. He

worked at the Korea Institute of Aeronautical Technology (KIAT) at Korean Air Ltd. as a design and process engineer for the composite materials of the MD-11 Aircraft Spoiler from 1991 to 1995. In 1999, he received his PhD from the Department of Material Science Engineering at École Polytechnique Fédérale de Lausane (EPFL), Lausanne, Switzerland. After returning to Korea, he worked at Hynix Semiconductor Ltd. as a packaging engineer for memory devices from 2000 to 2001. Since 2001, he has been with ETRI, Daejeon, Rep. of Korea, where he has been working as a packaging engineer. His research activities include the development of the interconnection materials based on the polymer for an electronic packaging and process design for 3D-IC and MEMS packaging.

**Ji-Hye Son** received her BS and MS from the Department of Advanced Organic Materials and Textile System Engineering at Chungnam National University, Daejeon, Rep. of Korea, in 2010 and 2012, respectively. Since 2012, she has been working for ETRI, Daejeon, Rep. of Korea. She has researched the design and

synthesis of organic polymers and the characterization of advanced polymers.

**Hyun-Cheol Bae** received his BS and MS in electrical engineering from Dongguk University, Seoul, Rep. of Korea, in 1999 and 2001, respectively. He joined the SiGe research team of ETRI, Daejeon, Rep. of Korea, in 2001 and worked as a design and process engineer for MMIC and passive devices. He moved to the

packaging research group of ETRI in 2007 and has been working as a packaging engineer. In 2009, he received his PhD in electrical engineering from Chungnam National University, Daejeon, Rep. of Korea. His research interests include the design and fabrication of integrated passive devices, 3D stacked chip packaging using TSV, and wafer-level packaging for MEMS devices.

**Kwang-Seong Choi** received his BS from Hanyang University, Rep. of Korea, and MS and PhD from the Korea Advanced Institute of Science and Technology (KAIST). From 1995 to 2001, he developed chip scale packages and PoP packages and designed high-speed electronic packages for DDR, Rambus, and RF devices for

Hynix Semiconductor. He has been developing high-speed packaging technologies for optical devices, such as modulators and receivers, since 2001 at ETRI, Daejeon, Rep. of Korea. Currently, his research areas include the development of the materials and processes for 3D ICs with through silicon via (TSV), next-generation displays, and silicon photonics.

Heung-Soap Choi received his BS in 1985 from the Department of Mechanical Engineering at Yonsei University (YSU) and his MS in 1987 from the Graduate School of YSU. He received his PhD in 1993 from the Center for Quality Engineering and Failure Prevention, CQEFP, in the Department of Mechanical

Engineering, McCormick School of Engineering at Northwestern University, USA. He studied thermo-mechanical behaviors of composite materials with interfacial defects between matrix and fiber materials and/or matrix cracking at the interface. In 1994, he started his first job at the Korea Institute of Aerospace Technology, Korean Air, Rep. of Korea, as a composite group member in KIAT. He participated in the G7-project to develop a composite control surface for small aircraft. Also, in cooperative program with United Technologies Co. in 1995, he and his colleagues studied cure and health monitoring techniques using FBG optical fiber sensors and applied the techniques to cure monitoring of the composite cure process. In 2000, he started the R&D activities and projects by KARI, Korea Aerospace Research Institute, on space structures, such as composite antennas and solar panel substrates. He also made significant contributions as a coordinator in the co-research projects (funded by Airbus) for the development of surface treatment techniques for GLARE repair of A380 aircraft. Until June 2012, he was involved in writing several proposals for developing new military aero-vehicle projects, such as MUAV, KLH, KFX, Korean Civil Aircraft, and so on, especially in composite R&D fields. Nowadays, he is working as an associate professor in the Department of Mechanical and Design Engineering at Hongik University, Rep. of Korea, and continues his composite research activities there.