# 오류 마루 현상이 완화된 비이진 LDPC 부호의 설계 및 성능 분석 연구

안 석 기<sup>\*</sup>, 임 승 찬<sup>\*</sup>, 양 영 오<sup>\*\*</sup>, 양 경 철<sup>\*</sup>

# Design and Performance Analysis of Nonbinary LDPC Codes With Low Error-Floors

Seok-Ki Ahn, Seung-Chan Lim, Youngoh Yang, Kyeongcheol Yang

요 약

본 논문은 오류 마루 영역에서 우수한 성능을 가지는 비이진 LDPC (low-density parity-check) 부호의 설계 방 법을 제안하고 성능을 검증한다. 제안된 설계 방법은 비이진 LDPC 부호의 이진 최소 거리(binary minimum distance)를 최대화하도록 패리티 검사 행렬의 비이진 원소 값들을 결정한다. BPSK (binary phase-shift keying) 변조 방식 하에서 제안된 방법으로 설계된 비이진 LDPC 부호가 오류 마루(error floor) 영역에서 우수한 성능을 가지는 것을 Monte Carlo 시뮬레이션과 중요도 표본 추출(importance sampling) 기법을 사용하여 검증한다.

**Key Words**: BPSK, cycle, error floor, importance sampling, nonbinary LDPC codes

### **ABSTRACT**

In this paper we propose a design algorithm for nonbinary LDPC (low-density parity-check) codes with low error-floors. The proposed algorithm determines the nonbinary values of the nonzero entries in the parity-check matrix in order to maximize the binary minimum distance of the designed nonbinary LDPC codes. We verify the performance of the designed nonbinary LDPC codes in the error-floor region by Monte Carlo simulation and importance sampling over BPSK (binary phase-shift keying) modulation.

# I. 서 론

1962년 Gallager에 의해 처음 소개된 LDPC (low-density parity-check) 부호는 메시지 전달 (message passing) 알고리즘을 이용한 반복 복호 (iterative decoding)를 통해 Shannon 한계(Shannon limit)에 근접한 성능을 얻을 수 있다<sup>[1,2]</sup>. 비이진 (nonbianry) 유한체(finite field) GF(q), q > 2 상에 서 정의된 비이진 LDPC 부호는 비교적 길지 않은 길이에서 q가 커질수록 우수한 성능을 가진다는 것 이 알려져 있다<sup>[3]</sup>. 이러한 장점때문에 비이진 LDPC 부호는 이진 LDPC 부호에 비해서 비교적 높은 복 호 복잡도를 가짐에도 불구하고 차세대 채널 부호 로서 큰 주목을 받고 있다.

비이진 LDPC 부호의 성능을 최적화하기 위해서는 패리티 검사 행렬을 신중히 설계해야 한다. 비이진 LDPC 부호의 패리티 검사 행렬은 0과 1뿐만 아니라 GF(q)상의 원소를 모두 포함할 수 있으므로 패리티

<sup>※</sup> 이 논문은 2013년도 정부(미래창조과학부)의 재원으로 한국연구재단의 지원을 받아 수행된 연구임(No. 2011-0017396).

<sup>◆</sup> First Author : 포항공과대학교 전자전기공학과 통신 및 신호설계 연구실, askstone@postech.ac.kr, 준회원 ° Corresponding Author : 포항공과대학교 전자전기공학과 통신 및 신호설계 연구실, kcyang@postech.ac.kr, 종신회원

포항공과대학, \*\* 제주대학교

논문번호: KICS2013-08-371, 접수일자: 2013년 8월 29일, 최종논문접수일자: 2013년 10월 7일

검사 행렬을 설계할 때에는 비이진 원소들의 위치뿐만 아니라 비이진 원소들의 값 또한 신중히 결정해야한다. Poulliat 등은 변수 노드(variable node)의 차수 (degree)가 2로 균일한 비이진 LDPC 부호의 최소 무게(minimum weight)를 최대화하는 설계 방법을 제안하였다<sup>(4)</sup>.

본 논문에서는 Poulliat 등이 제안한 기존의 설계 방법에 기반하여 BPSK (binary phase-shift keying) 변조 방식 하에서 오류 마루(error floor) 현상이 완화 된 비이진 LDPC 부호를 설계하는 방법을 제안한다. 기존의 설계 방법은 비이진 LDPC 부호의 최소 무게 를 최대화하는 반면에 제안된 방법은 부호어를 이진 비트들로 변환했을 때의 이진 최소 무게(binary minimum weight)를 최대화한다.

BPSK 변조 방식 하에서 제안된 방법으로 설계된 비이진 LDPC 부호가 오류 마루 영역에서 기존의 방법으로 설계된 비이진 LDPC 부호보다 우수한 성능을 가지는 것을 전산 실험을 통해서 검증한다. 이를 위해서 Monte Carlo 시뮬레이션뿐만 아니라 낮은 프레임오율(frame error rate, FER) 영역에서 효율적으로 성능을 예측하는 중요도 표본 추출(importance sampling) 기법을 사용한다.

본 논문의 구성은 다음과 같다. 2절에 기존의비이진 LDPC 부호 설계 방법을 설명한다. 3절에서는 기존의 설계 방법을 기반으로 BPSK 변조 방식 하에서 우수한 성능을 가지는 제안된설계 방법을 설명한다. 4절에서는 Monte Carlo 시뮬레이션과 중요도 표본 추출 기법을 사용하여 제안된 설계 방법의 성능을 검증한다. 5절에서는 본 논문의 내용을 요약, 정리한다.

#### Ⅱ. 기존의 설계 방법

Poulliat 등은 패리티 검사 행렬 내의 비이진 원소들의 위치가 결정된 후에 비이진 원소들의 값을 최적화하는 알고리즘을 제안하였다 $^{[4]}$ . 제안된 방법은 패리티 검사 행렬의 행 단위로 비이진 원소 값들을 결정한다. 이를 위해서 행 무게(row weight)가  $d_c$  라면  $d_c$ 개의 비이진 원소들의 조합을 이진 이미지(binary image) 관점에서 최적화하였다. 이 때  $d_c$ 개의 비이진 원소들의 최적 조합 개수가 W라면 각 조합들의 순열(permutation)을 고려하여  $(d_c!)$  W개의 가능한 조합들 중에서 행 단위로 비이진 원소들을 할당하였다.

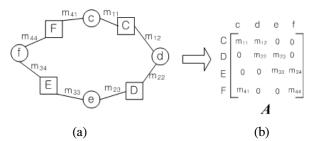

그림 1(a)는 변수 노드의 차수가 2로 균일한 비이진 LDPC 부호에 존재하는 길이가 8인 사이클에 포함된 변수 노드들의 부분 그래프(subgraph)를 나타낸다. 그림에서 ○와 □는 각각 변수 노드와 검사 노드(check node)를 나타내며, 그림 1(b)는 사이클에 포함된 변수노드와 검사 노드에 대응되는 부분행렬(submatrix)을 나타낸다. 이 때 패리티 검사 행렬의 비이진 원소 값들에 따라서 부분행렬 4의 랭크(rank)가 결정되며, 랭크가 변수 노드의 개수보다 작은 경우에는 변수 노드의 개수를 무게로 가지는 부호어가 생성된다<sup>14</sup>.

그림 1. 길이가 8인 사이클에 대응되는 부분행렬 Fig. 1. Submatrix corresponding to a length-8 cycle

비이진 LDPC 부호에 존재하는 무게가 작은 부호 어들은 짧은 사이클에 대응되는 부분행렬의 랭크 검사를 통해서 찾을 수 있다. 이처럼 랭크 검사를 통해 부호어의 존재 여부를 판단하는 것을 full rank condition (FRC) 라고 한다 $^{41}$ . Poulliat 등은 행 무게가  $d_c$ 인 경우에  $(d_c!)$  W개의 비이진 원소 조합들 중에서 행에 대응되는 검사 노드가 포함된 사이클들로부터 생성되는 부호어들의 최소 무게를 최대화하도록행 단위로 비이진 원소들을 할당하였다. 기존의 설계방법을 정리하면 다음과 같다:

**단계 1**: (초기화 단계) 패리티 검사 행렬의 비이 진 원소들의 위치를 결정한다. 이 때 부호의 거스를 g라고 한다. 이진 이미지 관점에서 패리티 검사 행렬의 행 무게에 최적화된 비이진 원소 조합들의 집합인 Z를 구성한다.

**단계 2**: (반복 최적화 단계,  $l \ge g$ ) 랜덤하게 선택된 행에 대응되는 검사 노드가 포함된 길이가 l인 사이클들 중에서 FRC를 만족하는 사이클의 개수가 최대가 되도록 원소 조합을 집합 Z로부터 선택한다. 만약 길이가 l인 모든 사이클이 FRC를 만족하면 l = l + 2로 증가시킨다.

단계 3: (종료 단계) FRC를 만족시키는 사이클

의 개수를 증가시키지 못하면 설계를 종료한다.

### Ⅲ. 제안된 설계 방법

본 논문은 BPSK 변조 방식 하에서 오류 마루 현상이 완화된 비이진 LDPC 부호의 설계 방법을 제안한다. BPSK 변조 방식 하에서 최대 우도 복호 (maximum likelihood decoding)를 사용하여 비이진 LDPC 부호를 복호하는 경우를 고려하자. 영 부호 어(all-zero codeword)가 전송된 경우에 이진 무게 (binary weight)가 d인 부호어로 잘못 복호될 PEP (pairwise error probability)는  $Q(\sqrt{2dE_b/N_0})$ 로 계

산된다. 여기서  $Q(x)=\int_x^\infty \frac{1}{\sqrt{2\pi}}e^{-\frac{z^2}{2}}dz$ ,  $E_b$ 는 정보 비트당 에너지, 그리고  $N_0$ 는 AWGN (additive white Gaussian noise)의 양측 전력 분포 (double-sided power spectral density)를 나타낸다. 그러므로 비이진 심볼을 구성하는 비트들의 이진 무게가 작은 부호어일수록 복호 오류를 유발할 확률이 커진다. 합-곱 복호(sum-product decoding)를 사용하는 경우에도 이러한 특성이 나타나는 것을 전산 실험을 통해 확인하였다. 특히 이와 같은 복호 오류는 오류 마루 영역에서 두드러지게 나타난다. 결과적으로 비이진 부호어의 무게가 동일하더라도 비이진 심볼을 구성하는 비트들의 이진 무게(binary weight)가 작아지면 오류 마루 현상에 미치는 영향이 크게 나타난다.

그림 1(b)의 부분행렬 A가 최대 랭크(full rank)를 가지지 못하는 경우에는 다음 식을 만족하는 영이 아닌 벡터 v가 존재한다:

$$A\underline{v} = \underline{0} \tag{1}$$

하나의 사이클에 대해서 식 (1)을 만족하는 벡터  $\underline{v}$ 가 존재하는 경우에는 다음과 같이 서로 다른 q-1개의 벡터가 식 (1)을 만족하게 된다:

$$\alpha^i \underline{v}, \quad i=1,2,...,q-1.$$

여기서  $\alpha$ 는 GF(q)의 원시 원소(primitive element)를 의미한다. 이 때 벡터  $\underline{v}$ 를 구성하는 비 이진 값들을 사이클에 포함된 변수 노드들에 할당하고, 나머지 변수 노드들에는 0을 할당하여 구성한 벡터  $\underline{c}$ 는 비이진 LDPC 부호의 부호어가 된다. 그 결과 다음의 q-1개의 부호어가 생성된다:

$$\alpha^i c, i = 1, 2, ..., q - 1.$$

생성된 q-1개의 부호어는 모두 사이클에 포함 된변수 노드의 개수를 무게로 가진다. 하지만 부호 어를 구성하는 비이진 심볼에 따라서 부호어의 이 진 무게는 달라지게 된다. 그러므로 BPSK 변조 방 식에서 우수한 성능을 가지기 위해서는 길이가 짧 은 사이클들로부터 발생되는 부호어들의 이진 무게 를 최대화하는 것이 중요하다. 이러한 내용을 기반 으로 다음과 같은 설계 방법을 제안한다:

**단계 1**: (초기화 단계) 패리티 검사 행렬의 비이 진 원소들의 위치를 결정한다. 이 때 부호의 거스를 g라고 한다. 이진 이미지 관점에서 패리티 검사 행렬의 행 무게에 최적화된 비이진 원소 조합들의 집합인 Z를 구성한다.

단계 2: (반복 최적화 단계) 랜덤하게 선택된 행에 대응되는 검사 노드가 포함된 길이가 g, g+2, 또는 g+4인 사이클들을 모두 찾는다. 집합 Z 내에서 임의의 원소 조합을 선택하여 행에 할당하였을 때, 사이클들로부터 생성되는 부호어들의 최소 이진 무게를 확인한다. 생성된 부호어들의 최소 이진 무게를 최대화하는 원소 조합을 Z로부터 선택한다. 이 때 같은 최소 이진 무게를 가지는 원소 조합들이 있다면 최소 이진 무게를 가지는 부호어의 개수가 최소인 원소 조합을 선택한다.

단계 3: (종료 단계) 단계 2를 반복적으로 수행하여도 더 이상 최소 이진 무게를 증가시키거나 최소 이진 무게를 가지는 부호어의 개수를 감소시키지 못하면 설계를 종료한다.

# Ⅳ. 전산 실험 결과

기존 방법과 제안된 방법을 사용하여 길이가 96이고, 부호율이 2/3인 변수 노드의 차수가 2로 균일한 비이진 LDPC 부호를 유한체 GF(8)상에서 설계하였다. 이를 위해  $32 \times 96$  패리티 검사 행렬 내의 비이진 원소들의 위치는 PEG (progressive edge-growth) 알고리즘<sup>[5]</sup>으로 결정하였으며, 설계된 패리티 검사 행렬의 사이클 정보는 표 1과 같다. 설계된 패리티 검사 행렬의 거스는 8이며, 길이가 14인 사이클까지 조사하였다.

표 1. 설계된 패리티 검사 행렬의 사이클 정보 Table 1. Numbers of cycles in the designed parity-check matrix

| Length | 8  | 10  | 12   | 14   |

|--------|----|-----|------|------|

| Number | 90 | 382 | 1415 | 5391 |

전산 실험에서 고려하는 설계 방법들은 다음과 같다:

- 랜덤 설계 방법 (Random) : 비이진 원소들을 GF(q)\0 상에서 랜덤하게 선택한다.

- 2) 기존 설계 방법 (Conventional) : 비이진 원소 들을 기존 설계 방법으로 선택하여 비이진 LDPC 부호의 최소 무게를 최대화한다.

- 3) 제안된 설계 방법 (Proposed) : 비이진 원소들을 제안된 설계 방법으로 선택하여 비이진 LDPC 부호의 이진 최소 무게를 최대화한다.

표 2는 세가지 방법으로 설계된 비이진 LDPC 부호에서 FRC를 만족하지 못하는 사이클의 개수를 나타낸 것이다.

표 2. FRC를 만족하지 못하는 사이클의 개수 Table 2. Numbers of cycles not satisfying the FRC

| Cycle length | 8 | 10 | 12  | 14  |  |

|--------------|---|----|-----|-----|--|

| Random       | 8 | 59 | 212 | 823 |  |

| Conventional | 0 | 9  | 222 | 870 |  |

| Proposed     | 0 | 15 | 232 | 843 |  |

표 2로부터 제안된 방법으로 설계된 비이진 LDPC 부호에는 무게가 5인 부호어가 105개 존재하며, 기존의 방법으로 설계된 비이진 LDPC 부호에는 무게가 5인 부호어가 63개 존재하는 것을 알수 있다.

표 3은 세가지 방법으로 설계된 비이진 LDPC 부호에 존재하는 작은 이진 무게를 가지는 부호어의 개수를 나타낸다. 표 3으로부터 이진 무게 관점에서는 제안된 설계 방법이 기존의 설계 방법보다유리함을 알 수 있다.

표 3. 비이진 LDPC 부호에 존재하는 작은 이진 거리를 가지는 부호어의 개수

Table 3. Numbers of codewords of small minimum distance in the designed nonbinary LDPC codes

| ·               |   |    |    |     |     |  |  |  |

|-----------------|---|----|----|-----|-----|--|--|--|

| Binary distance | 4 | 5  | 6  | 7   | 8   |  |  |  |

| Random          | 2 | 16 | 54 | 161 | 394 |  |  |  |

| Conventional    | 0 | 0  | 3  | 47  | 194 |  |  |  |

| Proposed        | 0 | 0  | 0  | 17  | 247 |  |  |  |

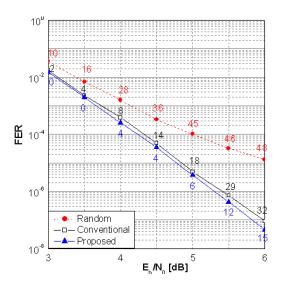

이러한 특징이 비이진 LDPC 부호의 FER 성능에 미치는 영향을 알아보기 위해서 BPSK 변조 방식 하에서 세 개의 비이진 LDPC 부호의 FER을 그림 2에 나타내었다. 그림 2에서 성능 곡선 위의 숫자들은 각각의 SNR 마다 관측된 50개의 복호 오류들 중에서 이진 거리가 7 이하인 부호어에 의해 발생한 복호 오류들의 개수를 나타낸다. 제안된 방법으로 설계된 비이진 LDPC 부호는 이진 무게가작은 부호어들을 가능한 최소로 가지기 때문에 BPSK 변조 방식 하에서 가장 우수한 성능을 가지는 것을 알 수 있다<sup>6</sup>.

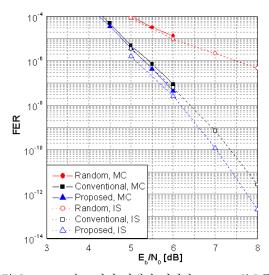

매우 낮은 FER 영역에서 설계된 부호들의 성능을 검증하기 위해서 Monte Carlo 시뮬레이션뿐만아니라 중요도 표본 추출(importance sampling, IS)<sup>[7,8]</sup> 기법을 사용하여 성능을 확인하여 그림 3에나타내었다. IS 기법을 적용할 때에는 표 3에나타난 작은 이진 무게를 가지는 부호어들을 주요 오류패턴으로 간주하였다. 그림 3으로부터 IS 기법으로예측된 FER 성능이 Monte Carlo 시뮬레이션으로얻은 FER 성능과 거의 일치함을 알 수 있다. 제안된 방법으로 설계된 비이진 LDPC 부호보다 FER 곡선의 기울기가 급하므로 SNR이 증가됨에 따라서 성능 이득은 더욱 커질 것으로 예상할수 있다.

그림 2. BPSK 변조 방식 하에서 비이진 LDPC 부호들의 FER 성능 (Monte Carlo 시뮬레이션)

Fig. 2. FER performances of the designed nonbinary LDPC codes over BPSK modulation (Monte Carlo simulation)

그림 3. BPSK 변조 방식 하에서 비이진 LDPC 부호들의 FER 성능 (IS 기법, 오류 마루 영역) Fig. 3. FER performances of the designed nonbinary LDPC codes over BPSK modulation (IS, error-floor region)

# V. 결 론

본 논문에서는 BPSK 변조 방식 하에서 우수한 성능을 가지는 비이진 LDPC 부호를 설계하는 방법을 제안하고 성능을 검증하였다. 제안된 방법은 비이진 LDPC 부호의 최소 무게를 최대화하는 기존 방법과는 달리 이진 최소 무게를 최대화 함으로써 오류 마루 영역에서 우수한 성능을 가진다. 제안된 방법은 변조 방식의 신호 성좌(signal constellation) 크기보다 비이진 LDPC 부호가 정의된 비이진 유한체 GF(q)의 크기가 큰 경우에 활용될 수 있다. 그러므로 제안된 방법은 고차 변조 방식을 사용하는 경우에도 활용될 수 있으며, 이에 대한 향후의 추가 연구가 필요하다.

### References

- [1] R. G. Gallager, *Low-Density Parity-Check Codes*. MIT Press, 1963.

- [2] S. Y. Chung, G. D. Forney, T. J. Richardson, and R. L. Urbanke, "On the design of low-density parity-check codes within 0.0045 dB of the Shannon limit," *IEEE Commun. Lett.*, vol. 5, no. 2, pp. 58-60, Feb. 2001.

- [3] M. C. Davey and D. MacKay, "Low-density parity-check codes over GF(q)," *IEEE Commum. Lett.*, vol. 2, no. 6, pp. 165-167,

- June 1998.

- [4] C. Poulliat, M. Fossorier, and D. Declercq, "Design of Regular (2, dc)-LDPC codes over GF(q) using their binary images," *IEEE Trans. Commun.*, vol. 56, no. 10, pp. 1626-1635, Oct. 2008.

- [5] X. Y. Hu, E. Eleftheriou, and D. M. Arnold, "Regular and irregular progressive edge-growth Tanner graphs," *IEEE Trans. Inform. Theory*, vol. 51, no. 1, pp. 386-398, Jan. 2005.

- [6] S.-K. Ahn and K. Yang, "Design of LDPC codes with low error-floors based on the progressive edge-growth (PEG) algorithm," in *Proc. 2012 Korean Inst. Commun. Inform. Sci.* (KICS) Summer Conf., Session 11A-22, pp. 443-444, Jeju Island, Korea, May 2012.

- [7] X. Zheng, F. C. M. Lau, C. K. Tse, Y. He, and M. Z. Wang, "A evaluation of the extremely low block error rate of irregular LDPC codes," in *Proc. Int. Conf. Commun.*, pp. 1-5, Dresden, Germany, 2009.

- [8] S.-K. Ahn, K. Yang, and D. Har, "Evaluation of the low error-rate performance of LDPC codes over Rayleigh fading channels using importance sampling," *IEEE Trans. Commun.*, vol. 61, no. 6, pp. 2166-2177, June 2013.

### 안 석 기 (Seok-Ki Ahn)

2006년 2월 포항공과대학교 전자전기공학과 학사 2008년 2월 포항공과대학교 전자전기공학과 석사 2013년 8월 포항공과대학교 전자전기공학과 박사 2013년 9월∼현재 삼성전자

DMC 연구소 책임연구원 <관심분야> 디지털 통신, 부호이론, 광대역 통신시 스템

# 임 승 찬 (Seung-Chan Lim)

2011년 2월 홍익대학교 전자 전기공학과 학사 2013년 2월 포항공과대학교 전자전기공학과 석사 2013년 3월~현재 포항공과대 학교 전자전기공학과 박사 과정

<관심분야> 디지털 통신, 부호이론

# 양영오 (Youngoh Yang)

1985년~현재 제주대학교 자연과학대학 수학과 교수

1981년~1985년 해군사관학교수학과 교수

2003년 3월~2005년 2월 제주대학교 자연과학대학 학장

2005년 5월~2007년 4월 제주

대학교 산학협력단장 2010년 8월~2013년 6월 제주발전연구원장 <관심분야> 해석학, 정보이론

### 양 경 철 (Kyeongcheol Yang)

1986년 2월 서울대학교 전자공학과 학사1988년 2월 서울대학교 전자공

1988년 2월 서울대학교 전자공 학과 석사

1992년 12월 University of Southern California 전기 공학과 박사

1993년 3월~1999년 2월 한양대학교 전자통신공학 과 조교수

1999년 2월~현재 포항공과대학교 전자전기공학과 교수

<관심분야> 디지털 통신, 부호이론, 다중 안테나 시 스템, 신호설계, 정보보호