논문 2013-50-8-19

# 입력전압을 감지하지 않는 전류연속/임계동작모드 Active Power Factor Correction Circuit

(A Continuous Conduction mode/Critical Conduction Mode Active Power Factor Correction Circuit with Input Voltage Sensor-less Control)

노 용 성\*, 유 창 식\*\*

(Yong-seong Roh and Changsik Yoo<sup>©</sup>)

요 약

본 논문에서는 입력전압을 감지하지 않는 전류연속/임계동작모드 active power factor correction(PFC) circuit을 제안하였다. 기존의 입력전압을 감지하지 않는 PFC circuit의 경우 출력전류가 낮은 경 부하 조건에서 DCM 동작을 수행하고, 이에 따라 PF가 감소하는 문제가 발생한다. 제안한 PFC circuit은 70KHz의 주파수로 CCM 동작을 수행하고, 경 부하 조건에서 최대 200KHz까지 스위칭 주파수가 가변되는 CRM 동작을 수행하도록 하였다. 이를 통해 경 부하 조건에서 PF가 감소하는 문제를 해결하였다. PFC controller IC는 0.35µm BCDMOS 공정을 이용하여 제작하였으며, 240W급 PFC prototype을 제작하여 실험하였다. 제안한 PFC circuit은 기존의 PFC circuit 대비 최대 10%의 역률이 향상되었고, IEC 61000-3-2 Class D 규격에 따른 경 부하 조건에서는 최대 4% 역률이 향상되었다.

# Abstract

An active power factor correction (PFC) circuit is presented which employs a newly proposed input voltage sensor-less control technique operated in continuous conduction mode (CCM) and critical conduction mode (CRM). The conventional PFC circuit with input voltage sensor-less control technique degrades the power factor (PF) under the light load condition due to DCM operation. In the proposed PFC circuit, the switching frequency is basically 70KHz in CCM operation. In light load condition, however, the PFC circuit operates in CRM and the switching frequency is increased up to 200KHz. So CCM/CRM operation of the PFC circuit alleviates the decreasing of the PF in light load condition. The proposed PFC controller IC has been implemented in a 0.35µm BCDMOS process and a 240W PFC prototype is built. Experimental results shows the PF of the proposed PFC circuit is improved up to 10% from the one employing the conventional CCM/DCM dual mode control technique. Also, the PF is improved up to 4% in the light load condition of the IEC 61000-3-2 Class D specifications.

**Keywords:** Power factor correction, continuous conduction mode, critical conduction mode, input voltage sensor-less control, zero current detection

(Department of Electronics and Computer Engineering, Hanyang University)

접수일자: 2013년6월18일, 수정완료일: 2013년7월22일

### I. 서 론

Power Factor (PF)는 피상전력에 대한 유효전력의 비로 정의되며, AC 입력전류와 입력전압의 위상차가 작고 정현파에 가까울수록 PF는 1에 가까운 값이 된다. PF가 낮은 경우 전력 손실이 증가하게 되며, 전원선에

<sup>&#</sup>x27;학생회원, \*\* 평생회원, 한양대학교 전자컴퓨터통신공 학과

<sup>©</sup> Corresponding Author(E-mail: csyoo@hanyang.ac.kr)

<sup>※</sup> 이 논문은 2013년도 정부(미래창조과학부)의 재원으로 한국연구재단의 지원을 받아 수행된 연구임

(No.2013R1A2A2A01004958)

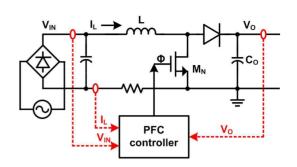

과도한 harmonics를 유발하여 전원선에 연결된 다른 전자기기에 영향을 미치게 된다. PF를 향상시키기 위해 입력전류가 입력전압과 동상이 되도록 하는 power factor correction (PFC) circuit을 사용하며 PFC circuit은 스위칭 소자의 유무에 따라 active 방식과 passive 방식으로 나뉜다. 이때 90% 이상의 높은 PF를 얻을 수 있고, 작은 크기로 제작 가능한 active 방식의 PFC circuit이 주로 사용되며, 그 구조는 boost converter에 기초한다. 이러한 active PFC circuit을 그림 1.에 나타내었다.

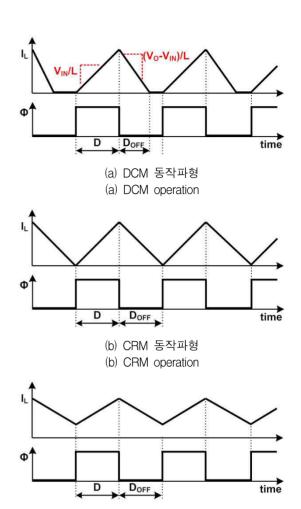

Active 방식의 PFC circuit은 그림 2. 와 같이 인덕터 에 흐르는 전류의 파형에 따라 discontinuous conduction mode (DCM), condinuous conduction mode (CCM), critical conduction mode (CRM)으로 구분한다<sup>[1]</sup>. DCM, CRM으로 동작하는 PFC circuit의 경우 다음 스 위칭이 발생하는 순간에 인덕터 전류가 영에서 시작하 므로 freewheeling diode의 소프트 스위칭 동작에 따라 높은 효율을 얻을 수 있다. 또한 NMOS 스위치  $M_N$ 의 ON이 되는 시간이 일정한 경우 자연적으로 평균 입력 전류와 입력전압이 동상이 되어 PFC 동작을 수행하게 되므로, 제어기의 설계가 용이하다<sup>[2]</sup>. 하지만 입력전류 의 리플은 평균 입력전류의 두 배 이상이 되므로. 출력 으로 공급하는 전류가 증가하는 경우 입력에서의 전류 리플이 매우 커진다. 따라서 PFC circuit의 입력단에 사 용하는 electro-magnetic interference (EMI) filter는 고 성능을 필요로 한다. 상기 문제를 개선하기 위해 출력 으로 공급하는 전류가 큰 경우 CCM으로 동작하는 PFC circuit이 주로 사용된다<sup>[3]</sup>. CCM 방식의 경우 입 력전류의 리플이 작아 스위칭 소자가 받는 전류 stress 가 감소하고, 입력단에 사용하는 EMI filter의 요구 성 능이 완화된다. 하지만 DCM/CRM 방식과 달리 제어기 의 설계가 복잡하다. CCM 방식으로 PFC 동작을 수행 하기 위해서는 출력전압의 레귤레이션을 위한 전압루프 와 입력전압과 전류를 동상으로 만들기 위한 전류루프 가 동시에 필요하다. 또한 그림 1.에서의 출력전압  $V_O$ 과 입력전압  $V_{IN}$  및 입력전류  $I_L$ 를 감지하기 위한 세 개의 센서가 필요하다[4~5]. 제어를 위한 루프와 센서의 증가는 PFC circuit의 비용과 form factor를 증가시키므 로 제어 기법을 단순화하고 센서를 줄여야 한다.

현재까지 CCM으로 동작하는 PFC circuit은 센서를 줄이고 제어를 단순화하는데 집중하고 있으며 이러한

그림 1. Boost converter에 기초한 active PFC circuit Fig. 1. Active PFC circuit based on boost converter.

연구 결과로 다양한 기술이 나오고 있다. 입력전류를 감지하는 센서를 제거하기 위해 인덕터 양단의 전압을 감지하여 인덕터의 전압과 전류 관계를 바탕으로 입력 전류를 예측하는 방법이 여러 논문들에서 제안되었다<sup>[6~9]</sup>. 또한 출력전압 센서를 제거하기 위한 제어기법도 제안 되었다<sup>[10]</sup>. 하지만 PFC circuit은 AC 입력전압 주파수 의 두 배의 주파수 성분이 출력전압에 나타나며, 이를 제거하기 위해 전압루프의 bandwidth는 통상적으로 20Hz 이하로 설계한다. 따라서 출력전류나 입력전압이 변하는 과도응답 상황에서 응답속도가 매우 느리므로, 신뢰성 있는 과전류 및 과전압 보호회로의 사용이 필수 적이다. 기존에 연구된 입력전류와 출력전압 센서를 제 거할 수 있는 방법들은 제어루프를 단순화 할 수 있으 나, 신뢰성 있는 보호회로의 기능은 대체할 수 없으므 로 실용성이 낮다. 이러한 문제를 해결하기 위해 입력 전압을 감지하는 센서를 제거하기 위한 다양한 기법들 이 제안되었다[11~13]. 하지만 디지털로 구현된 기법들은 복잡한 디지털 연산을 수행하기 위해 고속으로 동작하 는 digital signal processor (DSP)를 필요로 한다<sup>[11~12]</sup>. 반면 아날로그 회로를 통해 구현된 기법의 경우 CCM 으로 동작하는 PFC circuit에서만 PF를 향상시킬 수 있 다<sup>[13]</sup>. CCM으로 동작하도록 설계된 PFC circuit 이라도 출력전류가 작은 경 부하 조건이 되면 DCM으로 동작 하게 되고 PF가 감소하는 문제를 유발한다.

본 논문에서는 입력전압을 감지하지 않고 PF를 향상시키기 위한 제어기법을 제안하였으며, 출력전류가 감소하는 경우 PFC circuit을 CRM 방식으로 동작시켜 PF가 감소하는 문제를 해결하였다. II 장에서는 제안한 입력전압을 감지하지 않는 CCM/CRM 이중모드 PFC circuit에 대하여 설명한다. III 장에서는 PFC circuit을 구성하는 세부회로들에 대하여 기술한다. IV 장에서

실험결과를 설명하고 V 장에서 본 논문의 결론을 설명 한다.

# Ⅱ. 입력전압을 감지하지 않는 CCM/CRM 이중모드 PFC circuit

1. 입력전압을 감지하지 않는 PFC circuit 제어방법 PFC circuit은 출력전압을 안정화시키고 입력전압  $V_{IN}$ 과 입력전류  $I_L$ 을 동상으로 만들기 위한 두 가지 기 능을 수행한다. CCM 동작을 수행하는 PFC circuit에서 상기 동작을 수행하기 위해 제어회로는 일반적으로 그 림 1. 의 구조를 갖으며 출력전압  $V_{O}$ 과 입력전압  $V_{IN}$ 및 입력전류  $I_L$ 를 감지하기 위한 세 개의 센서가 필요 하다. 이와 같은 센서의 사용은 PFC 제어 IC의 핀수와 외부 소자를 증가시키므로 비용과 form factor 증가를 야기한다. 따라서 본 논문에서는 센서를 줄이기 위해 입력전압  $V_{IN}$ 을 감지하지 않는 제어기법을 제안하였다. CCM 동작을 수행하는 boost converter의 경우 입력

전압  $V_{IN}$ 과 출력전압  $V_O$ 은 수식 (1)의 관계를 갖는다.

$$\frac{V_{IN}}{V_O} = 1 - D = D_{OFF}.$$

(1)

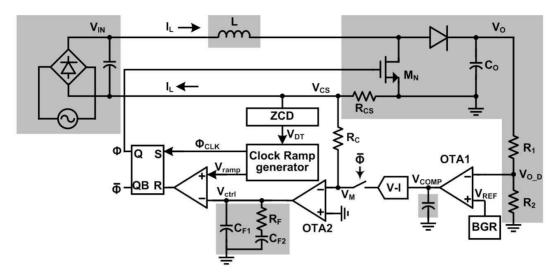

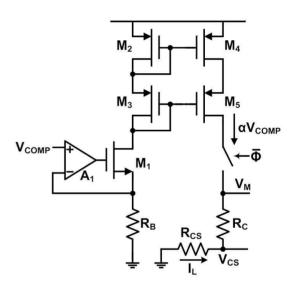

이때, D는 NMOS 스위치가 켜지는 converter의 duty 이고, Doff는 NMOS 스위치가 꺼지는 converter의 off duty이다. 만일 PFC circuit의 출력전압 Vo를 거의 DC 로 가정하면 입력전압  $V_{IN}$ 은 PFC circuit의 off duty  $D_{OFF}$ 와 비례한다. 따라서 입력전류  $I_L$ 을  $D_{OFF}$ 에 비례 하도록 구성하면, 수식 (1)에 의해 입력전압  $V_{LN}$ 과 입력 전류  $I_L$ 은 비례하게 된다. 입력전압이 정현파를 갖는다 면 입력전류는 동일한 위상을 갖는 정현파가 되고, PFC 동작을 수행하게 된다. 상기와 같이 off duty  $D_{OFF}$  $_{ell}$  입력전류  $I_L$ 이 비례하도록 구성하기 위해, 그림 3.과 같은 회로를 제안하였다. 여기서 음영으로 처리된 부분 은 외부 소자를 이용하여 구현한 것이다. 출력전압 $V_0$ 을 원하는 값으로 레귤레이션 하기 위해 bandgap reference (BGR)로부터 안정적인 기준전압  $V_{REF}$ 를 생 성하고 출력전압으로부터 저항분배에 의해 생성된  $V_{O_D}$ 와 비교하여 OTA1은 에러 전압  $V_{COMP}$  전압을 생 성한다. 생성된  $V_{COMP}$  전압은 전압 전류 변환기 (V-I)converter)를 이용하여 전압에 비례하는 전류  $aV_{COMP}$ 를 생성하고 이 전류는  $\Phi$ 가 LOW일 때, 저항  $R_C$ 로 흘

그림 2. 동작모드에 따른 전류 파형

Fig. 2. Current waveform with respect to operation

(c) CCM 동작파형 (c) CCM operation

려주게 된다. 센싱저항  $R_{CS}$ 를 ground (GND)와 bridge diode 사이에 연결하여 입력전류  $I_L$ 이  $R_{CS}$ 를 통해 흐르 게 되므로  $V_{CS}$ 는 수식 (2)의 값을 갖는다.

$$V_{CS} = -I_L R_{CS}. \tag{2}$$

따라서 OTA2의 negative 입력전압  $V_M$ 은 수식 (3)의 값을 갖는다.

$$\begin{split} V_{M} = & -I_{L}R_{CS} & (\Phi = HIGH) \\ V_{M} = & -I_{L}R_{CS} + \alpha \, V_{COMP} (\Phi = LOW). \end{split} \tag{3}$$

OTA2와  $R_F$ ,  $C_{F1}$ ,  $C_{F2}$ 로 구성된 적분기를 통해  $V_{ctrl}$ 전압을 생성하고, 이 전압을 클록 램프 생성기(clock and ramp generator)를 통해 생성된 ramp 전압  $V_{ramp}$ 와 비교하여 SR latch의 Reset 입력을 생성한다. SR latch

그림 3. 제안된 PFC circuit의 회로

Fig. 3. Schematic diagram of the proposed PFC circuit.

에 의해 클록신호  $\Phi_{CLK}$ 가 HIGH가 되면 NMOS 스위치 구동신호인  $\Phi$ 가 HIGH가 되어 입력전류가 증가한다.  $V_{ramp}$ 가  $V_{ctrt}$ 보다 커지면, SR-latch의 Reset 입력이 HIGH가 되어  $\Phi$ 는 LOW가 되고 입력전류는 감소한다. 이때 OTA2로 구성된 적분기의 동작에 의해  $V_M$ 의 한 주기  $T_S$  동안의 평균값은 수식 (4)의 관계를 갖는다.

$$\left\langle V_{M}\right\rangle _{T_{S}}=D_{OFF}(-I_{L}R_{CS}+\alpha V_{COMP})$$

$$+D(-I_{L}R_{CS})=0. \tag{4}$$

수식 (4)를 입력전류 IL에 대하여 정리하면, D+DOFF=1 이므로 수식 (5)를 얻을 수 있다.

$$I_L = \alpha D_{OFF} V_{COMP}. \tag{5}$$

수식 (1)과 수식 (5)로부터 다음과 같은 수식 (6)을 얻을 수 있다.

$$I_L = \frac{\alpha V_{COMP}}{V_O} \bullet V_{IN}. \tag{6}$$

PFC circuit의 출력전압은 DC 성분과 AC 입력전압 주파수의 두 배 주파수를 갖는 AC 성분의 합으로 구성된다. DC성분에 비해 AC성분은 매우 작으므로 출력전압은 DC로 고려할 수 있다. 출력전압에서 존재하는 AC 성분을 제거하기 위해 전압루프의 bandwidth는 통상적으로 20Hz 이하로 설계하므로  $V_{COMP}$  전압 또한 거의 DC로 가정할 수 있다. 따라서 수식 (6)의 입력전류  $I_L$ 은 입력전압  $V_{IV}$ 에 비례하게 되어. PFC 동작을 수행하

게 된다. 그림 3.과 같이 본 논문에서 제안하는 PFC circuit의 제어기법은 그림 1.과 같은 일반적인 구조의 PFC circuit과 달리 입력전압  $V_{IN}$ 에 대한 정보가 없어도 입력전류  $I_L$ 을 입력전압  $V_{IN}$ 에 비례하도록 동작한다. 따라서 기존의 PFC circuit 제어기법과 달리 입력전압을 감지할 필요가 없으며, 이를 통해 PFC 제어 IC의외장 핀과 외부 소자의 수를 줄일 수 있는 장점이 있다.

### 2. CCM/CRM 이중모드 PFC circuit

PFC circuit이 CCM으로 설계되었음에도 불구하고, 입력전압이 높고, 출력전류가 작은 경 부하 조건에서는 입력전류가 영인 구간이 존재하게 되며, DCM으로 동작하게 된다. DCM으로 동작하는 경우  $D+D_{OFF}$ ≠1이므로, 입력 및 출력전압과 duty 관계는 그림 2. 로부터 수식 (7)과 같이 유도할 수 있다.

$$V_{IN} = \frac{V_O D_{OFF}}{D + D_{OFF}}. (7)$$

입력전압  $V_{IN}$ 이  $D_{OFF}$ 에 비례하는 값이 아니므로, 본 논문에서 제안한 제어회로를 통해 입력전압에 비례하는 입력전류를 생성할 수 없다. 따라서 DCM으로 동작하는 경우 PF가 감소한다.

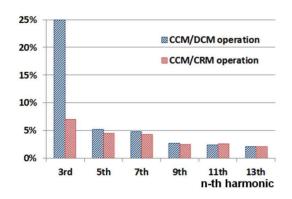

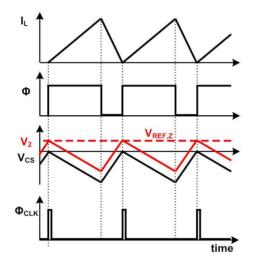

상기와 같은 문제를 해결하기 위해 본 논문에서는 출 력전류가 작은 경 부하 조건에서 입력전류가 영이 되 면, 강제로 스위칭 동작을 수행하여 CRM 동작을 수행 하도록 하였다. CRM 동작의 경우 입력전류가 영이 되

### 그림 4. 입력전압이 264VRMS 이고, 출력전류가 200mA 일 때 DCM과 CRM 동작에 따른 harmonics 비 교

Fig. 4. Harmonics comparison between CCM/DCM operation and CCM/CRM at VIN = 264VRMS, IOUT = 200mA.

면 다음 스위칭 동작을 수행하므로 CCM 동작의 일종 이 되고, 수식 (1)의 조건을 만족하게 된다. 따라서 경 부하 조건에서도 제안한 제어회로를 통해 입력전압에 비례하는 입력전류를 생성할 수 있고, PF의 감소를 막 을 수 있다. 입력전압이  $264V_{RMS}$  이고, 출력전류가 200mA일 때. CCM/DCM 동작을 수행하는 경우와 CCM/CRM 동작을 수행하는 경우의 입력전류의 harmonics에 대한 simulation 결과를 그림 4.에 비교하였다. 가로축에는 harmocis number를 표기하였고, 세로축에는 fundamental current에 대한 해당 harmocis current의 비율을 표기하 였다. CCM/CRM 동작을 수행하는 경우가 CCM/DCM 동작을 수행하는 경우보다 harmonics 성분이 감소하는 것을 확인할 수 있다. 하지만 CRM 동작을 수행하면 스 위칭 주파수는 빨라지게 되고, PFC circuit의 스위칭 loss가 증가하여 전체 PFC circuit의 효율이 감소할 수 있다. 따라서 CRM 동작을 수행하더라도 최대 스위칭 주파수를 제한할 필요가 있으며 본 논문에서 CCM 동 작 시 주파수는 70KHz이고 CRM 동작 시 최대 주파수 는 200KHz로 설정하였다.

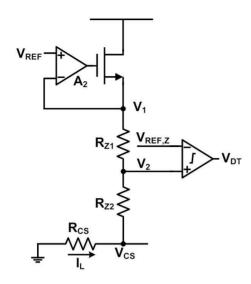

CRM 동작을 수행하기 위해서는 입력전류가 영임을 판별할 수 있는 zero current detector (ZCD) 회로가 필요하고 영전류가 되었을 때 클록신호를 발생시킬 수 있는 클록 램프 생성기가 필요하다. 따라서 그림 3. 와 같이 센싱저항  $R_{CS}$ 를 통해 생성된 전압  $V_{CS}$ 를 이용하여 입력전류가 영이 되면 ZCD 회로가  $V_{DT}$ 신호를 생성하고, 생성된  $V_{DT}$  신호와 동기화하여 클록을 생성할 수 있는 클록 램프 생성기를 사용하였다.

# Ⅲ. 구 현

# 1. 전압 전류 변환기(V-I converter)

OTA1 으로부터 생성된 에러 전압  $V_{COMP}$ 와 비례하는 전류를 생성하는 전압 전류 변환기의 구조를 그림 5. 에 나타내었다. 증폭기  $A_1$ 과 저항  $R_B$ , 트랜지스터  $M_1$ 으로 구성된 feedback loop는  $R_B$  양단의 전압이  $V_{COMP}$ 가 되도록 구성한다. 따라서  $R_B$ 에는  $V_{COMP}/R_B$ 의 전류가 흐르게 되고 이는 동일 크기로 구성된  $M_2$ - $M_4$ 에 의해 전압 전류 변환기의 출력전류  $aV_{COMP}$ 를 생성한다. 따라서  $R_C$ 로 공급되는 전류  $aV_{COMP}$ 는 수식 (8)과 같다.

$$\alpha V_{COMP} = \frac{V_{COMP}}{R_B}.$$

(8)

그림 5. 전압 전류 변환기 Fig. 5. V-I converter.

### 2. Zero current detector (ZCD)

제안한 PFC circuit의 CRM 동작을 위해서는 입력전류가 영이 되는 시점을 감지하기 위한 회로가 필요하다. 영전류를 감지하는 가장 쉬운 방법은 transformer를 이용하여 영전류 시 발생하는 공진을 감지하는 것이지만 추가적인 transformer의 사용에 따른 비용증가와 form factor의 증가를 야기한다 $^{[14]}$ . 따라서 제안한 회로에서는 입력전류를 감지하는 센싱저항  $R_{CS}$ 를 통해 생성되는  $V_{CS}$  전압을 이용하여 영전류를 감지하는 ZCD회로를 사용하였다.  $V_{CS}$ 의 전압은  $R_{CS}$ 에 의해  $-I_L \cdot R_{CS}$ 의 값을 갖는다. 따라서 음의 값을 갖는 전압을 비교하

그림 6. 영전류 감지회로 Fig. 6. Zero Current Detector.

그림 7. 영전류 감지회로의 동작파형

Fig. 7. Timing diagram of the zero current detector.

여 영전류가 되는 시점을 감지해야 한다. 이와 같은 동작을 수행하기 위해 그림 6.과 같이 레벨 시프팅 동작을 수행하였다. 증폭기  $A_2$ 와 트랜지스터  $M_1$ , 저항  $R_{Z1}$ ,  $R_{Z2}$ 를 이용하여 feedback loop를 구성하여  $V_1$ 의 전압이 기준전압  $V_{REF}$ 와 동일하게 하였다. 저항 분배 법칙에 의해  $V_2$  전압은 수식 (9)의 값을 갖는다.

$$V_2 = \frac{R_{Z1}}{R_{Z1} + R_{Z2}} V_{CS} + \frac{R_{Z2}}{R_{Z1} + R_{Z2}} V_{REF}.$$

(9)

생성된  $V_2$  전압을 수식 (9)의 관계에 따라 양의 값으로 레벨을 변화시킬 수 있다. 입력전류가 증가하면  $V_2$ 의 전압은 감소하고, 입력전류가 감소하여 영이 되면,

$V_2$  전압은  $R_{Z2} \cdot V_{REF}/(R_{Z1} + R_{Z2})$ 의 값을 갖는다. 이때 비교기를 이용하여 기준전압  $V_{REF,Z}$ 와 비교하여  $V_{REF,Z}$ 보다  $V_2$ 전압이 높아지면  $V_{DT}$ 를 HIGH로 변경하여 영전 류가 되는 순간을 감지한다. CRM으로 동작하는 경우와 CCM으로 동작하는 경우의 ZCD 회로의 동작을 그림 7. 에 나타내었다.

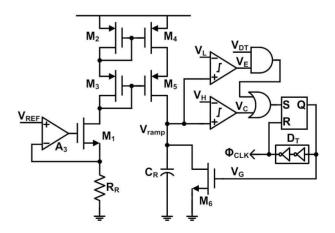

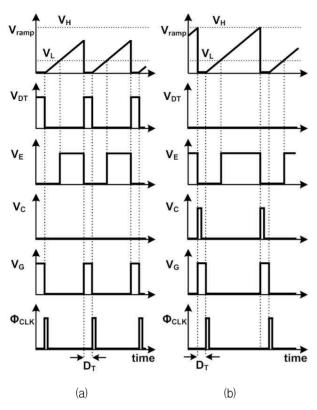

# 3. Clock and Ramp Generator

제안한 PFC circuit에서 설계한 클록 램프 생성기와 동작파형을 그림 8.와 그림. 9에 나타내었다. 초기 0V로 설정된 capacitor  $C_R$ 은 트랜지스터  $M_6$ 가 off 되면  $M_4$ 와  $M_5$ 를 통해 공급되는 전류에 의해 충전 동작을 수행 한다. 따라서 capacitor 양단의 전압  $V_{ramp}$ 는 선형적으로 증가하여 램프 전압을 생성한다.  $V_{ramp}$ 가 증가하여  $V_{H}$ 와 같아지면 비교기의 출력 Vc는 HIGH가 되고 SR latch의 동작에 의해  $V_G$ 는 HIGH가 된다. 이때 트랜지 스터  $M_6$ 는 ON이 되고  $V_{ramp}$ 의 전압은 다시 OV가 된다.  $D_T$ 의 delay를 갖는 delay circuit에 의해  $D_T$  시간 후  $\Phi$  $_{CLK}$ 는 HIGH가 되어 클록이 발생하고  $V_G$ 는 다시 LOW 가 된다. Capacitor 양단의 전압  $V_{ramp}$ 는 다시 상승하여 램프 전압을 생성하게 된다. 이때 CRM 동작을 지원하 기 위해 클록 램프 생성기는 입력전류가 영이 되면 발 생하는  $V_{DT}$  신호에 의해 동기화가 되어야 한다. 만일  $V_{ramp}$ 가  $V_L$ 보다 큰 경우  $V_{DT}$ 신호가 발생하면 ANDgate의 출력을 HIGH로 만들고 OR-gate에 의해 SR latch의 SET입력으로 인가된다. 따라서 CRM 동작에서  $V_{DT}$ 가  $V_C$ 보다 먼저 발생하는 경우에도  $V_{ramp}$ 가 초기화 되고  $D_T$  시간 후  $\Phi_{CLK}$ 이 발생하게 된다. 만일  $V_{ramp}$ 가

그림 8. 클록 램프 생성기 Fig. 8. Clock and ramp generator.

그림 9. 클록 램프 생성기의 동작파형. (a) CRM으로 동 작하는 경우, (b) CCM으로 동작하는 경우

Fig. 9. Timing diagram of the clock and ramp generator at (a) CRM and (b) CCM.

$V_L$ 보다 작다면  $V_{DT}$  신호가 발생하더라도 AND-gate에 의해 SR latch에 인가되지 않고  $V_{ramp}$ 가  $V_L$ 보다 커진후 SR latch에 인가된다. 따라서 PFC circuit의 입력전류가 영이 되더라도  $V_{ramp}$ 가  $V_L$ 보다 커지는 시간동안 스위칭이 발생할 수 없고, 해당 동작을 통해 최대 스위칭 주파수를 제한할 수 있다.

반면 PFC circuit이 영전류가 된 후에도 스위칭 동작을 수행하지 않으면 NMOS 스위치  $M_N$ 의 drain node에서는 공진이 발생하게 된다. 이때 공진주기는 NMOS스위치  $M_N$ 의 drain node에서 보이는 기생 capacitor와인덕터의 값에 의해 결정된다. 입력전류가 영이 된 후 drain node가 가장 낮은 전압이 되는 시간을  $D_T$ 와 동일하게 설정하면 soft switching 동작을 얻을 수 있고 효율을 향상시킬 수 있다.

# Ⅳ. 실 험

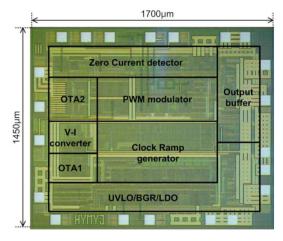

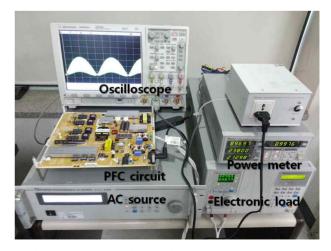

제안한 PFC circuit을 검증하기 위해 240W급 flat

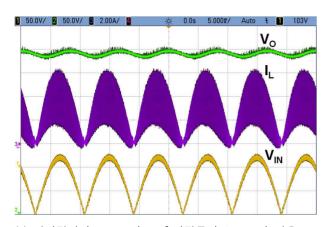

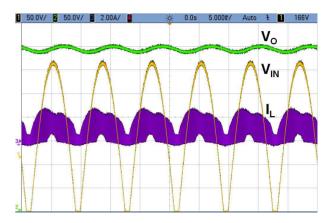

panel display 구동을 위한 PFC prototype을 구성하였다. PFC controller IC는 0.35µm BCDMOS 공정을 이용하여 제작하였으며, IC의 레이아웃 크기는 1700µm × 1450µm 이다. Chip 사진을 그림 10.에 첨부하였으며, PFC circuit의 측정환경을 그림 11.에 첨부하였다. 전원공급장치 (Chroma 61502)을 통해 AC 입력을 인가하고, PFC circuit을 통해 생성된 출력전압에 전자로드 (Chroma 63105A)를 연결하여 출력전압에 전자로드 (Chroma 63105A)를 연결하여 출력전류를 조절하였다. 파워미터 (Chroma 66201)과 오실로스코프 (Agilent DSO 7054B)을 이용하여 입출력 전압과 전류를 측정하였다. 입력전압이 90V<sub>RMS</sub>, 264V<sub>RMS</sub>이고 출력전류가 600mA 일 때의 입력전압과 전류, 출력전압의 측정과형을 그림 12.에 첨부하였다. CCM과 CRM 동작을 확인하기 위해 입력전압이 264V<sub>RMS</sub>이고 출력전류가 600mA

그림 10. Chip 사진

Fig. 10. Chip microphotograph.

그림 11. PFC circuit의 측정환경

Fig. 11. Measurement setup of the PFC circuit.

(b) 입력전압이 264V<sub>RMS</sub>이고, 출력전류가 600mA인 경우

(b)  $V_{IV} = 264V_{RMS}$ ,  $I_{OUT} = 600 \text{mA}$

그림 12. PFC circuit의 입력전압 및 전류, 출력전압의 측정파형

Fig. 12. Measurement results of input voltage VIN, current IL, and output voltage VO.

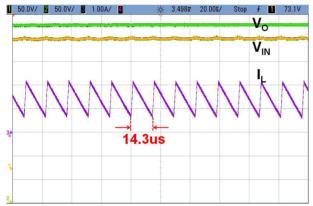

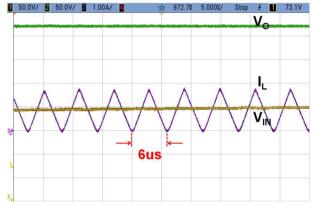

(a) CCM operation.

(b) CRM 동작을 수행하는 경우

(b) CRM operation.

그림 13. PFC circuit의 입력전압 및 전류, 출력전압의 세부 측정파형

Fig. 13. Measurement results of input voltage VIN, current IL, and output voltage VO.

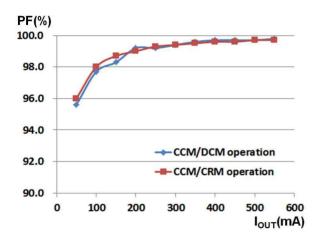

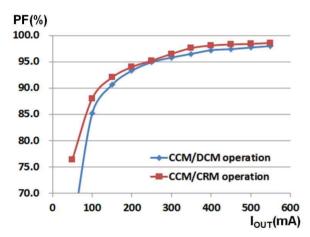

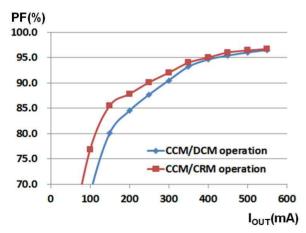

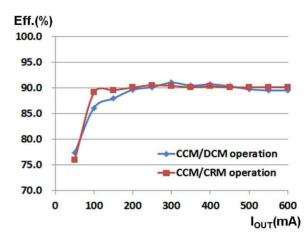

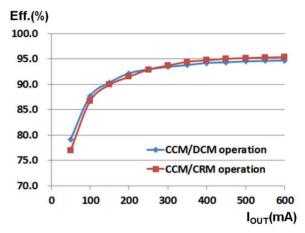

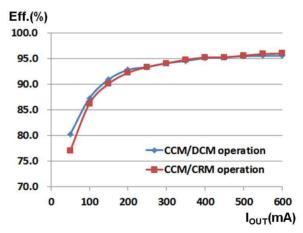

인 경우의 세부파형을 그림 13.에 첨부하였다. 그림 13. (a)에서는 70KHz 의 고정주파수로 CCM 동작을 수행하는 것을 확인할 수 있고, 그림 13. (b)에서는 CRM 동작을 수행하는 것을 확인할 수 있다. 출력전류가 작은 경 부하 조건에서 CRM 동작에 따른 PF의 개선을 확인하기 위해 CRM 동작의 유무를 결정할 수 있도록 PFC controller IC를 설계하였다. CRM 동작의 유무에 따른 출력전류에 대한 PF와 효율 측정결과를 그림 14. 와 그림 15.에 첨부하였고, 제안된 PFC circuit의 성능요약을 표 1.에 정리하였다. 또한 입출력 조건에 따른 PF와 효율을 표 2.에 기존의 CCM/DCM으로 동작하는 PFC 회로와 비교하였다. CCM/CRM 동작을 수행하는 경우 CCM/DCM의 경우보다 입력전압이 264V<sub>RMS</sub>이고 출력

전류가 100mA 일 때 최대 10% PF가 향상되는 것을 확인할 수 있다. PFC prototype의 경우 flat panel display 구동용으로 제작하였으며, IEC 61000-3-2 Class-D 규격을 따르게 되어 75W 이상의 출력전력 범위에서 PFC 동작을 수행해야 한다. 해당 조건은 출력전류가 190mA 이상인 조건이며, 이 경우 기존의 CCM/DCM으로 동작하는 PFC circuit 대비 최대 4%의 PF가 향상된다. 하지만 해당 조건에서 0.4%의 효율이 감소하였다. 이러한 현상은 출력전류가 작아지는 경부하 조건에서는 CRM 동작에 따라 스위칭 주파수가 빨라지게 되고, 스위칭 손실의 증가로 효율이 감소하기 때문이다. 스위칭 동작 시 최소 on time을 설정하게 되면 해당 효율 감소를 상쇄할 수 있다.

- (a) 입력전압이 90V<sub>RMS</sub>인 경우

- (a)  $V_{IN} = 90V_{BMS}$ .

- (b) 입력전압이 200V<sub>RMS</sub>인 경우

- (b)  $V_{IIV} = 200V_{RMS}$

- (c) 입력전압이 264V<sub>RMS</sub>인 경우

- (c)  $V_{IN} = 264V_{RMS}$ .

그림 14. CRM 동작의 유무에 따른 PF 비교

Fig. 14. PF comparisons between CCM/CRM operation and CCM/DCM operation.

- (a) 입력전압이 90V<sub>RMS</sub>인 경우

- (a)  $V_{IN} = 90V_{RMS}$ .

- (b) 입력전압이 200V<sub>RMS</sub>인 경우

- (b)  $V_{IV} = 200V_{RMS}$ .

- (c) 입력전압이 264V<sub>RMS</sub>인 경우

- (c)  $V_{IN} = 264V_{RMS}$ .

그림 15. CRM 동작의 유무에 따른 효율 비교

Fig. 15. Efficiency comparisons between CCM/CRM operation and CCM/DCM operation.

표 1. 제안한 PFC circuit의 성능요약

Table 1. Performance summay of the proposed PFC

| Parameter                | Value                 | Unit      |  |

|--------------------------|-----------------------|-----------|--|

| Technology               | 0.35µm BCDMOS process |           |  |

| Operating mode           | CCM/CRM               |           |  |

| AC Input voltage         | 90~264                | $V_{RMS}$ |  |

| Output voltage           | 393                   | V         |  |

| Max. output current      | 600                   | mA        |  |

| Max. switching frequency | 200                   | KHz       |  |

| Min. switching frequency | 70                    | KHz       |  |

| L                        | 160                   | μН        |  |

| $C_O$                    | 128                   | μF        |  |

| $R_{CS}$                 | 70                    | mΩ        |  |

| Current consumption      | 7                     | mA        |  |

표 2. CRM 동작의 유무에 따른 성능 비교 Table 2. Performance comparisons of CCM/CRM operation and CCM/DCM operation.

| Condition                                          | Power Factor(%) |      | Efficiency(%) |      |

|----------------------------------------------------|-----------------|------|---------------|------|

|                                                    | CRM             | DCM  | CRM           | DCM  |

| $V_{IN} = 90V_{RMS}$<br>$I_{OUT} = 190mA$          | 97.9            | 96.5 | 90.1          | 89.6 |

| $V_{IN} = 90V_{RMS}$<br>$I_{OUT} = 600mA$          | 99.3            | 99.1 | 90.1          | 89.5 |

| $V_{IN} = 264 V_{RMS}$<br>$I_{OUT} = 190 mA$       | 88.3            | 84.3 | 92.4          | 92.8 |

| $V_{IN} = 264V_{RMS}$<br>$I_{OUT} = 600 \text{mA}$ | 96.7            | 96.5 | 96.0          | 95.5 |

# Ⅴ. 결 론

본 논문에서는 입력전압을 감지하지 않는 전류연속/임계동작모드 active power factor correction(PFC) circuit을 제안하였다. 기존의 입력전압을 감지하지 않는 PFC circuit의 경우 출력전류가 낮은 경 부하 조건에서 DCM 동작을 수행하고, 이에 따라 PF가 감소하는 문제가 발생한다. 제안한 PFC circuit은 70KHz의 주파수로 CCM 동작을 수행하고, 경 부하 조건에서 최대 200KHz까지 스위칭 주파수가 가변되는 CRM 동작을 수행하도록 하였다. 이를 통해 경 부하 조건에서 PF가 감소하는

문제를 해결하였다. PFC controller IC는 0.35µm BCDMOS 공정을 이용하여 제작하였으며, 240W급 PFC prototype을 제작하여 실험하였다. 제안한 PFC circuit 은 기존의 PFC circuit 대비 최대 10%의 역률이 향상되었고 IEC 61000-3-2 Class D 규격에 따른 경 부하조건에서는 최대 4% 역률이 향상되었다.

### REFERENCES

- [1] R. W. Erickson and D. Maksimovic, *Fundamental* of *Power Electronics*, 2nd ed., Kluwer Academic Pub., pp 609–630, 2001.

- [2] J. Lai and D. Chen, "Design consideration for power factor correction boost converter operating at the boundary of continuous conduction mode and discontinuous conduction mode," in *Proceedings of IEEE Applied Power Electronics Conference and Exposition*, pp. 267–273, San Diego, CA., Mar. 1993.

- [3] S. Buso, P. Mattavelli, L. Rossetto, and G. Spiazzi, "Simple digital control improving dynamic performance of power factor preregulators," *IEEE Trans. Power Electronics*, vol. 13, no. 5, pp. 814 823, Sep. 1998.

- [4] F. Chen and D. Maksimovic, "Digital Control for Improved Efficiency and Reduced Harmonic Distortion over Wide Load Range in Boost PFC Rectifiers," In *Proc. Of IEEE Applied Power Electronics Conference and Exposition*, pp.760–766, Washington, DC., Feb. 2009.

- [5] 전인선, 김형우, 김기현, 서길수, 조효문, 이종화, "단일 역률 달성을 위한 Boost Converter용 PFC IC 설계," 전자공학회논문지, 제47권 SD편, 제2호, 60-67쪽, 2010년 2월.

- [6] H.-P. Le, C.-S. Chae, M.-C. Lee, S.-W. Wang, S.-I. Kim, and G.-H. Cho, "Integrated zeroinductor-current detection circuit for step-up DC-DC converters," *IET Electronics Letters*, vol. 42, no. 16, pp. 943 - 944, Aug. 2006.

- [7] Sivakumar S., Natarajan K., and Gudelewicz R. "Control of Power Factor Correcting Boost Converter Without Instantaneous Measurement of Input Current," *IEEE Trans. Power Electronics*, vol. 10, no. 4, pp. 435–445, Jul. 1995.

- [8] S. Bhowmik, A. van Zyl, R. Spee, and J. H. R. Enslin, "Sensorless Current Control for Active Rectifiers," *IEEE Trans. Ind. Applicat.*, vol. 33, no. 3, pp. 765–773, May./Jun. 1997.

- [9] Y. S. Roh, Y. J. Moon, J. C. Gong, and C. Yoo, "Active power factor correction (PFC) circuit with resistor-free zero-current detection," *IEEE Trans. Power Electronics*, vol. 26, no. 2, pp. 630 - 637, Feb. 2011.

- [10] T. O, and M. Hojo, "DC Voltage Sensorless Single-Phase PFC Converter," *IEEE Trans. Power Electronics*, vol. 19, no. 2, pp. 404-410, Mar., 2004.

- [11] P. Mattavelli, G. Spiazzi, and P. Tenti, "Predictive digital control of Power factor preregulators with input voltage estimation using disturbance observers," *IEEE Trans. Power Electronics*, vol. 20, no. 1, pp. 140 147, Jan. 2005.

- [12] W. Stefanutti, P. Mattavelli, G. Spiazzi, and P. Tenti, "Digital control of single-phase power factor preregulators based on current and voltage sensing at switch terminals," *IEEE Trans. Power Electronic*, vol. 21, no. 5, pp. 1356 1363, Sep. 2006.

- [13] K. De Gusseme, D. M. Van de Sype, A. P. M. Van den Bossche, and J. A. Melkebeek, "Input-Current Distortion of CCM Boost PFC Converters Operated in DCM," *IEEE Trans. Ind. Electronics*, vol. 54, no. 2, pp. 858 865, Apr. 2007.

- [14] 서길수, 김형우, 김기현, 박현일, 김남균, 박주성, "Zero Cross Detection Power factor Correction IC 설계," 대한전자공학회 하계종합학술대회 논문 집, 519-520쪽, 2008년.

- 저 자 소 개

노 용 성(학생회원)

2007년 한양대학교 전자통신

컴퓨터공학부 학사 졸업.

2007년∼현재 한양대학교 전자

컴퓨터통신공학과

석박사 통합과정.

<주관심분야: 전력관리용 반도체 회로설계>

유 창 식(평생회원) 1992년 서울대학교 정2

1992년 서울대학교 전자공학과 학사 졸업.

1994년 서울대학교 전자공학과 석사 졸업.

1998년 서울대학교 전자공학과 박사 졸업.

2002년~현재 한양대학교 융합전자공학부 교수. <주관심분야: 혼성 신호 회로 설계, 전력관리용 반도체 회로 설계>