# Cylindrical Silicon Nanowire Transistor Modeling Based on Adaptive **Neuro-Fuzzy Inference System (ANFIS)**

# Jalal Rostamimonfared<sup>†</sup>, Abolfazl Talebbaigy\*, Teamour Esmaeili\*, Mehdi Fazeli\* and Atena Kazemzadeh\*

**Abstract** – In this paper, Adaptive Neuro-Fuzzy Inference System (ANFIS) is applied for modeling and simulation of DC characteristic of cylindrical Silicon Nanowire Transistor (SNWT). Device Geometry parameters, terminal voltages, temperature and output current were selected as the main factors of modeling. The results obtained are compared with numerical method and a good match has been observed between them, which represent accuracy of model. Finally, we imported the ANFIS model as a voltage controlled current source in a circuit simulator like HSPICE and simulated a SNWT inverter and common-source amplifier by this model.

**Keywords**: Silicon Nanowire Transistor, Modeling, Simulation, ANFIS

#### 1. Introduction

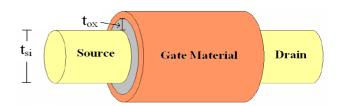

The silicon MOSFET for VLSI technology has been scaled down for higher integration and higher performance. Further miniaturization of silicon MOSFETs into nanoscale will have great impact on the advancement of future Integrated Circuit (IC) [1]. As the dimension of MOSFETs enters the nanometer regime, however, Short Channel Effects (SCEs) [2], such as threshold voltage (VT) and Drain-Induced Barrier-Lowering (DIBL), become more and more significant, which limit the scaling capability of planar bulk or Silicon-on-Insulator (SOI) MOSFETs [3]. Consequently, effective gate control is required for a nanoscale MOSFET to achieve good device performance. For these reasons, various new device structures and materials are being explored. The SNWT is one of promising technology in this field. This technology is based on silicon and may offer better gate control, simpler fabrication, more flexibility in device design and the best candidate for high speed applications [4, 5]. The cylindrical SNWT is shown in Fig. 1.

The silicon channel in this structure is covered by a cylindrical surrounding-gate electrode, providing an excellent control of Short-Channel Effects (SCEs). With respect to these points, description of characteristics of these devices is necessary.

Because the experimental work is difficult and expensive, there is requiring modeling the behavior of SNWT at circuit level. Such model must be enabling to simulate silicon nanowire circuit in a reasonable amount of time.

Number of attempts have been accomplished for modeling and simulation of SNWTs with numerical

Received: October 27, 2012; Accepted: April 9, 2013

methods that are based on different models like selfconsistent numerical model, Monte Carlo transport model, non equilibrium Green function (NEGF) approach and etc [6-10]. These methods are complicated and take a lot of simulation times. This paper introduces a method for modeling the SNWT based on computational intelligence technique (ANFIS) that can reduce the computational time while keeping the accuracy of previous models.

The data needed for training of ANFIS is obtained from

Fig. 1. The cross-section views of a cylindrical silicon Nanowire transistor structure

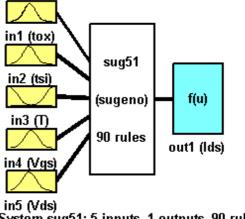

System sug51: 5 inputs, 1 outputs, 90 rules

Fig. 2. A simplified overview of ANFIS network model

Corresponding Author: Dept. of Electrical Engineering, Islamic Azad University, DarehShahr, Iran (jalalmonfared@yahoo.com)

Dept. of Electrical Engineering, Islamic Azad University, Dareh

SiNWFETToy2.0 program [11]. This program is a set of MATLAB subroutines that are derived by modifying an analytical approach proposed by A. Rahman et al. [12] for Silicon Nanowire Transistors. A simplified overview of ANFIS model is shown in Fig. 2.

Where, gate oxide thickness (tox or in1), silicon film thickness (tsi or in2), temperature (T or in3), gate-source voltage (Vgs or in4), drain-source voltage (Vds or in5) are the input parameters and drain current (Ids or out1) is outputparameter in the SNWT.

### 2. Adaptive neuro-fuzzy inference system (Anfis)

Combining both fuzzy logic and artificial neural network allows achieving all of the advantages of both systems. The ANFIS structure [13]-[16] is one of the proposed methods to combine fuzzy logic and artificial neural networks and that is a multilayer feed forward network where each node performs a particular function on incoming signals. In this paper, a hybrid algorithm, which is a combination of back-propagation gradient descent and the least-squares method, is used to identify linear and nonlinear parameters in the ANFIS [15]. More specifically, in the forward pass of the hybrid learning algorithm, node outputs go forward and the consequent parameters are identified by the least-squares method [13]. In the backward pass, the error signals propagate backwards and the premise parameters are updated by gradient descent.

This paper considers the ANFIS structure with a first-order Sugeno model containing 90 rules, five inputs in1 (tox ), in2 (tsi), in3 (T), in4 (Vgs), in5 (Vds) and one output out (Ids), a typical rule set with 90 fuzzy if-then rules can be expressed as:

- 1. If (in1 is in1mf1) and (in2 is in2mf1) and (in3 is in3mf1) and (in4 is in4mf1) and (in5 is in5mf1) then (out1 is out1mf1=p1in1+q1in2+h1in3+g1in4+k1in5+r1)

- 2. If (in1 is in1mf2) and (in2 is in2mf2) and (in3 is in3mf2) and (in4 is in4mf2) and (in5 is in5mf2) then (out1 is out1mf2= p2in1+q2in2+h2in3+g2in4+k2in5+r2)

89. If (in1 is in1mf89) and (in2 is in2mf89) and (in3 is in3mf89) and (in4 is in4mf89) and (in5 is in5mf89) then (out1 is out1mf89= p89in1+q89in2+h89in3+g89in4+k89in5+r89)

90. If (in1 is in1mf90) and (in2 is in2mf90) and (in3 is in3mf90) and (in4 is in4mf90) and (in5 is in5mf90) then (out1 is out1mf90 = p90in1+q90in2+h90in3+g90in4+k90in5+r90).

$\{pj,qj,hj,gj,kj,rj\}$  and inLmfj are linear output parameters and linguistic labels respectively, where j=1,2,...,90, L=1,2,...5.

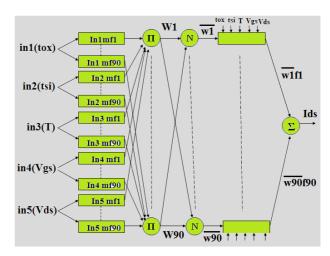

The architecture of the ANFIS is shown in Fig. 3. The

Fig. 3. ANFIS Model Structure

Table 1. Data ranges used for building the ANFIS model

| Range | input   |         |       |        |        |  |

|-------|---------|---------|-------|--------|--------|--|

|       | tox(nm) | tsi(nm) | T(ok) | Vgs(v) | Vds(v) |  |

| Min   | 1       | 1       | 300   | 0      | 0      |  |

| Max   | 3       | 5       | 320   | 1      | 1      |  |

complete system consists of five layers; the node functions in the same layer are similar and described as below.

**Layer 1:** Each node in this layer is an adaptive node and that generates membership grades of a linguistic label. For an external input xi, the following Gaussian membership function (MF) is assumed to be used:

$$O_{2,j} = w_j = \mu_1^{i_1} \mu_2^{i_2} \mu_3^{i_3} \mu_4^{i_4} \mu_5^{i_5}$$

$$(j = 1, ..., c_i), (i_1 = 1, ..., c_1), ..., (i_5 = 1, ..., c_5)$$

(2)

Where, in this work  $c_1 = ... = c_5 = 90$ .

Layer 3: every node in this layer presents a normalization of the firing strength from the previous layer. The jth node of this layer calculates the ratio of the jth rule's firing strength to the sum of all rule's firing strengths:

$$O_{3,j} = \overline{w_j} = wb_j = \frac{w_j}{\sum_i w_i}, (i = 1, ..., 90)$$

(3)

**Layer 4**: Every node j in this layer is a square node. The relationship between the inputs and output of this layer can be defined as the following:

$$O_{4,j} = \overline{w_j} f_j = \overline{w_j} (p_j t_{ox} + q_j t_{si} + h_j T + q_j V_{gs} + k_j V_{ds} + r_j), (j = 1, ...., 90)$$

(4)

Where  $\overline{w_j}$  is the output of layer 3, and  $\{p, q, h, g, k, r\}$  is the parameter set. Parameters in this layer are referred to as the consequent parameters.

**Layer 5**: The single node in this layer evaluates the overall outputs as the summation of all incoming signals:

$$O_5 = \sum_j \overline{w_j} f_j = \frac{\sum_j w_j f_j}{\sum_j w_j}$$

(5)

Where, O5 is the output of Layer 5.

# 3. Result and discussion

The required data for training ANFIS has been obtained from SiNWFETToy2.0 program. This data (3740 samples) is divided into two sets, Training set (about 70%) that is used for training and testing set (about 30%) that is used for testing of ANFIS network. The minimum and maximum input data ranges used for building the ANFIS model is shown in Table 1.

We used our database for training the ANFIS model with MATLAB 7.0.4 program. The final ANFIS architecture being used in this work is shown in Table 2.

We used the Mean Relative Error (MRE %) as a measure of error made by the network which is defined in Eq. (6).

MRE% =

$$\frac{1}{N_p} \sum_{i=1}^{N_p} \left| \frac{X_{num} - X_{pred}}{X_{num}} \right| \times 100$$

(6)

Where, Xnum and Xpred are numerical value obtained by SiNWFETToy2.0 program and predicted values obtained by ANFIS, respectively, also,  $N_P$  is number of points. The MRE% of output (Ids) for ANFIS is shown in Table 3.

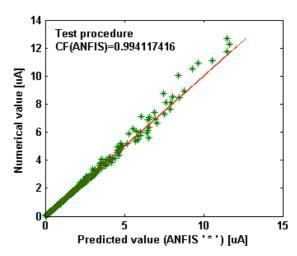

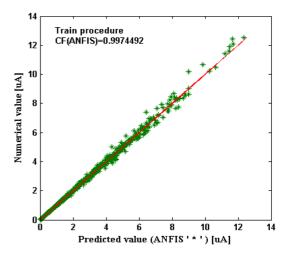

In order to confirm the predictive property of the optimized network structure, testing and training sets were compared with the network response. Figs. 4 and 5 shows that in these cases, a good match between SiNWFETToy2.0 simulation and predicted (ANFIS) results was found.

Table 2. Optimal specification of proposed ANFIS model

| Item                             |  | Specification      |  |

|----------------------------------|--|--------------------|--|

| Inputs/outputs                   |  | 5/1                |  |

| ANFIS model:                     |  |                    |  |

| FIS Type                         |  | Sugeno             |  |

| Train FIS method                 |  | hybrid             |  |

| Input MF Type                    |  | Gaussian mf        |  |

| No. of input membership function |  | 90 for each inputs |  |

| Output Membership Function Type  |  | Linear             |  |

| Number of rules                  |  | 90                 |  |

| Epochs                           |  | 500                |  |

Table 3. MRE% of output (Ids) for ANFIS model

|   | Data        | Train | Test |

|---|-------------|-------|------|

| _ | MRE%(ANFIS) | 1.80  | 2.33 |

**Fig. 4.** Comparisons of the numerical and the predicted results using ANFIS model for testing data

**Fig. 5.** Comparisons of the numerical and the predicted results using ANFIS model for training data

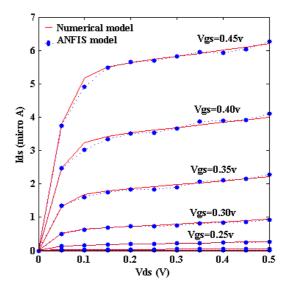

Fig. 6. Current-voltage characteristics curve (Ids-Vds) for ANFIS model

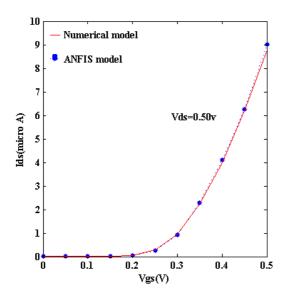

**Fig. 7.** Current-voltage characteristics curve (Ids-Vgs) for ANFIS model

**Table 4.** Approximate CPU time(s) comparison between the various approaches of modeling of the SNWT

| No. of simulation data | SiNWFETToy | ANFIS |

|------------------------|------------|-------|

| 30                     | 350.7      | 1.7   |

| 100                    | 772.1      | 2.2   |

| 150                    | 1109.4     | 3.4   |

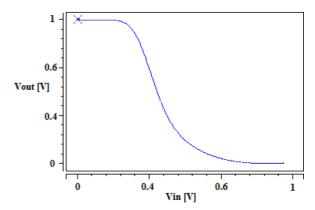

Figs. 6 and 7 compare predicted values and numerical results of the current-voltage characteristics (Ids-Vgs and Ids-Vds) with tox=1nm, tsi=3nm and T=300ok. It can be seen that the best match between them is obtained.

Beside their high precision, ANFIS model has a higher calculative speed rather than the numerical model. Table 4 offers a comparison between the amounts of the approximate required time for CPU to simulate SNWT with different methods in which the calculative time of intelligent model have been compared with those of the numerical models for different simulating data.

As the results shows, the intelligent models have a high precision and speed; therefore, they can be used as appropriate tools for simulating in the level of nanoscale circuits.

#### 4. Implementation into hspice

In HSPICE implementation, we imported ANFIS model of SNWT as a subcircuit constituted of a null current source (ig) between gate and source and a voltage-controlled current source Ids (Id) [17-19]. The general Syntax form in HSPICE software is:

. SUBCKT subname D G S ig G S  $\mathbf{0}$

Ids D S curr = 'ANFIS equations to obtain the drain current'

#### .ENDS

where 'subname' is the name for the subcircuit model, 'D', 'G' and 'S' are the drain, gate source nodes of the device, respectively. The 'curr' expression is drain current and given by the ANFIS functions.

In this study, the ANFIS evaluate the drain current as a function of input parameters set. Indeed, the results of the training process for ANFIS network are premise and consequent parameters associated with the nodes. Therefore, the final expression of the drain current is given by the equation (7) for ANFIS network.

$$I_{d} = \exp\left[\sum_{j} \overline{w_{j}} f_{j}\right] = \exp\left[\sum_{j=1}^{90} \overline{w_{j}} f_{j}\right]$$

$$f_{j} = (p_{j} t_{ox} + q_{j} t_{si} + h_{j} T + g_{j} V_{gs} + h_{j} V_{ds} + r_{j})$$

(7)

Where 90 number of rules,  $w_j$  using equations (3) until (5) and parameters set {pj, qj, hj, gj, kj, rj} (consequent parameters) achieved by ANFIS.

We used the logarithm scaling to decrease the dynamic of the drain current, so, for the descaling, we applied the

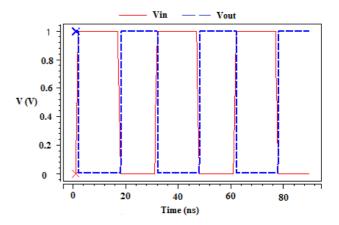

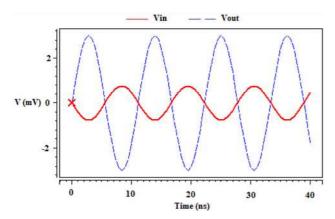

**Fig. 8.** The HSPICE input (-) and output (--) signals of our ANFIS inverter gate

**Fig. 9.** The predicted transfer curve of ANFIS SNWT inverter

**Fig. 10.** The HSPICE input (-) and output (--) signals of the ANFIS common-source amplifier

exponential function. Finally, in order to demonstrate the merit of our ANFIS model, the simulation of the SNWT inverter and common-source amplifier is suggested. Figs. 8 and 9 shows HSPICE input/output signals and transfer curve of our inverter gate, respectively. Also, HSPICE input/output signals for common-source amplifier are shown in Fig. 10.

#### 5. Conclusion

In this paper, an attempt has been made to demonstrate the capability of the ANFIS for modeling and simulation of cylindrical silicon nanowire transistor. We used numerical simulation of current-voltage characteristics of SNWT using SiNWFETToy2.0 program to build the required database in order to optimize our ANFIS structures. The result obtained shows that there is a very good agreement between the predicted output characteristics of the device based on the ANFIS model and the numerical method. These results, also, demonstrates that ANFIS model can be used as an interface between device modeling and circuit simulator (like HSPICE) in order to achieve high computation speed for circuit's simulation and to improve the simulation time of nano electronic devices.

#### Acknowledgements

This work was supported by the Department of Electric Engineering, Islamic Azad University, DarehShahr, Iran.

## References

[1] Toshiro Hiramoto, Kousuke Miyaji and Masaharu Kobayashi, "Nanoscale Silicon Devices Using Nanostructure Physics for VLSI Applications", Institute of Industrial Science, University of Tokyo.

- [2] Y. Taur and T. H. Ning, "Fundamentals of Modern VLSI Devices", Cambridge, UK: Cambridge University Press, 1998.

- [3] J. Wang, "Device physics and simulation of silicon nanowire transistors", a preliminary report, Purdue University, 2004.

- [4] J. Wang, E. Polizzi, and M. Lundstrom, "A computational study of ballistic silicon nanowire transistors" in IEDM Tech, pp, 29.5.1-29.5.4, 2003.

- [5] Mohammad Taghi Ahmadi, Hui Houg Lau, Razali Ismail, Vijay K. Arora, "Current voltage characteristics of a silicon nanowire transistor", Microelectronic Journal, 2008.

- [6] H. Sakaki, "Scattering suppression and high mobility effect of size quantized electron in ultrafin semiconductor wire structure", Jpn. J. Appl. Phys., Vol. 19, No. 12, pp. L735-L738, Dec. 1980.

- [7] Andrea Ghetti, GianPietro Carnevale and Denis Rideau, "Coupled Mechanical and 3-D Monte Carlo Simulation of Silicon Nanowire MOSFETs", IEEE Tranactions on nanotechnology, Vol. 6, No. 6, November 2007.

- [8] Jinghong Chen, "A circuit-compatible analytical device model for ballistic nanowire transistors", Microelectronics Journal 39, 2008.

- [9] Andrea Ghetti and Denis Rideaut, "3D Monte Carlo Device Simulation of NanoWire MOSFETs including Quantum Mechanical and Strain Effects", STMicroelectronics 2004.

- [10] Mincheol Shin, "Three-dimensional quantum simulation of multigate nanowire field effect transistors", sciencedirect, 2007.

- [11] http://www.nanohub.org/resources/Downloads/FE TToy 2.0.

- [12] A. Rahman, J. Guo, S. Datta, and M. Lundstrom, "Theory of Ballistic Nanotransistors", IEEE Trans. on Electron Device 50, 1853, 2003.

- [13] J.-S. Roger Jang, "ANFIS: Adaptive-Network-Based Fuzzy Inference System", Transactions on Systems, Man, and Cybernetics, Vol. 23, No. 3, pp. 665-685, 1993.

- [14] J.-S. R. Jang and C.-T. Sun, "Neuro-fuzzy modeling and control", Proc. IEEE, Vol. 83, pp. 378-406, Mar. 1995.

- [15] Xiao-Juan Wu, Xin-Jian Zhu, Guang-Yi Cao, Heng-Yong Tu, "Nonlinear modeling of a SOFC stack based on ANFIS identification", Simulation Modelling Practice and Theory, sciencedirect, 399-409, 2008.

- [16] J.-S.R. Jang, "Neuro-Fuzzy and Soft Computing", Prentice-Hall, New Jersey (1997).

- [17] "HSPICE Quick Reference Guide", Synopsys, Inc., 2003.

- [18] Hanene Ben Hammouda, Mongia Mhiri, Zièd Gafsi and Kamel Besbes, "Neural-Based Models

- of Semiconductor Devices for SPICE Simulator", American Journal of Applied Sciences 5 (4): 385-391, 2008.

- [19] Mohsen Hayati, Abbas Rezaei, Majid Seifi, Besbes, "CNT-MOSFET modeling based on artificial neural network: Application to simulation of nanoscale circuits", sciencedirect, 2009.

**Mehdi Fazeli** received his B.Sc Degree in Applied Physics in 2007 and his M.Sc. Degree in electronic engineering in 2010. His research interests include Semiconductor, Intrgrated Circuit Devices and power electronic circuits.

Jalal Rostamimonfared was born in Darehshahr, Iran in 1980. He received the B.Sc. degree from K. N. Toosi University of Technology in 2004 (Tehran/Iran), M.Sc. degree from Razi University of Kermanshah (Kermanshah/Iran), both in electrical engineering. His interested areas are artificial neural net-

work, semiconductor, Integrated Circuit Devices and power electronic circuits.

**Abolfazl Talebbaigy** was born in Arak, Iran, in 1984. He received the B.Sc. degree in electrical and electronic engineering from the Azad University of Engineering and Technology in 2007 (Arak), and the M.Sc. degree in electrical engineering with a major in electronic from the Razi University in

Kermanshah, Iran, in 2009. His interested areas are artificial neural network, semiconductor, Integrated Circuit Devices and power electronic circuits.

**Teamour Esmaeili** received his B.Sc. Degree in Computer Engineering Software from Shamsi Pour, iran, in 2007 and his M.Sc. Degree in Computer Software from Azad University of Arak, Iran, in 2010. His research interests include Network-On-Chip Architecture, Adhoc network and VANET.

Atena Kazemzadeh received his B.Sc. Degree in Computer Engineering Software from Azad University of Ahvaz, Iran, in 2010. His research interests include, Adhoc network and VANET.