http://dx.doi.org/10.6113/TKPE.2013.18.4.312

# 동기 정류기를 이용한 태양광 모듈용 플라이백 인버터 소프트 스위칭 제어 기법

장진우<sup>1</sup>, 김영호<sup>1</sup>, 최봉연<sup>1</sup>, 정용채<sup>2</sup>, 원충연<sup>†</sup>

Soft Switching Control Method for Photovoltaic AC Module Flyback Inverter using Synchronous Rectifier

Jin-Woo Jang<sup>1</sup>, Young-Ho Kim<sup>1</sup>, Bong-Yeon Choi<sup>1</sup>, Yong-Chae Jung<sup>2</sup>, and Chung-Yuen Won<sup>†</sup>

**Abstract** – In this paper, high efficiency control method for flyback inverter with synchronous rectifier(SR) based on photovoltaic AC modules is proposed. In this control method, the operation of SR is classified according to the voltage spike across main switch S<sub>P</sub>. When the voltage spike across S<sub>P</sub> is lower than the rating voltage of S<sub>P</sub>, the operation of active clamp circuit is interrupted for reducing the switching loss of auxiliary switch. In this time, the SR is operated for soft-switching of S<sub>P</sub>. When the voltage spike across Sp is higher than the rating voltage of S<sub>P</sub>, the operation of active circuit is activated for reducing the voltage spike. The SR is operated for reducing the conduction loss of secondary output diode. Thus, a switching loss of the main switch can be reduced in low power region, and weighted-efficiency can be improved. A theoretical analysis and the design principle of the proposed method are provided. And validity is confirmed through simulation and experimental results.

**Keywords:** voltage spike, synchronous rectifier(SR), soft switching, active clamp circuit, zero voltage switching(ZVS), photovoltaic(PV)

# 1. 서 론

최근 화석 연료의 고갈 및 환경오염에 의해 신재생에너지의 필요성이 부각되고 있다. 태양광 발전은 신재생의 하나로서 무한한 에너지원과 발전 부산물에 의한환경오염이 거의 없기 때문에 활발히 연구되고 있다.

태양광 발전 시스템은 태양 전지의 구조의 따라 Centralized, String, multi-string, 그리고 AC-module 방식 등으로 분류된다. 이 중 AC-module 방식은 각각의 태양 전지 모듈에 인버터가 집적되어 각 모듈이 바로 계통에 연결하여 사용하는 방식이다. AC-module 방식은 값비싼 DC 배전선이 불필요하고 용량 증설이 용이

할 뿐만 아니라 부분 음영에 의한 모듈간의 mismatch 문제에 강인하다는 장점을 갖고 있다. 또한 다른 방식에 비해 단점이 되었던 효율 문제도 극복이 됨에 따라 최 근 중점적으로 연구되고 있다.<sup>[1-3]</sup>

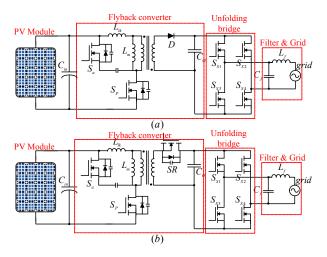

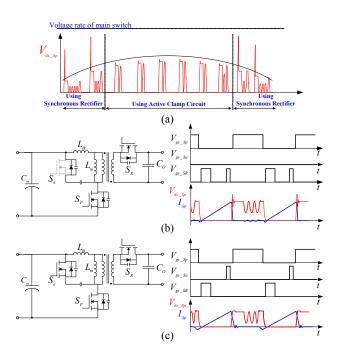

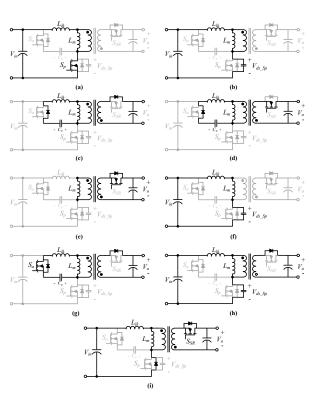

AC module형 topology 중에서 플라이백 타입은 절연형 구조이며 승압이 용이하고 소자 수가 비교적 적기때문에 고효율을 달성하기 유리하여 널리 사용되고 있다. [4-5] 기존의 플라이백 인버터는 그림 1(a)와 같이 PV모듈에서 생성된 에너지를 컨버터부에서 계통에 적합한 직류 전압 및 전류로 변환하고 Unfolding Bridge에서 컨버터의 직류 출력을 계통에 연계 되도록 교류로 변환한다. [6] 여기서 사용된 능동 클램프는 주스위치의 턴-오프 시점에서, 변압기의 누설 인덕터와 주스위치의 기생커패시터 간의 공진 전압 스파이크에 의한 주스위치의고장 및 오작동을 방지하고 소프트 스위칭이 가능하도록 함으로써 효율성과 안정성을 향상시킨다. [7]

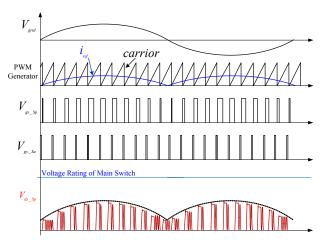

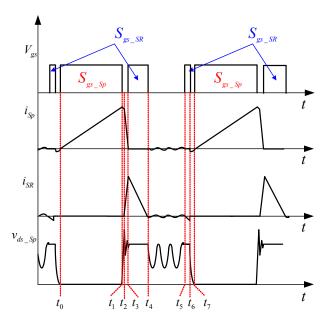

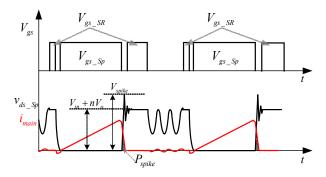

기존의 플라이백 인버터는 그림 2와 같이 능동 클램 프가 계통 주파수 내의 전 영역에서 동작하며 그에 따라 주스위치의 전압 파형이 정격 전압 이하에서 안정하

<sup>+</sup> Paper number: TKPE-2013-18-4-3 ISSN: 1229-2214 Corresponding author: woncy@skku.edu, College of

Information and Communication Eng. Sungkyunkwan Univ. Tel: +82-31-290-7115 Fax: +82-31-290-7179

<sup>&</sup>lt;sup>1</sup> College of Information and Communication Eng. Sungkyunkwan University

<sup>&</sup>lt;sup>2</sup> Dept. of Electronic Eng., Namseoul University Manuscript received Nov. 9, 2012; accepted Mar. 25, 2013 — 본 논문은 2012년 전력전자학술대회 우수추천논문임

게 동작하고 있다. 그러나 주스위치의 공진 전압 스파이 크는 도통하는 전류에 비례하기 때문에 주스위치 턴-온시간이 짧은 구간에서는 능동 클램프를 사용하지 않더라도 공진 전압 스파이크가 주스위치의 정격을 넘지 않는다. 특히 이 구간에서는 주스위치의 소프트 스위칭 효율 이득보다는 능동 클램프 회로의 손실이 크기 때문에능동 클램프를 사용하지 않는 것이 좋다.

동기 정류기는 효율 개선을 위한 방안이 된다. 동기 정류기는 기존의 출력 다이오드보다 도통 손실이 작기때문에 그림 1(b)와 같이 회로를 구성하여 2차 측 전류를 도통 할 경우 효율을 증가시킬 수 있다. 또한 동기정류기는 능동클램프를 대신하여 주스위치의 소프트 스위칭을 가능하게 하기 때문에 앞에서 언급한 능동 클램프를 사용하지 않는 영역에서 생기는 단점을 보완할 수있다. [8-11] 본 논문은 제안된 제어기법을 이론적으로 분석하고 시뮬레이션과 200[W]급 플라이백 인버터 실험장치를 통해서 타당성을 검증하였다.

# 2. 공진 전압 스파이크 분석

주스위치 양단의 전압 크기에 따른 스위치 제어를 하기 위하여 능동 클램프가 동작하지 않을 때의 주스위치의 전압 스파이크 크기 분석이 필요하다. 식 (1)과 같이고 크기는 입출력 전압과 1차 측 첨두치 전류, 그리고 주스위치 양단의 누설 인덕턴스 성분의 제곱근에 비례하고 기생 커패시턴스 성분의 제곱근에 반비례한다.

$$v_{\textit{Sp\_spike}} = v_{in} + \frac{V_{\textit{grid\_P}}}{n} + i_{\textit{pri\_p},\max} \sqrt{\frac{L_{lk}}{C_{oss\_eq}}} \left| \sin \theta \right| \tag{1}$$

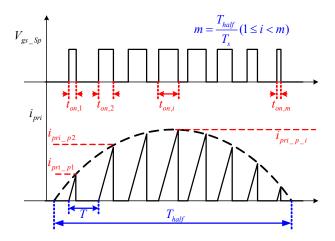

1차측 전류 첨두치 *ipri\_peak\_max*는 그림 3과 같이 계통 주기 내에서 주스위치에 불연속 전류 모드 (Discontinuous Current Mode: DCM)로 톱니파 전류

Fig. 1 (a) Conventional flyback diode rectifier inverter

(b) Proposed flyback synchronous rectifier inverter

가 흐를 때, 피크 전류 중 최대값이며 i번째 피크 전류 는 식 (2)와 같이 나타낼 수 있다.

$$i_{pri_{-}p,i} = \frac{v_{in}}{L_m} t_{on,i}$$

(2)

각각의 피크 전류를 계산하는 것은 복잡하기 때문에 최대 듀티 일 때의 값, 즉 계통 반주기 내 피크 전류의 최대값을 구하고 식 (1)과 같이 그 값을 기준으로 정현 파 형태로 만들어 준다. 최대 피크전류의 값은 다음의식 (3)과 같다.  $D_m$ 은 최대 듀티,  $T_{\text{SW}}$ 는 스위칭 주기이다.

$$i_{pri\_p,\max} = \frac{v_{in}D_mT_{sw}}{L_m} \tag{3}$$

주스위치 양단의 등가 커패시턴스는 식 (4)와 주스위치, 능동클램프 스위치, 동기 스위치의 기생 커패시터 그리고 능동 클램프 커패시터의 직병렬 커패시턴스의합으로 나타낼 수 있다.

Fig. 2 Key switch waveform of conventional inverter

Fig. 3 Gate signal and current waveform of main switch

$$C_{oss\_eq} = C_{oss}^{Sp} + \frac{C_{oss}^{Sa} C_a}{C_{oss}^{Sa} + C_a} + n^2 C_{oss}^{SR}$$

(4)

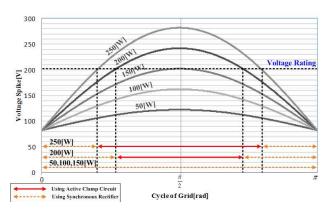

식 (1), (2), (3)을 이용하여 그림 4와 같이 출력 전력에 따른 계통 반주기 내 주스위치의 양단의 전압 스파이크의 크기를 나타낼 수 있다.

# 3. 제안된 제어 기법

#### 3.1 제안된 기법에 대한 알고리즘

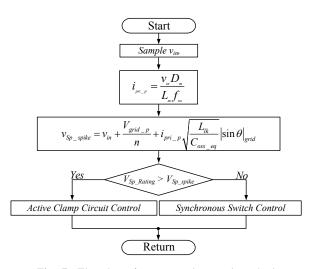

그림 5는 영역 판단을 위한 제안된 기법의 순서도이

Fig. 4 Voltage spike of main switch according to output power of PV Module

다. 먼저 태양 전지의 출력 전압과 계통의 위상을 검출하여 주스위치에 흐르는 최대 첨두치 전류 및 양단의 전압  $V_{Sp\_spike}$ 를 연산한다. 계산된 주스위치의 양단전압을 주스위치의 정격과 비교하여 영역을 판단하고 각 영역에 따른 스위칭 제어를 한다.

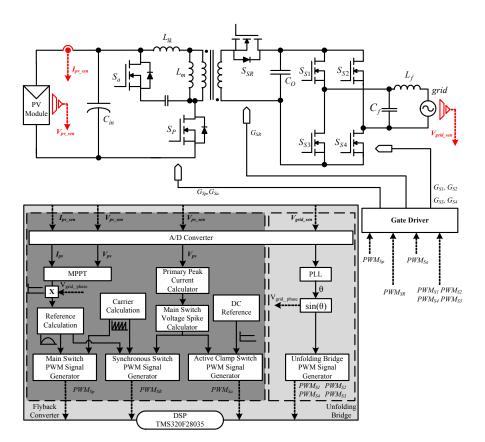

그림 6은 제안된 기법의 제어 블록도로 전체 제어 과정에서 그림 5의 순서도를 실행하기 위해 기존의 제어 블록도에서 최대 첨두치 전류 연산기, 전압 스파이크 계산기, 그리고 동기 스위치 제어기가 추가되었다.

Fig. 5 Flowchart for proposed control method

Fig. 6 Block diagram for proposed control method

따라서 그림 5와 그림 6에서 결정한 각 영역에서, 앞에서 언급한 것과 같이 클램프 회로가 없다고 가정하였을 때, 주스위치 양단의 전압이 주스위치 전압 정격보다큰 경우에는 그림 7(b)와 같이 기존의 능동 클램프를 사용하여 공진 전압 스파이크를 억제한다. 그러나 주스위치 양단의 전압이 주스위치 전압 정격보다 작은 경우에는 그림 7(c)와 같이 공진 전압 스파이크가 있더라도 주스위치의 정격 전압을 넘지 않기 때문에 능동 클램프를 사용하지 않고 동기 정류기의 스위칭 제어를 통하여 주스위치의 ZVS 턴-온을 한다. 따라서 계통 주파수 반주기 내에서 두 영역에 모두 존재한다면 제안된 기법이 적용되었을 경우, 전압 파형은 그림 7(a)와 같이 나타나게 된다.

#### 3.2 동작모드

PV 모듈의 고전력 출력 영역과 저전력 출력 영역에 대한 자세한 동작 모드는 각각 다음과 같다.

# 3.2.1 주스위칭 양단 고전압 영역 동작모드

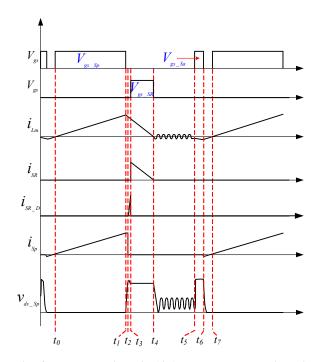

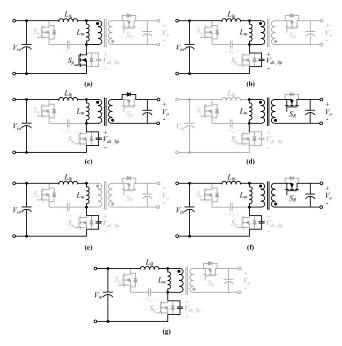

그림 8은 계통 한주기 내에서 주스위치의 전압스파이 크가 주스위치의 정격 전압보다 큰 영역에서의 스위칭 파형 및 주요 소자의 전류 전압 파형이다. 각 모드에 대 한 전류 흐름을 그림 9에 나타내었다.

Model(a)[to-t<sub>1</sub>]: 이 구간에서는 주스위치는 턴-온 되어 있고 보조 스위치와 동기 스위치는 턴-오프 되어 있다. 1차 측 전류는 자화 인덕터를 충전하면서 선형적 으로 증가한다.

$Mode2(b)[t_1-t_2]$  :  $t_1$ 에서 주스위치가 턴-오프 되면서

Fig. 7 Summary of proposed control method

주스위치의 출력 커패시턴스가 자화 인덕터 전류에 의해 충전된다. 주스위치의 출력 커패시터의 전압이 입력 전압과 클램프 커패시터의 전압의 합까지 증가하지만 큰 값의 클램프 커패시터에 의해 공진 전압 스파이크가 억제된다.

Fig. 8 Key waveform in high output power region of PV module

Fig. 9 Operation mode in high output power region of PV module

Mode3-1(c)[t2-t3] : 주스위치의 전압이  $V_{in}+V_{Ca}$ 에 도달하면 능동 클램프 스위치의 역병렬 다이오드로 전류가 흐르면서 누설 인덕터의 전류는 클램프 커패시터에 흡수되고 자화 인턱터에 저장된 에너지가 2차 측으로 동기정류기의 역병렬 다이오드 통하여 전달된다.

Mode3-2(d)[t<sub>2</sub>-t<sub>3</sub>]: 동기 정류기의 역병렬 다이오드의 전류가 흐르는 도중에 동기 정류기가 턴-온이 되면서 ZVS 조건을 만족하고 클램프 커패시터에 흡수되는 누설 인덕터의 전류가 0이 되면 이 모드가 끝난다.

Mode4(e)[t<sub>3</sub>-t<sub>4</sub>]: t<sub>3</sub>이 되면 누설 인덕터 전류가 0이되어 클램프 스위치의 역병렬 다이오드는 턴-오프가 되고 자화 인턱터의 저장된 에너지는 계속 2차 측에 에너지를 전달한다.

Mode5(f)[t₄-t₅]: 자화 인덕터의 전류가 0이 되면 자화 인덕터와 주스위치의 출력 커패시터 간의 공진이 일어난다.

Mode6(g)[t<sub>5</sub>-t<sub>6</sub>]: t<sub>5</sub>에서 클램프 스위치가 턴-온이되면, 충전된 클램프 커패시터의 에너지가 자화 인덕터와 누설 인덕터에 축적되면서 역방향 전류가 흐르고 이역전류는 주스위치의 ZVS를 만족하기 위해 사용된다. 또한 다음의 역전류에 의한 2차 측 전류는 동기 정류기의 역병렬 다이오드를 통해 에너지가 전달된다.

Mode7-1(h)[t<sub>6</sub>-t<sub>7</sub>]: t<sub>6</sub>에서 클램프 스위치가 턴-오 프가 되고 1차 측에 흐르던 역전류는 주스위치의 출력 커패시터를 도통하면서 방전시키고 자화 전류와 역방향 전류의 차이만큼 동기 정류기의 역병렬 다이오드를 통해 2차 측으로 전달된다.

Mode7-2(i)[t<sub>6</sub>-t<sub>7</sub>]: 역방향 전류는 주스위치의 출력 커패시터를 방전시킨 후 역병렬 다이오드를 통해 도통 한다. 이때 주스위치를 턴-온함으로써 ZVS 조건을 만족 시킬 수 있다.

#### 3.2.2 주스위칭 양단 저전압 영역 동작모드

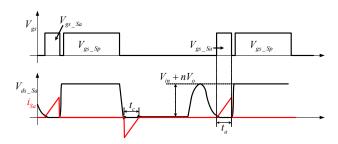

그림 10은 주스위치의 전압스파이크가 주스위치의 정 격 전압보다 작은 영역에서의 스위칭 파형 및 주요 소 자의 전류, 전압 파형이다. 각 모드에 대한 전류 흐름을 그림 11에 나타내었다.

Mode1(a)[t<sub>0</sub>-t<sub>1</sub>]: 주스위치 양단 고전압 영역과 마찬가지로 주스위치가 턴-온 되고 보조 스위치와 동기스위치는 턴-오프 되어 있다. 1차측 전류는 자화 인덕터를 충전하면서 선형적으로 증가한다.

$Mode2(b)[t_1-t_2]$ :  $t_1$ 이 되면 주스위치가 턴-오프 되면서 주스위치 양단에는 입력 전압과 2차 측에서 유도된 전압의 합이 될 때까지 전압이 증가한다.

$Mode3(c)[t_2-t_3]$ : 주스위치의 전압이  $V_{in}+nV_o$ 에 도달하면 자화 인턱터의 전류가 선형적으로 감소면서 저장된 에너지는 2차측 동기정류기의 역병렬 다이오드를 통하여 흐른다. 또한 주스위치에는 누설인덕턴스와 주스위치의 출력 다이오드간의 공진에 의해 전압 스파이크가

나타난다. 전류가 흐르는 도중 동기 정류기가 ZVS 조건을 만족하면서 턴-온이 되고 출력단에 에너지를 전달한다

Mode5(e)[t<sub>4</sub>-t<sub>5</sub>]: 자화 인덕터의 전류가 0이 되면 자화 인덕터와 주스위치의 출력 커패시터간의 공진이 일어난다.

$Mode6(f)[t_5-t_6]$ :  $t_5$ 에서 동기 정류기가 턴-온이 되면 2차 측에 역전류가 선형적으로 증가하면서 자화 인덕터에 충전한다.

Fig. 10 Key waveform in low output power region of PV module

Fig. 11 Operation mode in low output power region of PV module

차 측에서 역방향으로 흐르면서 주스위치의 출력 커패 스위치의 스위칭 및 도통 손실의 합이 된다. 시터를 방전시키면서 ZVS 조건을 만든다.

# 4. 주스위치 양단 저전압 영역 손실 분석

주스위치 양단 저전압 영역에서 각 방법에 따라 발생 하는 손실에 대하여 아래와 같은 방법으로 분석 할 수 있다. 단, 각 기법에서 공통적으로 발생하는 손실은 고 려하지 않는다.

# 4.1 주스위치 양단 저전압 영역에서 능동 클램프로 주스위치를 ZVS 동작시킬 경우의 손실

먼저 능동 클램프가 보조 스위치로서 동작 할 경우에 발생하는 손실은 능동 클램프 스위치의 스위칭 손실  $P_{SW\_Sa}$ , 클램프 스위치의 도통 손실  $P_{COND\_Sa}$ , 그리고 클 램프 스위치의 역병렬 다이오드 도통 손실 PCOND\_Dsr의 합이 된다.

$$P_{ACC} = P_{SW\_Sa} + P_{COND\_Sa} + P_{COND\_Dsr}$$

(5

능동 클램프의 게이트 신호 파형과 전압 전류 파형을 분석을 위하여 그림 12와 같이 다시 개괄적으로 나타내 었다. 전압 파형은 주스위치의 전압 파형이 상하 반전된 형태이고 전류는 그림 9의 모드 3-1과 모드 6에서 능동 클램프 커패시터와 누설 인덕터가 에너지 교환을 하면 서 능동 클램프 스위치 전류가 선형적으로 짧은 시간 증가하며 도통하는 파형이 생긴다. 에너지 평형의 원칙 에 따라 그림 9의 모드 3-1과 모드 6의 전류 증가율 및 도통 시간은 같다고 가정한다. 따라서 스위칭 주기 내에 서 같은 전류에 의해 능동 클램프 스위치와 능동 클램 프 스위치의 역병렬 다이오드에서 각각 한번 씩 도통 손실이 생긴다. 스위칭 손실의 경우, 자화 인덕턴스에 의한 낮은 전압 증가율과 주스위치 게이트 신호간의 데 드타임에 의해 무시할 수 있을 정도로 작다.

# 4.2 주스위치 양단 저전압 영역에서 동기스위치로 주스위치를 ZVS 동작 시킬 경우의 손실

동기 스위치가 동작할 경우에만 발생하는 손실은 (6)

Fig 12 Simplified waveform for conduction loss of active clamp switch

Mode7(g)[t<sub>6</sub>-t<sub>7</sub>]: 자화 인덕터에 충전된 에너지는 1 과 같이 주스위치의 턴-오프 전압 스파이크 손실, 동기

$$P_{ACC\_OFF} = P_{spike\_OFF} + P_{COND\_SR} + P_{SW\_SR}$$

(6)

주스위치의 턴오프 손실은 (7)와 같다.

$$P_{OFF\_Sp} = \frac{1}{2} V_{Sp} I_{peak} f_{SW} t_{off} \tag{7}$$

주스위치의 턴-오프 손실은 턴-오프 시 주스위치의 전압, 전류, 주파수, 턴-오프 시간에 비례한다. 주스위치 의 턴-오프 전압 스파이크 손실은 그림 13과 같이 주스 위치의 전압 스파이크가 발생하면 식(7)의 전압  $V_{Sp}$ 가 커지기 때문에 전압 스파이크가 증가할수록 손실도 커 지게 된다. 그러나 저전압 출력 영역에서는 전압 스파이 크의 크기가 매우 작아 전압 스파이크에 따른 추가 손 실을 무시 할 수 있다. 또한 능동 클램프 동작과 마찬가 지로 스위칭 손실의 경우 낮은 전류 상승률과 데드 타 임에 의해 무시 할 수 있다.

#### 4.3 두 기법의 손실 비교

두 기법에서 무시 할 수 있는 요인과 공통적인 요인 을 제외한 손실을 제외하면 능동 클램프 동작을 할 경 우 능동 클램프 스위치의 역병렬 다이오드 도통 손실만 이 남게 된다. 따라서 주스위치의 전압 스파이크가 주스 위치의 정격을 넘지 않는다면 능동클램프는 사용하지 않는 것이 좋다.

# 5. Design Considerations

주스위치가 ZVS 조건을 만족하기 위한 설계 조건은 다음과 같다. 주스위치가 턴-온 되기 직전, 자화 인덕터 는 주스위치 양단의 등가 커패시터를 방전시켜야 한다. 이를 에너지에 대한 식으로 나타내면 식 (8)와 같다.

$$E_{L}\!\!\left(=\frac{1}{2}\,L_{m}f_{pri}^{2}\right)\!\!>E_{c}\!\!\left(=\frac{1}{2}\,C_{oss\_eq}\,V_{Sp}^{2}\right) \tag{8}$$

Fig. 13 Simplified waveform for oltage spike and turn-off loss of main switch

| Table 1 | Simulation and experimental parameter of |

|---------|------------------------------------------|

|         | proposed interleaved flyback inverter    |

| Parameter                                  | Value                |

|--------------------------------------------|----------------------|

| Input voltage( $V_{in}$ )                  | $25 \sim 40[V_{DC}]$ |

| Output voltage( $V_{out}$ )                | $220[V_{rms}]$       |

| Output power( $P_{out}$ )                  | 200[ W]              |

| Transformer turn ratio( n )                | 6                    |

| Transformer magnetic inductance ( $L_m$ )  | 6.13[ μH ]           |

| Transformer leakage inductance( $L_{lk}$ ) | 0.8[ μΗ ]            |

| C-L filter inductance( $L_f$ )             | 1[ <i>mH</i> ]       |

| Input capacitance $(C_{in})$               | 11[ <i>mF</i> ]      |

| Clamp capacitance ( $C_{active}$ )         | 450[ <i>nF</i> ]     |

| DC-Link capacitance( $C_{out}$ )           | 136[ <i>nF</i> ]     |

| C-L Filter capacitance( $C_f$ )            | 33[ <i>nF</i> ]      |

| Switching frequency( $f_{SW}$ )            | 70[ <i>kHz</i> ]     |

식 (8)에서의 1차 측 전류, 스위치 전압, 그리고 L과 C를 임피던스 성분으로 나타내면 식 (9)-(11)과 같이 나 타낼 수 있다.

$$I_{pri} = I_{Sa} = \frac{I_{SR\_aux}}{n} \tag{9}$$

$$\frac{V_{Sp}}{I_{pri}} = Z = \sqrt{\frac{L_m}{C_{oss\_eq}}} \tag{10}$$

$$V_{Sp} = V_{in} + n V_o \tag{11}$$

식 (8)에 식 (9)-(11)을 대입하여 전류에 대해 정리하면 각 영역에서 주스위치의 ZVS 동작을 위한 동기정류기 및 능동 클램프의 전류의 크기를 식 (12),(13)과 같이계산 할 수 있다.

$$I_{SR} > \frac{n(V_{in} + nV_o)}{Z} \tag{12}$$

$$I_{Sa} > \frac{V_{in} + n V_o}{Z} \tag{13}$$

따라서 식 (12),(13)의 전류 조건을 이용하여 각 스위 치의 턴-온 시간을 식 (14),(15)와 같이 설계할 수 있다.

$$T_{SR} = \frac{L_m I_{SR}}{n^2 V_o} \tag{14}$$

$$T_{Sa} = \frac{L_m I_{Sa}}{n V_o} \tag{15}$$

# 6. 시뮬레이션

제안된 회로의 타당성을 시뮬레이션을 통 위한 제안 된 회로의 주요 파라미터는 표 1과 같다.

#### 6.1 계통 반주기에서의 대한 시뮬레이션 파형

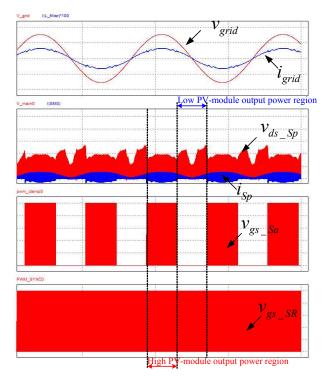

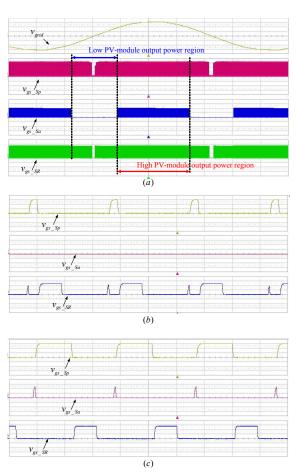

그림 14는 제안된 회로의 시뮬레이션 주요 파형이다. 계통 주기 내에서 능동 클램프의 스위칭 여부에 따라 주스위치 전압 파형이 영역이 나누어지는 것을 확인 할 수 있다

# 6.2 주스위치 양단 저전압 영역에서의 시뮬레이션 파형

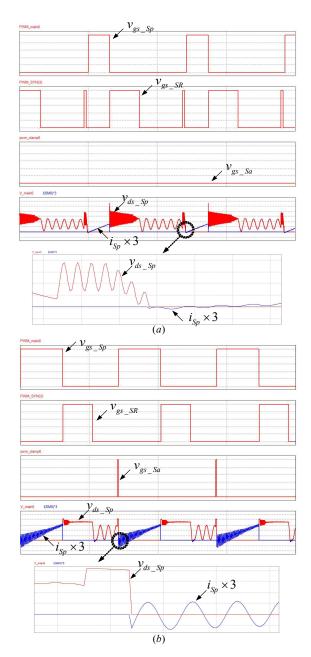

그림 15(a)은 주스위치 양단 저전압 영역에서의 각 스위치에 대한 스위칭 파형과 주스위치의 전압 및 전류파형이다. 이 구간에서는 능동클램프는 스위칭을 하지 않으며 동기 정류기가 주스위치의 ZVS를 위한 스위칭을한다. 마지막 파형은 주스위치가 턴-오프 되는 구간의확대 파형으로 동기 정류기에 의해 ZVS 동작이 되는 것을 확인 할 수 있다.

# 6.3 주스위치 양단 고전압 영역에서의 시뮬레이션 파형

그림 15(b)은 주스위치 양단 고전압 구간에서 각 스위치에 대한 스위칭 파형과 주스위치의 전압 및 전류 파형이다. 이 구간에서는 능동 클램프의 스위칭 파형이

Fig. 14 Key waveform of proposed interleaved flyback inverter

보조 스위치로서 나타나게 된다. 주스위치 양단 저전압 영역과 마찬가지로 마지막 파형에서는 턴-오프 되는 구 간의 확대 파형으로 ZVS 동작이 되는 것을 확인 할 수 있다.

# 7. 실 험

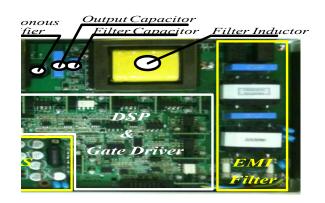

실험은 200[W]급 PV 모듈을 대체한 시뮬레이터로 진행하였으며 그림 16은 제안된 플라이백 인버터의 하드웨어이다.

Fig. 15 Simulation waveform of switches' gate signal, voltage and current across main switch in (a) low output power region of PV module and (b)high output power region of PV module

주요 소자에 대한 각부 명칭을 그림 16에 나타내었다. 실험 소자들의 파라미터는 시뮬레이션과 동일하게 설계 되었으며 각 소자들은 디지털 신호 처리장치(Digital Signal Processor : DSP) TMS320F28035에 의해 제어 된다.

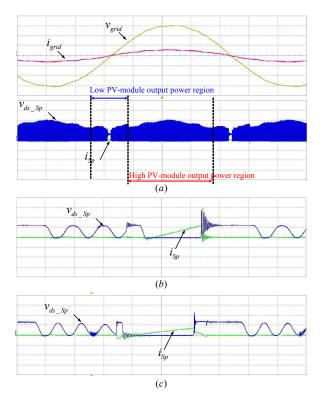

그림 17는 제안된 기법이 적용된 각 스위치의 게이트

Fig. 16 200[W] prototype board of flyback inverter

Fig. 17 Gate signals of main switch, active clamp switch, and synchronous switch in (a)entire region, (b)low output power region of PV module and (c)high output power region of PV module(150[W])

신호 파형이다. 전압 스파이크의 크기를 고려하여 능동 클램프의 스위치가 부분적으로 동작하는 것을 그림 17 (a)에서 확인할 수 있다. 그림 17의 (b)(c)는 각각 PV 모듈의 저전력 출력 영역과 고전력 출력 영역에서의 스위칭 신호의 파형이다.

그림 18은 제안된 기법이 적용된 주스위치의 전압, 전류 파형으로 전압이 능동 클램프 스위치의 스위칭 여부에 따라 영역이 나누어지는 것을 그림 18(a)에서 확인

Fig. 18 Experimental waveform of current and voltage, in (a)entire region, (b)low output power region of PV-module and (c)high output power region of PV-module(150[W])

Fig. 19 Measured efficiency of flyback inverter according to control methods

할 수 있다. 그림 18의 (b)(c)는 각각 주스위치 양단의 저전압 및 고전압 영역에서의 주스위치의 전압 전류 파 형으로 주스위치가 ZVS 턴-온이 되는 것을 실험으로 확인하였다.

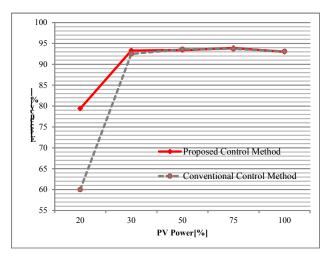

그림 19는 기존 제어 방법과 제안된 제어 방법에 의한 효율 비교 그래프이다. 고전압 출력 영역에서는 효율이 비슷하지만 저전력 영역에서의 효율이 제안된 방법에 의해 개선되어 가중치 효율이 향상됨을 확인 할 수있다.

### 8. 결 론

본 논문은 기존 방식에서 사용되었던 다이오드 정류기를 동기 정류기로 대체하여 도통 손실을 저감하였다. 또한 주스위치 양단의 공진 전압 스파이크가 주스위치의 정격 전압을 넘지 않는 영역에서, 동기 정류기를 이용한 주 스위치의 소프트 스위칭 기법을 제안하였다. 시뮬레이션과 200[W]급 플라이백 실험 장치를 통하여 제시된 기법의 타당성을 확인하였다.

본 연구는 2012년도 산업통상자원부의 재원으로 한국에너지기술평가원(KETEP)의 지원을 받아수행한 연구 과제(No. 20124010203300)입니다.

#### References

- [1] S.B. Kjaer, J.K. Pedersen, and F. Blaabjerg, "A review of single-phase grid-connected inverters for photovoltaic modules," *IEEE Trans. on Ind. Appl.* Vol. 41, No. 5 pp. 1292–1306, Oct. 2005.

- [2] S.B. Kjaer, J.K. Pedersen, and F. Blaabjerg, "Power inverter topologies for photovoltaic modules a review," in Proc. IEEE Trans. on Ind. Appl. Conf., No. 2, pp. 782–788, Oct. 2002.

- [3] Y. Xue, L. Chang, S. B. Kjaer, J. Bordonau, and T. Shimizu, "Topologies of single-phase inverters for small distributed power generators: an overview," *IEEE Trans. on Power Electron,* Vol. 19, No. 5, pp. 1305–1314, Sep. 2004.

- [4] T. Shimizu, K. Wada, and N. Nakamura, "Flyback-type single-phase utility interactive inverter with power pulsation decoupling on the DC input for an AC photovoltaic module system," *IEEE Trans. on Power Electron.*, Vol. 21, No. 5, pp. 1264–1272, Sep. 2006.

- [5] A.Ch. Kyritsis, E. C. Tatakis, and N. P. Papanikolaou, "Optimum design of the current-source flyback inverter for decentralized grid-connected photovoltaic systems," *IEEE Trans. on Energy Convers.*, Vol. 23, No. 1, pp. 281–293, Mar. 2008.

- [6] Y.-H. Kim, J.-G. Kim, Y.-H. Ji, C-Y. Won and T.-W.

- Lee, "A new control strategy of active clamped flyback inverter for a photovoltaic ac module system," in Proc. IEEE 8th Int. Conf. Power Electron. ECCE., pp. 1880–1885, May 2011.

- [7] J. Zhang; X. Huang; X. Wu; and Z. Qian; "A high efficiency flyback converter with new active clamp technique," *IEEE Trans. on*, Vol. 25, No. 7, pp. 1775–1785, July 2010.

- [8] W. Yuan, X.C. Huang, J. M Zhang, Z. M. Qian. "A novel soft switching flyback converter with synchronous rectification," in Proc. IEEE Power Electron. IPEMC 6th Int. Conf., pp. 551–555, May 2009.

- [9] J.-K. Park, Y.-H. Kim, Y.-H. Ji, Y.-C. Jung and C.-Y. Won., "A novel control strategy of an active clamped flyback inverter with synchronous rectifier for a photovoltaic AC module system," in Proc. IEEE Power Electron. ECCE 8th Int. Conf., pp. 401-405, May 2011.

- [10] D. Fu, Y. Liu, F. C Lee and M. Xu, "An improved novel driving scheme of synchronous rectifiers for LLC resonant converter," in Proc. IEEE Appl Power Electron APEC 23th Annu Conf., pp. 510–516, Feb. 2008.

- [11] D. Fu, Y. Liu, F. C Lee and M. Xu, "A novel driving scheme for synchronous rectifiers in LLC resonant converter," *IEEE Trans. Power Electron.*, Vol. 24, No. 5, pp. 1321–1329, May 2009.

- [12] S.-S Hong, S.-K. Ji, Y.-J. Jung, and C.-W. Rho, "Analysis and Design of a High Voltage Flyback Converter with Resonant Elements," *Journal of Power Electronics*, Vol. 10, No. 2, pp. 107–114, Mar. 2010.

- [13] B.-R Lin, C.-C, Chien, "Interleaved Boost-Flyback Converter with Boundary Conduction Mode for Power Factor Correction," *Journal of Power Electronics*, Vol. 12, No. 5, pp. 708–714, Sep. 2012.

- [14] E. Adib, H. Farzanehfard, "Family of Isolated Zero Current Transition PWM Converters," Journal of Power Electronics, Vol. 9, No. 2, pp. 156–163, Mar. 2009.

# 장진우(張鎭宇)

1984년 5월 7일생. 2012년 성균관대 전자 전기공학과 졸업. 2012년~현재 동 대학원 이동통신전력전자공학과 석사과정.

#### 김영호(金榮浩)

1981년 9월 29일생. 2010년 성균관대 대학원 태양광 시스템 협동과정 석사과정 졸업. 2010년~현재 동 대학원 태양광 시스템 협동과정 박사과정.

#### <u>최봉연(崔棒然)</u>

1987년 11월 16일생. 2012년 한양대 전자 컴퓨터공학부 졸업. 2012년~현재 성균관 대 대학원 전자전기컴퓨터공학부 석박통합 과정.

# 정용채(鄭龍采)

1966년 2월 28일생. 1989년 한양대 전자공학과 졸업. 1991년 한국과학기술원 전기 및 전자공학과 졸업(석사). 1995년 한국과학기술원 전기 및 전자공학과 졸업(공박). 1995년~1999년 LG 전자 홈어플라이언스 연구

소 선임연구원. 1999년~현재 남서울대 전자공학과 부교수. 당학회 편집이사.

# 원충연(元忠淵)

1955년 5월 10일생. 1978년 성균관대 공대 전기공학과 졸업. 1980년 서울대 공대 대학 원 전기공학과 졸업(석사). 1987년 서울대 공대 대학원 전기공학과 졸업(공박). 1991년 12월~1992년 12월 미국 테네시 주립대학

전기공학과 방문 교수. 1998년~현재 한국철도기술연구원 심사위원. 2006년~2009년 한국전력공사 PQ 심사위원. 2006년~2009년 차세대 첨단도시철도시스템(한국건설교통기술 평가원)기술개발사업 운영위원. 2006년~현재 ㈜로템 기술자문위원. 2010년~2012년 도시철도 공사 기술검증위원. 2007년~현재 삼성전기 에너지파워 연구센터장. 2011년~2013년 직류표준화 연구회 회장. 2010년 당 학회 회장. 현재 성균관대 정보통신대학교수.