## 특집: 전자패키지 및 자동차 전장품 접합기술

# 3차원 패키징을 위한 TSV의 다양한 Cu 충전 기술

노명훈\*・이준형\*・김원중\*, · 정재필\*・김형태\*\*

\*서울시립대학교 공과대학 신소재공학과

\*\*(주)아프로 알앤디

## Various Cu Filling Methods of TSV for Three Dimensional Packaging

Myong-Hoon Roh\*, Jun-Hyeong Lee\*, Wonjoong Kim\*,†, Jae Pil Jung\*, and Hyeong-Tea Kim\*\*

\*Department of Materials Science and Engineering, University of Seoul, Seoul 130-743, Korea

\*\*APRO R&D, Seoul 152-769, Korea

<sup>†</sup>Corresponding author: wjkim@uos.ac.kr

#### A bstract

Through-silicon-via (TSV) is a major technology in microelectronics for three dimensional high density packaging. The 3-dimensional TSV technology is applied to CMOS sensors, MEMS, HB-LED modules, stacked memories, power and analog, SIP and so on which can be employed to car electronics. The copper electroplating is widely used in the TSV filling process. In this paper, the various Cu filling methods using the control of the plating process were described in detail including recent studies. Via filling behavior by each method was also introduced.

Key Words: Three dimensional packaging, TSV, Cu electroplating, Functional layer

## 1. 서 론

3차원 패키징을 위한 TSV(through silicon via)는 전자부품의 소형화, 빠른 신호전달, 고집적도 및 스마 트한 기능에 대한 요구를 충족시킬 수 있는 기술이다. TSV는 실리콘 웨이퍼를 관통하는 미세 홀(via)을 형성 한 후 홀 내부에 전도성 물질(conductive materials) 을 충전시켜 칩 내부에 직접 전기적 연결 통로를 확보 하는 기술이다. 또한, 칩 내부에 직접 연결 통로가 확 보되기 때문에 다수의 칩을 수직으로 적층할 때 기존의 와이어 본딩을 이용한 3차원 패키징에서의 I/O 수의 제한, 단락 접촉 불량과 같은 문제점을 해결할 수 있다<sup>1)</sup>. TSV 기술은 CMOS sensors, MEMS, HB-LED modules, stacked memories, power and analog, SIP 등 고밀도 첨단 전자 패키징 분야에 이용되고 있 는데, 이러한 부품들은 자동차용 카메라 등 고밀도 자 동차 전장품에도 적용될 수 있다. 자동차 전장품은 여 러 가지 기술이 집적되어 있을 때 효과적이고 모듈화가 진행되고 있기 때문에, 자동차용 시스템 반도체 기술이 연구되고 있다.

TSV를 이용한 3차원 패키징을 위해서는 웨이퍼에 비아홀을 형성하는 기술<sup>2)</sup>, 기능성 박막층을 형성하는 기술<sup>3)</sup>, 전도성 물질을 충전하는 기술<sup>4)</sup>, 웨이퍼 연마 기술<sup>5)</sup>, 칩 적층 기술<sup>6,7)</sup> TSV 신뢰성 해석<sup>8)</sup> 등 다양한 기술들이 요구된다. 이러한 기술 중에서 비아홀에 전도 성 물질을 충전하는 기술은 결함 없는 충전을 위해서 상업적인 공정 시간이 길게는 10시간 이상 소요될 뿐만 아니라, 전체 공정 비용 중 약 26~40%를 차지한 다<sup>4,9)</sup>. 따라서 TSV의 상용화를 위해서 전도성 물질의 고속 충전은 매우 긴요한 분야이다.

TSV를 충전하는 전도성 금속으로는 Cu가 대표적으로 사용된다<sup>4-9)</sup>. Cu는 전기전도도가 Ag 다음으로 우수할 뿐만 아니라, 가격이 저렴하기 때문에 TSV 상용화를 위한 충전 금속으로 가장 많이 연구되고 있다. 전해도금은 TSV에 Cu를 충전할 때 가장 널리 사용되는 방법으로 공정비용이 비교적 저렴하고 양산이 용이하다

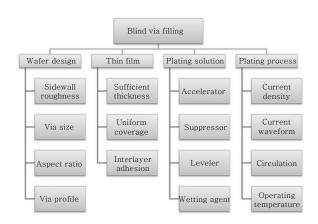

**Fig. 1** Summary of influence factors of electroplating based via-filling <sup>11)</sup>

10.11). 전해도금을 이용하여 TSV에 Cu를 충전할 때 영향을 미치는 변수들은 그림 1에 보인 것과 같이 웨이퍼의 디자인 (홀 크기, 종횡비 등), 기능성 박막 (두께, 균일 도포성 등), 도금액 (가속제, 억제제, 평활제 등), 도금공정 (전류밀도, 전류파형, 도금액 교반, 도금온도) 등이 있다<sup>11)</sup>.

본고에서는 TSV 충전에서의 다양한 변수들 중 기능성 박막과 도금공정에 의한 Cu 전해 도금을 자세히 소개하고자 한다.

#### 2. TSV의 Cu 전해도금을 위한 기능성 박막

기능박막(functional layer)이란 홀과 홀이 형성되지 않은 실리콘 웨이퍼 사이에 다음과 같은 목적을 위해 형성된다.

- ① 홀과 실리콘 웨이퍼의 전기적 절연, 절연층(insulating layer; 이산화규소(SiO<sub>2</sub>) 질화규소(SiN))

- ② 홀 내부 충전 금속과 실리콘 웨이퍼 사이의 접합력 확보, 접합층(adhesion layer; 티타늄(Ti))

- ③ 충전 금속의 전해도금을 용이하게 하기위한 전처리, 시드층(seed layer; 구리(Cu), 금(Au))

일반적으로 기능성 박막 증착에서 이산화규소/티타늄/ 구리와 같은 구조가 사용된다<sup>12,13)</sup>. 절연층으로 형성되 는 이산화규소의 경우 실레인(SiH<sub>4</sub>)을 이용하여 화학 기상 증착법(CVD: chemical vapor deposition)으로 증착하는 것이 일반적이다.

접합층은 절연층과 충전 금속인 구리의 접합력을 향상시키기 위해 절연층 및 충전 금속 양쪽과 접합성이 모두 좋은 티타늄을 이용하여 박막을 형성한다. 시드층은 충전 금속인 구리의 전해도금을 용이하게 하기 위해

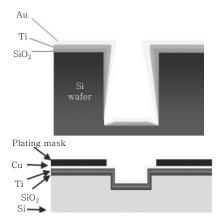

Fig. 2 Schematic of functional layer

형성된다. 주로 동종의 구리 박막이 입혀지는 경우가 대부분이나<sup>11)</sup> 시드층은 구리 대신에 금을 사용할 수 있다<sup>14)</sup>. 이는 산화방지 및 도금액 내에서의 화학적 안정성을 고려할 경우, 금의 특성이 구리에 비해 우수하기때문이다. 티타늄/구리 또는 티타늄/금과 같은 금속박막 형성은 스퍼터링(sputtering)을 이용하여 형성되는 것이 보통이다. 그림 2 기능박막이 홀 내에 형성된 구조의 예를 나타낸다.

### 3. 도금 공정 변수 조절에 의한 전해도금

도금 공전 변수 조절을 이용하여 TSV에 Cu를 전해 도금 할 때, TSV의 충전 거동은 전류인가 방법에 영향을 받는다. 특히, Cu 도금층의 특성은 전류밀도와 매우 밀접한 관계가 있다. 일반적으로 낮은 전류밀도로 Cu를 도금할 경우 균일한 도금층 형성이 용이하여 결함없는 충전이 가능하나 도금속도가 느려 충전시간이 오래 걸리는 단점이 있다. 이와 반대로 높은 전류밀도를 사용하면 도금 속도가 증가하여 충전시간을 단축 할 수 있으나, TSV 입구가 우선적으로 막혀 결함을 야기하다

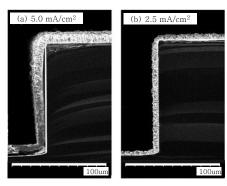

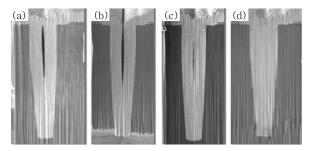

TSV에 Cu를 충전하는 전류인가 방법으로 직류전류 (direct current, DC)<sup>15)</sup>, 펄스 전류(pulse current, PC)<sup>16)</sup>, 펄스-역펄스 전류(pulse reverse current, PRC)<sup>17)</sup>, 주기적인 펄스-역펄스 전류(periodic pulse reverse current, PPR)<sup>18,19)</sup> 등이 연구되고 있다. 일 반적으로 DC 방법은 유기첨가제가 최적화된 도금액에서 많이 사용된다. 비록 유기첨가제를 최적화하였지만, TSV 충전은 전류밀도의 영향을 받는다. 그림 3에 유기첨가제가 첨가된 도금액을 이용하여 전해도금할 때 전류밀도 차이에 따른 TSV의 충전 거동을 나타내었다<sup>15)</sup>. 그림 3(a)에 보이는 것과 같이 전류밀도를 5.0mA/cm²

Fig. 3 Trench filling SEM images at crrent density (a) 5.0 and (b) 2.5  $\rm mA/cm^2$   $^{15)}$

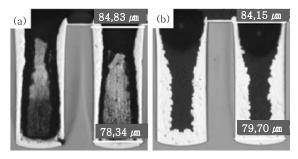

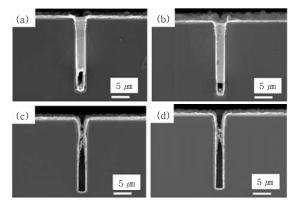

**Fig. 4** Opticla microscopic views of via fillings realized by the pulsed current with fixed  $I_{\rm on}=1$  A/dm²,  $t_{\rm on}=0.05~{\rm s}$  but a varying break  $t_{\rm off}$  which is set to 50 ms (a) and 300 ms (b). The results are obtained for the same plating charge  $^{16)}$

인가하였을 때, TSV 입구 부분과 바닥부분의 도금두께의 차이를 확인 할 수 있다. 이러한 비균일한 도금은 종국에 TSV내에 기공을 형성시킨다. 반면에 전류밀도를  $2.5 \text{mA/cm}^2$  인가한 경우 그림 3(b)에 보인 것과 같이 TSV내에 균일한 도금층이 형성되었다.

낮은 전류밀도의 DC 방법을 이용하여 TSV를 충전할 경우 충전시간이 오래 걸릴 뿐만 아니라 종횡비가 큰 TSV의 경우는 결함을 발생할 수 있다. 이러한 DC의 단점을 보완하기 위하여 높은 전류밀도 인가가 가능한 PC, PRC 방법 등이 고안되었다<sup>16,17)</sup>. PC 방법은 전류 인가 후 일정시간 동안 전류를 인가하지 않는 시간을 두어 전류인가/전류오프를 반복하는 방법이다. 이방법은 전류인가 시간동안 고갈된 Cu 이온이 전류오프시간동안 TSV 내부로 확산할 수 있도록 유도한다. PC 방법에서 전류오프 시간은 중요한 변수로써 그림 4에보인 것과 같이 전류 오프 시간에 따라 TSV의 충전 거동이 다르게 나타난다<sup>16)</sup>.

PRC 방법은 정방향(환원) 전류와 역방향(산화) 전류를 주기적으로 인가하여 Cu의 전착과 식각을 반복되

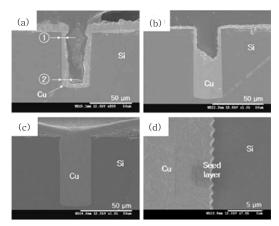

**Fig. 5** Effect of waveform on via filling (a) DC, (b) RC, (c) and (d) PRC with different reverse current 17)

도록 하는 것이다. PRC 방법은 TSV의 입구 모서리부분의 전류 집중을 역으로 이용한 것으로써 역펄스 기간에 모서리에 높은 산화 전류밀도가 인가되어 도금층을 식각하여 TSV 입구의 개방을 유지 할 수 있게 한다. 동일한 도금액의 조성에서 DC, PC, PRC의 방법에 따라 TSV가 충전되는 거동은 다르게 나타날 뿐만아니라, PRC의 파형 종류도 TSV 충전에 영향을 주며, 전류인가 방법에 의한 다양한 충전 거동을 그림 5에 보였다<sup>17)</sup>

PPR 방법은 PRC 방법에서 역방향 전류 인가 후 일 정시간 전류오프 시간을 두는 것을 반복하는 것이다<sup>18)</sup>. PPR 방법은 유기첨가제가 야기할 수 있는 도금액의 수 명감소와 공정 중에 유기 첨가제가 분해되어 전자제품의 신뢰성을 악화시킬 수도 있는 문제를 해결하기 위해도금액에 유기첨가제를 최소화하기 위하여 고안되었다. PPR 방법은 정방향/역방향 전류의 크기와 시간 및 전류오프 시간을 모두 조절해야하기 때문에 최적의 공정조건을 찾는 것이 다른 전류인가 방법들에 비해 복잡하다. 그림 6은 정방향/역방향 전류밀도와 정방향 전류인가 시간을 고정한 후, 역방향 전류인가 시간과 전류오

$\label{eq:Fig. 6} \begin{array}{lll} \textbf{Fig. 6} & \text{SEM images of 20} \; \mu\!\text{m} \; \text{deep TSV plated with} \\ & \text{different PPR parameter sets: (a)} \; \; t_R{=}2, \\ & t_{\text{off}}{=}20, \; \text{(b)} \; \; t_R{=}2, \; t_{\text{off}}{=}0, \; \text{(c)} \; \; t_R{=}1, \; t_{\text{off}}{=}20, \\ & \text{and (d)} \; \; t_R{=}1, \; t_{\text{off}}{=}0^{18)} \end{array}$

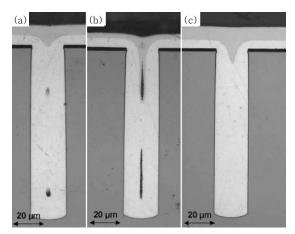

Fig. 7 Cu fillin into TSV by 3-step PPR: (a) 1st step, (b) 2nd step, (c) 3rd step, and (d) interface between via wall<sup>19)</sup>

프 시간을 조절하여 TSV 충전을 나타낸 것이다<sup>18)</sup>. 그림 6에 보인 것과 같이 각각의 PPR 조건에 따라 Cu의 충전거동이 다르게 나타난 것을 알 수 있다.

PPR 방법은 역방향 전류인가와 전류오프 시간으로 인해 다른 전류인가 방법들보다 공정 시간이 길어질 수 있는 단점이 있다. 이러한 PPR 방법의 단점을 보완하기 위해 PPR 방법을 단계적으로 적용하는 3단계 PPR 방법이 연구되었다<sup>19)</sup>. 3단계 PPR 방법은 1단계에서 낮은 평균전류밀도의 PPR을 인가하여 TSV에 균일한 도금층을 형성한다. 2단계에서는 중간 크기의 평균전류밀도의 PPR을 인가하여 TSV의 초등각 도금을 유도한후, 3단계에서 높은 평균 전류밀도의 PPR을 인가하여 TSV를 완전히 충전한다. 그림 7은 3단계 PPR 방법은 이용하여 충전한 TSV의 단계별 거동을 보인 것이다<sup>19)</sup>. 3단계 PPR 방법은 1단계에서 상대적으로 장시간 소요된 공정시간을 2단계와 3단계에서 만회가 가능하기 때문에 기존의 PPR 방법에서 발생할 수 있는 공정시간이길어질 수 있는 문제를 해결할 수 있다.

TSV에 전해도금으로 Cu를 충전하기 위해 사용되는 기본 도금액은 황산 용액과 황산구리로 구성되며, 도금 층의 특성을 조절하기 위하여 유기첨가제를 첨가한다. 기본 도금액에서 분자량이 작은 유기첨가제는 TSV 내부의 형상효과에 의해서 제어된다. TSV 내부의 형상효과는 IBM에서 연구되었는데, 이 유기첨가제는 TSV 내부로 침투하여 벽에서부터 Cu 도금이 진행되어 홀의단면적이 작아지는 Cu의 형상변화 때문에 상대적으로 농도가 높게 되어 바닥부터 충전이 진행된다. 큰 분자량을 갖고 있는 유기첨가제는 도금되는 웨이퍼 및 TSV의 확산현상에 의해 제어된다. 도금이 진행되는 동안도금액은 충분히 교반되기 때문에 웨이퍼 표면에는 확

**Fig. 8** Cu electrodeposition in  $100 \times 20 \mu m$  TSV : (a)  $25 \text{ g/L Cu}^{2+}$ , (b)  $75 \text{ g/L Cu}^{2+}$ , (c)  $50 \text{ g/L Cu}^{2+}$  21)

산층이 얇게 형성되고, 이로 인해 유기첨가제의 확산이용이하여 농도가 높게 유지된다. 반면에 TSV 내부 오목한 부분에는 상대적으로 교반이 약하기 때문에 확산층이 두꺼워져 첨가제의 농도가 낮게 유지된다. 따라서, TSV 내부는 도금이 촉진되고, 웨이퍼 표면에서는 도금이 억제된다. 또한, TSV에 Cu를 전해도금할 때, 도금액내에서 양전하로 존재하여 주로 음극에 위치하는 유기첨가제를 첨가하기도 한다. 이 첨가제는 음극의 오목한 부분보다는 볼록한 부분이나 TSV의 입구 모서리 같은 곳에 많이 존재하여 도금을 방해함으로써 전체적으로 균일한 도금층을 형성시키는 역할을 한다<sup>20)</sup>.

도금액의 Cu 이온 농도와 유기첨가제의 조성은 매우 밀접한 관계를 갖고 있다. 유기첨가제의 조성을 일정하게 유지한 후 Cu 이온 농도를 변화시키면서 TSV를 전해도금한 결과를 그림 8에 나타내었다<sup>21)</sup>. 그림 8에 보인 것과 같이 Cu 이온의 농도가 25 g/L일 때 TSV 내부에 기공이 형성되었으며, Cu 이온 농도가 75 g/L일 때는 시임(seem)이 발행하였다. 반면에 Cu 이온 농도가 50 g/L일 때 결함없이 충전되어 유기첨가제의 조성이 일정하여도 Cu 이온의 농도 변화에 따라 TSV의 충전 거동이 달라지는 것을 알 수 있었다.

지금까지 TSV에 Cu를 충전할 때 중요한 변수인 기능성박막과 도금 공정 변수에 대해 소개하였다. DC, PC, PRC 전류인가 방법을 이용하여 Cu를 전해도금할 경우 유기첨가제의 조성이 중요한 변수로 작용하며, 유기첨가제를 최소화한 TSV 충전에서는 PPR, 3단계 PPR과 같은 도금 공정 조건이 중요한 변수로 작용하였다. TSV를 상용화하기 위해서 유기첨가제를 첨가하지않고 Cu를 전해도금하는 것은 한계가 있기 때문에, 최소의 유기첨가제와 도금 공정 최적화를 통해 더욱 건전하고 고속의 Cu 충전이 가능할 것으로 기대한다.

## 4. 결 론

3차원 패키징을 위한 TSV 기술에서 비아 홀을 충전할 때 사용하는 다양한 Cu 전해도금법에 대해서 소개하였다. 반도체 공정에서 보편화된 전해도금을 이용한 Cu 충전은 적절한 기능성 박막과 유기첨가제의 조합 및 전류인가 방법과 같은 도금 공정 조절을 통해 공정시간 단축과 비용 절감이 가능할 것으로 기대된다. 본고를 통하여 향후 상용화될 TSV의 Cu 충전 기술에 대한 이해와 응용에 다소나마 도움이 되기를 바란다.

### 감사의 글

본 논문은 중소기업청 2012년도 산학연공동기술개발 산업(No.C0016669)과 서울시립대학교 2005년도 학 술연구용첨단장비 초고온 가공 및 강도측정장비 구매 지원으로 수행되었습니다.

## 참 고 문 헌

- M. Motoyoshi : Through-silicon via (TSV), Proceedings of IEEE, 97-1 (2009), 43-48

- X. Zhang, T.C. Chai, J.H. Lau, C.S. Selvanayagam, K. Biswas, S. Liu, D. Pinjala, (...), C.J. Vath III: Development of through silicon via (TSV) interposer technology for large die (21x21mm) fine-pitch Cu/low-k FCBGA package, Proceedings - Electronic Components and Technology Conference, (2009), 305-312

- J.A.T. Norman, M. Perez, S.E. Schulz, T. Waechtler

New precursors for CVD copper metallization, Microelectron. Eng., 85-100 (2008) 2159-2163

- M.J. Wolf, T. Dretschkow, B. Wunderle, N. Jűrgensen, G. Engelmann, O. Ehrmann, A. Uhlig, (...), H. Reichl

High aspect ratio TSV copper filling with different seed layers, Proceedings Electronic Components and Technology Conference, (2008) 563-570

- T.C. Tsai, W.C. Tsao, W. Lin, C.L. Hsu, C.L. Lin, C.M. Hsu, J.F. Lin, C.C. Huang, J.Y. Wu, CMP process development for the via-middle 3D TSV applications at 28nm technology node, Microelectronic Engineering, 92 (2012) 29-33

- S.J. Hong, J.H. Jung, J.P. Jung, M. Mayer, Y.N. Zhou: Sn bumping without photoresist mould and Si dice stacking for 3-D packaging, IEEE Transactions on Advanced Packaging, 33-4 (2010), 912-917

- S.C. Hong, W.G. Lee, J.K. Park, W.J. Kim, and J.P. Kim: Cu filling into TSV and non-PR Sn bumping for 3 dimension chip packaging, Journal of KWJS, 29-1 (2011) 9-13 (in Korean)

- 8. S.H. Choa and C.G. Song: Thermo-mechanical reliability analysis of copper TSV, Journal of KWJS, **29-1** (2011) 46-51 (in Korean)

- 9. H. Y. Li, E. Liao, X. F. Pang, H. Yu, X. X. Yu, J.

- Y. Sun, "Fast Electroplating TSV Process Development for the Via-Last Approach", 2010 Electronic Components and Technology Conference, (2010), 777-780

- D. Malta, C. Gregory, D. Temple, T. Knutson, C. Wang, T. Richardson, Y. Zhang, R. Rhoades: Integrated process for defect-free copper plating and chemical-mechanical polishing of through-silicon vias for 3D interconnects, Proceedings Electronic Components and Technology Conference (2010), 1769-1775

- K.Y.K. Tsui, S.K. Yau, V.C.K. Leung, P. Sun, D.X.Q. Shi: Parametric Study of Electroplatingbased Via-filling Process for TSV Applications, Int'l Conf. on Electron. Pack. Tech & High Dens. Pack. (ICEPT-HDP), (2009), 23-27

- T. Kenji, T. Hiroshi, T. Yoshihiro, Y. Yasuhiro, H. Masataka, S. Tomotoshi, M. Tadahiro, S. Masahiro, B. Manabu : Current status of research and development for three-dimensional chip stack technology, J. Appl. Phys. 40 (2001), 3032-3037

- 13. S.W.R. Lee, R. Ho, S.X.D. Zhang, C. K. Wong: 3D stacked flip chip packaging with through silicon vias and copper plating or conductive adhesive filling, Proceed. Elec. Pack. Tech. Conf., (2005) 795–801

- 14. B.H. Kim, H.C. Kim, K.J. Chun, J.H. KI, Y.S. Tak: Cantilevert-type microelectromechanical systems probe card with throunds-wafer interconnects for fine pitch and high-speed testing, Jpn. J. Applied Physics 43(6B) (2004) 3877

- 15. E.H. Choi, Y.S. Lee, and S.K. Rha: Effects of current density and organic additives on via copper electroplating for 3D packaging, Kor. J. Mater Res., **22-7** (2012), 374-378

- 16. C. Fang, A.L. Corre, and D. Yon: Copper electroplating into deep microvias for the "SiP" application, Microelectronic Engineering 88 (2011), 749-753

- 17. R. Beica, C. Sharbono, and T. Ritzdorf: Through silicon via copper electrodeposition for 3D integration, Electronic components and technology conference, IEEE (2008), 577-583

- 18. L. Hofmann, R. Ecke, S.D. Schulz, and T. Gessner : Investigations regarding Through Silicon Via filling for 3D integration by Periodic Pulse Reverse plating with and without additives, Microelectronic Engineering 88 (2011), 705-708

- 19. S.C. Hong, W.G. Lee, W.J. Kim, J.H. Kim, and J.P. Jung: Reduction of defects in TSV filled with Cu by high-speed 3-step PPR for 3D Si chip stacking, Microelectronics Reliability, 51 (2011) 2228-2235

- Q. Li, H. Ling, H. Cao, Z. Bian, M. Li, and D. Mao

Through silicon via filling by copper electroplating in acidic cupric methanesulfonate bath, International conference on electronic packaging technology & High density packaging (ICEPT-HDP), IEEE, (2009), 68-72

- T.H. Tsai and J.H. Juang : Electrochemical investigations for copper electrodeposition of throughsilicon via, Microelectronic Engineering 88 (2011), 195-199

- 노명훈

- 1980년생

- 서울시립대학교 박사과정

- 3D 패키징, 전해도금

- e-mail : mhroh@uos.ac.kr

- 이준형

- 1987년생

- 서울시립대학교 석사과정

- 전자패키징, 전해도금

- e-mail : leewnsgud@naver.com

- 김원중

- 1956년생

- 서울시립대학교 교수

- 금속 가공, 미세조직 분석

- e-mail : wjkim@uos.ac.kr

- 정재필

- 1959년생

- 서울시립대학교 교수

- 마이크로접합, 전재패키징, 전해도금

- $\bullet$  e-mail : jpjung@uos.ac.kr

- 김형태

- 1968년생

- (주)아프로 R&D 대표이사

- 습식·건식 표면처리, 신뢰성

- e-mail : htkim@apro.re.kr