# 멀티레벨 인버터의 순간정전 보상알고리즘에 관한 연구

(Voltage Dip Compensation Algorithm Using Multi-Level Inverter)

윤흥민\*·김 용\*\*

(Hong-Min Yun · Yong Kim)

#### **Abstract**

Cascaded H-Bridge multi-level inverters can be implemented through the series connection of single-phase modular power bridges. In recent years, multi-level inverters are becoming increasingly popular for high power applications due to its improved harmonic profile and increased power ratings. This paper presents a control method for balancing the dc-link voltage and ride-through enhancement, a modified pulse width-modulation Compensation algorithm of cascaded H-bridge multi-level inverters. During an under-voltage protection mechanism, causing the system to shut down within a few milliseconds after a power interruption in the main input sources. When a power interruption occurs finish, if the system is a large inertia restarting the load a long time is required. This paper suggests modifications in the control algorithm in order to improve the sag ride-through performance of ac inverter. The new proposed strategy recommends maintaining the DC-link voltage constant at the nominal value during a sag period, experimental results are presented.

Key Words: Multilevel Inverters, SAG, Ride-Through Compensation Algorithm

- \* 주저자: LS산전 자동화제품연구소 책임연구원

- \*\* 교신저자 : 동국대학교(서울) 전자전기공학부 교수

- \* Main author: Senior Research Engineer Automation R&D Center, LSIS Corporation, Ltd

- \*\* Corresponding author: Professor, Division of Electronics and Electrical Engineering, Dongguk University

Tel: 031-450-7583, Fax: 031-453-6263

E-mail: hmyuna@lsis.biz 접수일자: 2013년 10월 10일 1차심사: 2013년 10월 12일 심사완료: 2013년 11월 6일

## 1. 서 론

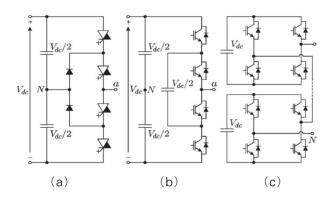

고전압, 대용량 부하에 사용되는 고압 인버터의 경우 전압변환용 Up/Down 입/출력 변압기를 사용하거나 SCR(Silicon Controlled Rectifier) 또는 GTO(Gate Turn-off Thyristor) 소자를 이용한 전류형 인버터를 이용하는 방식이 제안되었다[1]. 하지만 고전압 출력을 위해서 일반적으로 스위칭 소자의 직렬연결 방식을 채택하였으나 소자 각각의 특성 상이로 소자들의 스위칭 온・오프 시점을 정확히 일치해야 하는 문제점을 지니고 있다[1-2]. 그림 1은 고압 인버터를 위한 멀티레벨 인버터 토폴로지를 나타낸다. 그림 1 (a)의

NPC(Neutral Point Clamped) 인버터 방식은 다이오 드를 통하여 스위칭 소자에 걸리는 전압을 클램프하 여 소자의 전압 분배가 일정하도록 하는 방식이지 만, 클램핑 다이오드에 걸리는 전압 스트레스가 일 정치 않고 직류단 커패시터의 전압 밸런스가 불균형 한 단점이 존재하며[3], 그림 1 (b)의 플라잉 커패시 터 인버터 방식은 직류단 커패시터의 전압 밸런스가 균일해지는 특징도 있지만, 환류다이오드가 존재하 지 않으므로, 전류순환이 원활하지 않는 단점이 여 전히 존재하고 있다[3]. 따라서 스위치를 직렬로 연 결하는 그림 1 (a), (b)의 문제점을 해결하고, 고전압 출력에 적합하는 방식으로 그림 1 (c)와 같이 단상 H 형태의 셀을 직렬로 연결하는 Cascaded 방식이 제안되었다[4]. 이러한 Cascaded 방식은 각 커패시 터 사이에 전압 불균형 문제가 없으며, 전압 균형을 위한 별도의 소자가 필요 없고, 출력전압 레벨 수 증 가에도 제약이 없다는 장점을 가지고 있어서, 현재 고전압 인버터 토폴로지에 가장 중점적으로 연구가 진행되고 있다[4].

그림 1. 일반적인 멀티레벨 인버터 토폴로지 Fig. 1. General multilevel converter topologies

그림 1 (c)와 같은 Cascaded 방식의 고전압 인버터는 순간 정전이 발생하게 되면, 각 셀 인버터의 직류단전압이 급격하게 낮아지게 되고 수십 msec 안에 저전압 트립(Low Voltage Trip)이 발생하여 시스템 출력이 차단되는 문제가 제기되고 있다[5]. 또한 고전압Cascaded 방식의 인버터에서 순간 정전에 대한 복구를 위해서 전동기를 완전하게 정지하고 정상 속도로

가속하는 방식은 전동기의 관성이 크므로 시간이 오래 걸리는 문제점이 있으며[5-7], 순간정전 상태에서 전동기의 실제 회전속도를 감지하지 못하고, 인버터를 재기동하는 경우 순간적으로 과전류가 발생하는 문제점이 존재한다[5-7].

따라서 본 연구에서는 고전압 Cascaded 방식의 인 버터에서 순간정전 보상을 위해서 분산제어를 이용한 새로운 순간정전 보상알고리즘을 제안하고자 한다. 제안된 제어방식은 각 셀 제어기는 직류전압과, 부하추정을 담당하고, 마스터 제어기는 속도추정기 및 헌팅보상을 수행하여 순간 정전 발생시 인버터 출력 전류의 급격한 변화를 억제하는 역할을 수행하고 있다. 이를 통하여 순간정전시 각 커패시터에 전압 균형을 수행하고, 순간정전 시간이 100msec 이상에서도 안정적으로 순간전압강하 보상을 수행하는 알고리즘을 제시하고 이를 실험적으로 확인하고자 한다.

## 2. 본 론

#### 2.1 캐스케이드 멀티레벨 인버터

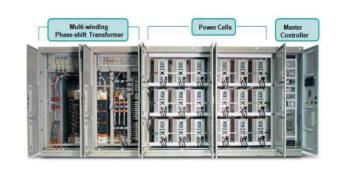

그림 2는 캐스케이드 멀티레벨 인버터 전체 시스템을 나타낸다.

그림 2. 캐스케이드 멀티레벨 인버터 시스템 Fig. 2. Cascaded Multi-level Inverter system

캐스케이드 멀티레벨 인버터는 각각 셀에 절연된 전 원을 공급하는 지그재그 변압기부, 고압출력을 생성하 기 위해 직렬연결된 단상 H-Bridge 형태의 파워셀부, 전체 시스템의 제어를 담당하는 마스터 제어부의 3부분으로 구성된다.

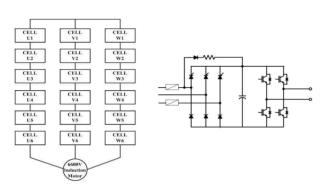

그림 3은 캐스케이드 결선 및 셀 구성을 나타낸다. 그림 3 (a)는 단상인버터를 직렬로 연결한 H-Bridge 방식 구성을 나타내며, 그림 3 (b)는 셀에 파워부 구성을 나타낸다. 셀은 크게 정류부, DC-Link 평활부, 인버터 부로 구성된다. 일반적인 저압 인버터의 경우 제어할 DC-link가 한 개로 보다 손쉽게 제어가 가능하지만, Cascaded H-Bridge 타입의 고압인버터의 경우 제어되어야할 DC-link가 충별로 여러 개 존재하므로 상대적으로 복잡한 제어가 요구된다.

(a) H-Bridge 방식 구성

(b) 셀의 구조

그림 3. 캐스케이드 결선 및 셀 구성

Fig. 3. Cascaded Diagram and Cell Schematic

#### 2.2 제안한 순간정전 보상 알고리즘

캐스케이드 방식의 고압인버터는 출력 전압과 전류의 위상이 각 셀마다 다르며, 전체 흐르는 전류는 동일하기 때문에 구조적으로 셀마다 감당해야할 전력 변화량이 다르게 나타난다. 입력파워(P<sub>in</sub>)과 출력파워(P<sub>out</sub>)커패시턴스(C<sub>d</sub>), 커패시터 전압(V<sub>dc</sub>) 일때 각 셀의 커패시터 전력 변화분의 전압은 식 (1)과 같다. 대용량 인버터가 적용된 부하는 전류가 매우 크기 때문에 각 셀에서 감당하는 커패시터의 용량으로는 저전압트립이 발생될 가능성이 매우 크다. 또한 위에서 언급한 층별로 다른 파워를 감당하는 셀에서의 커패시터 전압 안정화는 시스템 안정화를 위해 가장 필요한부분이다.

$$\frac{dW}{dt} = \frac{C_d}{2} \cdot \frac{dV_{dc}^2}{dt} = P_{in} - P_{out}$$

(1)

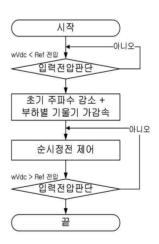

본 논문에서 제시한 알고리즘에서는 저전압 고장을 방지하기 위하여 입력전원 정전시 제어루프 초기에 인버터 운전주파수를 부하량에 따라 일정부분 감소하 여 회생에너지를 받는다. 이 방법으로 대용량 고압 인 버터는 정전 발생시 제어할 수 있는 초기 에너지를 얻 는다. 다음으로 부하에 맞게 적정한 감속 기울기로 인 버터 운전시킨다. 이때 계속적으로 전압을 검출하여 과전압 트립이 발생하지 않도록 적정한 기울기를 유 지한다.

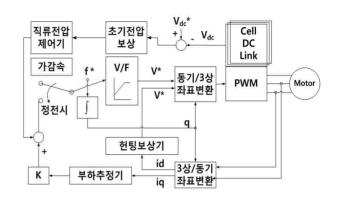

하지만 감속 중 회생량의 증가로 DC-Link 전압이 상승할 경우는 감소시키던 운전 주파수 지령을 전압 증가분만큼 증가하여 상승된 에너지를 소비한다. 입 력전압이 복전되어 정전구간을 벗어나게 되면 인버터 는 정상 운전하여 기존 목표 속도지령으로 복귀한다. 이후 인버터는 정전 이전 상태모드로 제어기를 복귀 할 수 있다. 그림 4는 마스터 제어 블록을 나타낸다.

그림 4. Master 제어 블록 Fig. 4. Master Control Block Diagram

효과적인 순시정전 보상 동작을 위하여 부하 특성을 정확하게 파악하여야 한다. 대용량 인버터 시스템의 경우 출력 차단시 모터의 감속 속도를 알아야 하는데 이는 항상 같을 수 없으며, 이에 따른 고려되는 변수는 대략 두 가지가 있다. 첫째 유전 속도에 따른 감속 속 도기울기 변화이며, 둘째로는 부하량에 따른 감속 속 도기울기를 설정해야 한다.

순간 정전이 발생하면 마스터제어기는 전동기를 발전기로 동작시켜 각 셀 인버터의 DC-Link에서 소 모되는 에너지를 확보하기 위하여 회생 모드로 운전 한다.

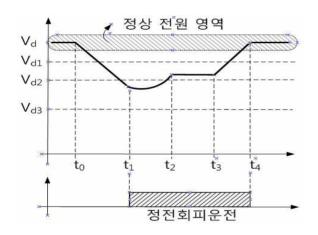

그림 5는 정전시 셀 DC-Link 전압을 나타낸다. 입력 전원(635 $V_{ac}$ )이 정상일 경우, 각 동작 전압은  $V_{d}$  890V,  $V_{d1}$  750V,  $V_{d2}$  700V,  $V_{d3}$  630V이다.  $V_{d}$ 는 정상 전압 레벨이며,  $V_{d1}$ ,  $V_{d2}$ 는 정전회피 운전시 제어전압 레벨이며,  $V_{d3}$ 는 저전압고장레벨이다. 본 논문에서는 시간  $t_{0}$ 에서 입력단에 순간 정전이 발생하고 시간  $t_{3}$ 에서 정상 전원으로 회복되어 시간  $t_{4}$ 에서 DC-Link 전압이 정상 상태에 도달하는 순간정압강하 보상 알고리즘을 수행한다.

그림 5. 정전시 셀 직류단 전압 Fig. 5. Voltage of the Cell DC-link during Sag

본 논문에서는 DC-Link 전압의 변화를 최소로 억제하기 위하여 최소 시간동안  $V_{dl}$ 과  $V_{d2}$  레벨 사이에 DC-Link 전압을 최대한으로 유지시키는 방법을 제안한 것이다. 그림 6은 제안된 순간전압강하 보상 제어기를 나타낸다. 기존의 Kai 등이 제안한 DC-Link 전압 제어 방식은 급격한 외란 발생시 DC-Link 안정화에 한계가 있었다[1].

하지만 제안된 순간전압강하 보상 알고리즘은 직류 전압 제어기와 부하추정기 및 속도추정기를 동시에 적용하며, 부하량 변동으로 인한 불안정을 해소하기 위하여 헌팅보상기를 동시에 적용하기에 가장 최적의 순간전압강하 보상 알고리즘으로 판단된다.

그림 6. 제안된 순간정전 보상 제어기 Fig. 6. Proposed sag compensation controller

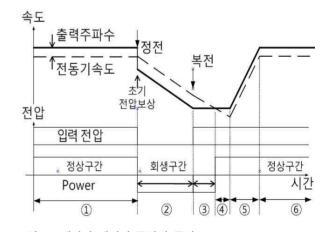

그림 7는 제안된 제어기의 구간별 동작을 나타낸다. 정상부분인 ①, ⑥ 시간은 전동기모드 동작구간으로 정전 발생 전후에 출력주파수와 전동기속도를 나타내고 있다. ② 시간은 시작점이 정전 발생부분이고, 제어기 동작에 의해 회생모드를 시작하는 구간이다. 초기전압보상 및 부하추정기를 포함해서 본 논문에서 제안하는 알고리즘 동작구간이다.

그림 7. 제안된 제어기 구간별 동작 Fig. 7. Proposed control actions each section

③ 시간은 입력전원이 복귀되고 정상상태로 진행하

기 위한 준비구간으로 이때 출력주파수는 일정하기 유지하여 전체 시스템이 안정화될 때까지 주파수를 제어하게 된다. 유의할 사항은 빠른 정상상태 복귀를 위해 복전시 바로 주파수를 변화하게 되면 출력 전압상승에 따른 과전압과 과전류 고장을 유발시킬수 있으므로 셀 커패시터 전압의 변화를 충분히 고려해야한다는 것이다. ④~⑤ 시간은 복전 후 정상목표주파수로 가속을 시작해 정상상태로 회복하는 동작구간이다.

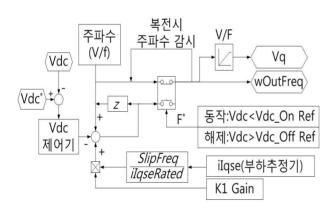

그림 8은 제안된 부하추정기를 나타낸다. 제안된 추정기는 출력 전류의 정격에 대비하여 부하량을 추정하고, 이를 주파수로 변환하여 기존 출력 주파수 대비하여 변동하는 출력 주파수를 추정하게 된다.

$$P_{\text{out}} = V_{\text{out}} \sin(\omega_o t) \cdot I_{\text{out}} \sin(\omega_o t + \phi)$$

(2)

식 (2)는 각각 셀에서의 전력을 나타낸 것이다. 전체 시리즈로 연결된 개별 셀에서 바라보면, 출력 전류는 동일하고 각 셀이 출력하는 전압이 다르므로 셀 별로 출력되는 전력이 다르게 된다.(출력파워  $P_{out}$ , 출력전류  $I_{out}$ , 주파수  $\omega_0$ , 역률  $\phi$ )

그림 8. 제안된 부하추정기 Fig. 8. Proposed load estimator

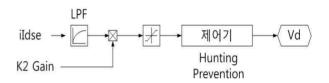

이로 인해 순간정전시 DC-Link 리플이 다르며, 제한된 부하추정기와 셀 층수에 따른 역률을 고 려해야만 안정된 커패시터 전압을 유지할 수 있 게 된다. 그림 9는 제안된 헌팅보상기를 나타낸다. 적용한 헌팅보상기는 총 출력 전류 중 자속분 전류(i<sub>d</sub>)를 바탕으로 이득(K2)을 고려하여 부하량 변동으로 인한 전류 불안정을 해소하는 방안으로 추가 적용하였다.

그림 9. 제안된 헌팅보상기 Fig. 9. Proposed hunting prevention

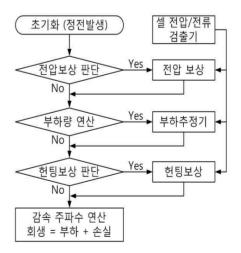

그림 10은 제안된 제어기 동작시 감속 주파수 연산과정을 나타낸 것이다. 초기 전압보상이 필요한 경우 전압보상판단 부분에서 최초 제어기 동작시까지 필요한 에너지를 전동기로부터 보상받고, 부하에 영향에 의해 급격히 변화될 수 있는 커패시터 에너지 방전을 막을 수 있는 부하추정기가 동작된다.

그림 10. 정전시 주파수 연산 Fig. 10. Frequency calculation during Sag

또한 출력전류 안정화를 위한 헌팅보상기를 추가하여 고장상황을 회피하여 정상운전이 가능하게 할 수 있는 출력 주파수를 생성한다.

## 3. 시뮬레이션 및 실험 결과

#### 3.1 시뮬레이션 결과

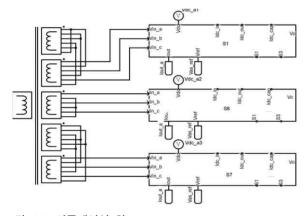

그림 11은 시뮬레이션 회로도를 나타낸다. 제안한 순간전압강하 보상 알고리즘을 검증하기 위해서 전류 진동과 전압 안정화에 대한 시뮬레이션 PSIM 9.0 프로그램으로 수행하였다.

표 1. 모의 실험 파라미터

Table 1. Parameter of simulation test

| 농형 유도전동기                 | 6600(V), 100(A) |

|--------------------------|-----------------|

| $Rs(\Omega), Rr(\Omega)$ | 0.217, 0.663    |

| Ls(mH), Lr(mH)           | 418.79, 398.52, |

| Lm(mH)                   | 413.74          |

그림 11. 시뮬레이션 회로도 Fig. 11. Simulation circuit

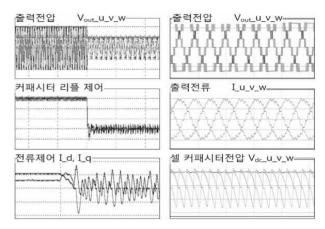

그림 12는 입력전원 전압변화시 시뮬레이션 결과 파형을 나타낸다. 그림 12와 같이 30Hz에서 입력 전원 변동시 순간전압강하 보상 알고리즘 적용한 경우 전류제어(d,q)에서 진동이 발생하고, 커패시터 리플도 상당히 발생하였지만, 출력 전압과 전류의 경우 끊김 없이 일정하게 유지되며, 커패시터 리플저감 알고리즘 적용에 따라 출력 전류의 진동이 상대적으로 적어지는 특성을 보이고 있다.

그림 12. 시뮬레이션 결과 Fig. 12. Simulation results

### 3.2 실험 결과

그림 13은 제안된 순간전압강하 보상 알고리즘의 테 스트를 위한 실험 장치를 나타낸다.

그림 13. 실험 장치 Fig. 13. Experimental apparatus

6.6kV 4MVA 에 연결된 모터 부하와 Cascaded H-Bridge 타입의 MV 시스템이다.(셀에 사용된 커패시터는 Nichicon 사의 NX Series 전해 커패시터입니다.) 모터에는 2.3:1 비율의 기어박스가 연결되어 있어서 다른 시스템과 비교할 때 정전시 감속이 더욱 빠르며 인버터 출력 주파수 50Hz이상으로 운전할 때는 그보다 감속이 더 빠르게 일어나는 것으로 확인되었다. 이는 제어기에 빠른 응답성을 확인하기 위한 좋은 시험 조건으로 제안된 알고리즘을 실험적으로 확인하고자 하였다.

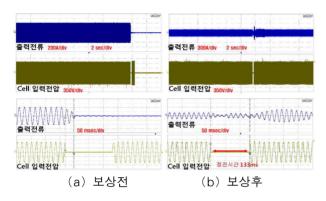

그림 14은 운전 주파수 60Hz에서 제안된 순간전압 강하 알고리즘의 보상 전 · 후의 실험파형을 나타낸다. 그림 14 (a)와 같이 순간전압강하 보상 알고리즘 적용하지 않는 경우 29msec 후 출력 전류가 저전압트립으로 차단되어 인버터가 정지하였다. 그림 14 (b)는 제안된 순간전압강하 보상 알고리즘을 적용한 파형으로 셀입력 전압이 133msec동안 정전되었으며, 이때도 셀DC-Link 전압을 일정하게 유지시켜 출력 전류 및 출력 주파수를 고장없이 정상 출력하는 것을 확인할 수있었다.

그림 14. 실험결과(출력주파수 : 60Hz, 정전 133msec) Fig. 14. Experimental results(output freq : 60Hz)

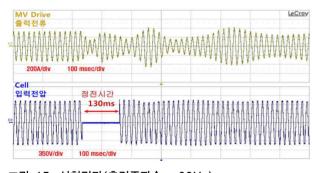

그림 15. 실험결과(출력주파수 : 60Hz) Fig. 15. Experimental results(output freq : 60Hz)

그림 15는 다른 부하인 6.6kV 3MVA 시스템에 운전 주파수 60Hz에서 제안된 순간전압강하 알고리즘의 보상시 실부하 실험파형을 나타낸다. 그림 15에서 순 간 정전 130msec 동안 연속적으로 출력 주파수를 유 지시켰고, 복전후 안전하게 제어됨을 확인하였다. 이 시험을 통해 다양한 부하에 제안된 순간전압강하 보 상 알고리즘의 적용할 수 있다는 타당성을 확인할 수 있었다.

#### 4. 결 론

본 논문은 Cascaded H-Bridge 타입의 MV 시스템 의 입력 전원 순간정전시 순간전압강하 보상 알고리 즘을 통한 연속 운전방법을 제안하였다. 각 셀 인버터 의 직류단 전압을 유지하기 위한 새로운 안정화 보상 알고리즘을 제안하였으며, 제안된 순간전압강하 보상 알고리즘은 직류전압 제어기, 부하추정기, 속도추정기 및 헌팅 보상기를 사용하여 순간 정전이 발생하는 경 우 인버터 출력 전류의 급격한 변화를 억제하고, 부하 량 변동에 따른 안정화를 추구하는 전류제어 방식을 도입하여 가장 최적의 순간전압강하 보상 방안을 새 롭게 제시하였다. 최소 보장가능한 시간은 100msec로 설정하였으며, PSIM 9.0을 통한 시뮬레이션과 6.6kV 3MVA, 4MVA 유도 전동기 실부하 실험을 통하여 정 전시 출력전류를 130-133msec까지 유지시킬 수 있었 다. 최대 전압이 유지 시간은 부하에 따라 가변가능하 며, 관성이 큰 부하를 가진 시스템의 경우 저압에서 확 인한 바와 같이 수초 정도의 정전보상도 가능할 것으 로 예상된다. 이로서 본 논문에서 제안한 순간정압강 하 보상 알고리즘의 타당성을 시뮬레이션과 실험에 의해서 검증하였다. 향후, 보다 부하량에 민감하지 않 는 제어시스템 디자인을 위해 계속 연구를 진행할 것 이다.

## **References**

- [1] B. Wu, High-Power Converters and AC Drive. New York: Wiley-IEE Press, Mar. 2006.

- [2] J. Rodriguez, S. Bernet, B. Wu, J. O. Pontt, and A. Kouro, "Multi-level voltage-source-converter topologies for industrial medium-voltage drives," IEEE Trans. Ind. Electron., vol. 54, no. 6, pp. 2930–2945, Dec. 2007.

- (3) A. Nabae, I. Takahashi, and H. Akagi, "A neutral-point-clamped PWM inverter," in Conf. Rec. IEEE IAS Annu. Meeting, Cincinnati, OH, vol.3, pp. 761-766, Sep. 28-Oct. 3, 1980.

- [4] P. Steimer, "High power electronics trends of technology and applications," in Proc. POM, Germany, May. 2007.

- [5] Kai Pietiläinen and Lennart Harnefors, Andreas Petersson, Hans-Peter Nee "DC-Link Stabilization and Voltage Sag Ride-Through of Inverter Drives", IEEE Transactions on Industrial Electronics, Vol.53, No.4, 1261–1268, Aug. 2006.

- (6) Joachim Holtz and Wolfgang Lotzkat, "Controled AC

- Drives with Capability at Power Interruption", IEEE Transactions on Industry Applications, Vol. 30, No. 5, pp. 1275–1283, Sept./Oct. 1994.

- [7] Brian J.Seibel, Russel J.Kerkman, and David Leggate, "Inverter Control During Overload and Following Power Interruption", IEEE Transactions on Industry Applications, Vol. 28, No. 3, pp. 567–573, May./June. 1992.

- [8] Shakweh, Y., Aufleger, P., 'Multimegawatt, medium-voltage, PWM, voltage source, sine-wave-output converter for industrial drive applications', PEVD98 Conf. Proc., IEE, London, UK., 1998, pp 632-637.

- [9] B. S. Kang, J. C. Kim, J. F. Moon, S.Y. Yun, "Investiga tion of the Impact of voltage Sags on 3-Phase induction motors", KIIEE Annual Spring Conference, pp. 361-365, 2004.

- [10] Y. M. Kwon, J. C. Kim, Y. S. Kim, Y. J. Lee, "Analysis on the effect of RC finer to mitigate transient overvoltage on the highl voltage induction motor fed by Multi level inverter", KIIEE Annual Autumn Conference, pp. 399-403, 2005.

## ◇ 저자소개 ◇

## 윤흥민(尹洪敏)

1976년 8월 8일생. 1999년 동국대 전기 공학과 졸업. 2001년 동 대학원 전기 공학과 졸업(석사). 2011년 ~ 현재 동 대학원 전기전자공학부 박사과정. 2001년 ~ 현재 LS산전 자동화제품연구소 책임 연구원.

#### 김 용(金 龍)

1957년 3월 20일생. 1981년 동국대 전기 공학과 졸업. 1994 동 대학원 전기공학과 졸업(박사). 1995년~현재 동국대 전자 전기공학부 교수.