## A Continuous Regional Current-Voltage Model for Short-channel Double-gate MOSFETs

Zhu Zhaomin, Yan Dawei, Xu Guoqing, Peng Yong, and Gu Xiaofeng

Abstract—A continuous, explicit drain-current equation for short-channel double-gate (**DG**) MOSFETs has been derived based on the explicit surface potential equation. The model is physically derived from Poisson's equation in each region of operation and adopted in the unified regional approach. The proposed model has been verified with numerical solutions, physically scalable with channel length and gate/oxide materials as well as oxide/channel thicknesses.

# *Index Terms*—Double-gate MOSFETs, short channel, surface potential

## I. INTRODUCTION

With the aggressive scaling of CMOS, future technology scaling will require novel device structures. Multiple-gate (MG) structures such as planar double-gate (DG) MOSFETs, vertical FinFETs, nanowire surrounding gate, and various 3D geometries [1] have been demonstrated. MG MOSFETs exhibit large inherent immunity to short-channel effects, sharper subthreshold slope, and higher drive current [2]. Intense efforts have been devoted to the development of compact models for DG-MOSFETs in the literature [3, 4]. Theoretical analysis of double-gate (DG) transistors dates back to 1967 [5], about the same time as bulk MOSFET models. Since 1980's many alternatives to the conventional bulk-

Manuscript received Oct. 15, 2012; accepted Feb. 27, 2013.

Key Laboratory of Advanced Process Control for Light Industry (Ministry of Education), Department of Electronic Engineering, Jiangnan University, Wuxi 214122, China. E-mail : zhuzhaomin@gmail.com MOSFETs [6-10]. Theoretically, this type of "generic" MOSFETs has a different boundary condition from bulk MOSFET due to the back-gate oxide. When the backgate oxide thickness approaches that of the front gate, SOI conceptually becomes DG. Recently, there has been intense research interest in the development of compact models for SOI/DG MOSFETs [11-15]. Most of the models are integrable ones [7, 11, 13]; some are iterative [11, 15] and others are explicit [13, 14]. Undoped s-DG/a-DG MOSFETs were analyzed by Taur [11]. Ortiz-Conde et al. presented an approximate solution to the undoped s-DG surface potential [13] in comparison with the iterative one, and an implicit solution by numerical iteration [15] for generic doped MOSFETs with two gates. Undoped s-DG MOSFETs have been solved both implicitly [16-18] and analytically [18-20], while undoped asymmetric cases have only been solved implicitly in literature [11]. Subthreshold characteristics in short channel double-gate MOSFETs has also been solved analytically [26].

silicon MOSFET have been proposed and developed,

such as the silicon-on-insulator (SOI) and double-gate

In this paper, we present a continuous, explicit draincurrent equation for short-channel double-gate (DG) MOSFETs based on the explicit surface potential equation, physically scalable with independent applied gate biases and oxide/channel thickness variations. Explicit regional solutions are derived for the first time for DG and the unified regional solution shows an error in the mili-volts range with respect to the numerical solutions.

## II. ANALYTICAL LONG-CHANNEL CURRENT-VOLTAGE SOLUTION

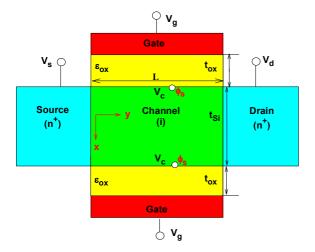

For long channel double-gate MOSFETs as shown in Fig. 1, the drain-current equation can be extracted from the Pao-Sah's integral, which is expressed as

$$I_D = \frac{W}{L} \mu \int_0^{Vds} \mathcal{Q}_i(V) dV \tag{1}$$

where  $I_D$  is drain current, W is gate width, L is gate length, u is mobility and  $Q_i(V)$  is inversion charge in the channel.  $Q_i(V)$  can be express by the Gauss's law

$$Q_i(V) = 2\varepsilon_{si}(\frac{d\phi}{dx})_{x = -t_{si}/2}$$

(2)

where  $\phi$  represents potential. After substituting (2) into (1) with boundary conditions, we get

$$I_D = \frac{2W}{L} \mu \int_0^{Vds} (\varepsilon_{ox} \frac{V_g - \Delta \phi_i - \varphi_s}{t_{ox}}) dV \qquad (3)$$

where Vg is gate voltage,  $t_{ox}$  is gate oxide thickness, and  $\phi_s$  is surface potential. After solving (3), a continuous, explicit drain-current equation is reached [21, 22]:

$$I_{ds} = \frac{2\mu W}{L} \frac{\varepsilon_{ox}}{t_{ox}} \left[ \frac{1}{2} (V_{gf} - \varphi_s)^2 + \frac{2kT}{q} (V_{gf} - \varphi_s) - \frac{t_{ox}}{2\varepsilon_{ox}} kTn_i t_{si} (e^{\frac{q(\varphi_s - V)}{kT}} - \frac{\varepsilon_{ox}^2 (V_{gf} - \varphi_s)^2}{2t_{ox}^2 \varepsilon_{si} kTn_i}) \right] \Big|_0^{V_{ds}}$$

(4)

Fig. 1. Schematic of a symmetric DG *n*-MOSFET.

where  $V_{gf} = V_g - \Delta \phi_i$ .  $\varepsilon_{ox}$  and  $\varepsilon_{si}$  are dielectric constant of oxide and silicon, respectively. q is the electron charge.  $n_i$  is the intrinsic carrier density.  $\phi_s$  can be got approximately from the following expressions [23]:

$$\phi_{sub} = V_{gf} , \qquad (5a)$$

$$\phi_{str} = V_{gf} - 2v_{th}\mathcal{L}_{+} \left\{ \frac{qt_{ox}}{\varepsilon_{ox}} \sqrt{\frac{n_i \varepsilon_{Si}}{2kT}} e^{\left(V_{gf} - V_c\right)/2v_{th}} \right\},$$

(5b)

$$\phi_s = \vartheta_{eff} \left\{ \phi_{sub}, \phi_{str}; \delta \right\}.$$

(5c)

where  $\mathcal{L}_{+}\{w\}$  is the *Lambert W* function [24] (principal branch), and

$$\vartheta_{eff} \left\{ x_{sub}, x_{str}; \delta \right\} \equiv x_{str} - 0.5 \left[ x_{str} - x_{sub} - \delta + \sqrt{\left( x_{str} - x_{sub} - \delta \right)^2 + 4\delta x_{str}} \right]$$

(6)

where  $\delta$  is a smoothing parameter [25], which is set as a constant 0.001 (which can be tuned for smoothness).

For symmetric case, we define the saturation voltage  $V_{dsat}$  at the point  $\varphi_{sub} = \varphi_{str}(V) - \delta_1$ , where  $\delta_1$  is a fitting parameter. Then we get

$$V_{Dsat} = V_{gf} + \frac{2kT}{q} \ln \frac{t_{ox}}{\delta \varepsilon_{ox}} \sqrt{2kTn_i \varepsilon_{Si}} - \delta_1 \qquad (7)$$

The subthreshold current is extracted by setting  $V_{gf} = \phi_s$ in Eq. (6),

$$I_{dsub} = \frac{\mu W}{L} k T n_i t_{si} e^{\frac{q V_{gf}}{kT}} (1 - e^{\frac{-V_{ds}}{kT}})$$

(8)

## III. ANALYTICAL SHORT-CHANNEL CURRENT-VOLTAGE SOLUTION

For short channel case, the drain-current equation can be expressed by [26]

$$I_D = \frac{W}{L} \mu_{eff} \int_0^{Vds} Q_i(V) dV = \frac{W}{L} \mu_{eff} \int_0^{Vds} Q_i(V) \frac{dV}{dy} dy$$

(9)

Because

$$\frac{dQ_i}{dx} = \frac{Q_i}{U_T} \left(\frac{d\varphi_s}{dy} - \frac{dV}{dy}\right)$$

[27], where

$$U_T = \frac{kT}{q}$$

So  $\frac{dV}{dy} = \frac{d\varphi_s}{dy} - \frac{U_T}{Q_i} \frac{dQ_i}{dy}$ , then we can get

$$I_D = \frac{W}{L} \mu_{eff} \int_0^{Vds} Q_i(V) (\frac{d\varphi_s}{dy} dy - \frac{U_T}{Q_i} dQ_i)$$

=  $I_{D1} - \frac{W}{L} \mu_{eff} U_T (Q_d - Q_s)$  (10)

where  $Q_s = \varepsilon_{ox} \frac{V_{gf} - \varphi_{ss}}{t_{ox}}$ ,  $Q_d = \varepsilon_{ox} \frac{V_{gf} - \varphi_{sd}}{t_{ox}}$ ,

$\varphi_{ss}$  and  $\varphi_{sd}$  are the surface potential at source side and drain side, respectively.

$$I_{D1} = \frac{W}{L} \mu_{eff} \int_0^L Q_i(y) \frac{d\varphi_s}{dy} dy$$

(11)

Considering velocity saturation effect,  $\mu_{\text{eff}}$  can be expressed by

$$\mu_{eff} = \frac{\mu_s}{\left[1 + \left(E_y / E_{sat}\right)^2\right]^{1/2}}$$

(12)

where  $E_{sat} = \frac{v_{sat}}{\mu_s}$ ,  $\mu_s$  is constant mobility.

Q<sub>i</sub>(y) can be extracted from Gauss' law,

$$Q_i(y) = \varepsilon_{si}(E'(y))t_{si} + 2\varepsilon_{si}E_s(y)$$

(13)

where

$$E_s(y) = -\varepsilon_{ox} \frac{V_{gf} - \varphi_s(y)}{\varepsilon_{si} t_{ox}}$$

(14)

In the linear region (V<sub>DS</sub><V<sub>dsat</sub>),  $E_y << E_C$ , so after substituting (13) into (11) we get

$$I_{D1} = \frac{\mu_{eff}W}{L} \int_0^L \frac{d\varphi_s(y)}{dy} [2\varepsilon_{si}E(y)]dy + \frac{\mu_{eff}W}{L} \int_0^L \frac{d\varphi_s(y)}{dy} [\varepsilon_{si}(E'(y))t_{si}]dy \quad (15) = I_{D2} + \frac{\mu_{eff}W}{L} [\varepsilon_{si}t_{si}](\frac{E(y)^2}{2})\Big|_0^L$$

where

$$I_{D2} = \frac{\mu_{eff}W}{L} \int_0^L \frac{d\varphi_s(y)}{dy} [2\varepsilon_{si}E(y)]dy \qquad (16)$$

Suppose

$$E(y) = -\frac{1}{\eta} \frac{d\varphi_s(y)}{dy}$$

(17)

where  $\boldsymbol{\eta}$  is a fitting parameter, and

$$E'(y) = -\frac{1}{\eta} \frac{d^2 \varphi_s(y)}{dy^2} \tag{18}$$

From Eq. (13), we can get

$$\varepsilon_{si}\left(-\frac{1}{\eta}\frac{d^{2}\varphi_{s}(y)}{dy^{2}}\right)t_{si}-2\varepsilon_{ox}\frac{V_{gf}-\varphi_{s}}{t_{ox}}=qn_{i}\int_{0}^{t_{si}}e^{\frac{q\phi(x,y)}{kT}}dx$$

(19)

When in the volume inversion region (subthreshold region  $V_G < V_T$ ), the inversion charge in the channel can be neglected. So

$$\varepsilon_{si}\left(-\frac{1}{\eta}\frac{d^{2}\varphi_{s}(y)}{dy^{2}}\right)t_{si}-2\varepsilon_{ox}\frac{V_{gf}-\varphi_{s}}{t_{ox}}\approx0$$

(20)

When in the strong inversion region ( $V_G < V_T$ ), the inversion charge in the channel can be approximated by

$$Q_{i}(y) = C_{ox}(V_{gf} - \varphi_{s}(y)), \text{ So}$$

$$\varepsilon_{si}(-\frac{1}{\eta}\frac{d^{2}\varphi_{s}(y)}{dy^{2}})t_{si} - 2\varepsilon_{ox}\frac{V_{gf} - \varphi_{s}}{t_{ox}} \approx C_{ox}(V_{gf} - \varphi_{s}(y))$$

(21)

Let's set

$$a = \frac{\varepsilon_{si} t_{si}}{\eta}, \quad d = \frac{2\varepsilon_{ox}}{t_{ox}}, \quad c = 2\varepsilon_{ox} \frac{\varphi_s(y)}{t_{ox}}$$

(22)

After solving (21), we can get

$$\varphi_{s}(y) = \frac{c}{d} + \frac{[\varphi_{s}(V_{D}) - \frac{c}{d}]}{\sinh(\sqrt{\frac{d}{a}}L)} \sinh(\sqrt{\frac{d}{a}}y) + [\varphi_{s}(V_{S}) - \frac{c}{d}] \frac{\sinh[\sqrt{\frac{d}{a}}(L-y)]}{\sinh(\sqrt{\frac{d}{a}}L)}$$

(23)

Then

$$-\frac{d\varphi_{s}(y)}{dy} = \frac{\varphi_{s}(V_{d}) - \frac{c}{d} - e^{(-\sqrt{\frac{d}{a}L})}(\varphi_{s}(0) - \frac{c}{d})}{2\sinh(\sqrt{\frac{d}{a}L})} \sqrt{\frac{d}{a}} e^{(\sqrt{\frac{d}{a}}y)} + \frac{\varphi_{s}(V_{d}) - \frac{c}{d} - e^{(\sqrt{\frac{d}{a}L})}(\varphi_{s}(0) - \frac{c}{d})}{2\sinh(\sqrt{\frac{d}{a}L})} \sqrt{\frac{d}{a}} e^{(-\sqrt{\frac{d}{a}}y)}$$

(24)

Meanwhile,

$$\varphi_{\rm s}(0) = \frac{kT}{q} \ln \frac{N_{SD}}{n_i}, \quad \varphi_{\rm s}({\rm V_d}) = \frac{kT}{q} \ln \frac{N_{SD}}{n_i} + V_{DS}$$

(25)

Now we can get  $I_{D2}$  after substituting (23) into (16)

$$\begin{split} I_{D2} &= \frac{2\varepsilon_{si}\mu_{s}W}{\eta L} \int_{0}^{L} (\frac{d\varphi_{s}}{dy})^{2} dy \\ &= \frac{2\varepsilon_{si}\mu_{s}W}{\eta L} [\frac{1}{2} (\frac{\varphi_{s}(V_{d}) - \frac{c}{d} - e^{(\sqrt{\frac{d}{a}}L)}(\varphi_{s}(0) - \frac{c}{d})}{2\sinh(\sqrt{\frac{d}{a}}L)})^{2} \sqrt{\frac{d}{a}} e^{(2\sqrt{\frac{d}{a}}y)} \\ &- \frac{1}{2} (\frac{\varphi_{s}(V_{d}) - \frac{c}{d} - e^{(\sqrt{\frac{d}{a}}L)}(\varphi_{s}(0) - \frac{c}{d})}{2\sinh(\sqrt{\frac{d}{a}}L)})^{2} \sqrt{\frac{d}{a}} e^{(-2\sqrt{\frac{d}{a}}y)} \\ &+ 2\frac{\varphi_{s}(V_{d}) - \frac{c}{d} - e^{(\sqrt{\frac{d}{a}}L)}(\varphi_{s}(0) - \frac{c}{d})}{2\sinh(\sqrt{\frac{d}{a}}L)} \\ &+ 2\frac{\varphi_{s}(V_{d}) - \frac{c}{d} - e^{(\sqrt{\frac{d}{a}}L)}(\varphi_{s}(0) - \frac{c}{d})}{2\sinh(\sqrt{\frac{d}{a}}L)} \\ &\times \frac{\varphi_{s}(V_{d}) - \frac{c}{d} - e^{(\sqrt{\frac{d}{a}}L)}(\varphi_{s}(0) - \frac{c}{d})}{2\sinh(\sqrt{\frac{d}{a}}L)} y] \Big|_{0}^{L} \end{split}$$

(26)

Finally we can get  $I_{D1}$  after substituting (24) and (26) into (16), accordingly  $I_D$  after substituting (15) into (10).

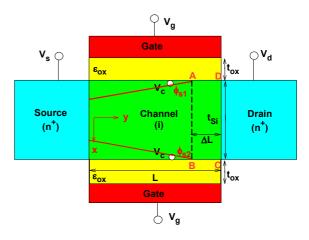

In the saturation region, the gradual channel approximation (GCA) will not be valid near drain side. So we divide the channel into two regions. In the region

$(0 \le y \le L - \Delta L)$  GCA still applies, but in the region L- $\Delta L \le y \le L$  we need to consider the effects of both vertical and lateral electrical fields.

Considering channel length modulation effect,

$$I_{ds} = I_D [1 - \frac{\Delta L}{L}]^{-1} \tag{27}$$

where  $\Delta L$  is width of non-GCA region, which can be extracted as follows.

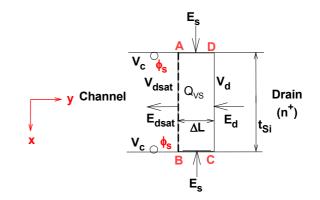

After we apply Gauss' law to the ABCD box in Fig. 2 (see Fig. 3), we can get the charge in the velocity saturation region  $(Q_{VS})$

$$Q_{VS}(y) = \varepsilon_{si}(E_y'(y))t_{si} + 2\varepsilon_{si}E_s(y)$$

(28)

where

**Fig. 2.** Schematic of a short-channel symmetric DG *n*-MOSFET.

**Fig. 3.** Velocity saturation region of a short-channel symmetric DG n-MOSFET.

$$E_s(y) = \varepsilon_{ox} \frac{V_{gf} - \varphi_{s0} - V(y)}{\varepsilon_{si} t_{ox}}$$

(29)

Substituting (29) into (28), we can get (for symmetric undoped double-gate MOSFETs),

$$Q_{vs}(y) = \varepsilon_{si} E_y'(y) t_{si} + 2 \frac{\varepsilon_{ox}}{t_{ox}} (V_{gf} - \varphi_{s0} - V(y))$$

(30)

When y=0, according to gradual channel approximation,

$$Q_{vs}(0) = 0 + 2\frac{\varepsilon_{ox}}{t_{ox}}(V_{gf} - \varphi_{s0} - V_{dsat})$$

(31)

In the ABCD box (velocity saturation region),

$$Q_{vs}(y) = Q_{vs}(0)$$

(32)

Then we can get  $E_y'(y)$  by Eq. (30) and (31),

$$E_{y}'(y) = 2 \frac{\varepsilon_{ox}}{\varepsilon_{Si} t_{Si} t_{ox}} (V(y) - V_{dsat})$$

(33)

The solution of the above equation is,

$$V(y) = V_{Dsat} + E_{sat} \sqrt{\frac{2\varepsilon_{ox}}{\varepsilon_{Si} t_{Si} t_{ox}}} \sinh(\frac{y}{\sqrt{\frac{2\varepsilon_{ox}}{\varepsilon_{Si} t_{Si} t_{ox}}}})$$

(34)

When  $y=\Delta L$ ,

$$V_D = V_{Dsat} + E_{sat} \sqrt{\frac{2\varepsilon_{ox}}{\varepsilon_{Si} t_{Si} t_{ox}}} \sinh(\frac{\Delta L}{\sqrt{\frac{2\varepsilon_{ox}}{\varepsilon_{Si} t_{Si} t_{ox}}}})$$

(35)

Then

$$\Delta L = \sqrt{\frac{2\varepsilon_{ox}}{\varepsilon_{Si}t_{Si}t_{ox}}} \operatorname{asinh}(\frac{\sqrt{\varepsilon_{Si}t_{Si}t_{ox}}(V_D - V_{Dsat})}{E_{sat}\sqrt{2\varepsilon_{ox}}})$$

(36)

### **IV. RESULTS AND DISCUSSION**

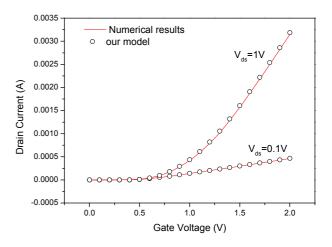

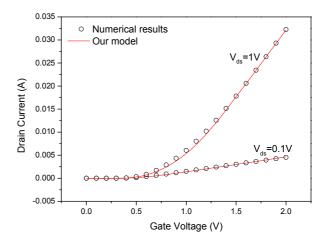

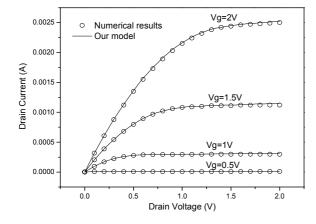

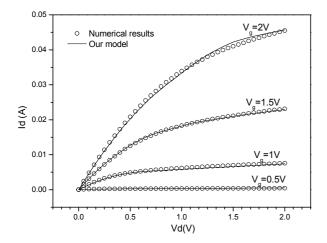

In this section, results of the explicit solutions are compared with the numerical solutions for various operating conditions. Fig. 4 demonstrates Id-Vg curves when channel length is  $1\mu$ m (long channel case). Fig. 5 plots Id-Vg curves when channel length is 0.1  $\mu$ m (short channel case). Fig. 6 gives the comparison of the explicit, analytical drain current-drain voltage output characteristics and that from MEDICI results when channel length is 1  $\mu$ m (long channel case). Fig. 7 compares the drain current-drain voltage output

**Fig. 4.** Id-Vg curves for long-channel undoped double-gate MOSFETs. Symbols are from numerical results and line is from our model. Oxide thickness is 3 nm and channel thickness is 30 nm. Channel length is 1 um.

**Fig. 5.** Id-Vg curves for short-channel undoped double-gate MOSFETs. Symbols are from numerical results and line is from our model. Oxide thickness is 3 nm and channel thickness is 30 nm. Channel length is 100 nm.

**Fig. 6.** Id-Vd curves for undoped double-gate MOSFETs. Lines are numerial results and symbols are our models. Oxide thickness is 3 nm and channel thickness is 30 nm. Channel length is 1 um.

**Fig. 7.** Id-Vd curves for undoped double-gate MOSFETs. Lines are numerial results and symbols are our models. Oxide thickness is 3 nm and channel thickness is 30 nm. Channel length is 100 nm.

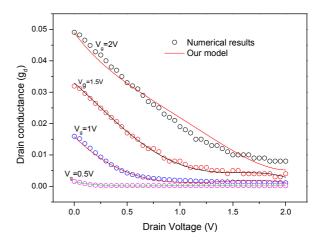

characteristics as calculated analytically with that from MEIDI results when channel length is 100 nm (short channel case), for four values of gate voltages. While we built our model, some fitting parameters are introduced for simplification and approximation of complicated equations, which otherwise cannot be solved analytically. The existence of the fitting parameters will produce some difference between MEDICI and our model. In general our model agrees very well with the simulated results. Fig. 8 gives the comparison of drain conductance (g<sub>d</sub>) between our model and simulated results.

Fig. 8.  $g_d$ -Vd curves for undoped double-gate MOSFETs. Lines are numerial results and symbols are our models. Oxide thickness is 3 nm and channel thickness is 30 nm. Channel length is 100 nm.

#### V. CONCLUSIONS

An explicit unified regional short-channel drain current-drain voltage model has been derived for undoped symmetric double-gate. The  $V_{dsat}$  equation of undoped DG MOSFET has also been derived. The scalability of the model for different channel length and oxide thicknesses has been verified with the numerical solutions. The explicit solution is not only computationally efficient, more importantly, it is also easier to evaluate in compact drain-current formulations. The model has shown good accuracy compared with MEDICI result.

### ACKNOWLEDGEMENT

This work is partly supported by the Fund of the State Key Laboratory of ASIC and System in Fudan University (11KF003), the Fundamental Research Funds for the Central Universities (JUSRP211A37, JUSRP51323B), Natural Science Foundation of Jiangsu Province (BK2012110), PAPD of Jiangsu Higher Education Institutions and the Summit of the Six Top Talents Program of Jiangsu Province (DZXX-053).

## REFERENCES

J. P. Colinge, *Solid-State Electron.*, vol. 48, pp. 897-905, 2004.

- [2] Q. Chen, K. A. Bowman, E. M. Harrell, and J. D. Meindl, "Double jeopardy in the nanoscale court," *IEEE Circuits Devices Mag.*, vol. 19, no.1, pp. 28-34, Jan. 2003.

- [3] K. Kim and J. G. Fossum, *IEEE Trans. Electron Devices*, vol. 48, no. 2, pp. 294-299, Feb. 2001.

- [4] K. Suzuki and T. Sugii, *IEEE Trans. Electron Devices*, vol. 42, no. 11, pp. 1940-1948, Nov. 1995.

- [5] H. R. Farrah and R. F. Steinberg, "Analysis of double-gate thin-film transistor," *IEEE Trans. Electron Devices*, vol. ED-14, no. 2, pp. 69-74, Feb. 1967.

- [6] F. Balestra, S. Cristoloveanu, M. Benachir, J. Brini, and T. Elewa, "Double-gate silicon-on-insulator transistor with volume inversion: A new device with greatly enhanced performance," *IEEE Electron Device Lett.*, vol. EDL-8, no. 9, pp. 410-412, Sept. 1987.

- [7] K. K. Young, "Analysis of conduction in fully depleted SOI MOSFET's," *IEEE Trans. Electron Devices*, vol. 36, no. 3, pp. 504-506, Mar. 1989.

- [8] K. Suzuki, T. Tanaka, Y. Tosaka, H. Horie, and Y. Arimoto, "Scaling theory for double-gate SOI MOSFET's," *Electron Devices, IEEE Transactions on*, vol. 40, no. 12, pp. 2326-2329, Dec. 1993.

- [9] P. Francis, A. Terao, D. Flandre, and F. Van de Wiele, "Modeling of ultrathin double-gate nMOS/SOI transistors," *IEEE Trans. Electron Devices*, vol. 41, no. 5, pp. 715-720, May 1994.

- [10] J. W. Sleight and R. Rios, "A continuous compact MOSFET model for fully- and partially-depleted SOI devices," *IEEE Trans. Electron Devices*, vol. 45, no. 4, pp. 821-825, Apr. 1998.

- [11] Y. Taur, "Analytic solutions of charge and capacitance in symmetric and asymmetric doublegate MOSFETs," *IEEE Trans. Electron Devices*, vol. 48, no. 12, pp. 2861-2869, Dec. 2001.

- [12] X. Shi and M. Wong, "Analytical solutions to the one-dimensional oxide-silicon-oxide system," *IEEE Trans. Electron Devices*, vol. 50, no. 8, pp. 1793-1800, Aug. 2003.

- [13] A. Ortiz-Conde, and F. J. Garcia-Sanchez, and S. Malobabic, "Analytic solution of the channel potential in undoped symmetric dual-gate MOSFETs," *IEEE Trans. Electron Devices*, vol. 52, no. 7, pp. 1669-1672, Jul. 2005.

- [14] Y. S. Yu, S. H. Kim, S. W. Hwang, and D. Ahn,

"All-analytic surface potential model for SOI MOSFETs," *IEE Proc.-Circuits Devices Systems*, vol. 152, no. 2, pp. 183-188, 2005.

- [15] A. Ortiz-Conde, R. Herrera, P. E. Schmidt, F. J. Garcia Sanchez, and J. Andrian, "Long-channel silicon-on-insulator MOSFET theory," *Solid-State Electron.*, vol. 35, pp. 1291-1298, Sept. 1992.

- [16] Y. Taur, *IEEE Electron Device Lett.*, vol. 21, pp. 245-247, May 2000.

- [17] J. He, X. Xi, C.-H. Lin, M. Chan, A. Niknejad, and C. Hu, *Proc. NSTI WCM-Nanotech 2004*, Boston, vol. 2, pp. 124-127, 2004.

- [18] S. Malobabic, A. Ortiz-Conde, F. J. G. Sanchez, Proc. 5th IEEE International Carrcas Conference on Devices, Circuits and Systems, Dominican Republic, pp. 19-25, Nov, 2004.

- [19] X. Shi and M. Wong, *IEEE Trans. Electron Devices*, vol. 50, pp. 1793-1800, Aug. 2003.

- [20] A. Ortiz-Conde, F. J. Garcia Sanchez, M.Guzman, Solid-State Electron., vol. 47, pp. 2067-2074, 2003.

- [21] Taur et. al., "A Continuous, Analytic Drain-Current Model for DG MOSFETs," IEEE ELECTRON DEVICE LETTERS, Vol. 25, No. 2, FEBRUARY 2004

- [22] Z. Zhu, X. Zhou, S. C. Rustagi, G. H. See, S. Lin, G. Zhu, C. Wei, and J. Zhang, "Analytic and explicit current model of undoped double-gate MOSFETs," *Electron. Lett.*, Vol. 43, No. 25, pp. 1464-1466, Dec. 2007.

- [23] Zhaomin Zhu, Xing Zhou, Karthik Chandrasekaran, Subhash C. Rustagi, and Gui Hui See, "Explicit Compact Surface-potential and Drain-Current Models for Generic Asymmetric Double-gate Metal-Oxide-Semiconductor Field-Effect Transistors", Japanese Journal of Applied Physics, Vol. 46, No. 4B, 2007, pp 2067-2072

- [24] R. M. Corless, G. H. Gonnet, D. E. G. Hare, and D. J. Jeffrey, "Lambert's W Function in Maple," Technical Report, Dept. of Applied Math., Univ. of Western Ontario, Canada.

- [25] X. Zhou, S. B. Chiah, K. Chandrasekaran, G. H. See, W. Shangguan, S. M. Pandey, M. Cheng, S. Chu, and L.-C. Hsia, *Proc. NSTI Nanotech 2005*, Anaheim, May, 2005, vol. WCM, pp. 25-30.

- [26] Xiaoping Liang, and Yuan Taur, "A 2-D Analytical Solution for SCEs in DG MOSFETs," IEEE Trans. Electron Devices, Vol. 51, pp. 1385-1391, Aug.

2004.

[27] Christian C. Enz, and Eric A. Vittoz, "Chargebased MOS Transistor Modeling: The EKV Model for Low-Power and RF IC Design", John Wiley & Sons, Ltd, 2006, pp. 59

**Zhu Zhaomin** received his Bachelor's degree in Nankai University in 1995, the Ph.D degree in Fudan University in 2002. In 2011, he joined the department of electrical engineering, Jiangnan University in China, where he is currently an

associate professor. His research involves device modeling, circuit design and image processing.

Yan Dawei received the Bachelor degree in Ludong University in 2005, the M.S. degree in Yantai University in 2008, and the Ph.D. degree in Nanjing University in 2011, respectively in china. His research interests focus on the III-nitride

HEMTs and LEDs Characterization & Reliability Analysis.

Xu Guoqing received the Bachelor degree in Jiangnan University in 2011. Now he's pursuing his Master's degree in Jiangnan University. His research interests focus on device modeling and image processing.

**Peng Yong** received his Master's degree in Nanjing University of Aeronautics and Astronautics in 1995. Now he's an associate professor in Jiangnan University. His research interests focus on circuit design and

device modeling.

**Gu Xiaofeng** received the Ph.D degree from the Johns Hopkins University in the United States in 2003. Now he is a professor in the department of electrical engineering in Jiangnan University. His research interests focus on circuit design and

study o f semiconductor device physics.