J. KIEEME

Vol. 26, No. 5, pp. 341-346, May 2013

DOI: http://dx.doi.org/10.4313/JKEM.2013.26.5.341

# 박막트랜지스터의 문턱전압 이동 시뮬레이션 방안

# 정태호<sup>1,a</sup>

<sup>1</sup> 서울과학기술대학교 전자IT미디어공학과

# Simulation Method of Threshold Voltage Shift in Thin-film Transistors

## Taeho Jung<sup>1,a</sup>

<sup>1</sup> Department of Electronic and IT Media Engineering, Seoul National University of Science and Technology, Seoul 139-743, Korea

(Received April 21, 2013; Revised April 23, 2013; Accepted April 24, 2013)

Abstract: Threshold voltage shift caused by trapping and release of charge carriers in a thin-film transistor (TFT) is implemented in AIM-SPICE tool. Turning on and off voltages are alternatively applied to a TFT to extract charge trapping and releasing process. Each process is divided into sequentially ordered processes, which are numerically modeled and implemented in a computer language. The results show a good agreement with the experimental data, which are modeled. Since the proposed method is independent of TFT's behavior models implemented in SPICE tools, it can be easily added to them.

Keywords: Threshold voltage shift, Modeling, SPICE

# 1. 서 론

박막트랜지스터 (thin-film transistor, TFT)는 재료와 공정이 다양할 뿐만 아니라 플렉시블 기판 위에도 제작이 가능하기 때문에 많은 관심을 받아오고 있다 [1,2]. 특히 스마트폰과 같은 모바일 기기의 수요가 확대되면서 이러한 장점을 지닌 TFT에 대한 연구는 더욱 증가하였다. 이로 인하여 비정질 실리콘 (amorphous silicon, a-Si) 반도체나 유기 반도체, 금속산화물 반도체 등 다양한 재료가 개발되었으며 공

a. Corresponding author; taeho.jung@snut.ac.kr

Copyright ©2013 KIEEME. All rights reserved.

This is an Open-Access article distributed under the terms of the Creative Commons Attribution Non-Commercial License (http://creativecommons.org/licenses/by-nc/3.0) which permits unrestricted non-commercial use, distribution, and reproduction in any medium, provided the original work is properly cited.

정도 발전되어 소자의 성능에도 많은 향상이 이루어 졌다. 하지만 다양한 재료와 공정을 사용하더라도 많은 TFT에서 동작의 신뢰성을 떨어뜨리는 문턱전압 이동이 발생하는 것으로 보고되고 있다 [3-5]. 특별한 경우에 있어서 문턱전압 이동이 발생하지 않는 TFT가 보고되고는 있지만, 저온에서 제작되는 특성으로 인하여 반도체를 구성하는 원자나 분자 간의 정렬과결합력이 좋지 않아 문턱전압 이동의 문제를 완전히해결할 수는 없게 된다.

현재 널리 알려진 문턱전압 이동의 원인을 설명하는 분석모델은 주로 a-Si TFT를 기반으로 제작되었다 [6]. a-Si TFT에서는 결함생성과 전하포획 현상에의해 문턱전압 이동이 관측되었으며, 전자의 경우에SE (stretched exponential) 또는 SH (stretched hyperbola) 형태의 분석적 수식이 유도되었다.

$$\Delta \ V_{th}(t) = \Delta \ V_{th}(\infty) \bigg\{ 1 - \exp \bigg[ - \bigg( \frac{t}{\tau} \bigg)^{\beta} \bigg] \bigg\} \eqno(1)$$

$$\Delta V_{th}(t) = \Delta V_{th}(\infty) \left\{ 1 - \left[ 1 + \left( \frac{t}{\tau} \right)^{\beta} \right]^{\frac{1}{1-\alpha}} \right\}$$

(2)

여기서 a는 1과 2 사이의 상수이고  $\beta$ 는 시간에 의존적인 상수,  $\tau$ 는 시상수이다. 이 모델들은 현재 다양한 TFT들에서 관측되고 있으며, 전하포획 현상도 이모델들로 설명되고 있다 [5,7].

문턱전압이 불안정하면 회로를 설계하는 데 문제가되며 신뢰성이 떨어지게 된다. 다행히 현재 TFT가주로 사용되는 디스플레이는 고유한 동작 조건 [8]을 가지고 있으며, 이 조건 하에서 문턱전압 이동의 크기는 SE 또는 SH 모델들과 같이 시간에 따라 단순증가하는 모습을 보이기 때문에 적절한 보상 방안이마련되고 있다 [8]. 하지만, TFT들에서는 문턱전압이동의 크기가 작아지는 회복 현상도 [5,9-11] 발생하기 때문에 다양한 분야에 TFT를 적용하는 것은 단순한 문제가 아니게 된다. InGaZnO TFT에서 회복기간 동안 발생하는 문턱전압 이동은 다음과 같이 보고되었다 [5].

$$\Delta V_{th}(t) = \Delta V_{th}(0) \left\{ \exp\left[-\left(\frac{t}{\tau}\right)^{\beta}\right] \right\}$$

(3)

여기서  $\Delta V_{th}(0)$ 은 회복 기간이 시작되는 시점까지 발생한 문턱전압 이동이다. 문턱전압의 회복은 여러 TFT들에서 발생하지만, 정확한 분석모델이 만들어진 경우는 그리 많지 않다. 더욱이 회복 기간을 측정하는 절차가 TFT에 다른 레벨의 전압 스트레스를 제공하는 것도 문제를 복잡하게 만들고 있다.

TFT의 응용분야를 확장하기 위해서는 회로 설계시 문턱전압 이동 현상을 고려한 시뮬레이션이 반드시필요하다. 최악의 경우 (worst-case)를 가정한 시뮬레이션 기법을 설계에 적용하여 신뢰성을 확보할 수 있으나, 회로의 크기가 크거나 복잡한 경우 시뮬레이션이 용이하지 않거나 정확도가 낮아질 수 있다. 이 외에 기존의 실리콘 기반 시뮬레이션에 사용되는 동작시간에 기반을 둔 신뢰성 분석 기법 [12]을 적용할 수도 있다. 이러한 시뮬레이션 방법들을 현재까지 사용되어 왔고, 그 효용성을 입증해 왔으나, 고정된 문턱전압 파라미터를 가진 TFT 모델을 사용하기 때문에 문턱전압 파라미터의 수치를 변경하며 시뮬레이션을

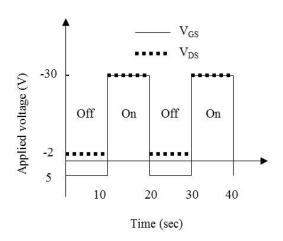

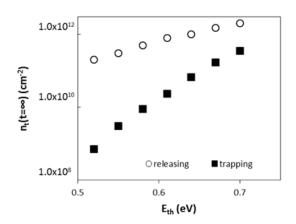

Fig. 1. Voltage patterns applied to a TFT.

여러 번 수행하여야 하는 단점을 가지고 있다. 만약 회로를 시뮬레이션하는 중간에 동작 환경에 맞도록 각 TFT들의 문턱전압 이동이 반영된다면 설계자의 수고가 줄어들 뿐 아니라 다양한 회로를 설계하고 시 험해 볼 수 있는 장점이 있다.

본 연구에서는 SPICE 시뮬레이션 툴로 TFT 회로를 시뮬레이션할 때 TFT의 구동 전압과 인가된 시간에 따라 문턱전압 이동이 실시간으로 시뮬레이션에 반영되는 방안을 마련하고자 한다. 수식 (1)과 (2)와같은 분석 모델은 구동 전압이 변할 때에 문턱전압이동을 예측할 수 없을 뿐만 아니라 [13] 일반적인 TFT에도 적용할 수 없으므로 [14], 본 연구에서는 수식 모델 [13]을 사용하여 시간에 따른 구동 전압의변화를 반영하는 방법을 마련하고 실제 시뮬레이션툴인 AIM-SPICE에 구현하여 실측치와 비교한다.

## 2. 실험 방법

# 2.1 TFT 제작 및 측정

본 실험에 사용된 펜타센 TFT는 3,000 Å의 SiO<sub>2</sub> 절연체 박막이 열적으로 형성된 실리콘 기판위에 제작 되었다. 펜타센 박막은  $2\times10^{-6}$  Torr의 압력에서  $0.2\sim0.5$  Å/s의 속도로 thermal evaporation 방법으로 증착하였으며, 300 Å 두께가 되도록 하였다. 소스와 드레인 전극은 쉐도우 마스크를 사용하여 제작하였으며, 500 Å 두께의 금을 증착시켰다. 채널의 길이와

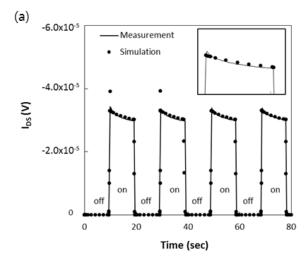

Fig. 2. (a) Drain current when time varying voltages are applied. The inset is the drain current during the third "on" state. (b) drain current in "off" states.

넓이는 각각 80 µm와 800 µm이다. TFT에 발생하는 스트레스 효과는 게이트 전극에 그림 1과 같이 -30 V와 5 V를 번갈아 인가할 때 드레인 전류에 발생하는 변화로 측정하였다. 게이트 전압과 드레인 전압이 -30 V일 때 TFT는 "on" 상태가 되어 채널 내에 유도된 정공들이 포획되기 시작하고 문턱전압이 변하기시작한다. 10초 간의 "on" 상태가 끝나면 게이트 전압에는 5 V를 드레인 전압에는 -2 V를 10초 간 인가하여 TFT를 "off" 상태로 만들어 포획된 정공을 회수하도록 한다.

#### 2.2 이론적 배경

본 연구에서는 전하의 포획과 방출에 의한 문턱전

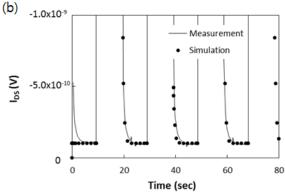

Fig. 3. Time dependent threshold voltage shift.

압 이동 현상을 시뮬레이션 툴에 구현하기 위하여 프로그래밍이 가능한 수치 모델을 사용한다 [13,14]. 전하의 포획과 방출 현상은 결함 생성 현상 [11]처럼 반응속도 식 (rate equation)으로 기술할 수 있다 [7,15].

$$\frac{n_t}{dt} = R_f n_s (N_t - n_t) - R_b (N_s - n_s) n_t \tag{4}$$

여기서  $R_f$ 와  $R_b$ 는 전하 포획과 방출에 대한 반응계수이고,  $n_t$ 은 트랩된 전하밀도,  $n_s$ 은 채널 내의 전하밀도,  $N_s$ 는 채널의 상태 밀도,  $N_t$ 는 트랩 사이트 밀도이다. 채널 내의 전하 포획과 방출 반응에 적용되는 식 (4)는 거시적인 관점에서 기술한 운동 메커니즘으로서 프로그래밍이 가능한 형태로 변형하기 위해서는 상호 의존적인 계수들을 포함하는 미분방정식을 풀어야하는 복잡한 절차를 거쳐야 한다 [15]. 본 연구에서는 미분 방정식의 해를 수치적으로 구하는 접근방법이 아니라 거시적인 운동 메커니즘인 수식 (4)를이산적인 운동 메커니즘으로 분해하여 수치 모델로변환하는 방안을 사용한다 [13]. 따라서 수식 (4)는다음과 같이 이산적으로 기술되는 반응 속도 식들의합으로 구성된다.

$$\frac{n_{t,i}}{dt} = R_{f,i} n_{s,i} (N_{t,i} - n_{t,i}) - R_{b,i} (N_{s,i} - n_{s,i}) n_{t,i}$$

(5)

여기서 첨자 i는 각 반응 속도 식들을 구분하는 구분자이다. 수식 (5)의 운동 메커니즘은 전하의 포획과 방출에 대한 것이므로, 결합생성 반응에서의 에너지

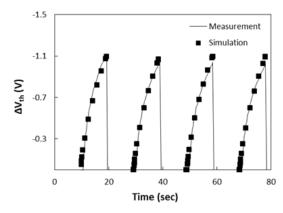

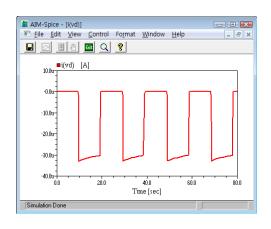

**Fig. 4.** The distribution of  $n_t(t=\infty)$  for trapping and releasing processes.

장벽 [11,15]과 유사하게 반응 계수들에 필요한 에너지는 전하의 이동에 연관된 의미를 갖는다. 즉, 전하의 터널링이나 열이온 방출 (thermionic emission)에 관련된 에너지 장벽이 반응 계수들의 크기를 결정하게 된다. 각 이산적인 포획과 방출 반응들이 독립적이라고 가정하고, 고유한 에너지 장벽에 대한 반응계수도 고유한 값을 갖는 것으로 가정하면 식 (5)에 대한 해는 다음과 같이 얻을 수 있다 [13].

$$n_{t,i}(t) = n_{t,i}(\infty) + \left[ n_{t,i}(0) - n_{t,i}(\infty) \right] \exp \left( -\frac{t}{\tau_i} \right) \ (6)$$

여기서  $n_{t,i}(\infty)$ 는 주어진 에너지 장벽에 대한 문턱 전압 이동이 더 이상 발생하지 않을 시간 (steady-state)에서의 포획된 전하 밀도이고,  $n_{t,i}(0)$  새 로운 전압이 인가되는 시점에 이미 포획된 전하 밀 도,  $\tau_i$ 는 에너지 장벽을 포함하는 시정수이다. 시뮬레 이션 코드에 구현되는 것은 수식 (6)이며, 에너지 장 벽에 연관된 시상수의 개수만큼 수식 (6)의 인스턴스 를 만들게 된다 [13]. 이 방법은 SE 모델을 분석하였 을 때 라플라스 변환 [16]과 유사한 개념이지만, 미분 방정식의 해들인 수식 (6)들이 서로 직교하지 않는 점이 다르다. 따라서 정확한 시뮬레이션을 위해서는 수식 (6)의 인스터스들을 많이 사용하되, 인스턴스들 이 담당하는 트랩 부분들 간의 중첩을 최소화하여야 한다.

문턱전압의 회복, 즉 전하의 방출 과정은 식 (4)에  $R_b$ 로 이미 포함되어 있기 때문에 본 연구에서 사용하

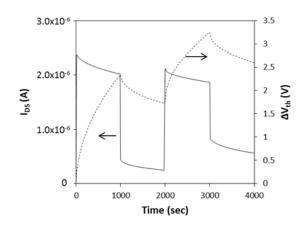

Fig. 5. Simulation result.

는 수치 모델링에서는 분석 모델 [5]와 같이 독립적인 수식을 필요로 하지 않는다. 하지만, 전압 인가 조건에 따라서 트랩 밀도  $N_t$ 를 포함하는 식 (6)의  $n_{t,i}$   $(\infty)$ 를 변경해 주어야 한다. 실제 회로에서는 TFT에다양한 전압이 연속적으로 구동되므로  $n_{t,i}(\infty)$ 의 값도연속적으로 갱신해 주어야한다. TFT는 소스-드레인과 소스-게이트 전압에 의해 구동되며 이에 대한 트랩 밀도의 물리적 모델이 마련되어 있지 않으므로 본연구에서는 일차적으로 두 개의 구동 전압 조건만을사용하여 문턱전압 이동을 시뮬레이션으로 구현한다. 구동 전압 조건은 그림 1에 표시된 바와 같다 [5].

### 2.3 모델링

TFT에서 측정된 드레인 전류는 그림 2에 표시되었다. TFT 내에 존재할 수 있는 포획된 전하를 없애기 위하여 "off" 상태에서부터 전압을 인가하였다. "on" 상태에서는 드레인 전류의 감소가 관측되었으며, 이는 채널 전류를 이루는 정공이 포획되어 발생하는 것이다. "on" 상태가 장기간 유지되면 문턱전압 이동의 효과는 더욱 커지게 된다 [14]. 이 소자를 위한 공정의 최적화가 이루어지지 않았기 때문에 SE 또는 SH 형태의 문턱전압 이동이 관측되지는 않는다.

"off" 상태에서는 누설전류가 흐르게 되며, 이 부분의 측정 결과는 그림 2(b)에 표시하였다. "off" 상태에서의 누설전류도 시간에 따라 감소하는 현상을 보이고 있다. 누설전류의 감소의 원인은 두 가지로 추측할 수 있다. 첫째는 추가적인 전자나 정공의 포획이다. 하지만, 뒤따라오는 "on"과 "off" 상태에서 일종의

누적효과가 관측되지 않으므로 "off" 상태에서는 추가적인 포획현상은 발생하지 않는 것을 알 수 있다. 오히려 이 전의 "on" 상태에서 발생한 정공의 포획 효과가 다음 번 "on" 상태에서 없어지는 것을 보아 "off" 상태에서는 포획된 정공이 방출되는 것을 알 수 있다. 누설전류를 구성하는 성분은 불순물에 의한 도핑효과로 발생하는 채널 전류일 수 있고 벌크로 흐르는 전류 등 다양한 원인이 있다. 본 연구의 주제는물리적 해석 보다는 관측된 전류의 양상을 구현하는 것이므로 누설전류가 특정 값으로 수렴하는 고정 성분과 포회된 전하 양에 의존하는 시변 성분으로 구성되는 것으로 모델링하였다. 또한 누설전류의 시변 성분은 시간에 따라 감소하기 때문에 그 양이 포획된 정공의 양에 비례하는 것으로 가정하였다.

$$I_{off}(t) = I_{off,0} + I_{off,nt}(t) = I_{off,0} + kn_t(t)$$

(7)

$$I_{DS} = \begin{cases} I_{off} & V_{GS} < V_{th} \\ K \left( V_{GS} - V_{th} - \frac{V_{DS}}{2} \right)^2 V_{DS} V_{DS} < V_{DSAT} \\ \frac{K}{2} \left( V_{GS} - V_{th} \right)^2 & V_{DSAT} < V_{DS} \end{cases}$$

(8)

여기서  $I_{off,nt}(t)$ 는 시변 성분이며, k는 비례상수이다. 그림 3에 드레인 전류에서 추출한 문턱전압 이동을 표시하였다. "on" 상태들에서 문턱전압 이동은 "off" 상태에서 초기화되는 것을 알 수 있다. "off" 상태에 서는 포획된 정공들이 방출되는 것이므로 수식 (7)을 사용하여 시간에 따른 방출된 전하의 양을 계산할 수 있게 된다. SPICE 시뮬레이션에 측정된 문턱전압 이 동을 구현하기 위해서는 수식 (6)의 인스턴스를 만들 어야 한다 [14]. 본 연구에서 한 구간에 사용된 시간 은 10초이므로 10<sup>10</sup> Hz의 주파수에서 열화 에너지 (thermalization energy) [11]로 변환하였을 때 6.6 eV 가 된다. 따라서 0.52 eV에서 0.03 eV 간격으로 총 7 개의 시정수를 만들어 수식 (6)의 인스턴스에 할당하 였다. 7개 인스턴스의 를 조절한 결과는 그림 4에 표 시하였다 [13]. SPICE에 구현하기 위하여 7개 인스터 스들의 계수들을 입력파라미터로 사용할 수 없으므로 근사식을 활용하였다 [14].

그림 4에서 트랩 사이트 밀도  $N_t$ 를 표시하는 가 같은 경우에 대하여 전하의 포획과 방출 시정수에 차이가 발생함을 볼 수 있다. 즉, 전하의 포획에 과정에서 발생한 시정수가 방출 과정에서는 줄어드는 것으로

예측할 수 있다. 이는 방출 반응이 포획 반응보다 빨리 진행되는 것을 뜻한다. TFT를 AIM-SPICE에 구현하기 위하여 Shockley의 1차 트랜지스터 모델을 수정하고 문턱전압 이동 모델을 결합하였다 [14].

# 3. 결과 및 고찰

"on"과 "off" 상태의 인가 전압들에 대하여 AIM-SPICE에서 시뮬레이션한 결과는 그림 5에 나타 내었으며, 측정치와의 비교는 그림 2와 3에 각각 표 시하였다. 그림 2(a)에서 TFT가 "on" 상태일 때 시 뮬레이션 결과는 원본 데이터와 매우 일치함을 볼 수 있다. 그림 2(b)에서 첫 번째 "off" 상태에서는 실험치 와 차이가 발생하는 것을 알 수 있다. 첫 번째 "off" 상태에서 실제 TFT에서 전하들이 방출된 이유는 TFT가 이미 여러 차례의 측정 절차를 거쳤기 때문 에 트랩에 전하들이 남아 있었기 때문이다. 반면 시 뮬레이션에 사용된 TFT 모델의 트랩들은 초기에 비 어있는 상태였으며, 이로 인하여 수식 (7)에서 설정한 고정 전류가 흐르도록 되었다. "off" 상태의 전류는 측정치와 대체적으로 일치하는 것을 알 수 있다. 시 뮬레이션 결과와는 다르게 측정치는 "off" 상태의 초 반에 변화가 주로 발생하며, 이 차이는 수식 (7)에서 전류와 포획된 전하의 양의 관계를 일차식으로 간단 히 모델링한 결과이며, SPICE 입력 파라미터를 단순 화하기 위하여 의 분포를 계산할 때 추세선 사용했기 때문이다 [14]. "off" 상태에 대한 보다 정확한 물리적 해석이 이루어지면 그림 2(b)에 나타난 차이가 더욱 줄어들 것이다.

측정치와의 문턱전압 이동에 대한 비교는 그림 3에 표시하였다. 문턱전압 이동의 크기는 포획된 전하의 양과 비례하므로 시뮬레이션 상에서도 "off" 상태에서 포획된 전하들이 모두 방출되고 있음을 알 수 있다.

본 시뮬레이션 방법의 확장성을 확인하기 위하여 전하의 포획과 방출 반응이 전형적인 SE 형태의 문 턱전압 이동 모델인 경우도 AIM-SPICE에 구현하였 다. "on"과 "off" 상태를 교차로 인가할 때의 구동조 건에서 시뮬레이션을 수행하였으며 그림 6에 결과를 표시하였다. 시뮬레이션 결과는 InGaZnO TFT에서 측정된 결과 [5]와 유사하게 나타났다.

시뮬레이션 결과들에서 볼 수 있듯이 문턱전압 이동이 수식 (6)으로 모델링될 수 있는 이유는 전압 인가에 따라 트랩 사이트의 개수에 변화가 생기지 않았

**Fig. 6.** Simulation result from the stretched-exponential time dependent threshold voltage shift model implemented in AIM-SPICE.

기 때문이다. 이는 본 연구에서 사용한 TFT와 InGaZnO TFT [5]에서 전하 포획과 방출 반응이 마코비안(Markovian) [10]인 것을 뜻한다. 따라서 다양한 구동 전압에서의 문턱전압 이동 결과를 모두 모델링하여 결합하면 일반적인 조건에서도 시뮬레이션이가능함을 보여준다.

#### 4. 결 론

본 연구에서는 전하의 포획과 방출 현상으로 인하여 발생하는 문턱전압 이동이 드레인 전류에 주는 영향을 AIM-SPICE 툴에 구현하였다. 구동 전압이 연속적으로 변할 때 트랩 밀도가 변하는 모델이 완성되어 있지 않으므로 본 연구에서는 1개의 전하 포획 상태와 1개의 전하 방출 상태를 사용하여 TFT의 동작모델을 구현하였다. 시뮬레이션 결과는 모델링하고자하는 측정치와 전반적으로 일치함을 확인하였다. 본연구에서 제안하는 시뮬레이션 방식은 TFT의 거동 모델과는 독립적이므로 기존의 RPI (rensselaer polytechnic institude)의 a-Si TFT 모델 등에도 결합이 가능하다.

#### 감사의 글

이 연구는 서울과학기술대학교 교내 학술연구비 지 원으로 수행되었습니다.

#### **REFERENCES**

- [1] H. Klauk, Chem. Soc. Rev., 39, 2643 (2010).

- [2] J. S. Park, W. J. Maeng, H. S. Kim, and J. S. Park, Thin Solid Films, 520, 1679 (2012).

- [3] J. H. Kang, C. E. Kim, P. Moon, and I. Yun, *IEEE Trans Dev. Mater. Reliab.*, **11**, 112 (2011).

- [4] Y. R. Liu, R. Liao, P. T. Lai, and R. H. Yao, *IEEE Trans Dev. Mater. Reliab.*, **12**, 58 (2012).

- [5] I. T. Cho, J. M. Lee, J. H. Lee, and H. I. Kwon, *Secmicond. Sci. Technol.*, **24**, 1 (2008).

- [6] W. B. Jackson, J. M. Marshall, and M. D. Moyer, Phys. Rev. B, 39, 1164 (1989).

- [7] A. A. Fomani and A. Nathan, J. Appl. Phys., 109, 084521 (2011).

- [8] C. L. Fan, Y. Y. Lin, B. S. Lin, J. Y. Chang, C. L. Fan, and H. C. Chang, J. Kor. Phy. Soc., 56, 1185 (2010).

- [9] G. Gu, M. G. Kane, and S.-C. Mau, J. Appl. Phys., 101, 014504 (2007).

- [10] S. Sambandan, L. Zhu, D. Striakhilev, P. Servati, and A. Nathan, *IEEE Elec. Dev. Lett.*, **26**, 375 (2005).

- [11] S. C. Deane, R. B. Wehrspohn, and M. J. Powell, Phys. Rev. B, 58, 12625 (1998).

- [12] X. Li, J. Qin, B. Huang, X. Zhang, and J. B. Bernstein, IEEE Trans. Dev. Mater. Reliab., 6, 247 (2006).

- [13] T. Jung, Proc. 6th Int. Conf. on Convergence and Hybrid Information Technology (eds. G. Lee, D. Howard, J. J. Kang, and D. Slezak) (Daejeon, Korea, 2012) p. 453.

- [14] T. Jung, J. KIEEME, 26, 92 (2013).

- [15] R. B. Wehrspohn, M. J. Powell, and S. C. Deane, J. Appl. Phys., 93, 5780 (2003).

- [16] S. Zafar, A. Callegari, E. Gusev, and M. V. Fischetti, J. Appl. Phys., 93, 9298 (2003).