# 3상 Z-소스 PWM 정류기의 입력 AC 전압 센서리스 제어

# Input AC Voltage Sensorless Control for a Three-Phase Z-Source PWM Rectifier

한 근 우\*·정 영 국<sup>†</sup>·임 영 철\*\* (Keun-Woo Han·Young-Gook Jung·Young-Cheol Lim)

Abstract - Respect to the input AC voltage and output DC voltage, conventional three-phase PWM rectifier is classified as the voltage type rectifier with boost capability and the current type rectifier voltage with buck capability. Conventional PWM rectifier can not at the same time the boost and buck capability and its bridge is weak in the shoot- through state. These problems can be solved by Z-source PWM rectifier which has all characteristic of voltage and current type PWM rectifier. By shoot-through duty ratio control, the Z-source PWM rectifier can buck and boost at the same time, also, there is no need to consider the dead time. This paper proposes the input AC voltage sensorless control method of a three-phase Z-source PWM rectifier in order to accomplish the unity input power factor and output DC voltage control. The proposed method is estimated the input AC voltage by using input AC current and output DC voltage, hence, the sensor for the input AC voltage detection is no needed. comparison of the estimated and detected input AC voltage, estimated phase angle of the input voltage, the output DC voltage response for reference value, unity power factor, FFT(Fast Fourier Transform) of the estimated voltage and efficiency are verified by PSIM simulation.

**Key Words**: Z-source PWM rectifier, Modified space vector modulation, Input AC voltage sensorless control, Modulation index, Unity input power factor, Output DC voltage control

#### 1. 서 론

최근 산업계에서 사용되는 전력전자기기에 대한 DC 전압 공급은 갈수록 중요한 비중을 차지하고 있다. 기존의 AC/DC 전력변환장치는 위상제어 컨버터나 출력 전압을 제어할 수 없는 다이오드 정류기가 주로 사용되어 왔다. 이러한 변환장치들은 AC 전원 단에서 저차 고조파의 발생 및역률 저하 등의 문제점을 가진다. 80년대 초 이후 전류와전압의 제어루프를 통한 고역률 AC/DC 컨버터 제어기를 제안한 이후 최근에는 단위 역률 등을 구현하는 3상 PWM 정류기에 대한 연구가 활발히 진행되어 산업계에 적용되고 있다[1-3].

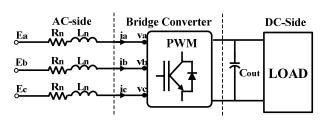

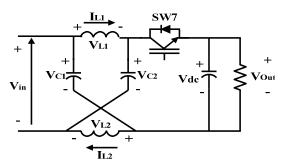

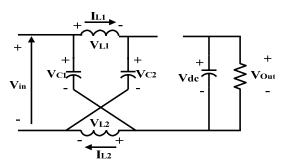

3상 PWM 정류기는 주어진 입력 AC전압에 대해 출력 DC전압의 승압 및 강압의 목적에 따라 크게 승압형 전압형 정류기와 강압형 전류형 정류기로 나눌 수 있다[4-6]. 그림 1(a)는 전압형 정류기를 나타내고 있으며, 항상 입력 전압에 대하여 출력 전압이 승압된다는 특성을 가지고 있다. 그림 1(b)는 전류형 정류기를 나타내고 있다.

인덕터에 전류를 축적하여 변환하는 이 정류기는 출력 단 에 직렬로 인덕터가 연결되어 있으며, 스위치의 듀티비를 이

E-mail: jyg@db.ac.kr

Received: December 24, 2012; Accepted: February 27, 2013

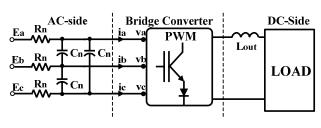

용한 전력변환이 가능하다. 기본동작 특성은 전압원 정류기와 반대로 출력 전압은 항상 입력 전압과 같거나 강압된다. 또한 출력전압을 다양하게 제어하기 위해서는 그림 2와 같은 승압 또는 강압형 컨버터가 별로도 필요하며, 스위치 동작 시 일어나는 암 단락(shoot-through state)은 스위치 소자에 손상을 발생하므로 정류기 브리지의 스위치에 데드타임이 필요하다.

(a) Voltage source rectifier

(b) Current source rectifier

그림 1 일반적인 PWM 정류기 Fig. 1 Traditional PWM rectifier

<sup>\*</sup> Dept. of Electrical Engineering, Chonnam National University, Korea

<sup>\*\*</sup> Dept. of Electrical Engineering, Chonnam National University, Korea

<sup>†</sup> Corresponding Author: Dept. of Electrical Engineering, Daebul University, Korea

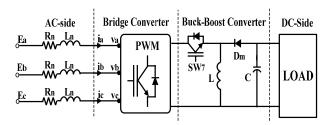

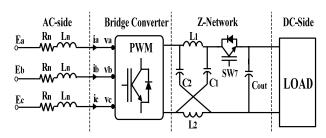

이러한 문제점들을 해결하기 위하여 Z-소스 PWM 정류기[4-6]가 제시되었다. 일반적인 PWM 정류기와 달리 L-C 조합된 Z-소스 네트워크를 이용하기 때문에 한 대의 정류기만으로 전압형 및 전류형 정류기 특성을 발휘할 수 있다.

따라서 추가적인 승압/강압 컨버터와 입력 전압의 가변 없이 원하는 출력 DC전압을 얻을 수 있다. 또한 브리지 컨버터 스위치의 암 단락 시간을 이용하므로 데드타임이 필요하지 않다[7]. Z-소스 PWM 정류기 시스템은 외부 전압제어 루프와 내부 전류제어 루프로 구성되며, 출력 전압제어를 위해 직류전압 검출, 전류제어를 위한 입력전류 검출이 필요하고, 전류 지령치를 생성하기 위한 입력 전압 검출 또한 필요하다.

그림 2 승-강압 기능을 갖는 2단 PWM 정류기

Fig. 2 Two-stage PWM rectifier with buck-boost capability

본 논문에서는 센서리스[8-15] 입력전압 제어 기반의 3상 Z-소스 PWM 정류기를 제안한다. 제안된 방법은 입력 단AC 전압센서 없이 입력 AC전류 센서와 DC단 전압 센서만을 이용하여 입력 AC전압을 추정하고 단위 입력역률을 구현한다. 이를 위해 수정된 공간벡터 변조방식(MSVPWM)을 적용하고, 추정된 입력전압과 검출된 입력전압의 위상각과 파형을 비교하고, 입력역률 제어와 기준치에 대한 출력전압의 응답과 추정된 전압의 FFT분석을 한다. 본 연구의 타당성은 PSIM 시뮬레이션을 통하여 입증을 하고자 한다.

## 2. 3상 Z-소스 PWM 정류기

## 2.1. 정류기 모델링

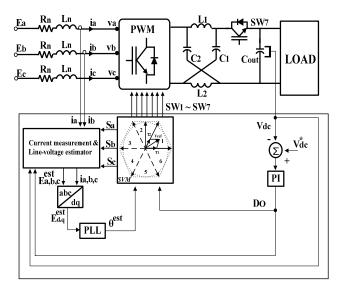

그림 3은 3상 Z-소스 PWM 정류기를 나타내며, 일반적인 PWM 정류기와 다르게 Z-임피던스 네트워크( $L_1$ ,  $L_2$ ,  $C_1$ ,  $C_2$ ) 와 직류단 스위치 SW $_7$ 로 구성되어 있다[4-6].

**그림 3** 3상 Z-소스 PWM 정류기

Fig. 3 Three-phase Z-source PWM rectifier

그림 3에 대한 a상 전압 방정식은 식 (1)과 같다. 여기서, Ea는 입력 상전압, ia는 상전류를 나타내며, va는 계통의 중성점 사이에 걸리는 각 상의 전압이다. 또, Ln, Rn은 교류측인덕터와 저항, Cout 과 LOAD는 직류 측 커패시터와 DC 부하를 나타낸다.

$$E_a = R_n i_a + L_n \frac{di_a}{dt} + v_a \tag{1}$$

이로부터 우변 제 3항의 브리지 입력 상전압은 식 (2)와 같이 표현된다.

$$v_{a} = (\frac{2}{3}S_{a} - \frac{1}{3}(S_{a} + S_{b} + S_{c})) V_{dc}$$

(2)

여기서,  $S_a$ ,  $S_b$ ,  $S_c$ 는 각 상의 스위칭 상태이며, 스위치가 온 될 때는 1, 오프일 때는 0이 된다. 3상 Z-소스 PWM 정류기에 스위칭 패턴은 기존 PWM 정류기와 달리 6개의 유효 벡터와 2개의 영벡터 그리고 추가된 영벡터를 포함하여 9개의 스위칭 패턴으로 구성된다. 추가된 영벡터는 직류단 스위치  $SW_7$ 이 차단 상태일 경우 발생한다.

(a) Active state

(b) Shoot-through state

그림 4 비 암단락 및 암단락 모드

Fig. 4 Active state (non shoot-through state) and shoot-through state

그림 4는  $3 \mbox{V} - 2 \mbox{V} - 2 \mbox{V} - 2 \mbox{PWM}$  정류기 동작 모드를 나타내고 있다. 동작은 비 암단락(non shoot-through state, active state)모드와 암단락(shoot-through state) 모드로 구분 할 수 있다. 동일 암에 위치한 두 스위치의 비 암 단락 시간  $(T_R)$  동안은 그림 4(a)와 같은 모드를 가지며, 이 기간 동안

Z-소스 PWM 정류기는 전압형 정류기와 같게 동작한다. 이 때 Z-네트워크에 인가되는 입력 DC전압 $(V_{in})$ 과 출력 DC전 압 $(V_{dc})$ 은 같으며 스위치  $SW_7$ 은 도통 상태가 된다. 동일 암에 위치한 두 스위치가 암 단락되는 시간 $(T_D)$  동안에는 그림 4(b)와 같은 모드가 형성된다. 이 경우 Z-네트워크에 인가되는 입력 DC전압 $(V_{in})$ 은 출력 DC전압 $(V_{dc})$  보다 높은 전압으로 인가되고 스위치  $SW_7$  차단 상태가 된다.

동작 모드시 인가되는 인덕터 평균전압  $V_L$ 과 커패시터에 인가되는 평균 전압 $V_C$ 는 식 (3), (4)과 같다.

$$V_{L} = \frac{T_{D}V_{C} + T_{R}(V_{IN} - V_{C})}{T_{s}} = 0 \tag{3}$$

$$V_{C} = \frac{T_{R}}{T_{R} - T_{D}} V_{IN} = \frac{1 - \frac{T_{D}}{T_{S}}}{1 - 2\frac{T_{D}}{T_{S}}} V_{IN} \tag{4}$$

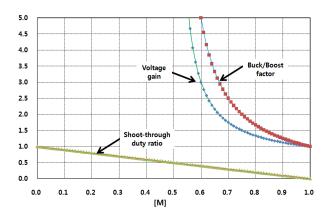

브리지 컨버터에 다이오드와 Z-소스 네트워크의 커페시터를 통하여 전류 루프가 형성된 암 단락 상태에서는 Z-소스 PWM 정류기는 출력 전압을 승압 또는 강압을 할 수 있으며, 식(5), (6) 같이 표현된다[16]. Z-소스 PWM정류기의 상전압의 최대치( $E_{pk}$ )는 식(5)와 같으며, 종전의 PWM 정류기와 다르게 출력전압( $V_{dc}$ )과 승/강압률(B), 변조지수(M) 그리고 암 단락 지수( $D_{o}$ )가 정의된다. 식 (6)은 승/강압율(B)와 전압 게인(G)를 나타낸다. 여기서  $T_{S}$ 는 스위칭 주기이며,  $T_{7}$ 은 스위치  $SW_{7}$ 의 스위칭 시간을 나타낸다. 또한 Z-소스 정류기 DC-link 전압은 식 (7)과 같이 나타낼 수 있다.

$$E_{pk} = M \frac{V_{dc}}{2} B, \quad M = 1 - D_o$$

(5)

$$B = \left(2\frac{T_7}{T_S} - 1\right) \le 1, \ G = \frac{E_{pk}}{\frac{V_{de}}{2}} = MB$$

(6)

$$V_{dc} = \left(2\frac{T_7}{T_S} - 1\right) \cdot \frac{2E_{pk}}{\cos\Psi} = B\frac{2E_{pk}}{\cos\Psi} , \quad (\Psi = \tan^{-1}\frac{wL_n}{R_n})$$

(7)

3상 Z-소스 PWM 정류기의 정상상태 모델링은 식(7)과 같이 나타낼 수 있다. 모델링 방정식은 크게 Z-소스 임피던스 네트워크( $L_1$ = $L_2$ , $C_1$ = $C_2$ )와 상전압과 상전류 그리고 DC-link 커패시턴스로 구성이 되어있다. 여기서  $L_n$ ,  $R_n$ 은 교류측 인덕터와 저항,  $C_{out}$ 는 DC-link 커패시터, L과 C는 Z-소스 네트워크의 인덕터와 커패시터 요소이다.  $i_{abc}$ ,  $v_{abc}$ 는 각각 선간전류와 선간전압을 나타낸다.  $V_{Cout}$ 는 DC-link 전압 ,  $R_{Load}$ 는 부하저항이다.  $v_c$ ,  $i_L$ 은 Z-소스 네트워크에 인가되는 커패시터 전압과 인덕터 전압이다. 끝으로  $v_c$ 는 각선간전압의 듀티 사이클,  $v_c$ 는 암단락 (shoot-through state)시의 듀티비이다.

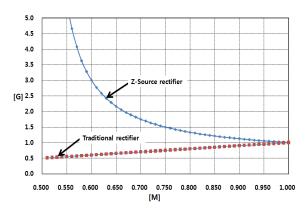

그림 5는 Z-소스 PWM 정류기와 종전의 PWM 정류기의 제어방식에 따른 전압 게인을 비교한 그래프이다. 전압 게인은 변조지수에 따라서 가변되는 것을 볼 수 있다. 종전의 PWM 정류기에 경우, 변조지수 증가에 비례하여 전압 게인이 선형적으로 증가되나, Z-소스 PWM 정류기는 변조지수에 따라서 지수 함수적으로 전압 게인을 제어 할 수 있다.

그림 5 변조지수 M에 따른 각 방식의 전압 게인 비교

Fig. 5 Voltage gain comparison of each method according to M

이는 L-C조합 Z-소스 네트워크의 단락 시간을 제어하여 승압 및 강압의 특성을 모두 이용할 수 있기 때문이다. 이상의 특성은 그림 6과 같이 Z-소스 PWM 정류기의 변조 지수 변화에 대한 제어변수 특성으로 살펴 볼 수 있으며, 식(5)~(6)으로 나타낼 수 있다.

그림 6 변조지수 변화에 따른 Z-소스 PWM 정류기의 제어 변수의 비교

Fig. 6 Comparison of the control parameters of Z-source PWM rectifier according to M

$$\begin{aligned} \frac{di_{ab}}{dt} &= \frac{v_{ab}}{3L_n} - \frac{(2v_c - v_{Cout})d_{ab}}{3L_n} - \frac{i_{ab}R_n}{L_n} \\ \frac{di_{bc}}{dt} &= \frac{v_{bc}}{3L_n} - \frac{(2v_c - v_{Cout})d_{dc}}{3L_n} - \frac{i_{bc}R_n}{L_n} \\ \frac{di_{ca}}{dt} &= \frac{v_{ca}}{3L_n} - \frac{(2v_c - v_{Cout})d_{ca}}{3L_n} - \frac{i_{ca}R_n}{L_n} \\ \frac{di_{L}}{dt} &= \frac{v_c(1 - 2d_{ST})}{L} - \frac{v_{Cout}(1 - d_{ST})}{L} \\ \frac{dv_c}{dt} &= \frac{(d_{ab}i_{ab} + d_{bc}i_{bc} + d_{ca}i_{ca})(1 - d_{ST})}{C} - \frac{i_L(1 - 2d_{ST})}{C} \\ \frac{dv_{Cout}}{dt} &= \frac{2i_L(1 - d_{ST})}{C_{out}} - \frac{(d_{ab}i_{ab} + d_{bc}i_{bc} + d_{ca}i_{ca})(1 - d_{ST})}{C_{out}} \\ - \frac{v_{Cout}}{R_{Load}C_{out}} \end{aligned}$$

#### 2.2. 단위역률 동작

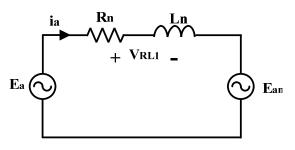

그림 7은 정상상태에서 A상의 등가회로를 나타내며,  $E_{\rm an}$ 은 컨버터 브리지에서 인가되는 필스형태의 전압의 기본파성분을 나타낸다. A상 전류  $i_a$ 는 입력 임피던스의 양단 전압인  $V_{\rm RLI}$ 보다 위상이 항상 식(9) 만큼 뒤진다. 그러므로 입력임피던스의 양단 전압  $V_{\rm RLI}$ 이 입력 상전압인  $E_a$ 보다  $\delta$ 만큼앞서도록 입력임피던스 양단 전압의 지령 전압을 식(10)과같이 유지시킨다면, 입력 상전압인  $E_a$ 와 상전류  $i_a$ 이 동위상이 되며 단위 입력역률이 실현된다.

$$\delta = \tan^{-1}(\frac{\omega L}{R}) \tag{9}$$

$$E_{an} = E_a - |V_{RL1}| \angle \delta \tag{10}$$

그림 7 한 상의 등가회로

Fig. 7 A-phase equivalent circuit

식(9), (10)을 이용하여 다른 상에 대해서도 적용하면, 식(11), (12)와 같이 된다.

$$E_{bn} = E_b \angle 120^{\circ} - |V_{RL2}| \angle (\delta + 120^{\circ})$$

(11)

$$E_{cn} = E_{c} \angle -120^{\circ} - |V_{RI3}| \angle (\delta - 120^{\circ})$$

(12)

## 3. 입력 전압 센서리스 제어

### 3.1. 입력 전압 추정

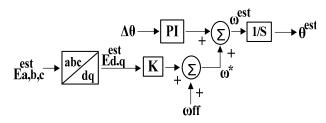

제안된 Z-소스 PWM정류기의 입력전압 센서리스 제어를 위하여 전류제어기, 입력 전압 추정기 그리고 위상각 추정기 가 구성되며, 전체 제어블록은 그림 8과 같이 표현된다.

여기서  $E^{\rm est}_{a,b,c}$ 는 추정된 입력 전압값,  $i_{a,b,c}$ 는 측정된 입력 전류값,  $E_{\rm dq}^{\rm est}$ 는 추정된 입력 전압의 전압에 대한 D-Q 변환 값이다.  $V_{\rm dc}$ 와  $V_{\rm dc}^*$ 는  $DC-{\rm link}$ 단 측정과 지령치  $D_{\rm O}$ 는  $DC-{\rm link}$ 전압제어기를 통하여 발생된 암단락 지수이다.  $\Theta^{\rm est}$ 는 추정된 입력전압과 PLL을 통하여 발생된 추정된 위상각이다

3상 입력 AC전원이 평형이라고 가정하면, 입력 AC전류는 식(13)과 같은 조건이 되므로, 검출된 두 상의 전류로부터 나머지 한 상의 전류를 구할 수 있다.

$$i_a + i_b + i_c = 0$$

(13)

출력 DC전압과 식 (1), (2)를 이용하면, 다음 수식으로 입력

AC전압을 추정 할 수 있다. 단 여기서, Sk=Sa+Sb+Sc 이다.

$$E_{a} = L_{n} \frac{di_{a}}{dt} + R_{n}i_{a} + S_{k}V_{dc} - \frac{V_{dc}}{3}(S_{a} + S_{b} + S_{c})$$

(14)

$$L_{n}\frac{di_{a}}{dt} = E_{a} - R_{n}i_{a} + S_{k}V_{dc} + \frac{V_{dc}}{3}(S_{a} + S_{b} + S_{c})$$

(15)

$$E_a^{est} = E_a \frac{D_o}{2D_c - 1} \tag{16}$$

**그림 8** Z-소스 PWM 정류기의 입력전압 센서리스 제어도

Fig. 8 Block diagram of sensorless input voltage control for Z-source PWM rectifier

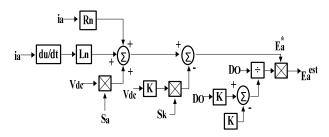

그림 9는 입력 AC전압 추정기의 제어 블록선도를 나타낸다. 검출된 상전류와 출력 DC전압 그리고 스위칭 함수로부터 입력 AC전압의 진폭 지령치  $E^*_{a}$ 를 생성한다. 지령 전압  $E^*_{a}$ 는 식 (14)로 부터 연산된 Z-소스 PWM정류기의 암단락 지수 $(D_a)$ 와 곱해져서 추정된 입력 전압  $E^{est}_{a}$ 를 발생시킨다.

그림 9 입력 전압 추정기의 제어 블록도

Fig. 9 Control block diagram of input voltage estimator

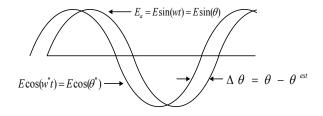

#### 3.2. 전압 위상각 동기

PWM 정류기의 입력전압 위상각은 계통과 연결을 이루는 컨버터 시스템의 동작을 위한 중요한 정보이다. 이러한 정보는 정지↔회전 좌표에 맞게 피드백하여 조정하거나, 유/무효전력의 흐름을 제어하는 목적으로 사용한다.

PLL 제어모델은 그림 10(a)와 같다. D-Q변환이 안정적으로

이루어졌다면 위상각  $\Theta$ 와 PLL출력  $\Theta^{est}$  사이의 오차  $\Delta\Theta$ 는 0이 되며,  $E_q^{est}$ =E,  $E_d^{est}$ =0이 된다. 시스템 안정을 위해서는  $E_d^{est}$ 의 값이 0값을 추정해야 하므로 D축을 위상의 에러 성분으로 보고 PI제어를 실행한다. PI 제어기를 통하여 출력된 값과 위상각 지령치  $\omega^*$ 와 연산하여 위상각  $\Theta^{est}$  가 도출되며, 그 정보를 통하여 계통전압이 동기 된다.

(a) Input phase voltage and PLL output

(b) Control model of the PLL system

그림 10 PLL을 이용한 동기각 추정

Fig. 10 Estimation of synchronous angle using PLL

식(17), (18)로 부터 식 (19)와 같이 위상각을 추정하고, 추정된 위상각 정보를 좌표 변환에 사용한다[12].

$$\begin{bmatrix} E_d^{est} \\ E_q^{est} \end{bmatrix} = \begin{bmatrix} -E_d^{est} \sin(\theta - \theta^{est}) \\ E_q^{est} \cos(\theta - \theta^{est}) \end{bmatrix}$$

(17)

$$\omega^{est} = -\left(K_{p+} \frac{K_i}{s}\right) \Delta\theta + \omega_{ff} \tag{18}$$

$$\theta^{est} = \frac{1}{s} \omega^{est} \tag{19}$$

$$\Delta\theta = \theta - \theta^{est} = \tan^{-1}\left(\frac{-E_{l}^{est}}{E_{l}^{est}}\right) \tag{20}$$

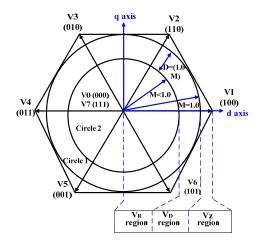

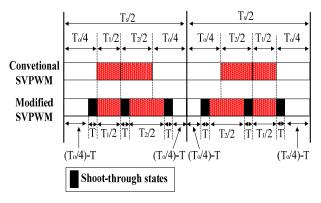

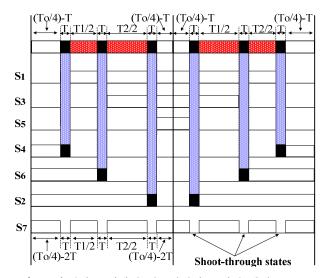

#### 3.3. 공간벡터 변조방식

공간벡터 변조방식은 높은 변조율과 고조파 함유율이 낮아 3상 전력변환 시스템에 많이 사용되고 있다. 그림 11(a)는 공간 벡터도를 나타내고 있다. 일반적인 공간벡터 변조방식(SVPWM)은 변조지수의 크기에 비례하는 기준 벡터  $V_R$ 과 영 벡터  $V_Z$ 로 구성된다.

그에 반해 3상 Z-소스 PWM정류기에 적용되는 수정된 공간벡터 변조방식(MSVPWM)은 최대 크기를 가지는  $V_R$ 의 크기( $Maximum\ V_R$ )를 변조지수 M=1과 같게 하고 그 M에 따라 변화하는  $V_R$ 과 암 단락 벡터  $V_D$ 로 최대 크기를 가지는

(a) Space vector modulation

(b) Switching pattern of MSVPWM

그림 11 수정된 공간벡터 변조방법

Fig. 11 Modified space vector modulation method

그림 12 수정된 공간벡터 변조방식의 스위칭 패턴

Fig. 12 MSVPWM switching pattern

$V_R$ 을 구성한다. 이 때 영 벡터는 항상 최소의 크기를 갖는다 [17,18]. 적용된 공간벡터 변조방식의 출력전압 제어방법은 추정된 입력 상전압과 출력 전압을 검출하여 D-Q 변환과

PI제어를 통하여 스위칭 인가시간과 출력전압을 제어한다.

본 논문에서 적용되는 공간벡터 변조방식의 기준벡터 인 가시간은 식  $(21)\sim(24)$ 와 같으며, 여기서 N은 섹터 번호,  $\alpha$ 는 위상각을 의미한다.

표 1 MSVPWM의 각 섹터별 스위칭 패턴

Table 1 Active time of switching pattern for each sector of MSVPWM

|        | T                              |                                |

|--------|--------------------------------|--------------------------------|

| Sector | MSVPWM                         |                                |

|        | Upper switches                 | Lower switches                 |

| 1      | $S_1=T_1+T_2+T_0/2+2T$         | $S_4 = T_0/2$                  |

|        | $S_3 = T_2 + T_0/2$            | $S_6 = T_1 + T_0/2 + 2T$       |

|        | $S_5 = T_0/2 - 2T$             | $S_2=T_1+T_2+T_0/2+4T$         |

| 2      | $S_1 = T_1 + T_0/2$            | $S_4 = T_2 + T_0/2 + 2T$       |

|        | $S_3=T_1+T_2+T_0/2+2T$         | $S_6 = T_0/2$                  |

|        | $S_5 = T_0/2 - 2T$             | $S_2=T_1+T_2+T_0/2+4T$         |

| 3      | $S_1 = T_0/2 - 2T$             | $S_4=T_1+T_2+T_0/2+4T$         |

|        | $S_3=T_1+T_2+T_0/2+2T$         | $S_6 = T_0/2$                  |

|        | $S_5 = T_2 + T_0/2$            | $S_2=T_1+T_0/2+2T$             |

| 4      | $S_1 = T_0/2 - 2T$             | $S_4=T_1+T_2+T_0/2+4T$         |

|        | $S_3 = T_1 + T_0/2$            | $S_6 = T_2 + T_0/2 + 2T$       |

|        | $S_5=T_1+T_2+T_0/2+2T$         | $S_2 = T_0/2$                  |

| 5      | $S_1 = T_2 + T_0/2$            | $S_4 = T_1 + T_0/2 + 2T$       |

|        | $S_3 = T_0/2 - 2T$             | $S_6 = T_1 + T_2 + T_0/2 + 4T$ |

|        | $S_5 = T_1 + T_2 + T_0/2 + 2T$ | $S_2 = T_0/2$                  |

| 6      | $S_1=T_1+T_2+T_0/2+2T$         | $S_4 = T_0/2$                  |

|        | $S_3 = T_0/2 - 2T$             | $S_6 = T_1 + T_2 + T_0/2 + 4T$ |

|        | $S_5 = T_1 + T_0/2$            | $S_2 = T_2 + T_0/2 + 2T$       |

$$T_1 = MT_s \sin\left(\frac{\pi N}{3} - \alpha\right) \tag{21}$$

$$T_2 = MT_s \sin\left(\alpha - \frac{\pi(N-1)}{3}\right) \tag{22}$$

$$T_D = T_S(1 - M) \tag{23}$$

$$T_Z = T_S - (T_D + T_1 + T_2) \tag{24}$$

#### 4. 결과 고찰

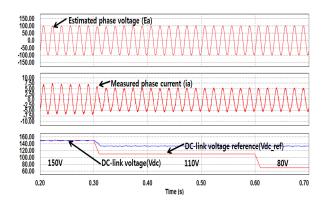

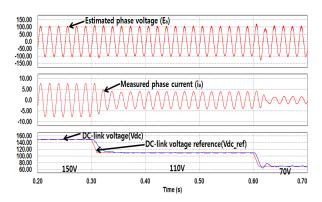

제안된 센서리스 제어기법의 타당성을 확인하기 위하여그림 8과 같은 제어 시스템을 PSIM으로 구성하였다. 시스템은 입력 AC전압 센서가 없으며, 입력 AC전류 센서와 DC단 전압 센서만으로 제어된다. 출력 DC전압의 기준치가  $150[V] \rightarrow 110[V] \rightarrow 70[V]$ 로 급변시 출력 DC전압의 승/강압과 과도응답 특성, 추정된 입력 AC전압 파형의 FFT 그리고 효율 등을 PSIM 시뮬레이션을 통하여 검증하였다. 표 2는 시뮬레이션 파라미터를 나타내고 있다.

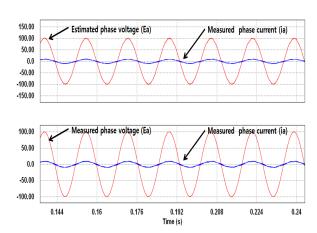

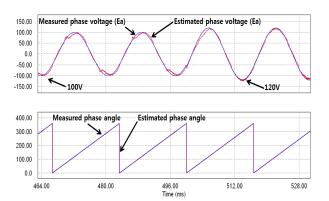

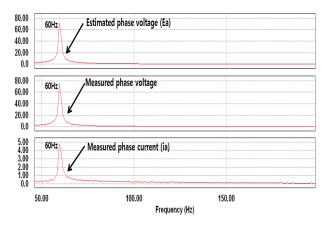

그림 13은 정상상태에서의 추정된 입력 AC전압과 측정된 입력 AC전압을 비교한 것을 상 전류와 같이 나타낸 것이다. 먼저 추정된 입력 상전압은 두 상의 입력전류와 DC전압 만을 사용하여 식 (14) ~ (16)에 의해 연산되었다. 입력 상전압을 직접 검출한 과형과 비교해 볼 때, 동일한 형태를 보이

표 2 시뮬레이션 파라미터

Table 2 Simulation parameters

| Paramet          | Value                      |       |

|------------------|----------------------------|-------|

| Input vol        | 100V <sub>peak</sub> /60Hz |       |

| Input ind        | 1mH,0.5Ω                   |       |

| DC-link ca       | 2000uF                     |       |

| Load res         | 10Ω                        |       |

| 7                | Inductor                   | 3mH   |

| Z-source network | Capacitor                  | 200uF |

| Voltage PI cont  | 0.0035                     |       |

| Voltage PI cont  | 0.0000001                  |       |

| PLL PI control   | 0.005                      |       |

| PLL PI control   | 0.01                       |       |

| Switching fr     | 10kHz                      |       |

그림 13 추정된 입력 전압과 측정된 입력 전압

Fig. 13 Estimated input voltage and measured input voltage

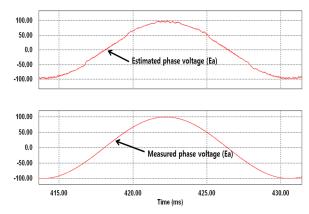

**그림 14** 각 입력 전압의 확대 파형 (위: 추정된 입력 상전 압, 아래: 검출된 입력 상 전압)

Fig. 14 Enlarged waveform of each input voltage(top: estimated input phase voltage, bottom: measured phase voltage)

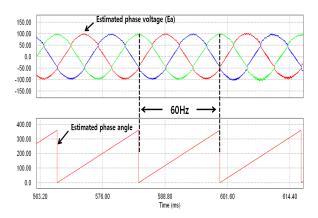

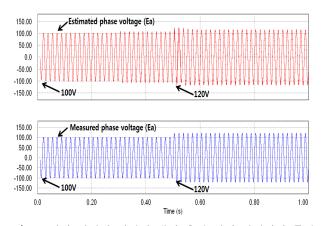

는 것을 알 수 있다. 또한 그림 14는 추정된 입력 전압과 직접 검출된 전원 전압의 파형을 확대한 것으로서, 서로 진 폭과 위상이 일치함을 볼 수 있다. 그림 15는 추정된 3상 입력 상전압 파형과 위상각을 나타내는 것으로, PLL을 통하여 일정 주파수를 추종하는 것을 볼수 있다. 그림 16은 입력 상전압이 변화할 때 추정 입력 상전압 파형의 과도 응답을 나타내고 있다. 입력 상전압이 0.5[s] 구간에서 100[V] → 120[V]로 변동 되어도 추정된 입력 상전압은 입력 상전압을 잘 추정함을 알 수 있다.

그림 17은 과도상태를 확대한 파형으로서, 입력 전압이 변동하는 0.5초 구간에서도 추정된 입력 전압은 측정된 파형과비교해 볼 때, 위상각의 변동 없이 일정 주파수를 유지함을 볼 수 있다.

그림 15 추정된 3상 입력 상전압과 위상각

Fig. 15 Estimated three-phase input phase voltage and its phase angle

그림 16 입력 상전압 변화에 대한 추정 입력 상전압의 동적 응답

Fig. 16 Dynamic response of the estimated input phase voltage for input phase voltage change

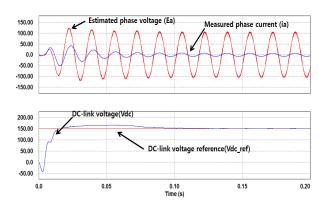

그림 18은 단위 입력역률 제어와 DC-link 전압 제어를 한 경우에 대한 시뮬레이션 결과를 보여준다. 먼저 그림 18의 상단 과형은 추정된 입력 교류 상전압과 측정된 입력 교류 전류 과형을 나타내고 있으며, 서로 동상임을 알 수 있다. 그림 18의 하단 과형은 DC-link 전압의 기준치를 150[V]로 일정 제어했을 때의 출력측 직류전압으로 리플이거의 보이지 않고 지령치에 잘 추종하는 것을 알 수 있다.

그림 17 확대된 입력 상전압과 위상각

Fig. 17 Enlarged input phase voltage and its phase angle

그림 18 단위 입력역률과 DC-link 전압제어 파형

Fig. 18 Unity input power factor and controlled DC-link voltage

그림 19 일반적인 PWM 정류기의 DC-link 기준 전압 변동 의 동특성

Fig. 19 Dynamic response of DC-link voltage reference change of the traditional PWM rectifier

그림 19와 그림 20은 일반적인 3상 전압형 PWM 정류기와 제안된 입력 전압 센서리스 3상 Z-소스 PWM 정류기에 대해, DC-Link 기준 전압을 급격한 제어를 한 경우에 대한 응답결과를 나타낸 것이다. 먼저 그림 19의 일반적인 3상 전압형 PWM 정류기의 경우에는, 150[V] → 110[V] → 70[V]의 출력 DC전압 기준치에 대하여, 이미 서론에서 언급

한 바와 같이, 출력 전압은 입력 전압 이상의 전압으로만 제어됨을 알 수 있다. 이는 브리지 회로내 스위치 온 동작으로 연결되는 회로는 항상 선간전압이 걸리는 특성 때문에 DC-Link 기준 전압은 입력 전압 이하로는 제어 할 수 없기때문이다. 따라서 입력전압 보다 낮은 전압으로 출력 DC전압을 제어하려면 다른 구조의 PWM정류기가 필요하게 된다. 반면에 그림 20과 같이 150[V] → 110[V] → 70[V]로 급격한 제어를 할 경우에도 3상 Z-소스 PWM 정류기는 입력전압보다 승압된 출력 DC전압을 얻거나, 강압된 전압을 얻는 것이 모두 가능함을 볼 수 있다.

그림 20 Z-소스 PWM 정류기의 DC-link 전압 변동의 동특성 Fig. 20 Dynamic response of DC-link voltage reference change of Z-source PWM rectifier

그림 21 추정된 입력 전압과 측정된 입력 전압 그리고 입력 전류에 대한 FFT 분석 결과

Fig. 21 FFT results of estimated / measured input voltage and its input current

그림 21은 추정된 입력 전압과 측정된 입력 전압 그리고 입력 전류의 FFT분석 결과를 나타낸 것이다. FFT분석 결 과를 보면 모두 60[Hz] 기본과 성분을 제외하고는 고조파가 미미한 것으로 보아, 각 과형들이 모두 정형과형임을 알 수 있다.

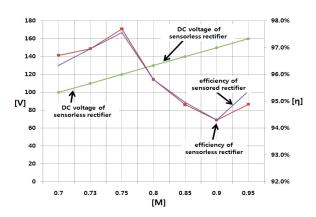

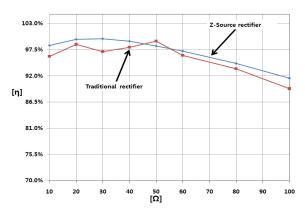

그림 22와 그림 23은 센서기반 Z-소스 PWM 정류기, 전통적인 PWM 정류기와 제안된 입력 전압 센서리스 Z-소스 PWM 정류기에 대한 출력 전압 및 효율을 변조지수 변화에 대해 그래프로 나타내었다. 입력 전압은 100[V]로 고정하고

그림 22 변조지수에 따른 출력 전압 및 효율

Fig. 22 Output voltage and efficiency according to modulation index

그림 23 부하변동에 따른 효율

Fig. 23 Efficiency of according to change load

DC-Link 기준 전압을 100[V]에서 160[V]까지 단계적으로 가변을 하였다. 도출된 그래프를 볼 때 제안된 입력 전압 센서리스 제어기법은 기존의 입력 전압 센서 적용방식과 변조지수에 따른 출력 전압 및 효율은 두 방식이 유사한 결과를 보임을 알 수 있다.

그림 22에서 보는 바와 같이, 변조지수 M=0.75에서는 효율이 97.5[%]로 가장 높았으며, 그 이상의 변조지수에서는 점차 효율 낮아지는 추세를 보이고 있다. 출력 전압의 경우에는 변조지수 증가에 따라 출력 전압이 선형적으로 증가하는 것을 볼 수 있다. 또한 그림 23의 부하 변동에 따른 효율을 살펴보면, 부하 조건을 10~100[Ω]으로 단계적으로 변화하는 조건하에서, 제안된 Z-소스 PWM 정류기는 전통적인 PWM 정류기와 거의 유사한 결과를 볼 수 있다. 결론적으로 제안된 센서리스 시스템은 센서기반 시스템과 거의 동일한 제어 특성을 발휘 한다고 볼 수 있다.

# 5. 결 론

본 논문에서는 입력 전압 센서리스 제어기법에 의한 3상 Z-소스 PWM 정류기를 제안하였다. 제안된 시스템은 상전 압을 검출을 하지 않고 DC-link단 전압과 상전류만을 이용

하여 전압제어를 수행하는 센서리스 제어기법을 기반으로 하고 있다. 이를 위하여 PWM 정류기의 스위칭함수와 DC-link 전압으로 부터 상전압를 재구성하고, 이를 다음 샘플링 시점의 상전압까지 예측하는 제어기를 구성하였다. 또한 전원 측에서 공급되는 입력전력이 부하에서 소비하는 출력전력에 따라 변동하는 출력전압과 추정된 상전압을 검출하여 D-Q변환 및 PI제어를 통하여 공간 벡터 변조기의 스위칭 인가시간과 출력전압을 제어하였다.

제안된 시스템에 타당성을 검증하기 위하여  $100V_{peak}/60$ Hz 입력 전압조건에 대한 PSIM 시뮬레이션을 정상상태와 과도상태에 대하여 수행하였다. 그 결과 입력 AC전압의검출없이 두 상의 입력전류와 DC-link 전압의 검출만으로 3상 입력 상전압을 추정할 수 있었으며, 단위 입력역률도 구현할 수 있었다. 입력 AC전압이  $100[V] \rightarrow 120[V]$ 로 급변하는 과도상태에 대해서도 검출된 입력 AC전압과 추정된 입력 AC전압은 크기과 주파수 모두 일치하였다. 또한 제안된입력전압 센서리스 3상 Z-소스 PWM 정류기는 DC-Link기준 전압  $150[V] \rightarrow 110[V] \rightarrow 70[V]$ 의 급변한 제어조건에서도 입력 전압의 추정성능의 저하없이 단위 입력역률을 유지하면서 DC-link 출력 DC전압의 과도특성이 양호하였다. 끝으로 제안된 기법은 기존의 센서 기반의 Z-소스 정류기와출력전압 및 효율에 있어서도 동일한 특성을 보여줌을 확인할 수 있었다.

#### 참 고 문 헌

- [1] R. Wu, S. B. Dewan, and G. R. Slemon, "Analysis of an ac-to-dc voltage source converter using PWM with phase and amplitude control," IEEE Trans. Ind. Appl., vol. 27, no.2, pp. 355–364, Mar./Apr. 1991.

- [2] V. Kaura, and V. Blasko, "Operation of a voltage source converter at increased utility voltage," IEEE Trans. Power Electron.,vol. 12, pp. 132–137, Jan. 1997.

- [3] V. Blasko, and V. Kaura, "A new mathematical model and control of a three-phase AC-DC voltage source converter," IEEE Trans. Power Electron., vol. 12, pp. 116-123, Jan. 1997.

- [4] Xinping Ding, Zhaoming Qian, Yeyuan Xie, Zhengyu Lu, "Three phase Z-source rectifier," in Proc. IEEE PESC '05. IEEE., pp. 494–500, Jun. 2005.

- [5] D. M. Vilathgamuwa, P. C. Loh and K. Karunakar, "Modelling of three phase Z-source boost-buck rectifiers," in Conf IEEE PEDS., pp. 1471–1476, Nov. 2007.

- [6] K. Karunakar and D. M.Vilathgamuwa, "Dynamic analysis of three phase Z-source boost-buck rectifier," in Conf, IEEE PECon., pp. 198-202, Dec. 2008.

- [7] F. Z. Peng, "Z-source inverter," IEEE Trans. Ind.

- Applicat., vol. 39, No.2, pp. 504-510, March/April 2003.

- [8] T. Ohnishi and K. Fujii, "Line voltage sensorless three phase PWM converter by tracking control of operating frequency," in Conf. Rec. of Power Conversion Conference, 1997, vol. 1, pp. 247–252.

- [9] T. Noguchi, H. Tomiki, S. Kondo, and I. Takahashi, "Direct power control of PWM converter without power-source voltage sensors," IEEE Trans Ind. Applicat., vol. 34, no.3, pp. 473-479, May./Jun. 1998.

- [10] S. Hansen, M. Malinowski, F. Blaabjerg, and M. P. Kazmierkowski, "Sensorless control strategy for PWM rectifier," in Conf. Rec. of IEEE APEC'00, 2000, vol. 2, pp. 832–838.

- [11] H. S. Song, I. W. Joo, and K. Nam, "Source Voltage Sensorless Estimation Scheme for PWM Rectifiers Under Unbalanced Conditions," IEEE Trans Ind. Electron., vol. 50, no.6, pp. 1238 - 1245, DEC. 2003.

- [12] H. Yoo, J. H. Kim, and S. K. Sul, "Sensorless Operation of a PWM Rectifier for a Distributed Generation," IEEE Trans Power Electron., vol. 22, no. 3, pp. 1014 - 1018, May. 2007

- [13] W. C. Lee, D. S. Hyun, and T. K. Lee, "A Novel control method for three-phase PWM rectifiers using a single current sensor," IEEE Trans Power Electron., vol. 15, no. 5, pp. 861 - 870, Sep. 2000

- [14] D. C. Lee, and D. S. Lim, "AC voltage and current sensorless control of three-phase PWM rectifier," IEEE Trans Power Electron., vol. 17, no. 6, pp. 883 - 890, Nov. 2002

- [15] H. Kim, and T. M. Jahns, "Phase current reconstruction for AC motor drives using a DC link single current sensor and measurement voltage vectors," IEEE Trans Power Electron., vol. 21, no. 5, pp. 1413 1419. Sept. 2006

- [16] G. Lo Calzo, A. Lidozzi, L. Solero, and F. Crescimbini, "Three-phase Z-source power supply design and dynamic modeling," in Conf. Rec. of IEEE ECCE'11,2011, pp. 1339 1345.

- [17] Tae-Won Chun, Quang-Vinh Tran, Jung-Ryol Ahn, and Jih-Sheng Lai, "AC output voltage control with minimization of voltage stress across devices in the Z-source inverter using modified SVPWM", in Conf. Rec. of IEEE PESC'06, 2006, pp. 1-5.

- [18] Se-Jin Kim, Young-Gook Jung, Young-Cheol Lim, and Seung-Hak Yang, "Output AC voltage control of a three-phase Z-source inverter by the voltage gain and modulation index control", Trans. KIEE, vol. 59, no. 11, pp. 1996 2005. Nov. 2010

# 저 자 소 개

## 한 근 우 (韓 勤 牛)

1978년 9월 28일생. 2004년 2월 대불대학교 전기공학과 졸업. 2006년 전남대학교대학원 전기공학과 졸업(석사). 현재 동대학원 박사과정. 2005~2010년 LG이노텍(주) POWER LAB 선임연구원, 2010~현재 삼성전자(주) 생활가전사업부 책임연구원.

Tel: 062-530-0852

E-mail: tesla7930@gmail.com

# 정 영 국 (鄭 榮 國)

1963년 11월 10일생. 1986년 전남대학교 전기공학과 졸업. 1988년 동 대학원 전기 공학과 졸업(석사). 1996년 동 대학원 전 기공학과 졸업(박사). 2000년 일본 오카 야마대학교 연구방문. 현재 대불대학교 융합기술학부 부교수.

Tel: 061-469-1263 E-mail: jyg@db.ac.kr

## 임 영 철 (任 永 徹)

1953년 4월 23일생. 1975년 전남대학교 전기공학과 졸업. 1977년 고려대학교 대학원 전기공학과 졸업(석사). 1990년 동대학원 전기공학과 졸업(박사). 1997년 호주 모나시대학교 Visiting Scholar. 1998~2007년 산업자원부 지정 전남대학교 고품질 전기전자부품 및 시스템연구센터 소장. 현재 전남대학교 전기공학과교수.

$Tel\,:\,062\text{--}530\text{--}1743$

E-mail: yclim@chonnam.ac.kr