# Behavioral Current-Voltage Model with Intermediate States for Unipolar Resistive Memories

Young Su Kim and Kyeong-Sik Min

Abstract—In this paper, a behavioral current-voltage model with intermediate states is proposed for analog applications of unipolar resistive memories, where intermediate resistance values between SET and RESET state are used to store analog data. In this model, SET and RESET behaviors are unified into one equation by the blending function and the percentage volume fraction of each region is modeled by the Johnson-Mehl-Avrami (JMA) equation that can describe the time-dependent phase transformation of unipolar memory. The proposed model is verified by the measured results of TiO<sub>2</sub> unipolar memory and tested by the SPECTRE circuit simulation with CMOS read and write circuits for unipolar resistive memories. With the proposed model, we also show that the behavioral model that combines the blending equation and JMA kinetics can universally describe not only unipolar memories but also bipolar ones. This universal behavioral model can be useful in practical applications, where various kinds of both unipolar and bipolar memories are being intensively studied, regardless of polarity of resistive memories.

*Index Terms*—Unipolar resistive memories, behavioral model, Johnson-Mehl-Avrami equation

A part of this work was presented in Korean Conference on Semiconductors, Gangwon-do in Korea, Feb. 2013

The authors are with School of Electrical Engineering, Kookmin University, 861-1, Jeongneung-dong, Seongbuk-gu, Seoul 136-702, Korea

#### I. INTRODUCTION

Resistive memories have been developed for many years because they have been considered to be able to replace current DRAM and FLASH memories in future. Though underlying physics are still not fully understood, some behavioral models have been proposed for circuit simulators such as HSPICE and SPECTRE. Generally speaking, resistive memories can be categorized into two types that are bipolar and unipolar, respectively. For bipolar resistive memories, many behavioral models that are based on the state variable equations were developed [1-4]. However, very few models were proposed for unipolar resistive memories compared with bipolar ones [5-7]. The SPICE macromodel for unipolar memories that was proposed by Lee et al [5] cannot describe the intermediate resistance values between SET and RESET states accurately. If we try to consider intermediate states in the macromodel, many complicated sub-blocks such as comparators should be added to the model. This complicated macromodel with intermediate states needs a long simulation time and a large amount of main memory for the simulation.

As a different modeling approach, the behavioral unipolar memory model that was formulated by doublewell potential function was developed [6]. Though the behavior model does not need any circuit block, it is described by very complex mathematical equations [6]. Moreover, the intermediate states between SET and RESET states that are very important in realizing analog memory applications such as neuromorphic systems were not considered in the behavioral model formulated by the double-well potential [6].

In this paper, we will propose a new behavioral

Manuscript received Apr. 24, 2013; accepted Jul. 19, 2013

E-mail : mks@kookmin.ac.kr

current-voltage model with intermediate states that is implemented by Verilog-A for unipolar memories [7]. The proposed model will be verified by the measurement results of TiO<sub>2</sub> unipolar memory [8] and tested by the SPECTRE circuit simulation with CMOS read and write circuits for unipolar memories. With the new behavioral model, we will extend the concept of combing the blending equation [9, 10] and Johnson-Mehl-Avrami (JMA) kinetic equation [11] to bipolar memories. Thus, in this paper, we will show that the proposed model can universally describe the current-voltage relationship of both unipolar and bipolar memories with intermediate states, regardless of polarity. The universal behavioral model can be more useful than unipolar-only or bipolaronly model in practical applications because both unipolar and bipolar resistive memories are being studied and developed for various analog and digital applications nowadays. In terms of materials and processing technologies of resistive memories, many scholars are still trying to find the best one for resistive memory applications regardless of polarity of memory charactersistics. For them, the universal behavioral model proposed in this paper can be used to compare and analyze the electrical characteristics and behaviors between various materials and processing technologies. Furthermore, the universal resistive memory model can help circuit engineers design various resistive memory circuits regardless of the polarity of memories.

# II. BEHAVIORAL MODEL WITH INTERMEDIATE STATES BETWEEN SET AND RESET FOR UNIPOLAR RESISTIVE MEMORIES

To describe the current-voltage behavior in both SET and RESET regions of unipolar resistive memories, we assume the following blending equation that can merge two regional equations into a united expression as shown below [9, 10].

$$i(t) = f_{SET}(v(t)) \times \exp\left((1 - C_{SET}) \cdot \ln\left(\frac{f_{RESET}(v(t))}{f_{SET}(v(t))}\right)\right) \quad (1)$$

Here  $C_{SET}$  is a percentage volume fraction of SET region that varies between 0 and 1 [9]. In Eq. (1),  $f_{SET}(v(t))$  means the current-voltage relationship in SET

state and  $f_{RESET}(v(t))$  means the current-voltage relationship in RESET state. v(t) and i(t) represent voltage and current of resistive memories, respectively.  $f_{SET}(v(t))$  and  $f_{RESET}(v(t))$  can be described by  $a_1 \cdot \sinh(b_1 \cdot v(t))$  and  $a_2 \cdot \sinh(b_1 \cdot v(t))$ , respectively [12]. Here the parameters of  $f_{SET}(v(t))$  and  $f_{RESET}(v(t))$ that are used in this paper are  $a_1 = 5$  [A],  $b_1 = 10^{-3}$ ,  $a_2 = 10^{-4}$  [A], and  $b_2 = 3$ , respectively. When  $f_{SET}(v(t))$  and  $f_{RESET}(v(t))$  seem very linear, we can use simple linear current-voltage relationships of  $i(t) = v(t)/R_{SET}$  and  $i(t) = v(t)/R_{RESET}$ , respectively, for  $f_{SET}(v(t))$  and  $f_{RESET}(v(t))$ . R<sub>SET</sub> and R<sub>RESET</sub> mean LOW resistance at SET state and HIGH resistance at RESET state, respectively.

In Eq. (1), when  $C_{SET}$  is 1, the unipolar resistive memory is dominated by  $f_{SET}(v(t))$ , where the resistive memory is in SET state. On the contrary, when the resistive memory is in RESET state, it can be described by  $f_{RESET}(v(t))$  because  $C_{SET}$  in Eq. (1) is 0. Between SET and RESET, there can be some intermediate states, where  $C_{SET}$  is larger than 0 but smaller than 1.

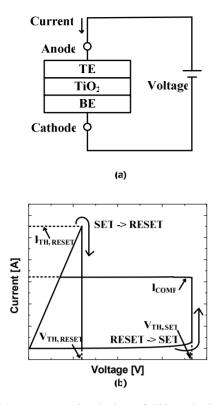

Let's assume that we apply a voltage or current pulse to TiO<sub>2</sub> unipolar resistive memory that is shown in Fig. 1(a), where TE and BE are the top and bottom electrode, respectively. As a current or voltage stress accumulates in  $TiO_2$ , the state variable that is represented by  $C_{SET}$  in Eq. (1) starts to be changed with respect to time thereby the conductivity of unipolar resistive memory changes, too. Fig. 1(b) shows briefly the SET and RESET operation in unipolar memories. I<sub>TH,RESET</sub> and V<sub>TH,RESET</sub> are the threshold current and threshold voltage for SETto-RESET transition, respectively. I<sub>COMP</sub> is the compliance current that limits a maximum allowable current through resistive memory. V<sub>TH SET</sub> is the threshold voltage for RESET-to-SET transition in resistive memory. If the applied current exceeds I<sub>TH,RESET</sub>, C<sub>SET</sub> becomes lower to 0. On the contrary, if the applied voltage of unipolar memory exceeds V<sub>TH.SET</sub>, the state changes from RESET to SET.

It is known that the percentage volume fraction of SET region is changed with respect to time if the unipolar memory is applied by a voltage or current stress. The measurement by S. Song et al [13] indicates that phase transformation that happens in  $TiO_2$  unipolar memories could be described by the Johnson-Mehl-Avrami (JMA)

**Fig. 1.** (a) A cross-sectional view of  $TiO_2$  unipolar resistive memories. TE and BE mean the top electrode and the bottom electrode, respectively, (b) Current-voltage relationship of SET and RESET operation in unipolar memories.

equation [11]. Thus, according to the JMA equation, the percentage volume fraction of RESET region,  $1-C_{SET}$ , can be expressed with

$$1 - C_{SET} = K_0 e^{\frac{t^n}{\tau}} \qquad for \quad v(t) \ge V_{TH,SET}$$

$$= 1 - K_1 e^{\frac{t^n}{\tau}} \qquad for \quad V_{TH,RESET} \le v(t) < V_{TH,SET}$$

$$= 0 \qquad for \quad v(t) < V_{TH,RESET} \qquad (2)$$

Here  $K_0$  and  $K_1$  are the coefficients for accounting for the initial values of 1-C<sub>SET</sub>. If we assume the full RESET state at the initial point,  $K_0$  is 1. Otherwise, assuming the full SET state,  $K_1$  should be 1. In Eq. (2),  $\tau$  means the time constant of phase-transformation in unipolar memories. The value of  $\tau$  in this paper is  $1.08 \times 10^{-8}$  [sec]. In Eq. (2), 'n' means Avrami exponent. Here the value of 'n' is 1. V<sub>TH,SET</sub> and V<sub>TH,RESET</sub> are threshold voltages for SET and RESET, respectively.

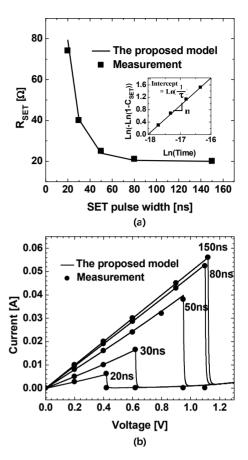

Fig. 2(a) compares the measured  $R_{SET}$  and the proposed model with respect to the SET pulse width. As the SET pulse width increases,  $R_{SET}$  becomes smaller. If

**Fig. 2.** (a) Comparison of the proposed model and measured data [8]. The inset figure shows  $Ln(-Ln(1-C_{SET}))$  versus Ln(time) plot. Here 'n' in Eq. (2) can be extracted by the slope of  $Ln(-Ln(1-C_{SET}))$  versus Ln(time) relationship. The  $Ln(1/\tau)$  can be calculated by the y-intercept point of  $Ln(-Ln(1-C_{SET}))$  with respect to Ln(time), (b) Comparison of the proposed behavioral model and the measured data that are obtained by Choi et al [8].

the SET pulse width is longer than 80 ns,  $R_{SET}$  begins to saturate around 20  $\Omega$ . Here the measured data obtained by Choi et al [8] that are shown in rectangle symbols are in good agreement with the proposed model that is shown in solid line. Here the inset figure in Fig. 2(a) shows that the plot of Ln(-Ln(1-C<sub>SET</sub>)) versus Ln(time) has a very good linearity. This good linearity means that the phase transformation in TiO<sub>2</sub> unipolar resistive memories follows the JMA equation well. Fig. 2(b) compares the proposed behavioral model and the measured data that are obtained by Choi et al [8]. For different intermediate states, the proposed model shows good agreement with the measured data, as shown in Fig. 2(b).

# III. CIRCUIT SIMULATION RESULTS WITH THE PROPOSED BEHAVIORAL MODEL

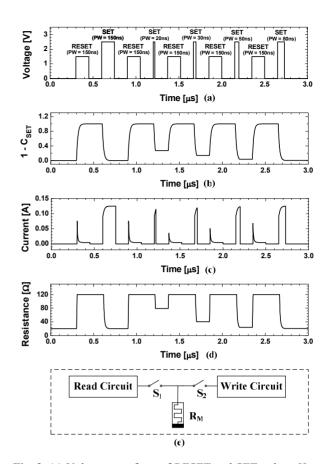

The transient simulation of unipolar resistive memories is shown in Figs. 3(a)-(d). Here, the voltage waveform in Fig. 3(a) is applied to a resistive memory with the proposed behavioral model. Here, RESET voltage with the amplitude of 1.5 V and the pulse width of 150 ns is applied first. And, then, SET voltage with the amplitude of 2.5 V and the pulse width of 150 ns comes next. Fig. 3(b) shows the percentage volume fraction of SET region C<sub>SET</sub> that is changed by the applied voltage with respect to time. After the first RESET pulse,  $(1-C_{SET})$  becomes 1 that means the resistive memory is in full RESET state. And, then, (1-C<sub>SET</sub>) becomes 0 by the first SET pulse thereby the resistive memory moves to full SET state. In Fig. 3(a), after the first RESET and SET pulses, the second RESET and SET pulses comes again. From Fig. 3(a), we can know that RESET pulses are long enough to change the resistive memory to full RESET state. However, SET pulses have different pulse widths thereby the resistive memory can be changed to different intermediate states, where the percentage volume fraction of SET region is between 0 and 1. Fig. 3(c) shows the current waveform of resistive memory. Resistance values that are changed according to the applied voltage in Fig. 3(a) are shown in Fig. 3(d). Here we can know that resistance values after RESET pulses become as large as R<sub>RESET</sub>. The resistance values after various SET pulses that

have different pulse widths can be different each other by the pulse width duration. These different resistance values indicate that there are intermediate states between SET and RESET states. Fig. 3(e) shows a block diagram of the read and write circuits for the proposed behavioral Verilog-A model of unipolar resistive memories. In Fig. 3(e), when  $S_1$  is closed, the memristive behavioral model is connected to the read circuit. When  $S_2$  is closed, the write circuit can change memristance of the behavioral model that is calculated with Eqs. (1) and (2).

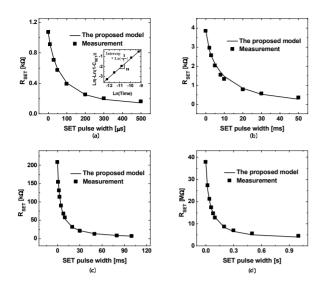

To show that the proposed behavioral model can universally describe not only unipolar resistive memories but also bipolar ones, we compared the proposed model with various measured data that are obtained by different bipolar memories [12, 14-17] in Figs. 4(a)-(d). Here one more thing to note is that various materials including

**Fig. 3.** (a) Voltage waveform of RESET and SET pulses. Here all RESET pulse widths are 150 ns. For SET pulse, the first pulse width is as long as 150 ns to change the resistive memory from RESET to full SET state. The second, third, fourth, and fifth are 20 ns, 30 ns, 50 ns, and 80 ns, respectively. By applying different SET pulse widths, the resistive memory can be changed to intermediate states, where intermediate SET resistance is larger than SET resistance with full SET state, (b) Here  $1-C_{\text{SET}}$  means the percentage volume fraction of SET region that is changed by the applied RESET and SET pulses, (c) Current waveform of resistive memory, (d) Resistance waveform of resistive memory, (e) Block diagram of the read and write circuits for the proposed behavioral Verilog-A model of unipolar resistive memories

TiO<sub>2</sub> were verified by the proposed model. For example, Fig. 4(a) compares the behavioral model with the silver chalcogenide based resistive memory that contains Ge<sub>2</sub>Se<sub>3</sub> and Ag [12, 14]. Figs. 4(b) and (c) show the measured data from TiO<sub>2</sub> based resistive memories that have bipolar switching characteristics [12, 15, 16]. The measured data in Fig. 4(d) were obtained from a layered device with co-sputtered Ag and Si active layers. Here Ag/Si mixture ratio can be changed to form an Ag-rich region or a Si-rich region thereby the conductivity of Ag/Si mixed layer can be variable [12, 17].

**Fig. 4.** Comparison of the proposed behavioral model and various devices (a) The measured device is silver chalcogenide based bi-polar resistive memory that contains  $Ge_2Se_3$  and Ag [12, 14], (b) The measured device is  $TiO_2$  crossbar resistive memory with bi-polar hysteresis loops [12, 15], (c) The measured device is another bi-polar  $TiO_2$  memristive switching memory [12, 16], (d) The measured device is made by co-sputtering Ag and Si active layers, where Ag/Si mixture ratio can be changed to form a Ag-rich region or a Si-rich region [12, 17].

Table 1. Comparison of the previous models [5, 6] and this work [7]

|                                                                               | The previous model [5]                                           | The previous model [6]                  | This work [7]                                          |

|-------------------------------------------------------------------------------|------------------------------------------------------------------|-----------------------------------------|--------------------------------------------------------|

| Spice macromodel<br>vs. Behavioral<br>model                                   | Spice<br>macromodel                                              | Behavioral model                        | Behavioral model                                       |

| Complexity of the macromodel or behavioral model                              | Complicated circuit blocks                                       | Complex<br>mathematical<br>equation     | Simple                                                 |

| Intermediate states                                                           | Considered but<br>many<br>complicated<br>circuit blocks<br>added | Not considered                          | Considered                                             |

| Be able to<br>universally describe<br>both uni-polar and<br>bi-polar memories | Tested only for<br>unipolar<br>memories                          | Tested only for<br>unipolar<br>memories | Tested for both<br>unipolar and<br>bipolar<br>memories |

In all the comparison with different materials and different processing technologies, the proposed behavioral model shows very good agreement with the measured data [12, 14-17]. In Fig. 4(a),  $R_{SET}$  changes from 1070  $\Omega$  to 162  $\Omega$  with a dynamic range as wide as one order of magnitude. Fig. 4(c) shows wider dynamic range of  $R_{SET}$  which is as wide as two orders of magnitude than one order of magnitude in Fig. 4(a). Fig.

4(c) indicates that the proposed behavioral model can fit to the measured data very well in spite of this wide dynamic range of  $R_{SET}$  variation. Though the dynamic range of  $R_{SET}$  in Fig. 4(b) is much smaller than Figs. 4(a) and (c), the calculated memristance values in Fig. 4(b) show good agreement with the measurement [12, 15]. In Fig. 4(d), the pulse width becomes as long as almost 1 sec. Despite this long programming pulse, the calculated  $R_{SET}$  values in Fig. 4(d) are in good agreement with the measurement.

Finally, we summarized the proposed model in comparison with the previous ones in Table 1.

## **IV. CONCLUSIONS**

In this paper, we proposed the behavioral currentvoltage model with intermediate states that was implemented by Verilog-A for unipolar resistive memories. The proposed model was verified by the measurement results of TiO<sub>2</sub> unipolar memory and tested by the SPECTRE circuit simulation with CMOS read and write circuits for unipolar resistive memories. With the proposed model, we also showed that the behavioral model that combines the blending equation and JMA kinetics could universally describe not only unipolar memories but also bipolar ones. This universal behavioral model can be useful in practical applications, where various kinds of unipolar and bipolar memories are being intensively studied, regardless of polarity of resistive memories.

#### **ACKNOWLEDGMENTS**

This work was financially supported by the Global Research Network Program (NRF-2011-220-D00089), the Nano-Material Technology Development Program (2011-0030228), and NRF-2013K1A3A1A25038533 through the National Research Foundation of Korea (NRF) funded by the Ministry of Science, ICT & Future Planning and the Industrial Strategic Technology Development Program funded by the Ministry of Trade, Industry and Energy (MOTIE, Korea) (10039239). The CAD tools were supported by the IC Design Education Center (IDEC), Korea.

### REFERENCES

- D. Strukov, G. Snider, D. Stewart, and R. Williams, "The missing memristor found," *Nature*, vol. 453, pp. 80-83, May 2008.

- [2] Y. Joglekar and S. Wolf, "The elusive memristor: properties of basic electrical circuits," *Eur. J. Phys.*, vol. 30, pp. 661-673, Jan. 2009.

- [3] J. Hur, M. Lee, C. Lee, Y. Kim, and C. Kim, "Modeling for bipolar resistive memory switching in transition-metal oxides," *Physical Review B*, vol. 82, 155321, Oct. 2010.

- [4] B. Gao, J. Kang, L. Liu, X. Liu, and B. Yu, "A physical model for bipolar oxide-based resistive switching memory based on ion-transportrecombination effect," *Appl. Phys. Lett.*, vol. 98, 232108, June 2011.

- [5] J. Lee, D. Kim, J. Lee, D. Kim, and K. Min, "A compact HSPICE macromodel of resistive RAM," *IEICE Electron. Express*, vol. 4, no. 19, pp. 600-605, Oct. 2007.

- [6] N. Akou, T. Asai, T. Yanagida, T. Kawai, and Y. Amemiya, "A behavioral model of unipolar resistive RAMs and its application to HSPICE integration," *IEICE Electron. Express*, vol. 7, no. 19, pp. 1467-1473, Oct. 2010.

- [7] Y. Kim and K. Min, "Behavioral model with intermediate states for unipolar resistive memories," *Korean Conf. on Semiconductors*, Feb. 2013.

- [8] B. Choi, S. Choi, K. Kim, Y. Shin, C. hwang, S. Hwang, S. Cho, S. Park, and S. Hong, "Study on the resistive switching time of TiO<sub>2</sub> thin films," *Appl. Phys. Lett.*, vol. 89, 012906, July 2006.

- [9] D. Batas and H. Fiedler, "A memristor SPICE implementation and a new approach for magnetic flux-controlled memristor modeling," *IEEE Trans. Nanotechnol.*, vol. 10, no. 2, pp. 250-255, Mar. 2011.

- [10] C. Jung, E. Lee, and K. Min, "Continuous and accurate PCRAM current-voltage model," *Journal* of Semiconductor Technology and Science, vol. 11, no. 3, pp. 162-168, Sep. 2011.

- [11] W. Johnson and R. Mehl, "Reaction kinetics in processes of nucleation and growth," *Trans. Am. Inst. Min. Metal.*, vol. 135, pp. 416-442, 1939.

- [12] C. Yakopcic, T. Taha, G. Subramanyam, R. Pino,

and S. Rogers, "A memristor device model," *IEEE Electron Device Lett.*, vol. 32, no. 10, pp. 1436-1438, Oct. 2011.

- [13] S. Song, J. Seok, J. Yoon, K. Kim, G. Kim, M. Lee, and C. Hwang, "Johnson-Mehl-Avrami type kinetic model for identifying the evolution of conducting nano-filaments in TiO<sub>2</sub> ReRAM," *Korean Conf. on Semiconductors*, pp. 421-422, 2011.

- [14] A. Oblea, A. Timilsina, D. Moore, and K. Campbell, "Silver chalcogenide based memristor devices," *in Proc. IJCNN*, pp. 1-3, July 2010.

- [15] G. Snider, "Cortical computing with memristive nanodevices," *SciDAC Rev.*, vol. 10. pp. 58-65 2008.

- [16] J. Yang, M. Pickett, X. Li, D. Ohlberg, D. Stewart, and R. Williams, "Memristive switching mechanism for metal/oxide/metal nanodevices," *Nat. Nanotechnol.*, vol. 3, no. 7, pp. 429-433, July 2008.

- [17] S. Jo, T. Chang, I. Ebong, B. Bhadviya, P. Mazumder, and W. Lu, "Nanoscale memristor device as synapse in neuromorphic systems," *Nano Lett.*, vol. 10, no. 4, pp. 1297-1301, Apr. 2010.

Young Su Kim received the B. S. degree in Electrical Engineering from Kookmin University, Seoul, Korea, in 2011. He is currently working toward the Master's degree of Electrical Engineering at Kookmin

University, Seoul, Korea. His research interest includes the circuit design and neural network system

**Kyeong-Sik Min** received the B.S. degree in Electronic and Computer Engineering from Korea University, Seoul, Korea, in 1991, and the M.S.E.E. and Ph. D. degrees in Electrical Engineering from Korea

Advanced Institute of Science and Technology (KAIST), Daejeon, Korea, in 1993 and 1997, respectively. In 1997, he joined Hynix Semiconductor Inc., where he was engaged in developing low-power and high-speed DRAM circuits. From 2001 to 2002, he was a research associate at University of Tokyo, Tokyo, Japan, where he designed low-leakage memories and logic circuits. In September 2002, he joined the faculty of Kookmin University, Seoul, Korea, where he is currently a Professor at School of Electrical Engineering. At Kookmin Univ., he is working in low-power VLSI design, new emerging memory modeling and circuit design, and developing power management IC for energy harvesting. Prof. Min served on the technical program committees of Asian Solid-State Circuits Conference (A-SSCC), Korean Conference on Semiconductors (KCS), International SoC Design Conference (ISOCC), etc. He is a member of IEEE, IEICE, and IEEK.