# A Subthreshold Slope and Low-frequency Noise Characteristics in Charge Trap Flash Memories with Gate-All-Around and Planar Structure

Myoung-Sun Lee, Sung-Min Joe, Jang-Gn Yun\*, Hyungcheol Shin, Byung-Gook Park, Sang-Sik Park\*\*, and Jong-Ho Lee

Abstract—The causes of showing different subthreshold slopes (SS) in programmed and erased states for two different charge trap flash (CTF) memory devices, SONOS type flash memory with gate-all-around (GAA) structure and TANOS type NAND flash memory with planar structure were investigated. To analyze the difference in SSs, TCAD simulation and low-frequency noise (LFN) measurement were fulfilled. The device simulation was performed to compare SSs considering the gate electric field effect to the channel and to check the localized trapped charge distribution effect in nitride layer while the comparison of noise power spectrum was carried out to inspect the generation of interface traps  $(N_{\rm IT})$ . When each cell in the measured two memory devices is erased, the normalized LFN power is increased by one order of magnitude, which is attributed to the generation of  $N_{\rm IT}$  originated by the movement of hydrogen species  $(h^*)$  from the interface. As a result, the SS is degraded for the GAA SONOS memory device when erased where the  $N_{\rm IT}$  generation is a prominent factor. However, the TANOS memory cell is relatively immune to the SS degradation effect induced by the generated  $N_{\rm IT}$ .

Manuscript received Oct. 31, 2011; revised Jun. 6, 2012.

Inter -University Semiconductor Research Center (ISRC), and School of Electrical Engineering and Computer Science, Seoul National University, Seoul, 151-742, Korea.

E-mail: jhl@snu.ac.kr

Index Terms—Subthreshold slope (SS), charge trap flash (CTF) memory, gate-all-around (GAA), low-frequency noise, interface trap ( $N_{\rm IT}$ )

### I. Introduction

The differential demands for high density non-volatile memories with low-cost process have strongly increased in the last decade. However, today the scaling of standard planar flash structures having floating gate seems to face serious limitations, due to the loss of memory cell electrostatic integrity and the appearance of parasitic inter-coupling between adjacent cells in the arrays [1]. In addition, since the tunneling oxide thickness in floating gate memory devices is relatively thick to suppress the stress induced leakage current (SILC), the high voltages are required for the write and erase operations [2].

In order to overcome these issues, charge trap flash (CTF) memories have been proposed as one of the most promising candidates for the next generation NAND flash technology. As an example, SONOS type flash memory based on a gate–all-around (GAA) structure has strong gate controllability and suppressed short channel effect due the merits of GAA structure even in the ultimately scaled regime [3, 4]. TANOS CTF memory with planar channel structure has a better program/erase speed and it is enable to decrease a backward tunneling current by using high-k dielectric material (Al<sub>2</sub>O<sub>3</sub>) and metal gate (TaN) compared to SONOS based CTF memories [5]. They are examples as substitutes for floating gate type flash memory while still have a

<sup>\*</sup> Semiconductor R&D Center of Samsung Electronics Company Ltd., Suwon 443-742, Korea.

<sup>\*\*</sup> Department of Electronics Engineering, Sejong University, Seoul 143-747, Korea

reliability issue such as the data retention.

On the other hand, subthreshold slope (SS) of a read current in a NAND flash memory cell is different depending on the cell state. In other words, the SS is changed when the cell is programmed or erased and cycled. In addition, overlap length between the source/drain and the gate affects the SS variation. Several authors have reported about the causes of the SS changes in the NAND flash memories, but comprehensive understanding of them are still missing [6-8]. Thus, more detailed analysis should be made for clear understanding.

In this paper, we investigate SS characteristics in the  $I_D$ - $V_G$  (or  $I_{BL}$ - $V_{read}$ ) curves of the SONOS GAA and the TANOS planar CTF devices to analyze of their SS variation when they are programmed and causes. To analyze the cause clearly, 2-D device simulation [16] and measurement of low-frequency noise (LFN) power were performed. Since the LFN characteristic reflects generated interface traps ( $N_{IT}$ ) near the interface between the channel and the tunneling oxide, we can improve accuracy in the analysis of the SS variation.

### II. EXPERIMENTAL PROCEDURE

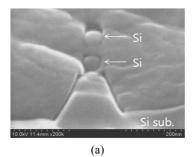

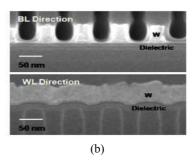

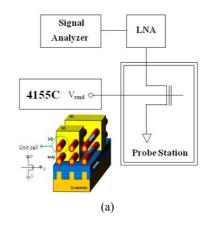

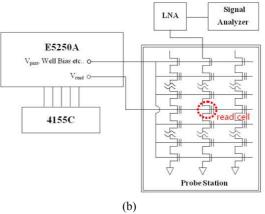

Fig. 1(a) and (b) show the cross sectional SEM image of Si-nanowire stacked array cells having GAA structure [9] and the cross sectional profiles with bit-line (BL) and word-line (WL) directions for TANOS based CTF cells [10], respectively. I-V measurement of the devices was carried out with 4155C (Agilent) for comparing SSs. The systematic setups for noise measurement are presented in Fig. 2(a) and (b) for each device. The noise measurement was performed with an arbitrary unit cell for the SONOS GAA CTF memory while for the TANOS planar CTF memory a cell in a string was randomly selected where all of the unselected (or pass) cells were erased. In the case of the TANOS based NAND flash memory devices, the read voltages and pass voltages were applied to a selected cell and unselected cells, respectively. Since the selected cell determines the bit-line current in a cell string, the noise in the current attributes to the selected cell [11]. The low-frequency noise measurement was carried out with the low noise current amplifier (SR570) and dynamic signal analyzer (Agilent 35670A). The devices were measured in a shield chamber at room temperature.

**Fig. 1.** (a) Cross sectional FESEM image of the SONOS GAA nanowire flash memory, (b) cross sectional TEM profiles of the TANOS based CTF memory with BL and WL directions.

**Fig. 2.** Schematic view of noise measurement setup for (a) GAA nanowire flash memory unit cell, (b) TANOS based CTF memory cell in a string.

# III. RESULTS AND DISCUSSION

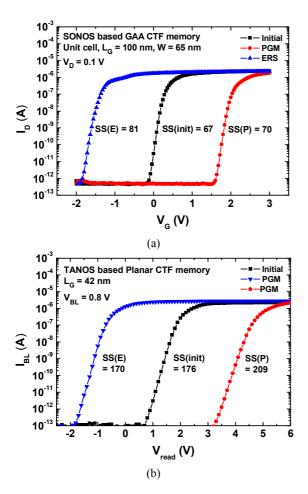

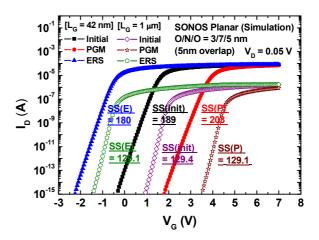

The representative  $I_D$ - $V_G$  characteristics in initial, programmed and erased states are depicted for two different kinds of the flash memories, SONOS GAA and TANOS planar CTF memories as shown in Fig. 3(a) and (b), respectively. For program and erase operations, 9 V for 1 $\mu$ s and -10 V for 10  $\mu$ s were applied to the former while 14 V for 100  $\mu$ s and -16 V for 1ms were applied to the latter. In addition, each value of the subthreshold slopes [SS=( $d\log I_D/dV_G$ )<sup>-1</sup>] in programmed and erased states was extracted as denoted next to each  $I_D$ - $V_G$  lines as shown in Fig. 3(a) and (b).

Comparing the SSs in programmed and erased states in each device, the SS in erased state is larger than that in programmed state in the GAA SONOS CTF memory unit

**Fig. 3.**  $I_D$ - $V_G$  curves in initial, programmed and erased states for (a) the SONOS based GAA nanowire CTF memory, (b) the TANOS based planar CTF flash memory. The SSs (mV/dec) shown next to each  $I_D$ - $V_G$  curve are extracted by linear fit in subthreshold region.

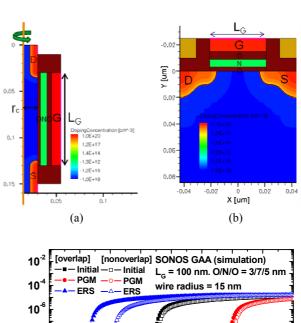

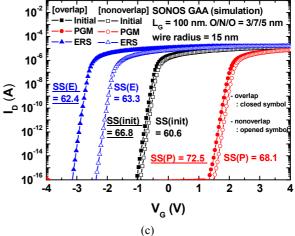

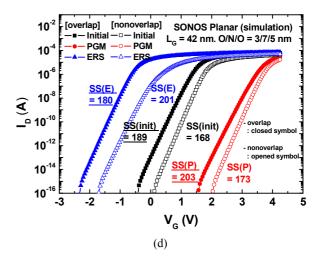

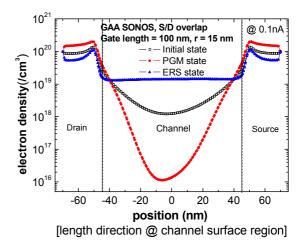

**Fig. 4.** 2D simulated device structures of SONOS memory cells with (a) GAA, (b) planar architecture, and their  $I_D$ - $V_G$  curves are presented according to the cell state and 5 nm of S/D overlap condition in (c) and (d), respectively. SSs (mV/dec) are extracted from the simulated  $I_D$ - $V_G$  curves as shown beside each plot. SSs of the S/D overlap (5 nm) structure are underlined for classification.

cell as exhibited in Fig. 3(a), whereas the opposite characteristics are displayed in the TANOS CTF memory device. The reported I-V characteristics for CTF memories adopting GAA and planar structures show more degraded SSs in programmed state [12, 13].

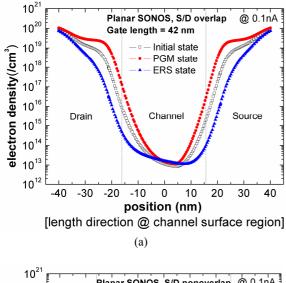

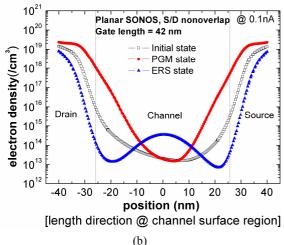

For detailed analysis, SSs in the programmed and erased states were compared in GAA and planar SONOS cells by utilizing TCAD simulation tool [14]. Fig. 4(a) and (b) show simulated device structures and their I<sub>D</sub>-V<sub>G</sub> characteristics with extracted SSs depending on the cell state and source/drain overlap condition are depicted in Fig. 4(c) and (d). The trap densities in nitride layer were defined as  $4\times10^{19}$  cm<sup>-3</sup> for the planar SONOS device and 1×10<sup>20</sup> cm<sup>-3</sup> for the GAA SONOS device with uniform trap distributions which are in a proper range of values [15-17]. The tunnel-oxide, nitride, blocking-oxide thickness are 3, 7 and 5 nm, respectively. The body doping concentration is  $1 \times 10^{18}$  ions/cm<sup>3</sup> in common for the two devices. The gate length is 42 nm for the planar SONOS cell but 100 nm for GAA SONOS cell. The silicon radius of the GAA SONOS device is 15 nm [9]. Here, the nonoverlap length is 5 nm for both devices. The I<sub>D</sub>-V<sub>G</sub> curves of the devices with source/drain overlapped structure are given by solid symbols. From the simulated I<sub>D</sub>-V<sub>G</sub> plots, the SSs in programmed state are larger compared to those in erased state for both devices except for the planar SONOS device with source/drain nonoverlap structure. It can be explained by a short channel effect induced by a nonuniformly trapped charge distribution in nitride layer. The programmed charge density in the nitride layer shows a peak near the center region of the channel and decreases going to the both edges. This kind of nonuniform distribution comes from normal program operation in which the electric field responsible for the FN (Fowler Nordheim) tunneling is weaker near both edges due to a fringing electric field. Thus, the V<sub>th</sub> near the center region of the channel is a bit higher than those in the channel edges. This means that an effective channel length of the device is shorter than the physical gate length. For this reason, the I<sub>D</sub> (or I<sub>BL</sub>) is affected more easily by the drain (or bit-line) bias, which is called DIBL (drain-induced barrier-lowering). This explanation was confirmed by the simulation result which was obtained from the SONOS devices with gate lengths of 42 nm and 1 µm. SS degradation of the 1 µm device is negligible as shown in Fig. 5. The gate bias

**Fig. 5.** 2D TCAD simulated  $I_D$ - $V_G$  curves in initial, programmed and erased states for the planar SONOS devices with 42 nm and 1 $\mu$ m. SSs are extracted in each plot.

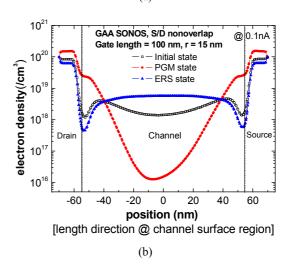

applied to read  $I_D$ - $V_G$  curves of a cell makes the electric field in the channel, and the field intensity is different for different cell states (program and erase). The electric field in the programmed cell is stronger near the edge parts of the channel than that of the erased cell due to the lower charge near the edge regions at a fixed channel current. The distribution of the electric field is reflected in that of the electron charge density, and the distributions for two different cells along the channel are shown in Fig. 6 and 7. As shown in these figures, effective channel length is shorter when programmed than when erased, which gives SS degradation due to DIBL. In addition, SS even at initial state is more degraded than that in erased state owing to the same reason.

This channel length variation effect is more significant for the source/drain nonoverlap structure compared to that in the source/drain overlap structure because the fringing electric field from the gate influences more effectively electron density in the S/D nonoverlap region. This results in remarkable electron density distribution difference between programmed and erased states as presented in Fig. 6(b) and 7(b). This effect is more serious in the planar structure since the simulated GAA SONOS device has a smaller channel length variation from the longer gate length and stronger gate controllability. Moreover, the fringing field can induce a side wall channel inversion before the main channel is turned on leading to the degradation of SS for a programmed device with planar structure while it does

**Fig. 6.** Electron densities in initial, programmed and erased states at 0.1 nA of read current along the surface of silicon channel with a length direction for (a) the S/D overlap, (b) S/D nonoverlap structure for the planar SONOS device.

not happen in a device with GAA structure of surrounding the channel [8]. Therefore, more remarkable SS degradation is observed in the measured planar TANOS memory cell in programmed state as shown in Fig. 3(b).

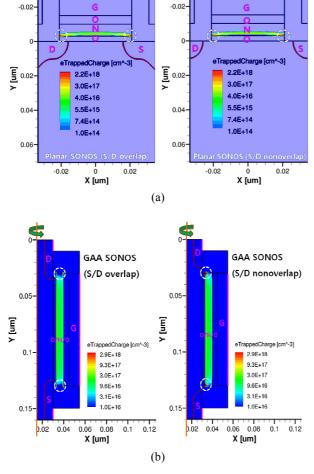

On the other hand, during programming procedure, more electrons are trapped in the center of nitride layer in the two simulated devices. After that, when they are erased, the electrons trapped at the edges of nitride layer are not detrapped easily and the remained charge can have an effect on I-V characteristics as shown in Fig. 8(a) and (b). Lancher *et al.* reported that localized electron charge over source/drain (S/D) region in nitride layer not only influence V<sub>th</sub> but also SS [7]. SS increases as the charge is getting closer to the bottom side of the nitride

**Fig. 7.** Electron densities in initial, programmed and erased states at 0.1 nA of read current along the surface of silicon channel with a length direction for (a) the S/D overlap, (b) S/D nonoverlap structure for the GAA SONOS device.

layer or the density of the charge increases. Similarly, oxide charges over the vicinity of the S/D region have an effect on the SS [6]. The crowded oxide charges located on the relatively small S/D overlap region can repulse the electrons in the S/D and channel region. It is followed by SS degradation owing to the decrease of subthreshold current in the channel surface and degradation of gate controllability.

In the analogous way, the more increased subthreshold slope is represented for the planar device with 5 nm of S/D nonoverlap structure in erased state compared to that in programmed state where it has the dense trapped electron charge of about  $2\times10^{18}$  cm<sup>-3</sup> at the bottom edges of nitride layer as shown in Fig. 8(a). Comparing the both structures, the GAA structure is immune to the SS

**Fig. 8.** Electron trapped charge distributions for the (a) planar SONOS, (b) GAA SONOS devices after erase operation where the both devices were programmed previously.

degradation effect induced by the charge at the edges because of its strong gate controllability to the channel region as shown in Fig. 4(c). However, the  $I_D$ - $V_G$  curve of the measured GAA SONOS device represents an opposite way from the simulation results as shown in Fig. 3(a). It shows remarkably more degraded SS in erased state compared to that in programmed state. This can be elucidated by the interface states generation due to diffused  $h^*$  species from the  $Si/SiO_2$  interface after erase operation which results in the subthreshold degradation [18].

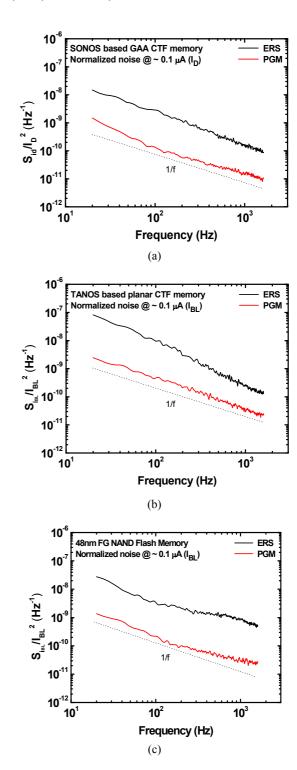

To investigate the generation of interface traps in erased state, we measured low frequency noise of the GAA SONOS and planar TANOS devices. The normalized current power spectral densities  $[S_{id}/I_D^2]$  (or  $S_{iBL}/I_{read}^2$ ) at about 0.1  $\mu$ A of the read current in the ohmic regime for randomly selected flash memory cells are compared in both erased and programmed states for

**Fig. 9.** Normalized current power spectral densities  $[S_{id}/I_D^2 (S_{iBI}/I_{read}^2)]$  measured at a read current of 0.1  $\mu$ A in both programmed and erased states for the (a) GAA SONOS, (b) planar TANOS, (c) 48 nm FG flash memory cells.

each device as shown in Fig. 9(a) and (b). The magnitude of  $S_{id}/I_D^2$  in erased state is about 1 order higher than that in programmed state for both the CTF memories which

means that more interface traps exist in erased state comparing to that in programmed state. Villa et al. proved correlation between interface trap density and 1/f noise in metal-oxide semiconductor field effect transistors (MOSFETs) through experiment [19]. The  $N_{\rm IT}$ derived from the suggested 1/f noise numerical model equation considering both carrier number and mobility fluctuations are also quite consistent with that of C-V measurement. It indicates that the flicker noise measurement is a useful technique to characterize interface and oxide traps in the MOSFETs with charge pumping method. The traps in nitride layer may also have an effect on the flicker noise spectrum in the SONOS and TANOS memory devices. However, we can understand that the generation of traps is a negligible factor for 1/f noise since the magnitude of  $S_{id}/I_D^2$  in a cell of 48 nm floating-gate (FG) NAND flash memory as shown in Fig. 9(c) is comparable with those of the two CTF memory devices. The tunnel oxide thickness of the measured FG NAND flash memory is about 7 nm which is much thicker than the measured two CTF memory devices, and the charge storage layer is not nitride layer but floating gate. Therefore, it indicates that the main noise source is originated from the interface between Si and tunnel oxide.

$N_{\rm IT}$  generation induced by the movement of  $h^*$  species occurred in both of the two CTF memory devices and FG memory device as well after erase operation as demonstrated by noise measurement. It is noted that the induced interface states of the measured GAA SONOS memory cell in erased state function as a more prominent source for determining the subthreshold current properties than those in the planar TANOS and FG memory devices. This is because the measured cylindrical GAA SONOS devices have longer channel length and is not influenced by the channel side wall turn-on effect because the gate surrounds the channel.

# IV. CONCLUSIONS

We have studied which makes SSs of memory cells in between programmed and erased states different for TANOS based NAND flash memory cell and GAA SONOS based flash memory unit cell each by employing TACD simulation and noise measurement. The deteriorated SS comes from the short channel effect induced by nonuniform charge distribution in nitride layer for both of the programmed devices. In addition, the remained localized trapped electron charge in nitride edge after erase operation is shown for both devices and it has an effect on SS degradation particularly in the simulated planar SONOS device with S/D nonoverlap structure while it is negligible in the GAA structure. On the other hand,  $N_{IT}$  generation originated from released  $h^*$  species from the Si/SiO<sub>2</sub> interface after erase operation can be explained by the low frequency noise measurement. The increased  $S_{id}/I_D^2$  after erase operation indicates the interface states generation and it is a critical factor for degrading SS of the measured GAA SONOS memory cell.

#### ACKNOWLEDGMENTS

This work was supported by the IT Research and Development Program of Ministry of Knowledge Economy/Korea Evaluation Institute of Industrial Technology under Grant 10035320 (Development of novel 3-D stacked devices and core materials for the next-generation Flash memory).

## REFERENCES

- [1] J.-D. Lee, S.-H. Hur, and J.-D Choi, "Effects of Floating-Gate Interference on NAND Flash Memory Cell operation," *IEEE Electron Device letters*, vol. 23, no. 5, pp. 264-266, 2002.

- [2] Y. Wang, M. White, "An analytical retention model for SONOS nonvolatile memory devices in the excess electron state," *Solid-State Elect.*. vol. 49, no, pp. 97-107, 2005.

- [3] S. D. Suk, S.-Y. Lee, S.-M. Kim, E.-J. Yoon, M.-S Kim, M. L, C. W. Oh, K. H. Yeo, S. H. Kim, D.-S. Shin, K.-H. Lee, H. S. Park, J. N. Han, C. J. Park, J.-B. Park, D.-W. Kim, D.-W. Kim, D. P, and B.-I. Ryu, "High Performance 5nm radius Twin Silicon Nanowire MOSFET(TSNWFET): Fabrication on Bulk Si Wafer, Characteristics, and Reliability", *Technical Digest of IEDM*, pp. 717-713, 2005.

- [4] K. H. Yeo, S. D. Suk, M. L. Li, Y.-Y Yeoh, K. H. Cho, K.-H Hong, S. Yun, M. S. Lee, N. Cho, K. Lee, D. H, B. Park, D.-W. Kim, D. Park, and B.-I. Ryu, "Gate-All-Around (GAA) Twin Silicon

- Nanowire MOSFET (TSNWFET) with 15nm Length Gate and 4nm Radius Nanowires", *Technical Digest of IEDM*, pp. 539-542, 2006.

- [5] Y. Park, J. Choi, C. Kang, C. Lee, C. Lee, Y. Shin, B. Choi, J. Kim, S. Jeon, J. Sel, J. Park, K. Choi, T. Yoo, J. Sim, and K. Kim, "Highly Manufacturable 32Gb Multi – level NAND Flash Memory with 0.0098 μm² Cell Size using TANOS(Si – Oxide – Al<sub>2</sub>O<sub>3</sub> – TaN) Cell Technology", *Technical Digest* of IEDM, 346900, 2006.

- [6] A. Fayrushin, K. Seol, J. Na, S. Hur, J. Choi and K. Kim, "The New Program/Erase Cycling Degradation Mechanism of NAND Flash Memory Devices", *Technical Digest of IEDM*, pp. 823-826, 2009.

- [7] L. Larcher, G. Verzellesi, P. Pavan, E. Lusky, I. Bloom and B. Eitan, "Impact of Programming Charge Distribution on Threshold Voltage and Subthreshold Slope of NROM Memory Cells", *IEEE Trans. Electron Devices*, vol. 49, no. 11, pp. 1939-1946, 2002.

- [8] H.-T. Lue, T.-H. Hsu, S.-Y. Wang, Y.-H. Hsiao, E.-K. Lai, L.-W. Yang, T. Yang, K.-C. Chen, K.-Y. Hsieh, R. Liu, and C.-Y. Lu, "Understanding STI Edge Fringing Field Effect on the Scaling of Charge-Trapping (CT) NAND Flash and Modeling of Incremental Step Pulse Programming (ISPP), Technical Digest of IEDM, pp. 839-842, 2009.

- [9] J.-G. Yun, G. Kim, J.-E. Lee, Y. Kim, W. B. Shim, J.-H. Lee, H. Shin, J. D. Lee, B.-G. Park, "Single-Crystalline Si Stacked Array (STAR) NAND Flash Memory," *IEEE Trans. Electron Devices*, vol. 58, no. 4, pp. 1006-1013, 2011.

- [10] J. Kim, C. Kang, S.-I. Chang, J. Kim, Y. Jeong, C. Park, J.-H. Kang, S.-H. Kim, S. Hwang, B.-I. Choe, J. Park, J. Chung, Y. Park, J. Choi, C. Chung, "New phenomena for the Lifetime Prediction of TANOS-based Charge Trap NAND Flash Memory", *Device Research Conference (DRC)*, pp. 99-100, 2010.

- [11] S.-H Bae, J.-H Lee, H.-I kwon, J.-R Ahn, J.-C Om, C. H. Park, "The 1/f Noise and Random Telegraph Noise Characteristics in Floating-Gate NAND Flash Memories", *IEEE Trans. Electron Devices*, vol. 56, no. 8, pp. 1624-1630, 2009.

- [12] J. Fu, K. D. Buddharaju, S. H. G. Teo, C. Zhu, M. B. Yu, N. Singh, G. Q. Lo, N. Balasubramanian, and D. L. Kwong, "Trap Layer Engineered Gate-All-Around Vertically Stacked Twin Si-Nanowire

- Nonvolatile Memory", *Technical Digest of IEDM*, pp. 79-82, 2007.

- [13] D. K, J. Park, K. Kim, Y. Y, S. Ahn, Y. Park, J. Kim, W. Jeong, J. Kim, M. Park, B. Yoo, S. Song, H. Kim, J. Sim, S. Kwon, B. Hwang, H. Park, S. Kim, Y. Lee, H. Shin, N. Yim, K. Lee, M. Kim, Y. Lee, J. Park, S. Park, J. Jung, K. Kim, "Integration Technology of 30nm Generation Multi-Level NAND Flash for 64Gb NAND Flash Memory", Technical Digest of IEDM, pp. 12-13, 2007.

- [14] Sentaurus Device Simulations, www.synopsys.com.

- [15] A. Mauri, S. M. Amoroso, C. M. Compagnoni, A. Maconi, A. S. Spinelli, "Comprehensive numerical simulation of threshold-voltage transients in nitride memories", *Solid-State Elect.*, vol. 56, pp. 23-30, 2011.

- [16] E. Gnani, S. Reggiani, A. Gnudi, G. Baccarani, J. Fu, N. Singh, G. Q. Lo, D. L. kwong, "Modeling of Nonvolatile Gate-All-Around Charge-Trapping SONOS Memory Cells", *Solid-State Elect.*, vol. 54, pp. 997-1002, 2010.

- [17] E. Nowak, A. Hubert, L. Perniola, T. Ernst, G. Ghibaudo, G. Reimbold, B. De Salvo, F. Boulanger, "In-Depth Analysis of 3D Silicon Nanowire SONOS Memory Characteristics by TCAD Simulations," *Proc. IMW Tech. Dig., pp. 116-119, 2010.*

- [18] S. H. Seo, G.-C. Kang, K. S. Roh, K. Y. Kim, S. Lee, K.-J. Song, C. M. Choi, S. R. Park, K. Jeon, J.-H. Park, B.-G. Park, J. D. Lee, D. M. Kim, and D. H. Kim, "Dynamic bias temperature instability-like behaviors under Fowler-Nordheim program/erase in nanoscale silicon-oxide-nitride-oxide-silicon memories", *Appl. Phys. Lett.*, vol. 92, 133508, 2008.

- [19] S. Villa, G. De Geronimo, A. Pacelli, A. L. Lacaita, and A. Longoni, "Application of 1/f noise measurements to the characterization of near-interface oxide traps in ULSI n-MOFETs", Microelectron. Reliab., vol. 38, pp. 1919-1923, 1998.

Myoung-Sun Lee received his B.S. degree from Kookmin University, Seoul, Korea, in 2009 and the M.S. degree from Seoul National University, Seoul, in 2011. He is currently working toward the Ph.D.

degree in the Department of electrical engineering, Seoul National University (SNU), Seoul, Korea. His current research interests include the characterization, measurement, simulation, and modeling of 3-dimensional NAND Flash memories.

Sung-Min Joe received his B.S. and M.S. degrees from Kyung-book National University (KNU), Daegu, Korea, in 2004 and 2010, respectively. He is currently working toward the Ph.D. degree in the Department of electrical engineering, Seoul National

University (SNU), Seoul, Korea. His current research interests include the characterization, measurement, and modeling of LFN in NAND flash memory.

Jang-Gn Yun received was born in Deajeon, korea, in 1980. He received the B.S. and M.S. degrees in electronics engineering from Chungnam National University, Deajeon, in 2003 and 2006, respectively, and the Ph.D. degree in electrical engineering

from Seoul National University, Seoul, Korea, in 2010. From June 2004 to May 2005, he was with the Instit de Microélectronique, Elctromagnétisme et Photonique, Grenoble, France, for an international joint research program supported by the Korean Science and Engineering Foundation. He is currently working with Samsung Electronics Company Ltd., Suwon, Korea. He is the author or coauthor of more than 150 papers in domestic and international journals and conferences. His main research interests include salicide process, siliconon-insulator devices, and Flash memories for nanoscale complementary metal-oxide-semiconductor and nonvolatile memory technologies. Dr. Yun has served as a Reviewer of the IEEE Transactions on Electron Devices, the IEE Electron Device Letters, the American Chemical Society Applied Materials and Interfaces, and the International Journal of Physical Sciences since 2008. He was the recipient of one bronze and two silver prizes from Samsung Humantech Thesis Prize in 2003, 2009, and 2010, respectively, and the Silver Prize from the IEEE Student Paper Contest held by IEEE Seoul Section in 2009.

Hyungcheol Shin received the B.S. (*magna cum laude*) and M.S. degrees in electronics engineering from Seoul National University, Seoul, Korea, in 1985 and 1987, respectively, and the Ph.D. degree in electrical engineering from the

University of California Berkeley, Berkeley, in 1993. From 1994 to 1996, he was a Senior Device Engineer with Motorola Advanced Custom Technologies. In 1996, he was with the Department of Electrical Engineering and Computer Sciences, Korea Advanced Institute of Science and Technology (KAIST), Daejeon, Korea. During his sabbatical leave from 2001 to 2002, he was a Staff Scientist with Berkana Wireless Inc., San Jose, CA, where he was in charge of CMOS RF modeling. Since 2003, he has been with the School of Electrical Engineering and Computer Science, Seoul National University. He has published over 450 technical papers in international journals and conference proceedings. He also wrote a chapter in a Japanese book on plasma charging damage and semiconductor device physics. His current research interests include flash memory, dynamic RAM cell transistor, nano-CMOS, CMOS RF, and noise. Prof. Shin was a committee member of the International Electron Devices Meeting. He was also a committee member of the IEEE Electron Devices Society Graduate Student Fellowship and of several international conferences, including the InternationalWorkshop on Compact Modeling and the Structures, Solid State Devices and Materials. He is a lifetime member of the Institute of Electronics Engineers of Korea (IEEK). He received the Second Best Paper Award from the American Vacuum Society in 1991, the Excellent Teaching Award from the Department of Electrical Engineering and Computer Sciences, KAIST, in 1998, the Haedong Paper Award from IEEK in 1999, and the Excellent Teaching Award from Seoul National University in 2005, 2007, and 2009. He is listed in Who's Who in the World.

**Byung-Gook Park** received his B.S. and M.S. degrees in Electronics Engineering from Seoul National University (SNU) in 1982 and 1984, respectively, and his Ph. D. degree in Electrical Engineering from Stanford

University in 1990. From 1990 to 1993, he worked at the AT&T Bell Laboratories, where he contributed to the development of 0.1 micron CMOS and its characterization. From 1993 to 1994, he was with Texas Instruments, developing 0.25 micron CMOS. In 1994, he joined SNU as an assistant professor in the School of Electrical Engineering (SoEE), where he is currently a professor. In 2002, he worked at Stanford University as a visiting professor, on his sabbatical leave from SNU. He has been leading the Inter-university Semiconductor Research Center (ISRC) at SNU as the director from June 2008. His current research interests include the design and fabrication of nanoscale CMOS, flash memories, silicon quantum devices and organic thin film transistors. He has authored and co-authored over 580 research papers in journals and conferences, and currently holds 34 Korean and 7 U.S. patents. He has served as a committee member on several international conferences, including Micro- processes and Nanotechnology, IEEE International Electron Devices Meeting, International Conference on Solid State Devices and Materials, and IEEE Silicon Nanoelectronics Workshop (technical program chair in 2005, general chair in 2007). He is currently serving as an executive director of Institute of Electronics Engineers of Korea (IEEK) and the board member of IEEE Seoul Section. He received "Best Teacher" Award from SoEE in 1997, Doyeon Award for Creative Research from ISRC in 2003, Haedong Paper Award from IEEK in 2005, and Educational Award from College of Engineering, SNU, in 2006. Also, he received Haedong Academic Research Award from IEEK in 2008.

Sang-Sik Park received the B.S., M.S., and Ph.D degrees in electrical engineering from Seoul National University, in 1984, 1986, and 1989, respectively. He was a Researcher with the System LSI Institute of Semiconductor Division, Samsung

Elctronics, Korea, from 1989 to 2000, where he worked on CCD image sensors. Since 2000, he has been in Associate Professor at the Sejong University, Seoul, Korea. His main research interests are field emission display and CMOS active pixel image sensors.

Jong-Ho Lee received the B.S. degree from Kyungpook National University, Daegu, Korea, in 1987 and the M.S. and Ph.D. degrees from Seoul National University, Seoul, in 1989 and 1993, respectively, all in electronic engineering. In 1993, he worked on

advanced BiCMOS process development at ISRC, Seoul National University as an Engineer. In 1994, he was with the School of Electrical Engineering, Wonkwang University, Iksan, Chonpuk, Korea. In 2002, he moved to Kyungpook National University, Daegu Korea, as a Professor of the School of Electrical Engineering and Computer Science. Since September 2009, he has been a Professor in the School of Electrical Engineering, Seoul National University, Seoul Korea. From 1994 to 1998, he was with ETRI as an invited member of technical staff, where he worked on deep submicron MOS devices, device isolation. From August 1998 to July 1999, he was with Massachusetts Institute of Technology, Cambridge, as a postdoctoral fellow, where he was engaged in the research on sub-100 nm double-gate CMOS devices. He has authored or coauthored more than 140 papers published in refereed journals and over 250 conference papers related to his research and has been granted 88 patents in this area. His research interests include CMOS technology, non-volatile memory devices, thin film transistors, sensors, bio interface, neuromorphic technology, and device characterization and modeling. Prof. Lee is a Lifetime Member of the Institute of Electronics Engineers of Korea (IEEK). He has been served as a subcommittee member of IEDM, ITRS ERD member, a general chair of IPFA2011, and IEEE EDS Korea chapter chair. He received several best paper awards from international and domestic conferences, and also received several research awards for excellent research. In 2006, he was a recipient of the "This Month's Scientist Award" for his contribution in the development of practical high-density/high-performance 3dimensional nano-scale CMOS devices. He invented Saddle FinFET (or recess FinFET) for DRAM cell and NAND flash cell string with virtual source/drain, which have been applying for mass production.